vhdl 四位流水线乘法器

VHDL的乘法器设计——数字电路课程设计

cout=>c4,s=>s4(1));

------------------------------last u12:full_adder port map (a=>d4(1),b=>d4(2),cin=>d4(3),

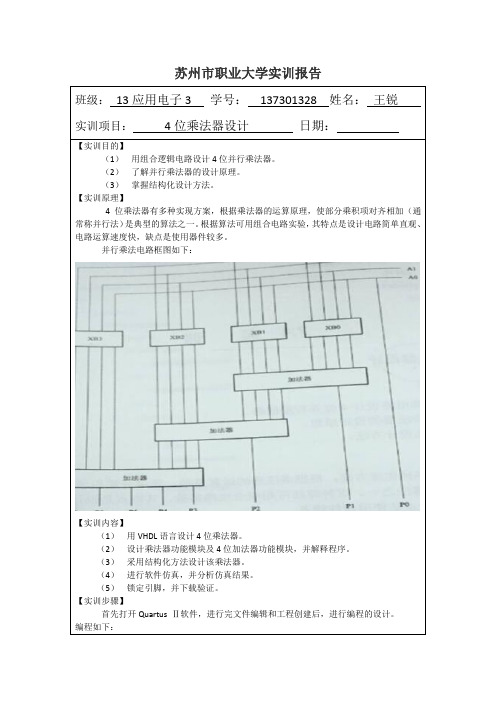

【第二章】:设计思路及方案 算法结构(无符号)

由上图可见,乘法的运算最终是加法的运算,两个 4BIT 输入,输出为 7BIT。 模块一、半加器:单比特输入相加,

模块二、全加器:由两个半加器组成,有一个进位输入,

模块三、进位保留加法器:

3

最终程序结构图

流水设计的原理:在前向割集上加入四级流水

图一 图二

elsif clk'event and clk='1' then

--------------------------------------first d1(1)<= x(1); d1(2)<= x(2); d1(3)<= x(3);

7

d1(4)<= x(4); d1(5)<= x(5); d1(6)<= x(6); d1(7)<=c1(1) ; d1(8)<=s1(1); d1(9)<= x(9); d1(10)<=x(10); d1(11)<=c1(2); d1(12)<=s1(2); d1(13)<=x(13); d1(14)<=c1(3) ; d1(15)<=s1(3) ; d1(16)<=x(16);

四位硬件乘法器

四位硬件乘法器一、实验目的:1、学习移位相加时序式乘法器的设计方法2、学习层次化设计方法3、学习原理图调用VHDL模块方法4、熟悉EDA仿真分析方法二、实验原理:乘法器的原理是,乘法通过逐项移位相加原理来实现,从被乘数的最地位开始,若为1,则乘数左移后与上一次的和相加;若为0,左移后以全零相加,直至被乘数的最高位。

ARICTL是乘法运算控制电路,它的START信号的上升沿与高电平有两个功能,即16位寄存器清0和被乘数A向移位寄存器SREG加载;它的低电平则作为乘法使能信号CLK位乘法时钟信号,被乘数加载于4位右移寄存器SREG 后,在时钟同步下由低位至高位逐位移出,当其为1时,与门ANDARITH打开,4位乘数B在同一节拍进入4位加法器,与上一节拍锁存在16位锁存器REG的高4位进行相加,其和在下一时钟节拍的上升沿被锁进此锁存器;而当被乘数的移出位为0时,与门全0输出。

如此往复,直至4个时钟脉冲后,乘法运算过程中止,此时REG的输出值即最后乘积。

三、实验设备:计算机一台操作系统:WINDOWS XP软件:ispDesignEXPERT System四、实验步骤:1、4位右移寄存器SREGLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SREG ISPORT(EN:IN STD_LOGIC;CLK: IN STD_LOGIC;LOAD:IN STD_LOGIC;DIN: IN STD_LOGIC_VECTOR(3 DOWNTO 0);QB: OUT STD_LOGIC);END SREG;ARCHITECTURE ART1 OF SREG ISSIGNAL REG:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS(CLK,LOAD)BEGINIF CLK'EVENT AND CLK='1'THENIF LOAD='1'THEN REG<=DIN;ELSEREG(2 DOWNTO 0)<=REG(3 DOWNTO 1);END IF;END IF;END PROCESS;QB<=REG(0);END ART1;2、4位加法器ADDERLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY ADDER ISPORT(CIN:IN STD_LOGIC_VECTOR;B,A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);S: OUT STD_LOGIC_VECTOR(4 DOWNTO 0);COUNT:OUT STD_LOGIC_VECTOR);END ADDER;ARCHITECTURE ART2 OF ADDER ISBEGINS<='0'&A+B;END ART2;3、选通与门模块ANDARITHLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ANDARITH ISPORT(ABIN:IN STD_LOGIC;DIN: IN STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END ANDARITH;ARCHITECTURE ART3 OF ANDARITH ISBEGINPROCESS(ABIN,DIN)BEGINFOR I IN 0 TO 3 LOOPDOUT(I)<=DIN(I) AND ABIN;END LOOP;END PROCESS;END ART3;4、锁存器REGLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY REG ISPORT(CLK,CLR,EN:IN STD_LOGIC;D: IN STD_LOGIC_VECTOR(4 DOWNTO 0);Q: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END REG;ARCHITECTURE ART4 OF REG ISSIGNAL R8S:STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINPROCESS(CLK,CLR)BEGINIF CLR='1'THEN R8S<=(OTHERS=>'0');ELSIF CLK'EVENT AND CLK='1'THENR8S(2 DOWNTO 0)<=R8S(3 DOWNTO 1);R8S(7 DOWNTO 3)<=D;END IF;END PROCESS;Q<=R8S;Q1<=R8S(7 DOWNTO 4);Q2<=R8S(3 DOWNTO 0);END ART4;5、运算控制器ARICTLLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY ARICTL ISPORT(CLK: IN STD_LOGIC;START: IN STD_LOGIC;CLKOUT: OUT STD_LOGIC;RSTALL: OUT STD_LOGIC;ARIEND: OUT STD_LOGIC);END ENTITY ARICTL;ARCHITECTURE ART5 OF ARICTL ISSIGNAL CNT:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINRSTALL<=START;PROCESS(CLK,START) ISBEGINIF START='1'THEN CNT<="0000";ELSIF CLK'EVENT AND CLK='1'THENIF CNT<4 THENCNT<=CNT+1;END IF;END IF;END PROCESS;PROCESS(CLK,CNT,START) ISBEGINIF START='0'THENIF CNT<4 THENCLKOUT<=CLK;ARIEND<='0';ELSE CLKOUT<='0';ARIEND<='1';END IF;ELSE CLKOUT<=CLK;ARIEND<='0';END IF;END PROCESS;END ARCHITECTURE ART5;6、顶层原理图。

用VHDL语言描述和实现乘法累加器设计

设计应完成的功能要求:(1)乘法累加器的结构如下图所示,5位的被乘数X和5位的乘数Y输入后,暂存在寄存器5位的寄存器A和B中,寄存器A和B的输出首先相乘,得到10位乘积,该乘积通过选择信号sel的控制,可以和10位寄存器C的输出相加,相加结果保存在寄存器C 中,实现乘法累加功能;也可以通过sel选择全零和乘积相加,实现乘法功能。

寄存器C 的输出也是系统输出Z。

:用VHDL语言描述和实现乘法累加器设计(2)要求乘法器和加法器都采用电路描述,不采用算法描述。

(3)要求寄存器A,B,C具有异步清零功能,全部寄存器采用相同的时钟和清零信号。

(4)设计的最终输出是设计报告。

设计报告的内容要求:(1)设计报告的格式采用标准的深圳大学设计报告格式(2)设计报告应包括该电路的总体结构图和主要功能模块组成图;(3)设计报告应根据总体结构图,说明VHDL代码编写的设计思路和基本原理;(4)设计报告应完成该电路的VHDL代码设计;(5)设计报告应完成该电路的VHDL仿真分析。

一、实验目的用VHDL语言描述和实现乘法累加器设计二、实验内容及步骤一.总体结构图设计思路及原理:首先,寄存器A、B、C具有异步清零功能,rest在clk之前调用,当复位信号rest为1时,寄存器A、B、C复位,当rest为0时,并且在它们同一时钟clk的上升沿到来时,输出将等于输入,起到了数据锁存功能。

同时,寄存器的输出Z既是整个结果的输出,也可以被内部引用,因此在定义Z的端口时,把端口类型定义为buffer。

5位的被乘数X和5位的乘数Y输入后,暂存在寄存器5位的寄存器A和B中,通过寄存器A、B的寄存,能够让不同时到达的数据X和Y能够在同一时钟的控制下同时参与运算,寄存器A和B的输出分别为x_temp和y_temp,他们首先相乘,得到10位乘积mul,该乘积通过选择信号sel的控制,当sel为1时,acc=z,即乘积mul可以和10位寄存器C的输出相加,相加结果保存在寄存器C中,实现乘法累加功能;当sel为0时,acc为全零,即选择全零和乘积相加,实现乘法功能。

数电— 4位并行乘法器的电路设计与仿真

# 155reset=0,a=15,b=14,y=162

# 170reset=0,a=15,b=14,y=178

# 185reset=0,a=15,b=14,y=210

# 200reset=0,a= 0,b= 0,y=210

# 225reset=0,a= 0,b= 0,y=156

reg a,b,ci;

wire s,co;

fulladder add0(s,co,a,b,ci);

initial

begin

a=1'b0;b=1'b0;ci=1'b1;

#15 a=1'b0;b=1'b0;ci=1'b0;

$monitor($time,"a=%d,b=%d,ci=%d,s=%d,co=%d",a,b,ci,s,co);

文档:分析文档、设计文档、测试文档、代码和总结。

设要有完整的组合逻辑电路设计步骤;

每一步骤完成要正确合理;

设计电路时分模块测试。

时间安排

分析设计阶段:周一至周二上午;

代码编写阶段:周二下午至周三;

代码测试优化阶段:周四;

仿真分析及总结:周五上午;

验收:周五下午。

验收标准

文档齐全(20分)。

注:无文档不可以进行下一步。

#15 a=1'b1;b=1'b1;ci=1'b1;

end

endmodule

//一位全加器加上最大延迟15ns,分析乘法器最大延时为90ns(六个全加器),

//实际测得乘法器延时75ns,即可输出正确结果。测试结果如下:

# 0reset=1,a= 1,b= 4,y= 0

VHDL四位加法器实验报告

硬件描述语言实验:四位加法器实验实验人姓名:王昭学号: 2010482062实验地点: B3-216 实验三:-- Quartus II VHDL Template-- Basic Shift Registerlibrary ieee;use ieee.std_logic_1164.all;entity adder4 isport(a ,b : in std_logic_vector (3 downto 0);ci : in std_logic;s : out std_logic_vector (3 downto 0);co :out std_logic);end entity;architecture rtl of adder4 issignal c0,c1,c2 : std_logic;begins(0) <= a (0) xor b(0) xor ci;c0<= (a(0) and b(0)) or (a(0) and ci) or (b(0) and ci);s(1)<=a(1) xor b(1) xor c0;c1<=(a(1) and b(1)) or (a(1) and c0) or (b(1) and c0);s(2)<=a(2) xor b(2) xor c1;c2<= (a(2) and b(2)) or (a(2) and c1) or (b(2) and c1);s(3)<=a(3) xor b(3) xor c2;co<= (a(3) and b(3)) or (a(3) and c2) or (b(3) and c2);end rtl;实验原理:a和b为两个四位的数,定义三个信号量,c0,c1,c2;低位进位si=0;s(0)=a(0)+b(0)+si;进位为c0;s(1)=a(1)+b(1)+c0;进位为c1;s(2)=a(2)+b(2)+c1;进位为c2;s(3)=a(3)+b(3)+c2;进位为co;低位进位si都为0;如果a+b的值大于15时,则co为1,s=a+b-16;如果不是大于15,则相加时则s=a+b的值,co=0;经仿真可以验证此四位加法器正确。

流水线乘法累加器EDA仿真

流水线乘法累加器EDA仿真Augusting1991(浙江XXXX XXXXXX,浙江XX xxxxxx)摘要:为了能更好的理解、掌握和应用EDA技术,并在EDA工具软件的平台上,读懂相应的硬件描述语言HDL,进行流水线乘法累加器的混合输入设计仿真实验。

在流水线乘法累加器电路中,用到包括16位加法器(ADDER16B)、8位锁存器(FF0)、8位乘法器(MULT8B),然后通过顶层的原理图设计建立MUILADD工程,进行工程的逻辑编译和仿真测试,得出相对于的仿真波形。

通过本次实验能基本掌握EDA技术,使用QUARTUS II软件进行硬件描述语言的电路设计,掌握实验的基本流程,为下一步在硬件平台上的测试,到最后到FPGA的最终开放打下基础。

关键词:EDA技术;累加器;QUARTUS II;HDL中图分类号: TN91文献标识码: A文章编号:The Design of Toy Car Wireless Remote Control System Based on ZigBeeLI Bing(College of Information Science and Technology, Zhejiang Shuren University, Hangzhou 310015,China)Abstract: In order to better understand, grasp and application of EDA technology, and in the EDA software platform, read the corresponding hardware description language HDL, are pipelined multiplication accumulator mixed input design simulation experiment. In a pipelined multiplication accumulator circuit, used includes16 bit adder ( ADDER16B ), the 8latch ( FF0),8 bit multiplier ( MULT8B ), and then through the top of the schematic design to establish MUILADD engineering, engineering logic compilation and simulation test, obtains relative to the simulation waveform. Through this experiment to master the basic technique of EDA, use the QUARTUS II software for hardware description language in the circuit design, to grasp the basic flow, for the next step in the hardware platform of testing, finally to the FPGA final open lay the foundation.Key words: EDA ;accumulator ;QUARTUS II; HDL;0 引言随着基于PLD的EDA技术的发展和应用领域的扩大与深入EDA技术在电子信息、通信、自动控制及计算机应用领域的重要性日益突出。

9X9乘法表VHDL

9*9乘法器的VHDL的设计1 设计任务制作一个9*9乘法器2 设计说明输入两个四位二进制信号a,b分别作为被乘数和乘数,以8421bcd码编号,输入一个一位信号oc作为控制信号;输出两个四位二进制信号c,d分别作为结果的十位和个位,以8421bcd码编号。

3 设计结果3.1 原理图图1 原理图3.2 信号表a:被乘数,用4位二进制8421bcd码表示;b:乘数,用4位二进制8421bcd码表示;oc:控制信号;c:结果的十位,用4位二进制8421bcd码表示;d:结果的个位,用4位二进制8421bcd码表示;图2 信号表3.3仿真结果图3 oc、a、b分别为0、2、8和0、4、3时结果图4 oc、a、b分别为1、2、8和1、4、3时结果图5 oc、a、b分别为0、10、8和0、4、11时结果3.4 电路图图6 原理图3.5 程序清单LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY mul9 ISPORT (oc: IN std_logic;a,b: IN std_logic_vector (3 downto 0);c,d: OUT std_logic_vector(3 downto 0));END;ARCHITECTURE one OF mul9 ISBEGINPROCESS(a,b)BEGINIF(oc = '1') THENIF(a = "0001") THENCASE b ISWHEN "0001" =>c <= "0000"; d <= "0001"; WHEN "0010" =>c <= "0000"; d <= "0010";WHEN "0011" =>c <= "0000"; d <= "0011"; WHEN "0100" =>c <= "0000"; d <= "0100";WHEN "0101" =>c <= "0000"; d <= "0101"; WHEN "0110" =>c <= "0000"; d <= "0110";WHEN "0111" =>c <= "0000"; d <= "0111"; WHEN "1000" =>c <= "0000"; d <= "1000";WHEN "1001" =>c <= "0000"; d <= "1001"; WHEN OTHERS =>c <= "0000"; d <= "0000";END CASE;CASE b ISWHEN "0001" =>c <= "0000"; d <= "0010"; WHEN "0010" =>c <= "0000"; d <= "0100";WHEN "0011" =>c <= "0000"; d <= "0101"; WHEN "0100" =>c <= "0000"; d <= "1000";WHEN "0101" =>c <= "0001"; d <= "0000"; WHEN "0110" =>c <= "0001"; d <= "0010";WHEN "0111" =>c <= "0001"; d <= "0100"; WHEN "1000" =>c <= "0001"; d <= "0110";WHEN "1001" =>c <= "0001"; d <= "1000"; WHEN OTHERS =>c <= "0000"; d <= "0000";END CASE;ELSIF(a = "0011") THENCASE b ISWHEN "0001" =>c <= "0000"; d <= "0101"; WHEN "0010" =>c <= "0000"; d <= "0110";WHEN "0011" =>c <= "0000"; d <= "1001"; WHEN "0100" =>c <= "0001"; d <= "0010";WHEN "0101" =>c <= "0001"; d <= "0101"; WHEN "0110" =>c <= "0001"; d <= "1000";WHEN "0111" =>c <= "0010"; d <= "0001"; WHEN "1000" =>c <= "0010"; d <= "0100";WHEN "1001" =>c <= "0010"; d <= "0111"; WHEN OTHERS =>c <= "0000"; d <= "0000";END CASE;CASE b ISWHEN "0001" =>c <= "0000"; d <= "0100"; WHEN "0010" =>c <= "0000"; d <= "1000";WHEN "0011" =>c <= "0001"; d <= "0010"; WHEN "0100" =>c <= "0001"; d <= "0110";WHEN "0101" =>c <= "0010"; d <= "0000"; WHEN "0110" =>c <= "0010"; d <= "0100";WHEN "0111" =>c <= "0010"; d <= "1000"; WHEN "1000" =>c <= "0011"; d <= "0010";WHEN "1001" =>c <= "0011"; d <= "0101"; WHEN OTHERS =>c <= "0000"; d <= "0000";END CASE;ELSIF(a = "0101") THENCASE b ISWHEN "0001" =>c <= "0000"; d <= "0101"; WHEN "0010" =>c <= "0001"; d <= "0000";WHEN "0011" =>c <= "0001"; d <= "0101"; WHEN "0100" =>c <= "0010"; d <= "0000";WHEN "0101" =>c <= "0010"; d <= "0101"; WHEN "0110" =>c <= "0011"; d <= "0000";WHEN "0111" =>c <= "0011"; d <= "0101"; WHEN "1000" =>c <= "0100"; d <= "0000";WHEN "1001" =>c <= "0100"; d <= "0101"; WHEN OTHERS =>c <= "0000"; d <= "0000";END CASE;CASE b ISWHEN "0001" =>c <= "0000"; d <= "0110"; WHEN "0010" =>c <= "0001"; d <= "0010";WHEN "0011" =>c <= "0001"; d <= "1000"; WHEN "0100" =>c <= "0010"; d <= "0100";WHEN "0101" =>c <= "0011"; d <= "0000"; WHEN "0110" =>c <= "0011"; d <= "0110";WHEN "0111" =>c <= "0100"; d <= "0010"; WHEN "1000" =>c <= "0100"; d <= "1000";WHEN "1001" =>c <= "0101"; d <= "0100"; WHEN OTHERS =>c <= "0000"; d <= "0000";END CASE;ELSIF(a = "0111") THENCASE b ISWHEN "0001" =>c <= "0000"; d <= "0111"; WHEN "0010" =>c <= "0001"; d <= "0100";WHEN "0011" =>c <= "0010"; d <= "0001"; WHEN "0100" =>c <= "0010"; d <= "1000";WHEN "0101" =>c <= "0011"; d <= "0101"; WHEN "0110" =>c <= "0100"; d <= "0010";WHEN "0111" =>c <= "0100"; d <= "1001"; WHEN "1000" =>c <= "0101"; d <= "0110";WHEN "1001" =>c <= "0110"; d <= "0011"; WHEN OTHERS =>c <= "0000"; d <= "0000";END CASE;CASE b ISWHEN "0001" =>c <= "0000"; d <= "1000"; WHEN "0010" =>c <= "0001"; d <= "0110";WHEN "0011" =>c <= "0010"; d <= "0110"; WHEN "0100" =>c <= "0011"; d <= "0010";WHEN "0101" =>c <= "0100"; d <= "0000"; WHEN "0110" =>c <= "0100"; d <= "1000";WHEN "0111" =>c <= "0101"; d <= "0110"; WHEN "1000" =>c <= "0110"; d <= "0100";WHEN "1001" =>c <= "0111"; d <= "0010"; WHEN OTHERS =>c <= "0000"; d <= "0000";END CASE;ELSIF(a = "1001") THENCASE b ISWHEN "0001" =>c <= "0000"; d <= "1001"; WHEN "0010" =>c <= "0001"; d <= "1000";WHEN "0011" =>c <= "0010"; d <= "0111"; WHEN "0100" =>c <= "0010"; d <= "0110";WHEN "0101" =>c <= "0100"; d <= "0101"; WHEN "0110" =>c <= "0101"; d <= "0100";WHEN "0111" =>c <= "0101"; d <= "0110"; WHEN "1000" =>c <= "0111"; d <= "0010";WHEN "1001" =>c <= "1000"; d <= "0001"; WHEN OTHERS =>c <= "0000"; d <= "0000";END CASE;ELSEc <= "0000";d <= "0000";END IF;ELSE c <= "0000"; d <= "0000";END IF;END PROCESS;END one;4 实验总结通过这次课程设计,我进一步加深了对电子设计自动化的了解。

Verilog_HDL_四位移位乘法器

实验五四位移位乘法器一、实验代码:(led显示)module mult(mul,a,b);output [7:0] mul;//input ckl;input [3:0] a,b;reg [7:0] mul;wire [3:0] out1,out2,out3,out4;//wire [3:0] out2;//wire [3:0] out3;//wire [3:0] out4;//如果always快里有问题,用clk进行延时接受,确保无问题reg [7:0] temp=8'b0;reg [7:0] temp_mul=8'b0;multply cheng1(out1,a,b[3]);multply cheng2(out2,a,b[2]);multply cheng3(out3,a,b[1]);multply cheng4(out4,a,b[0]);always@ (a or b)begintemp={4'b0,out1};temp_mul=temp<<1;temp={4'b0,out2};temp_mul=temp_mul+temp;temp_mul=temp_mul<<1;temp={4'b0,out3};temp_mul=temp_mul+temp;temp_mul=temp_mul<<1;temp={4'b0,out4};mul=temp_mul+temp;endendmodulemodule multply(out,mul4,mul1);output [3:0] out;input [3:0] mul4;input mul1;reg [3:0] out;reg [3:0] tem;always@ (mul4 or mul1)begincase(mul1)1'b0: tem=4'b0;default: tem=mul4&4'b1111;endcaseout=tem;endendmodule二、管脚配置:通过拨动输入:a[0] input PIN_200a[1] input PIN_202a[2] input PIN_203a[3] input PIN_204b[0] input PIN_205b[1] input PIN_206b[2] input PIN_207b[3] input PIN_208led灯输出:mul[0] output PIN_191mul[1] output PIN_192mul[2] output PIN_193mul[3] output PIN_195mul[4] output PIN_196mul[5] output PIN_197mul[6] output PIN_198mul[7] output PIN_199三、实验连线:通过拨动输入:K1-K8:11-18Led灯显示连线:L1-L8:3-10四、电路工作原理手动拨动,开关k1-k8,根据Led灯的显示,亮表示1,不亮表示0来看结果。

基于VHDL语言的组合乘法器设计与仿真

i ii 《现代电子技术》20 05 年第 18 期总第 20 9 期þ 集 成 电 路 ü基于 VH DL 语言的组合乘法器设计与仿真刘姝延1 , 吴 志2 , 丁 红1 , 马秋明1( 1. 烟台师范学院 物理与电子工程学 院 山东 烟台 26 40 25; 2 . 烟台师范学院 基建处 山东 烟台 26 40 25 )摘 要: 基于 V H DL 的数字系统设计具有设计技术 齐全、方法灵活、支持广泛等优点, 同时也是 E DA 技术的重要 组成 部分。

文章用 V H DL 语言设计了左移法和进位节省法实现的两种组 合乘法器, 通过功能仿真 , 对两种乘法器的性能进 行了 比较, 从而得知后者的传输延迟时间小, 即速度较快 。

通过设 计实例, 介绍了利用 VH D L 语言进行数字系统设计的方法。

关键词: V H D L ; 组合乘法器; 左移法; 进位节省法中图分类号: T N 7 9 文 献标识码: B 文章编号: 1 00 4 37 3X ( 2 00 5) 18 0 77 0 2Design an d Simulation of Combin a tion a l Mu l t ip l ier Based on VH DL LanguageL I U Sh u y a n 1 , WU Zh i 2 , D I N G H o n g 1 , MA Q i u m i n g 1( 1 . Scho o l o f P hy s i cs a nd Elect ro nic E ng ineer ing , Ya nt ai Nor m a l Un iver si t y, Yant ai, 2 64 02 5, Ch ina;2 . Dep ar tmen t of Basic Bu ilding , Ya nt ai Nor m a l Un iver si t y, Yan t ai, 2 64 02 5, Ch ina)Abs t r a ct : Dig i t a l s y s t e ms u s i n g V H D L h a s t h e adv a n t a ges of comp r eh e n s i v e d e s i gn t e ch n o l o g i e s , fl e xi b l e des i g n met ho d s an d w i dera ng e s u p p o r t , it ′s al s o an i m po r t ant comp o n e n t o f E D A . T he co m b i n a t i o n a l mul t i p l i er s t o us e t w o met h o d s of left sh i f t s an d car rys a ve ar e des i g n e d i n V H D L la ng u a ge , by fun c t i o n a l s i mu l a t i o n , comp a r in g t h e pecu l i a ri t y o f t wo m ul t i p i er s , fi n d t h e car ry s a ve mu l t i - pl i er ′s del a y s h o r t e r , s p e ed fa st er. T h r o u g h d e si g n ex a mp l es , t h i s p a per in t r od u c es t h e met h o d of di g it al s y s t e ms des i g n based o nV H D L .Ke yw o rd s : VH D L ; comb i n a t i o n a l m ul t i p l i er ; met h o d o f left sh i ft ; met h o d o f carr y s a ve1 引 言随着计算机技术和大规模集成电路技术的发展, 传统 的通过 逻辑图 和布尔方 程设计 硬件电路 的方法 已大大落 后于当今 技术的发展, 取而代之 的是硬件描 述语言 H D L 使 用通用逻辑元、器件的限制, 电路尺寸大为缩小, 保密 程度大为提高。

eda乘法器设计

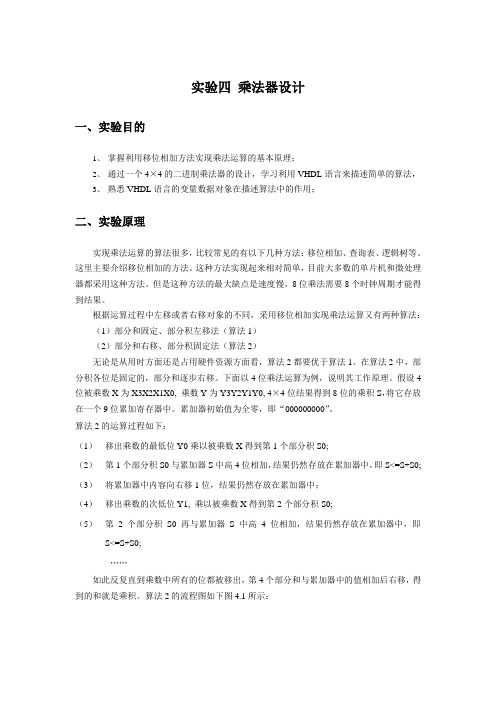

实验四乘法器设计一、实验目的1、掌握利用移位相加方法实现乘法运算的基本原理;2、通过一个4×4的二进制乘法器的设计,学习利用VHDL语言来描述简单的算法,3、熟悉VHDL语言的变量数据对象在描述算法中的作用;二、实验原理实现乘法运算的算法很多,比较常见的有以下几种方法:移位相加、查询表、逻辑树等。

这里主要介绍移位相加的方法。

这种方法实现起来相对简单,目前大多数的单片机和微处理器都采用这种方法。

但是这种方法的最大缺点是速度慢,8位乘法需要8个时钟周期才能得到结果。

根据运算过程中左移或者右移对象的不同,采用移位相加实现乘法运算又有两种算法:(1)部分和固定、部分积左移法(算法1)(2)部分和右移、部分积固定法(算法2)无论是从用时方面还是占用硬件资源方面看,算法2都要优于算法1。

在算法2中,部分积各位是固定的,部分和逐步右移。

下面以4位乘法运算为例,说明其工作原理。

假设4位被乘数X为X3X2X1X0, 乘数Y为Y3Y2Y1Y0, 4×4位结果得到8位的乘积S,将它存放在一个9位累加寄存器中。

累加器初始值为全零,即“000000000”。

算法2的运算过程如下:(1)移出乘数的最低位Y0乘以被乘数X得到第1个部分积S0;(2)第1个部分积S0与累加器S中高4位相加,结果仍然存放在累加器中,即S<=S+S0; (3)将累加器中内容向右移1位,结果仍然存放在累加器中;(4)移出乘数的次低位Y1, 乘以被乘数X得到第2个部分积S0;(5)第2个部分积S0 再与累加器S中高4位相加,结果仍然存放在累加器中,即S<=S+S0;……如此反复直到乘数中所有的位都被移出,第4个部分和与累加器中的值相加后右移,得到的和就是乘积。

算法2的流程图如下图4.1所示:在本实验中将设计一个如下图4.2所示的4位乘法器,输入信号X和Y分别是4位乘数和被乘数Y,CLK为输入时钟信号,START 是乘法启动信号。

太原理工大学 EDA实验 VHDL方式设计4位加法计数器

本科实验报告课程名称:CPLD/FPGA应用设计实验名称: VHDL方式设计4位加法计数器实验二VHDL方式设计4位加法计数器一、实验目的1、学习时序电路的VHDL描述方法。

2、掌握时序进程中同步、异步控制信号的设计。

3、熟悉EDA的仿真分析和硬件测试技术。

二、实验原理设计一个含计数使能、异步复位和并行预置功能的4位加法计数器,RST是异步复位信号,高电平有效;CLK是时钟信号;当使能信号ENA为“1”时,加法计数,COUT为计数进位输出,OUTY为计数输出。

三、实验仪器Windows xp操作系统;ispDesignEXPERT System软件;1016E开发板。

四、实验任务1、编写4位二进制加法计数器的VHDL程序。

2、在ispDesignEXPERT System上对编码器进行仿真。

3、将输入引脚连接到拨码开关,时钟输入锁定到相应频率的时钟信号,输出连接到发光二极管,下载后在实验板上验证其功能,记录实验结果。

五、实验步骤1、VHDL文本编辑在MUX+PLUS集成环境下,执行“file”中的“new”命令,弹出编辑文本类型的对话框,选择“text edior file”后单击“OK”。

先采用VHDL文本输入设计法实现4位二进制加法计数器的数字逻辑电路,并将文件cnt4.vhd保存到创建的目录下。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt4 isport(clk : in std_logic;rst : in std_logic;ena : in std_logic;outy :out std_logic_vector(3 downto 0);cout :out std_logic);end cnt4;architecture behav of cnt4 issignal cqi : std_logic_vector(3 downto 0);beginp_reg : process(clk,rst,ena)beginif rst ='1'then cqi <="0000";elsif clk'event and clk ='1'thenif ena='1' thencqi<=cqi+1;end if;end if;outy <= cqi;end process p_reg;cout <=cqi(0) and cqi(1) and cqi(2) and cqi(3);end behav;2、编译文件对cnt4.vhd设计文件进行编译,进而实现四位同步二进制加法计数器的数字逻辑电路3、功能时序仿真4位加法计数器功能仿真图4位加法计数器时序仿真图4、引脚锁定5、器件适配在ispDesignEXPERT System Project Navigator主窗口中选中左侧的ispLSI1016E器件,双击右侧的Compile Design选项,进行器件适配。

乘法器vhdl课程设计

乘法器vhdl课程设计一、课程目标知识目标:1. 理解乘法器的原理及其在数字信号处理中的应用。

2. 掌握VHDL语言的基本语法和结构,能够使用VHDL进行简单的程序编写。

3. 学习并掌握利用VHDL设计乘法器的方法,理解其位运算和结构设计。

技能目标:1. 能够运用所学知识,独立设计并实现一个简单的乘法器VHDL程序。

2. 培养学生利用电子设计自动化(EDA)工具进行代码编写、仿真和测试的能力。

3. 提高学生的问题分析能力,学会使用VHDL解决实际的数字电路设计问题。

情感态度价值观目标:1. 培养学生对于电子信息和数字电路设计的兴趣,激发学生创新精神和探索欲望。

2. 增强团队合作意识,通过小组讨论和协作,提高学生之间的沟通能力和协作解决问题的能力。

3. 强化学生的工程伦理观念,了解所学技术在国家经济发展和国防建设中的重要性,树立正确的价值观。

本课程针对高年级电子信息工程及相关专业学生设计,结合学生已具备的基础知识和课程性质,以实践性和应用性为导向,旨在通过具体的乘法器VHDL课程设计,将理论知识与实践技能相结合,提升学生解决实际工程问题的能力。

通过本课程的学习,学生应能够展示出上述具体的学习成果。

二、教学内容1. 乘法器原理回顾:包括乘法器的基本工作原理,不同类型的乘法器结构对比,以及乘法器在数字信号处理中的应用。

- 相关教材章节:第三章“数字电路基础”,第5节“算术逻辑单元”。

2. VHDL语言基础:VHDL的基本语法,数据类型,信号与变量,运算符,顺序与并行语句,进程,实体和架构等。

- 相关教材章节:第五章“硬件描述语言VHDL”,第1-3节。

3. 乘法器的VHDL设计方法:- 位运算乘法器设计原理与实现。

- 流水线乘法器设计原理与实现。

- 相关教材章节:第五章“硬件描述语言VHDL”,第4节“VHDL设计实例”;第六章“数字信号处理器的硬件实现”,第2节“乘法器的硬件实现”。

4. EDA工具的应用:利用EDA工具进行VHDL代码的编写、编译、仿真和测试。

VHDL语言完成4位十进制计数器、4位锁存器、测频控制器的设计

电子设计自动化实验实验名称综合性实验二、硬件描述语言的层次化设计实验设备(1)EDA实验箱(型号 ),(2)计算机,(3)EDA软件(QuartusII)实验目的1、熟悉EDA软件(QuartusII)的硬件描述语言输入设计方法;2、掌握VHDL语言的层次化设计方法和仿真分析方法;3、了解功能仿真、时序仿真和时序参数分析的意义。

实验容1、用VHDL语言完成4位十进制计数器、4位锁存器、测频控制器的设计,包括编译、综合、仿真;**2、采用层次化设计的方法,用VHDL语言的元件例化语句写出4位十进制频率计的顶层文件,并分别给出其测频功能和时序仿真分析波形图,并加以分析;**3、用EDA实验箱进行硬件验证,并分析测量结果;建议硬件测试实验电路采用NO.0 电路结构,待测信号F_IN接clock0;测频控制时钟CLK接clock2;**4、在2基础上将其扩展为8位十进制频率计,或带译码输出的4位十进制频率计。

实验报告要求根据以上实验容写出实验报告:1、简述4位频率计模块的工作原理及其设计、编译、仿真分析过程;2、给出模块设计文件、仿真测试文件、仿真结果波形图及其分析报告;3、简述硬件验证过程和验证结果。

1、简述4位频率计模块的工作原理根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的对输入信号脉冲计数允许的信号;1秒计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器清0信号。

这3个信号可以由一个测频控制信号发生器产生,即TESTCTL,它的设计要,TESTCTL的计数使能信号CNT_EN能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的ENA使能端进行同步控制。

当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要产生一个锁存信号LOAD,在该信号上升沿时,将计数器在前1秒钟的计数值锁存进各锁存器REG4B中,并由外部的7段译码器译出,显示计数值。

vhdl 四位流水线乘法器

实验二四位流水线乘法器一、实验目的1.了解四位并行乘法器的原理。

2.了解四位并行乘法器的设计思想和流水线的实现方法。

3.掌握用VHDL 语言实现基本二进制运算的方法。

二、实验内容与要求通过开关和键盘输入两组4BIT的二进制数据,按照二进制加法器原理进行加和,求出和及进位,并通过LED显示灯输出显示,完成编译、综合、适配、仿真、实验箱上的硬件测试。

三、实验原理流水线结构的并行乘法器的最大有点就是速度快,尤其实在连续输入的乘法器中,可以达到近乎单周期的运算速度。

流水线乘法器是组合逻辑电路实现无符号数乘法的方法上发展而来的。

其关键是在组合逻辑电路的基础上插入寄存器。

假如有被乘数A 和乘数B,首先用A 与B 的最低位相乘得到S1,然后再把A 左移1 位与B 的第2 位相乘得到S2,再将A 左移3 位与B 的第三位相乘得到S3,依此类推,直到把B 的所有位都乘完为止,然后再把乘得的结果S1、S2、S3……相加即得到相乘的结果。

需要注意的是,具体实现乘法器是,并不是真正的去乘,而是利用简单的判断去实现,举个简单的例子。

假如A 左移n 位后与B 的第n 位相乘,如果B 的这位为‘1’,那么相乘的中间结果就是A 左移n 位后的结果,否则如果B 的这位为‘0’,那么就直接让相乘的中间结果为0 即可。

带B 的所有位相乘结束后,把所有的中间结果相加即得到A 与B 相乘的结果。

在此基础上插入寄存器即可实现流水线乘法器。

四、实验平台(1)硬件:计算机、GX-SOC/SOPC-DEV-LABCycloneII EP2C35F672C8核心板(2)软件:Quartus II软件PIN_AF8 DATAOUT[4] LED4PIN_AE7 DATAOUT[5] LED5PIN_AF7 DATAOUT[6] LED6PIN_AA11 DATAOUT[7] LED7PIN_AE21 BCD[0] 数码管DP4BPIN_AB20 BCD[1]PIN_AC20 BCD[2]PIN_AF20 BCD[3]PIN_AE20 BCD[4] 数码管DP5BPIN_AD19 BCD[5]PIN_AC19 BCD[6]PIN_AA17 BCD[7]PIN_AA18 BCD[8] 数码管DP6BPIN_W17 BCD[9]PIN_V17 BCD[10]PIN_AB18 BCD[11]六、仿真截图七、硬件实现八、程序代码1---clkgen.vhdlibrary IEEE;-- 1HZuse IEEE.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clkgen isport (CLK : in std_logic;CLK1HZ: out std_logic);end entity;architecture clk_arch of clkgen issignal COUNT : integer range 0 to 50000000; --50MHZ -->1hz begin -- 50M/1=50000000 PROCESS(CLK)BEGINif clk'event and clk='1' thenIF COUNT= 50000000 thenCOUNT<=0;ELSE COUNT<=COUNT+1;END IF;END IF;END PROCESS;PROCESS(COUNT)BEGINIF COUNT= 5000000 THEN -- 1HZCLK1HZ<='1';ELSE CLK1HZ<='0';END IF;END PROCESS;end architecture;2—BCD-- 输出控制模块,把乘法器的输出转换成BCD码在数码管上显示、-- SCKZ.VHDlibrary IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity BIN2BCD isport ( DIN: in std_logic_vector(7 downto 0); ---The input 8bit binaryBCDOUT: out std_logic_vector(11 downto 0)--输出显示, 已转换成BCD码);end entity;architecture arch of BIN2BCD issignal data2,data3,data4 :std_logic_vector(9 downto 0);-- 输出数据缓存signal hundred,ten,unit:std_logic_vector(3 downto 0);--signal bcdbuffer:std_logic_vector(11 downto 0);---2'1111_1001_11=999beginBCDOUT<= bcdbuffer;bcdbuffer(11 downto 8)<=hundred;bcdbuffer(7 downto 4)<=ten;bcdbuffer(3 downto 0)<=unit;get_hundred_value:process(data2)beginDA TA2<="00"&DIN;---get hundred valueif data2>=900 thenhundred<="1001";--9data3<=data2-900;elsif data2>=800 thenhundred<="1000";--8data3<=data2-500;elsif data2>=700 thenhundred<="0111";--7data3<=data2-700;elsif data2>=600 thenhundred<="0110";--6data3<=data2-600;elsif data2>=500 thenhundred<="0101";--5data3<=data2-500;elsif data2>=400 thenhundred<="0100";--4data3<=data2-400;elsif data2>=300 thenhundred<="0011";--3data3<=data2-300;elsif data2>=200 thenhundred<="0010";--2data3<=data2-200;elsif data2>=100 thenhundred<="0001";--1data3<=data2-100;else data3<=data2;hundred<="0000";end if;end process; ---get_thousand_valueget_tens_value:process(data3) begin---get tens placeif data3>=90 thenten<="1001";--9data4<=data3-90;elsif data3>=80 thenten<="1000";--8data4<=data3-50;elsif data3>=70 thenten<="0111";--7data4<=data3-70;elsif data3>=60 thenten<="0110";--6data4<=data3-60;elsif data3>=50 thenten<="0101";--5data4<=data3-50;elsif data3>=40 thenten<="0100";--4data4<=data3-40;elsif data3>=30 thenten<="0011";--3data4<=data3-30;elsif data3>=20 thenten<="0010";--2data4<=data3-20;elsif data3>=10 thenten<="0001";--1data4<=data3-10;else data4<=data3;ten<="0000";end if;end process; ---get_ten_valueget_unit_value:process(data4)begin--unit's orderif (data4>0) thenunit<=data4(3 downto 0);else unit<="0000";end if;end process;end arch;3 multi4b --------------------------------------------------------------------------------/ -- DESCRIPTION : Signed mulitplier:-- AIN (A) input width : 4-- BIN (B) input width : 4-- Q (data_out) output width : 8-- 并行流水乘法器--------------------------------------------------------------------------------/--10 × 9 = 90-- 1 0 1 0-- 1 0 0 1 =-- --------------- 1 0 1 0-- 0 0 0 0 --partial products-- 0 0 0 0-- 1 0 1 0-- -------------------- 1 0 1 1 0 1 0--parallel : process all the inputs at the same time--pipeline : use several stages with registers to implement it----关键思想,插入寄存器library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity multi4b isport ( CLK: in STD_LOGIC; ---system clockAIN: in STD_LOGIC_VECTOR (3 downto 0); ---one inputBIN: in STD_LOGIC_VECTOR (3 downto 0);-- the other inputdata_out: out STD_LOGIC_VECTOR (7 downto 0)---the result ---make sure the biggest value ,i,e. 1111x1111=1110_0001 can be held in the register );end multi4b;architecture multi_arch of multi4b issignal A,B :std_logic_vector(3 downto 0); --input register---registers to hold the result of the first processing---registers added to make use of pipeline, the 1st stagesignal A_MULT_B0: STD_LOGIC_VECTOR (3 downto 0);signal A_MULT_B1: STD_LOGIC_VECTOR (3 downto 0);signal A_MULT_B2: STD_LOGIC_VECTOR (3 downto 0);signal A_MULT_B3: STD_LOGIC_VECTOR (3 downto 0);---register to hold the result of the multipliersignal C_TEMP : STD_LOGIC_VECTOR (7 downto 0);beginPROCESS(CLK,AIN,BIN)beginif CLK'EVENT AND CLK='1' THEN-- multiplier operand inputs are registeredA<= AIN;B<= BIN;-----------------Fist stage of the multiplier------------------here we get the axb(0),axb(1),axb(2),axb(3),i.e.partial products---put them into the responding registersA_MULT_B0(0) <= A (0) and B (0);----- multi 1 , get the a(0) and b(0), & put it into the register A_MULT_B0(0)A_MULT_B0(1) <= A (1) and B (0);A_MULT_B0(2) <= A (2) and B (0);A_MULT_B0(3) <= A (3) and B (0);--10 × 9 = 90-- 1 0 1 0-- 1 0 0 1 =-- --------------- 0 0 0 0 1 0 1 0-- 0 0 0 0 0 0 0 0 --partial products-- 0 0 0 0-- 1 0 1 0-- -------------------- 1 0 1 1 0 1 0A_MULT_B1(0) <= A (0) and B (1);A_MULT_B1(1) <= A (1) and B (1);A_MULT_B1(2) <= A (2) and B (1);A_MULT_B1(3) <= A (3) and B (1);A_MULT_B2(0) <= A (0) and B (2);A_MULT_B2(1) <= A (1) and B (2);A_MULT_B2(2) <= A (2) and B (2);A_MULT_B2(3) <= A (3) and B (2);A_MULT_B3(0) <= A (0) and B (3);A_MULT_B3(1) <= A (1) and B (3);A_MULT_B3(2) <= A (2) and B (3);A_MULT_B3(3) <= A (3) and B (3);end if;end process;--------------------Second stage of the multiplier---------------add the all the partial products ,then get the result of the multiplier C_TEMP<=( "0000" & A_MULT_B0 )+( "000"& A_MULT_B1 &'0' )+( "00" & A_MULT_B2 & "00" )+( '0'&A_MULT_B3 & "000" );--build a signal register output---输出寄存,利于实现流水data_out <= C_TEMP; --output registerend multi_arch;九、实验总结。

VHDL-4位计数器的设计

*******bcd译码器******library ieee;use ieee.std_logic_1164.all;entity decoder isport(bcd: in std_logic_vector(3 downto 0);y: out std_logic_vector(7 downto 0));end entity;architecture rtl of decoder isbeginprocess (bcd)begincase bcd iswhen "0000" => y<="11000000"; --0: h g f e d c b a when "0001" => y<="11111001"; --1when "0010" => y<="10100100"; --2when "0011" => y<="10110000"; --3when "0100" => y<="10011001"; --4when "0101" => y<="10010010"; --5when "0110" => y<="10000010"; --6when "0111" => y<="11111000"; --7when "1000" => y<="10000000"; --8when "1001" => y<="10010000"; --9when others => y<="11111111";end case;end process;end rtl;***********多路选择控制************library ieee;use ieee.std_logic_1164.all;entity mux isport (input_a:in std_logic_vector(3 downto 0); input_b:in std_logic_vector(3 downto 0);input_c:in std_logic_vector(3 downto 0);input_d:in std_logic_vector(3 downto 0);sel:in std_logic_vector(1 downto 0);y:out std_logic_vector(3 downto 0));end entity mux;architecture rtl of mux isbeginprocess(sel)isbeginif(sel="00")theny<=input_a;elsif(sel="01")theny<=input_b;elsif(sel="10")theny<=input_c;elsey<=input_d;end if;end process;end rtl;************分频************library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clk4ms isport (clk:in std_logic;y:buffer std_logic);end entity clk4ms ;architecture rtl of clk4ms issignal a:STD_LOGIC_VECTOR(17 DOWNTO 0); beginprocess(clk)isbeginif(clk'event and clk='1')thenif(a="100000") thena<="0000000";y<=not y;elsea<=a+'1';end if;end if;end process;end rtl;************计数器************library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt isport (clk,clr,en:in std_logic;a:out std_logic_vector(3 downto 0);b:out std_logic_vector(3 downto 0);c:out std_logic_vector(3 downto 0);d:out std_logic_vector(3 downto 0));end entity cnt ;architecture rtl of cnt issignal dout_0,dout_10,dout_100,dout_1000:std_logic_vector(3 downto 0); beginprocess(clr,clk,en)isbegina<=dout_0;b<=dout_10;c<=dout_100;d<=dout_1000;if clr='1' thendout_0<="0000";dout_10<="0000";dout_100<="0000";dout_1000<="0000";elsif(en='1')thenif(clk'event and clk='1')thenif(dout_0="1001")then ---计数dout_0<="0000";elsedout_0<=dout_0+'1';end if;elsif(clk'event and clk='1' and dout_0="1001")thenif(dout_10="1001") then ---计数dout_10<="0000";elsedout_10<=dout_10+'1';end if;elsif(clk'event and clk='1' and dout_0="1001" and dout_10="1001")thenif(dout_100="1001") then ---计数dout_100<="0000";elsedout_100<=dout_100+'1';end if;elsif(clk'event and clk='1' and dout_0="1001" and dout_10="1001" and dout_100="1001")thenif(dout_1000="1001") then ---计数dout_1000<="0000";elsedout_1000<=dout_1000+'1';end if;end if;end if;end process;end rtl;************位选************LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY wei ISPORT(clk4ms:IN STD_LOGIC;q:BUFFER STD_LOGIC_VECTOR(1 DOWNTO 0);d:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END ENTITY wei;ARCHITECTURE rtl OF wei ISBEGINPROCESS(clk4ms) ISBEGINIF(clk4ms 'EVENT AND clk4ms='1') THEN IF(q="11") THENq<="00";ELSEq<=q+'1';END IF;IF(q="00") THENd<="1000";ELSIF(q="01") THENd<="0100";ELSIF(q="10") THENd<="0010";ELSEd<="0001";END IF;END IF;END PROCESS;END ARCHITECTURE rtl;**********总程序*********LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY ZONG ISPORT( clr :IN STD_LOGIC;clk :IN STD_LOGIC;CLK4M:IN STD_LOGIC;en:IN STD_LOGIC;Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ZONG ;ARCHITECTURE a OF ZONG ISCOMPONENT cnt isport (clk,clr,en:in std_logic;a:out std_logic_vector(3 downto 0);b:out std_logic_vector(3 downto 0);c:out std_logic_vector(3 downto 0);d:out std_logic_vector(3 downto 0));END COMPONENT;COMPONENT MUX isport (input_a:in std_logic_vector(3 downto 0); input_b:in std_logic_vector(3 downto 0);input_c:in std_logic_vector(3 downto 0);input_d:in std_logic_vector(3 downto 0);sel:in std_logic_vector(1 downto 0);y:out std_logic_vector(3 downto 0));end COMPONENT;COMPONENT DECODER isport(bcd:in std_logic_vector(3 downto 0);y: out std_logic_vector(7 downto 0));end COMPONENT;COMPONENT WEI isport(clk4ms:in std_logic;d:out std_logic_vector(3 downto 0));end COMPONENT;COMPONENT CLK4MS isport(clk:in std_logic;y:out std_logic);end COMPONENT;SIGNAL aa,bb,cc,dd:STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL mm:STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL ss:STD_LOGIC;signal ww:STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINu1 : cnt PORT MAP(clk,clr,en,aa,bb,cc,dd);u2 : mux PORT MAP(aa,bb,cc,dd,ww,mm);u3 :decoder PORT MAP(mm,y);u4 : wei PORT MAP(ss,ww,dig);u5 : clk4ms PORT MAP(clk4m,ss);END a;。

4位乘法器设计

U2:ls283 port map(o1=>sb(4 downto 1),o2=>sa,res=>result(7 downto 3));

U3:and4aport map(a=>op2,en=>op1(2),r=>sc);

signal sf:std_logic_vector(3 downto 0);

signal sg:std_logic_vector(3 downto 0);

--signal tmpl:std_logic;

begin

sg<=('0'&sf(3 downto 1));

--tmpl<=op1(1);

u0:and4aport map(a=>op2,en=>op1(1),r=>se);

(3)在芯片引脚设计时,每个脚多对应的时钟脉冲不一样,要看清要求。

(4)了解并行乘法器的设计原理,在给输入引脚输出引脚时钟脉冲时,要符合时钟脉冲的要求。

成绩:指导教师签名:

result(1)<=sd(0);

result(2)<=sb(0);

--result(7 downto 0)<='00000000'

end count;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity and4ais

signal sb:std_logic_vector(4 downto 0);

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验二四位流水线乘法器一、实验目的1.了解四位并行乘法器的原理。

2.了解四位并行乘法器的设计思想和流水线的实现方法。

3.掌握用VHDL 语言实现基本二进制运算的方法。

二、实验内容与要求通过开关和键盘输入两组4BIT的二进制数据,按照二进制加法器原理进行加和,求出和及进位,并通过LED显示灯输出显示,完成编译、综合、适配、仿真、实验箱上的硬件测试。

三、实验原理流水线结构的并行乘法器的最大有点就是速度快,尤其实在连续输入的乘法器中,可以达到近乎单周期的运算速度。

流水线乘法器是组合逻辑电路实现无符号数乘法的方法上发展而来的。

其关键是在组合逻辑电路的基础上插入寄存器。

假如有被乘数A 和乘数B,首先用A 与B 的最低位相乘得到S1,然后再把A 左移1 位与B 的第2 位相乘得到S2,再将A 左移3 位与B 的第三位相乘得到S3,依此类推,直到把B 的所有位都乘完为止,然后再把乘得的结果S1、S2、S3……相加即得到相乘的结果。

需要注意的是,具体实现乘法器是,并不是真正的去乘,而是利用简单的判断去实现,举个简单的例子。

假如A 左移n 位后与B 的第n 位相乘,如果B 的这位为‘1’,那么相乘的中间结果就是A 左移n 位后的结果,否则如果B 的这位为‘0’,那么就直接让相乘的中间结果为0 即可。

带B 的所有位相乘结束后,把所有的中间结果相加即得到A 与B 相乘的结果。

在此基础上插入寄存器即可实现流水线乘法器。

四、实验平台(1)硬件:计算机、GX-SOC/SOPC-DEV-LABCycloneII EP2C35F672C8核心板(2)软件:Quartus II软件PIN_AF8 DATAOUT[4] LED4PIN_AE7 DATAOUT[5] LED5PIN_AF7 DATAOUT[6] LED6PIN_AA11 DATAOUT[7] LED7PIN_AE21 BCD[0] 数码管DP4BPIN_AB20 BCD[1]PIN_AC20 BCD[2]PIN_AF20 BCD[3]PIN_AE20 BCD[4] 数码管DP5BPIN_AD19 BCD[5]PIN_AC19 BCD[6]PIN_AA17 BCD[7]PIN_AA18 BCD[8] 数码管DP6BPIN_W17 BCD[9]PIN_V17 BCD[10]PIN_AB18 BCD[11]六、仿真截图七、硬件实现八、程序代码1---clkgen.vhdlibrary IEEE;-- 1HZuse IEEE.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clkgen isport (CLK : in std_logic;CLK1HZ: out std_logic);end entity;architecture clk_arch of clkgen issignal COUNT : integer range 0 to 50000000; --50MHZ -->1hz begin -- 50M/1=50000000 PROCESS(CLK)BEGINif clk'event and clk='1' thenIF COUNT= 50000000 thenCOUNT<=0;ELSE COUNT<=COUNT+1;END IF;END IF;END PROCESS;PROCESS(COUNT)BEGINIF COUNT= 5000000 THEN -- 1HZCLK1HZ<='1';ELSE CLK1HZ<='0';END IF;END PROCESS;end architecture;2—BCD-- 输出控制模块,把乘法器的输出转换成BCD码在数码管上显示、-- SCKZ.VHDlibrary IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity BIN2BCD isport ( DIN: in std_logic_vector(7 downto 0); ---The input 8bit binaryBCDOUT: out std_logic_vector(11 downto 0)--输出显示, 已转换成BCD码);end entity;architecture arch of BIN2BCD issignal data2,data3,data4 :std_logic_vector(9 downto 0);-- 输出数据缓存signal hundred,ten,unit:std_logic_vector(3 downto 0);--signal bcdbuffer:std_logic_vector(11 downto 0);---2'1111_1001_11=999beginBCDOUT<= bcdbuffer;bcdbuffer(11 downto 8)<=hundred;bcdbuffer(7 downto 4)<=ten;bcdbuffer(3 downto 0)<=unit;get_hundred_value:process(data2)beginDA TA2<="00"&DIN;---get hundred valueif data2>=900 thenhundred<="1001";--9data3<=data2-900;elsif data2>=800 thenhundred<="1000";--8data3<=data2-500;elsif data2>=700 thenhundred<="0111";--7data3<=data2-700;elsif data2>=600 thenhundred<="0110";--6data3<=data2-600;elsif data2>=500 thenhundred<="0101";--5data3<=data2-500;elsif data2>=400 thenhundred<="0100";--4data3<=data2-400;elsif data2>=300 thenhundred<="0011";--3data3<=data2-300;elsif data2>=200 thenhundred<="0010";--2data3<=data2-200;elsif data2>=100 thenhundred<="0001";--1data3<=data2-100;else data3<=data2;hundred<="0000";end if;end process; ---get_thousand_valueget_tens_value:process(data3) begin---get tens placeif data3>=90 thenten<="1001";--9data4<=data3-90;elsif data3>=80 thenten<="1000";--8data4<=data3-50;elsif data3>=70 thenten<="0111";--7data4<=data3-70;elsif data3>=60 thenten<="0110";--6data4<=data3-60;elsif data3>=50 thenten<="0101";--5data4<=data3-50;elsif data3>=40 thenten<="0100";--4data4<=data3-40;elsif data3>=30 thenten<="0011";--3data4<=data3-30;elsif data3>=20 thenten<="0010";--2data4<=data3-20;elsif data3>=10 thenten<="0001";--1data4<=data3-10;else data4<=data3;ten<="0000";end if;end process; ---get_ten_valueget_unit_value:process(data4)begin--unit's orderif (data4>0) thenunit<=data4(3 downto 0);else unit<="0000";end if;end process;end arch;3 multi4b --------------------------------------------------------------------------------/ -- DESCRIPTION : Signed mulitplier:-- AIN (A) input width : 4-- BIN (B) input width : 4-- Q (data_out) output width : 8-- 并行流水乘法器--------------------------------------------------------------------------------/--10 × 9 = 90-- 1 0 1 0-- 1 0 0 1 =-- --------------- 1 0 1 0-- 0 0 0 0 --partial products-- 0 0 0 0-- 1 0 1 0-- -------------------- 1 0 1 1 0 1 0--parallel : process all the inputs at the same time--pipeline : use several stages with registers to implement it----关键思想,插入寄存器library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity multi4b isport ( CLK: in STD_LOGIC; ---system clockAIN: in STD_LOGIC_VECTOR (3 downto 0); ---one inputBIN: in STD_LOGIC_VECTOR (3 downto 0);-- the other inputdata_out: out STD_LOGIC_VECTOR (7 downto 0)---the result ---make sure the biggest value ,i,e. 1111x1111=1110_0001 can be held in the register );end multi4b;architecture multi_arch of multi4b issignal A,B :std_logic_vector(3 downto 0); --input register---registers to hold the result of the first processing---registers added to make use of pipeline, the 1st stagesignal A_MULT_B0: STD_LOGIC_VECTOR (3 downto 0);signal A_MULT_B1: STD_LOGIC_VECTOR (3 downto 0);signal A_MULT_B2: STD_LOGIC_VECTOR (3 downto 0);signal A_MULT_B3: STD_LOGIC_VECTOR (3 downto 0);---register to hold the result of the multipliersignal C_TEMP : STD_LOGIC_VECTOR (7 downto 0);beginPROCESS(CLK,AIN,BIN)beginif CLK'EVENT AND CLK='1' THEN-- multiplier operand inputs are registeredA<= AIN;B<= BIN;-----------------Fist stage of the multiplier------------------here we get the axb(0),axb(1),axb(2),axb(3),i.e.partial products---put them into the responding registersA_MULT_B0(0) <= A (0) and B (0);----- multi 1 , get the a(0) and b(0), & put it into the register A_MULT_B0(0)A_MULT_B0(1) <= A (1) and B (0);A_MULT_B0(2) <= A (2) and B (0);A_MULT_B0(3) <= A (3) and B (0);--10 × 9 = 90-- 1 0 1 0-- 1 0 0 1 =-- --------------- 0 0 0 0 1 0 1 0-- 0 0 0 0 0 0 0 0 --partial products-- 0 0 0 0-- 1 0 1 0-- -------------------- 1 0 1 1 0 1 0A_MULT_B1(0) <= A (0) and B (1);A_MULT_B1(1) <= A (1) and B (1);A_MULT_B1(2) <= A (2) and B (1);A_MULT_B1(3) <= A (3) and B (1);A_MULT_B2(0) <= A (0) and B (2);A_MULT_B2(1) <= A (1) and B (2);A_MULT_B2(2) <= A (2) and B (2);A_MULT_B2(3) <= A (3) and B (2);A_MULT_B3(0) <= A (0) and B (3);A_MULT_B3(1) <= A (1) and B (3);A_MULT_B3(2) <= A (2) and B (3);A_MULT_B3(3) <= A (3) and B (3);end if;end process;--------------------Second stage of the multiplier---------------add the all the partial products ,then get the result of the multiplier C_TEMP<=( "0000" & A_MULT_B0 )+( "000"& A_MULT_B1 &'0' )+( "00" & A_MULT_B2 & "00" )+( '0'&A_MULT_B3 & "000" );--build a signal register output---输出寄存,利于实现流水data_out <= C_TEMP; --output registerend multi_arch;九、实验总结。