实验十寄存器及寄存器堆设计

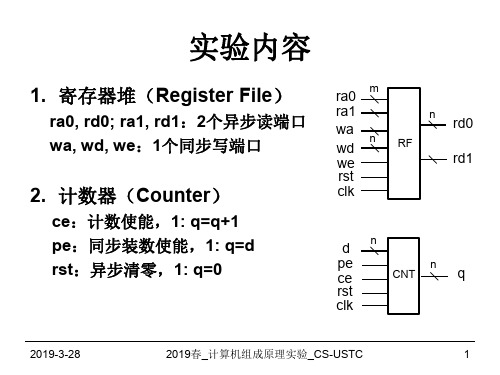

实验内容寄存器堆(RegisterFile)ra0,rd0;ra1,rd1

• 检查下载测试是否正确

• 检查代码设计,代码是否独立完成

2019-3-28

2019春_计算机组成原理实验_CS-USTC

3

实验报告

• 内容包括但不限于:逻辑设计(数据通路和状态 图)、核心代码、仿真/下载结果、结果分析、实 验总结、意见/建议等,附设计和仿真代码

• 实验检查后一周内提交实验报告

2019春_计算机组成原理实验_CS-USTC

2

实验要求和检查

• 完成1和3的的逻辑设计、仿真和下载测试

– 逻辑设计采用模块化设计 – 仿真3时忽略display – 下载测试时,时钟采用板载100MHz时钟,其他输入

由拨动开关和按钮开关设置,结果输出至LED指示灯 或7段数码管

• 查看1和2的电路性能和资源使用情况

rst

FIFO

16

display

4

out empty

- out, in:出/入队列数据

clk

full

- full, empty:队列空/满, 空/满时忽略出/入队操作

- display:8个数码管的控 制信号,显示队列状态

.

1. 2 3 2. 3

复位 数据1, 2, 3依次入队 列

数据1出队列

2019-3-28

– ftp://202.38.79.134/ 相应文件夹 – 文件名格式:Labn_学号_姓名.pdf (其中n为第几次

实验,不满足该格式的视为未提交实验报告)

• 严禁抄袭,否则作零分处理

2019-3-28

2019春_计算机组成原理实验_CS-USTC

4

The End

2019-3-28

2019春_计算机组成原理实验_CS-USTC

计算机寄存器实验报告

一、实验目的1. 理解计算机寄存器的概念、作用和分类;2. 掌握寄存器在计算机系统中的基本操作;3. 熟悉寄存器的控制信号及其工作原理;4. 培养实验操作能力和分析问题能力。

二、实验环境1. 实验设备:计算机组成原理实验箱、计算机、Proteus仿真软件;2. 实验软件:Proteus仿真软件、模型机仿真软件;3. 实验环境:实验室。

三、实验内容1. 寄存器基本概念及分类;2. 寄存器操作实验;3. 寄存器控制信号实验;4. 寄存器在计算机系统中的应用实验。

四、实验步骤1. 寄存器基本概念及分类实验(1)打开Proteus仿真软件,创建一个新的项目;(2)在项目中选择计算机组成原理实验箱中的寄存器模块;(3)观察寄存器的结构,了解寄存器的分类(如累加器、寄存器组、地址寄存器等);(4)总结寄存器的作用,如暂存数据、控制指令等。

2. 寄存器操作实验(1)在Proteus仿真软件中,搭建一个简单的寄存器操作电路;(2)设置输入数据,观察寄存器的输出;(3)通过改变输入数据,验证寄存器的存储功能;(4)总结寄存器操作的基本步骤。

3. 寄存器控制信号实验(1)在Proteus仿真软件中,搭建一个包含控制信号的寄存器电路;(2)观察控制信号对寄存器操作的影响;(3)通过改变控制信号,验证寄存器的读写功能;(4)总结寄存器控制信号的作用和意义。

4. 寄存器在计算机系统中的应用实验(1)在Proteus仿真软件中,搭建一个简单的计算机系统电路;(2)观察寄存器在计算机系统中的操作过程;(3)分析寄存器在计算机系统中的作用,如数据暂存、指令控制等;(4)总结寄存器在计算机系统中的应用。

五、实验结果与分析1. 通过实验,掌握了寄存器的基本概念、作用和分类;2. 熟悉了寄存器的操作过程,包括输入、输出、读写等;3. 了解寄存器控制信号的作用,以及它们对寄存器操作的影响;4. 分析了寄存器在计算机系统中的应用,如数据暂存、指令控制等。

通用寄存器存储器实验

计算机组成原理实验报告学号:姓名:提交日期:成绩:东北大学秦皇岛分校实验三通用寄存器存储器实验1、实验目的与要求实验目的:熟悉通用寄存器的数据通路;掌握通用寄存器的构成和运用;熟悉和了解存储器组织与总线组成的数据通路实验要求:在掌握了AX、BX运算寄存器的读写操作后,继续完成CX、DX通用寄存器的数据写入与读出;按照实验步骤完成实验项目,掌握存储部件在原理计算机中的运用。

2、实验原理通用寄存器:通用寄存器数据通路如下图所示。

由四片8位字长的74LS574组成CX、DX通用寄存器组。

途中X1 X2 X0定义为输出选通使能,SI、XP控制位为源选通选择。

RXW为寄存器数据写入使能,Q2 Q1 Q0及OP、DI为目的寄存器选择。

T4信号为寄存器、对战数据写入脉冲,上升沿有效。

准双向I/O 输入输出端口用于置数操作,经2片74LS245三态门与数据总线相连。

存储器:存储器是计算机的存储部件,用于存放程序和数据。

存储器是计算机信息存储的核心,是计算机必不可少的部件之一,计算机就是按存放在存储器中的程序自动有序不间断地进行工作。

本系统从提高存储器存储信息效率的角度设计数据通路,按现代计算机中最为典型的分段存储理念把存储器组织划分为程序段、数据段等,由此派生了数据总线(DBus)、指令总线(IBus)、微总线(μBus)等与现代计算机设计规范相吻合的实验环境。

实验所用的存储器电路原理如图3-1所示,该存储器组织由二片6116构成具有奇偶概念的十六位信息存储体系,该存储体系AddBus由IP指针和AR指针分时提供,E/M控位为“1”时选通IP,反之选通AR。

该存储体系可随机定义总线宽度,动态变更总线结构,把我们的教学实验提高到能与现代计算机设计规范相匹配与接轨的层面。

本系统存储器由三个部分组成,详见下表:分类 存储容量寻址范围 程序段 4K 0~07FF 数据段 4K 0~07FF 内存段256字节0~0FF程序存储器源与目的寻址3、实验内容 (1)手动/搭接方式1、实验连线连线 信号孔 接入孔 作用有效电平 1DRCKCLOCK单元手动实验状态的时钟来源上升沿打入程序段与数据段源寻址 程序段与数据段目的寻址 源使能 源编址注释 目的编址注释 X 2 X 1 X 0 E/M W XPMW R E/M WXP0 1 11 0 0 程序段字读1 0 0程序段字写 1 0 程序段偶读1 0程序段偶写 X 1程序段奇读X 1程序段奇写0 0 0数据段字读0 0 0数据段字写 1 0数据段偶读1 0数据段偶写 X 1数据段奇读X 1数据段奇写注:在【单拍】按钮下降沿写入2 W K6(M6) 总线字长:0=16位字操作,1=8位字节操作3 X2 K10(M10) 源部件定义译码端X2三八译码八中选一 低电平有效4 X1 K9(M9) 源部件定义译码端X15 X0 K8(M8)源部件定义译码端X06 SI K19(M19) 原寄存器编址:0=CX ,1=DX ,定义到M197 XP K7(M7)源寄存器奇偶位:0=偶地址,1=奇地址8 RXW K18(M18) 寄存器写使能,本例定义到M18位低电平有效9DIK217(M17) 目标寄存器编址:0=CX ,1=DX ,定义到M1710 OP K16(M16) 目标寄存器奇偶位:0=偶地址,1=奇地址2、CX 、DX 寄存器的写入和读出上图是CX 、DX 寄存器的写入步骤操作流程图,其中RWX=0.令RWX=1,如下改变操作位置数,即为CX 、DX 寄存器的读出(CX=2134,DX=2134)(2)手动/在线方式1、存储器数据段读写操作(1) 数据段写操作(字)向0址单元写入1234h 为例表述操作流程。

计算机组成原理实验报告_存储系统设计实验

实验四存储系统设计实验一、实验目的本实训项目帮助大家理解计算机中重要部件—存储器,要求同学们掌握存储扩展的基本方法,能设计MIPS 寄存器堆、MIPS RAM 存储器。

能够利用所学习的cache 的基本原理设计直接相联、全相联,组相联映射的硬件cache。

二、实验原理、内容与步骤实验原理、实验内容参考:1、汉字字库存储芯片扩展设计实验1)设计原理该实验本质上是8个16K×32b 的ROM 存储系统。

现在需要把其中一个(1 号)16K×32b 的ROM 芯片用4个4K×32b 的芯片来替代,实际上就是存储器的字扩展问题。

a) 需要4 片4个4K×32b 芯片才可以扩展成16K×32b 的芯片。

b) 目标芯片16K个地址,地址线共14 条,备用芯片12 条地址线,高两位(分线器分开)用作片选,可以接到2-4 译码器的输入端。

c) 低12 位地址直接连4K×32b 的ROM 芯片的地址线。

4个芯片的32 位输出直接连到D1,因为同时只有一个芯片工作,因此不会冲突。

芯片内数据如何分配:a) 16K×32b 的ROM 的内部各自存储16K个地址,每个地址里存放4个字节数据。

地址范围都一样:0x0000~0x3FFF。

b) 4个4K×32b 的ROM,地址范围分别是也都一样:0x000~0xFFF,每个共有4K个地址,现在需要把16K×32b 的ROM 中的数据按照顺序每4个为一组分为三组,分别放到4个4K×32b 的ROM 中去。

HZK16_1 .txt 中的1~4096个数据放到0 号4K 的ROM 中,4097~8192 个数据放到 1 号4K 的ROM 中,8193~12288 个数据放到2 号4K 的ROM 中,12289~16384个数据放到3 号4K 的ROM 中。

c) 注意实际给的16K 数据,倒数第二个4K(8193~12288 个数据)中部分是0,最后4K(12289~16384 数据)全都是0。

寄存器实验报告

寄存器实验报告一、实验目的1. 了解寄存器的分类方法,掌握各种寄存器的工作原理;2. 学习使用Verilog HDL 语言设计两种类型的寄存器。

二、实验设备PC 微机一台,TD-EDA 实验箱一台,SOPC 开发板一块。

三、实验内容寄存器中二进制数的位可以用两种方式移入或移出寄存器。

第一种方法是以串行的方式将数据每次移动一位,这种方法称之为串行移位(Serial Shifting),线路较少,但耗费时间较多。

第二种方法是以并行的方式将数据同时移动,这种方法称之为并行移位(Parallel Shifting),线路较为复杂,但是数据传送的速度较快。

因此,按照数据进出移位寄存器的方式,可以将移位寄存器分为四种类型:串行输入串行输出移位寄存器(Serial In- Serial Out)、串行输入并行输出移位寄存器(Serial In- Parallel Out)、并行输入串行输出移位寄存器(Parallel In- Serial Out)、并行输入并行输出移位寄存器(Parallel In-Parallel Out)。

本实验使用Verilog HDL 语言设计一个八位并行输入串行输出右移移位寄存器(Parallel In- Serial Out)和一个八位串行输入并行输出寄存器(Serial In- Parallel Out),分别进行仿真、引脚分配并下载到电路板进行功能验证。

四、实验步骤1.并行输入串行输出移位寄存器实验步骤1). 运行Quartus II 软件,选择File New Project Wizard 菜单,工程名称及顶层文件名称为SHIFT8R,器件设置对话框中选择Cyclone 系列EP1C6Q240C8 芯片,建立新工程。

2.) 选择File New 菜单,创建Verilog HDL 描述语言设计文件,打开文本编辑器界面。

3.) 在文本编辑器界面中编写Verilog HDL 程序,源程序如下:module SHFIT8R(din,r_st,clk,load,dout);input [7:0]din;input clk,r_st,load;output dout;reg dout;reg [7:0]tmp;always @(posedge clk)if(!r_st)begindout<=0;endelsebeginif(load)begintmp=din;endelsebegintmp[6:0]=tmp[7:1];tmp[7]=0;enddout<=tmp[0];endendmodule4). 选择File Save As 菜单,将创建的VHDL 设计文件保存为工程顶层文件名SHIFT8R.V。

寄存器相关实验

实验一一、实验目的二、实验设备三、工作原理(图)四、实验内容与结果实验内容:3种置数方式(进位保持、进位清零、进位置1),分别设置2组数据。

每个数据,分别验证5种操作(保持、循环右移、带进位循环右移、循环左移、带进位循环左移),并将结果以表格形式,列在下面,注意进位Z标志,一并记录。

实验结果:实验二移位运算实验内容1、往移位寄存器置数(进位清零)000FH,分别执行功能“循环右移”4次和“循环左移”4次后的结果(包括进位标识Z及进位指示灯的状态);2、往移位寄存器置数(进位置1)000FH,分别执行功能“带进位循环右移”8次和“带进位循环左移”8次后的结果;3、往移位寄存器置数(进位置1)8E60H,执行功能“带进位循环右移”4次,再执行“循环左移”4次后的结果;4、往移位寄存器置数(进位置1)1080H后,执行功能“带进位循环左移”4次后的结果;执行“循环左移”4次后的结果;5、置数(进位保持)3A00H,执行功能“带进位循环右移”4次,执行功能“循环右移”4次,执行功能“保持”后的结果。

结果记录参考格式例:置数(进位清零)执行功能执行结果进位及指示灯状态000FH “循环右移”4次0F000H 0 灭实验三存储器读写和总线控制实验实验内容1、通过数据总线,输入地址00H,读出此内存单元的值;再输入地址10H,读出此内存单元值;输入地址20H,读出此内存单元值;这些值代表什么?输入地址30FFH,此时存储的地址单元是多少?2、往RAM的任意地址存放十组以上的数据,然后读出并检查结果是否正确,并查看地址总线指示灯(A0。

A7)与数据总线指示灯(D0。

D15)的状态;3、通过键盘操作方式,输入并验证P32页的表3-1数据。

实验五微程序设计实验内容1、输入和验证实验材料P52页表5-3微代码并运行;2、参照P50页表5-2的微代码格式,试着编写8条简单的微代码,使之能循环运行,并参照表5-2下的微代码含义说明写出各条微代码含义。

2016新编计算机组成原理实验堆栈寄存器实验

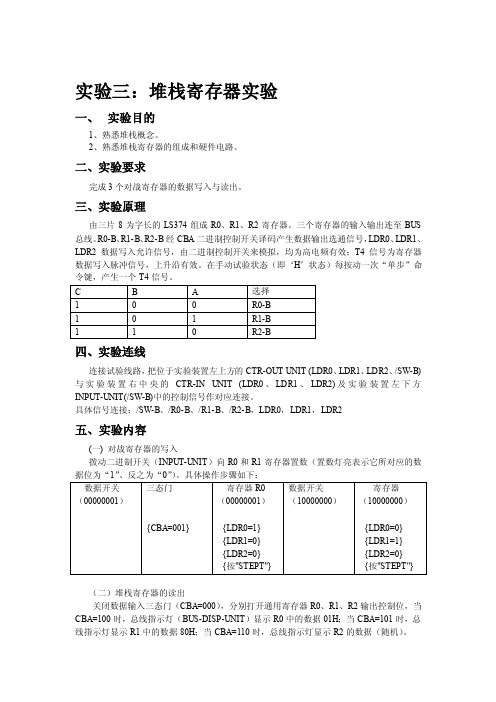

实验三:堆栈寄存器实验一、实验目的1、熟悉堆栈概念。

2、熟悉堆栈寄存器的组成和硬件电路。

二、实验要求完成3个对战寄存器的数据写入与读出。

三、实验原理由三片8为字长的LS374组成R0、R1、R2寄存器。

三个寄存器的输入输出连至BUS 总线。

R0-B、R1-B、R2-B经CBA二进制控制开关译码产生数据输出选通信号,LDR0、LDR1、LDR2数据写入允许信号,由二进制控制开关来模拟,均为高电频有效;T4信号为寄存器数据写入脉冲信号,上升沿有效。

在手动试验状态(即‘H’状态)每按动一次“单步”命令键,产生一个T4信号。

四、实验连线连接试验线路,把位于实验装置左上方的CTR-OUT UNIT (LDR0、LDR1、LDR2、/SW-B)与实验装置右中央的CTR-IN UNIT (LDR0、LDR1、LDR2)及实验装置左下方INPUT-UNIT(/SW-B)中的控制信号作对应连接。

具体信号连接:/SW-B、/R0-B、/R1-B、/R2-B,LDR0,LDR1,LDR2五、实验内容(一) 对战寄存器的写入拨动二进制开关(INPUT-UNIT)向R0和R1寄存器置数(置数灯亮表示它所对应的数据位为“1”、反之为“0”)。

具体操作步骤如下:(二)堆栈寄存器的读出关闭数据输入三态门(CBA=000),分别打开通用寄存器R0、R1、R2输出控制位,当CBA=100时,总线指示灯(BUS-DISP-UNIT)显示R0中的数据01H;当CBA=101时,总线指示灯显示R1中的数据80H;当CBA=110时,总线指示灯显示R2的数据(随机)。

电力安全月工作总结[电力安全月工作总结]电力安全月工作总结2011年3月1日至3月31日为我公司的安全生产月,**变电站围绕;夯实基储提高素质、树立标杆、争创一流;的主题,开展了丰富多彩、形式多样的具体行动:通过看板形式宣传安全第一、预防为主的方针;通过48+4的学习机会,进行安全生产大讨论;通过安全活动进行查找本站的隐患的活动,电力安全月工作总结。

实验十寄存器及寄存器堆设计报告

寄存器及寄存器堆设计

2018/10/11

15

pbdebounce p0(clk,btn_in[0],btn_out[0]); pbdebounce p1(clk,btn_in[1],btn_out[1]); pbdebounce p2(clk,btn_in[2],btn_out[2]); pbdebounce p3(clk,btn_in[3],btn_out[3]); pbdebounce p4(clk,btn_in[4],btn_out[4]); pbdebounce p5(clk,btn_in[5],btn_out[5]); pbdebounce p6(clk,btn_in[6],btn_out[6]); pbdebounce p7(clk,btn_in[7],btn_out[7]);

实验材料

无

寄存器及寄存器堆设计

2018/10/11

3

实现含由16个16位寄存器构成的寄存器堆,要求: 支持寄存器地址选择 支持写入任意16位值 支持读取寄存器的值

加入到多功能计算器中。

寄存器及寄存器堆设计

2018/10/11

4

寄存器是计算机常用的基本器件

1 、由同一信号控制的一组相互并联的触发器构成

2010-12-12 13

移位寄存器设计与应用

引脚分配(2)及操作说明

类 引脚 型 btn[0] btn[1] 输 btn[2] 入 btn[3] 取值 含义

btn[0]=1(主板按健) 为计数分频器的脉冲的计数控制开关

《CPU设计实验报告》word版

CPU设计实验报告姓名:学号:邮箱:一、实验目的:1、掌握硬件描述语言VHDL和EDA工具Quartus II;利用VHDL设计16位串行CPU,实现算术和逻辑运算指令、转移指令、访存指令、堆栈指令和控制指令;2、掌握CPU的调试和测试方法。

二、实验内容:1、运用硬件描述语言VHDL实现寄存器堆和算数逻辑单元设计、指令集和指令格式、时序设计和整体结构设计、指令译码器的设计、访存单元的设计、调试单元的设计;2、上机调试。

三、实验步骤:1、寄存器堆的设计寄存器堆由16个16位寄存器组成。

其中reset是异步清0端,reset=0时将所有寄存器清0。

dr_sel和sr_sel是目实用文档标寄存器和源寄存器编号,dr_out和sr_out输出目标寄存器和源寄存器的内容。

reg_sel指定一个寄存器编号,将该寄存器内容送给reg_out,这两个端口用于调试时观察每个寄存器的值。

reg_en是写允许端。

reg_en=“01”时,在clk的上升沿将from_alu写入dr_sel指定的寄存器;reg_en=“10”时,在clk的上升沿将from_mem写入dr_sel指定的寄存器。

reg_en取其他值时不改变寄存器堆的值。

设计方法:subtype WORD is std_logic_vector(15 downto 0);type REGISTERARRAY is array ( 0 to 15 ) of WORD;signal reg_bank: REGISTERARRAY 则reg_bank就是我们所需要的寄存器堆。

写寄存器堆的方法:reg_bank(conv_integer(dr_sel))<=from_alu;实用文档读寄存器堆的方法:dr_out <= reg_bank(conv_integer(dr_sel));其中,conv_integer是STD_LOGIC_ UNSINGED 程序包提供的函数,将标准逻辑矢量转换成整数,作为reg_bank 的下标。

堆栈寄存器实验实验报告(3篇)

第1篇一、实验目的1. 理解堆栈的概念和原理。

2. 掌握堆栈寄存器的组成和硬件电路。

3. 熟悉堆栈寄存器的数据写入与读出操作。

二、实验原理堆栈是一种先进后出(FILO)的数据结构,它由一组存储单元和相应的操作指令组成。

堆栈寄存器用于存储堆栈的指针,通常称为栈顶指针(Stack Pointer,SP)。

当数据被压入堆栈时,栈顶指针会自动增加;当数据从堆栈中弹出时,栈顶指针会自动减少。

实验中使用的堆栈寄存器由三片8位字长的LS374组成,分别命名为R0、R1、R2。

这三个寄存器的输入输出连接至BUS总线。

R0-B、R1-B、R2-B通过CBA二进制控制开关译码产生数据输出选通信号,LDR0、LDR1、LDR2数据写入允许信号,由二进制控制开关产生。

三、实验仪器与设备1. 实验台2. 8位字长的LS374芯片三片3. BUS总线4. CBA二进制控制开关5. LDR0、LDR1、LDR2数据写入允许信号6. 电源四、实验步骤1. 连接实验电路,将三片LS374芯片的输入输出端连接至BUS总线,CBA二进制控制开关连接至数据输出选通信号,LDR0、LDR1、LDR2数据写入允许信号连接至相应的控制信号。

2. 按照实验要求,将数据写入R0、R1、R2寄存器。

3. 读取R0、R1、R2寄存器中的数据,观察数据是否正确写入。

4. 对堆栈进行压栈操作,将数据压入堆栈。

5. 对堆栈进行弹栈操作,将数据从堆栈中弹出。

6. 观察栈顶指针的变化,验证堆栈操作的正确性。

五、实验结果与分析1. 实验步骤1:连接实验电路,按照要求连接LS374芯片、BUS总线、CBA二进制控制开关、LDR0、LDR1、LDR2数据写入允许信号等。

2. 实验步骤2:将数据写入R0、R1、R2寄存器。

通过观察BUS总线上的数据,发现数据已正确写入。

3. 实验步骤3:读取R0、R1、R2寄存器中的数据。

通过观察BUS总线上的数据,发现数据已正确读取。

寄存器的应用与实验

寄存器的应用与实验寄存器是计算机中一种重要的存储元件,用于临时存储和传输数据。

它在计算机系统中扮演着关键的角色,广泛应用于各种计算和数据处理任务中。

本文将探讨寄存器的应用领域以及相关的实验。

一、寄存器的概述寄存器是计算机中的一种高速存储器件,用于存储和传输二进制数据。

它由若干个触发器组成,每个触发器都能存储一个二进制位。

寄存器可以用于存储操作数、存储器地址、指令等。

在计算机运算和控制过程中,寄存器的作用不可忽视。

二、寄存器的应用1. 数据存储与传输计算机需要在运算过程中保存中间结果和操作数,这就需要使用寄存器进行数据的存储和传输。

寄存器的高速读写特性使其非常适合作为数据的临时存储单元。

2. 地址寄存器地址寄存器用于存储内存地址信息,它在访问内存时起到桥梁的作用。

将地址信息存储在寄存器中可以提高内存访问的效率,并简化地址的传输过程。

3. 累加器累加器是一种特殊的寄存器,用于存储和操作运算过程中的累加结果。

在算术逻辑运算中,累加器发挥着重要的作用,可以用于加法、减法、乘法和逻辑运算等。

4. 标志寄存器标志寄存器存储着一些标志位,用于记录运算过程中的状态信息。

例如,进位标志位用于记录加法是否产生进位,零标志位用于记录运算结果是否为零等。

5. 控制寄存器控制寄存器用于存储控制信号,用于控制计算机各个部件的工作状态。

例如,时钟控制寄存器用于控制计算机的时钟频率,中断控制寄存器用于控制中断信号的触发和处理等。

三、寄存器的实验为了更好地理解寄存器的应用和工作原理,我们可以进行一些简单的实验。

1. 数据存储与传输实验设定一个8位的寄存器,并将一组特定的二进制数值存储到寄存器中。

验证数据是否正确存储,并进行数据传输实验,将寄存器中的数据传输到其他寄存器或存储单元。

2. 累加器实验设计一个4位累加器,实现两个4位二进制数的相加运算。

验证累加器的结果是否正确,并进行进一步的逻辑运算实验,例如与运算、或运算等。

3. 控制寄存器实验选择一个具有控制寄存器的单元,例如定时器或状态机。

寄存器堆的设计

寄存器堆的设计————————————————————————————————作者: ————————————————————————————————日期:寄存器堆设计1、功能概述:MIPS指令格式中的寄存器号是5bits,指令可以访问25=32个32位的寄存器。

这样的一堆寄存器“堆在一起”构成一个寄存器堆(Register File)。

2、接口说明:寄存器堆模块接口信号说明表脉冲reg,复位端reg,写使能端reg,写地址reg,写数据reg,读地址一reg,读地址二reg,读数据一reg,读数据二reg;设计思路:1、复位处理是利用标志位flag实现的,当复位时,flag=0;利用i来计数,当i<31时,flag都等于0;直到i=32,复位完成,flag=1,这时,才可以进行写操作。

2、当复位时,需要32个脉冲才能将寄存器全部复位。

复位未完成,flag一直等于0。

若复位未完成时,进行写操作,这时,并不能写进去,便出错了。

所以,进行32分频,当寄存器可以写入时,复位已完成。

3、设计电路源代码//----32个32位寄存器堆moduleregfile(inputreg, //脉冲input reg, //复位端inputreg,//写使能端input[4:0] reg读地址一input[4:0]reg读地址二input[4:0] reg,//写地址input[31:0]reg,//写数据output[31:0] reg读数据一output [31:0] reg读数据二);//----------------------------------reg[31:0]regfiles[0:31]; //实现寄存功能reg [4:0]i;//实现flag的变换reg flag;//实现复位的标志regreg; //实现写数据的脉冲reg [4:0]count;//---32分频处理always@(posedgereg or posedge reg)beginif(reg)begincount<=5'd0;ﻩreg<=1'b0;ﻩendﻩelse if(count<5'd16)ﻩbeginﻩcount<=count+1'b1;endelseﻩbeginﻩcount<=5'd0;ﻩreg<=~reg;endend//---复位处理always@(posedge reg orposedge reg)beginif(reg)ﻩbegini<=5'd0;ﻩflag<=1'b0;ﻩendﻩelseif(i<5'b11111)beginﻩi<=i+1'b1;flag<=1'b0;endﻩelseflag<=1'b1;ﻩend//---写操作always@(posedgereg)beginif(~flag)ﻩregfiles[i]<=32'd0;elsebeginif(reg(reg'd0)) //写使能端为一,写地址不为零ﻩbeginﻩﻩregfiles[reg]<=reg;//写入ﻩﻩﻩendﻩﻩendend//---读操作assign reg(reg'd0)?32'd0:regfiles[reg];assign reg(reg'd0)?32'd0:regfiles[reg];////----------------------------------------endmodule4、设计电路仿真所设计的指令存储器模块电路,采用ISE仿真器工具进行了设计仿真验证,验证结果表明存储器功能以及接口时序完全正确,如下是仿真验证的波形图。

杭电计算机组成原理寄存器堆设计实验-4

杭州电子科技大学计算机学院实验报告课程名称:计算机组成原理实验项目:寄存器堆设计实验指导教师实验位置:姓班级:学号:日期:2015年5月7日(接上)实验内容(算法、程序、步骤和方法)3.管脚配置NET "Addr[0]" LOC = M8;NET "Addr[1]" LOC = N8;NET "Addr[2]" LOC = U8;NET "Addr[3]" LOC = V8;NET "Addr[4]" LOC = T5;NET "C1[0]" LOC = T10;NET "C1[1]" LOC = T9;NET "C2" LOC = B8;NET "Clk" LOC = C9;NET "LED[0]" LOC = U16;NET "LED[1]" LOC = V16;NET "LED[2]" LOC = U15;NET "LED[3]" LOC = V15;NET "LED[4]" LOC = M11;NET "LED[5]" LOC = N11;NET "LED[6]" LOC = R11;NET "LED[7]" LOC = T11;NET "Reset" LOC = D9;NET "Write_Reg" LOC = V9;数据记录和计算实验仿真波形:结论(结果)按照实验的要求,一步步的进行操作。

能够正确的进行Wire_Reg写操作,进行读操作时LED灯的显示,利用选择A,B操作读出信号,已经Reset进行清零信号的操作,都能顺利的进行,本实验多次失败,收获不小。

计算机组成原理寄存器存储器实验心得,寄存器实验心得(共10篇).docx

计算机组成原理寄存器存储器实验⼼得,寄存器实验⼼得(共10篇).docx寄存器实验⼼得(共10篇)通⽤寄存器实验报告 ⼀、实验⽬的: 1、了解通⽤寄存器组的⽤途及对CPU的重要性。

2、掌握通⽤寄存器组的设计⽅法。

⼆、实验内容: 1、通⽤寄存器组的作⽤ 通⽤寄存器组是CPU的重要组成部分。

从存储器和外部设备取来的数据要放在通⽤寄存器中;向存储器和外部设备输出的数据从通⽤寄存器中取出;参加算术运算和逻辑运算的数据从通⽤寄存器组中取出,同时通⽤寄存器也 是运算结果的暂存地。

通⽤寄存器组有两个读端⼝,负责提供进⾏算术逻辑单元需要的源操作数和⽬的操作数;有⼀个写端⼝,负责将运算结果保存到指定的寄存器内。

2、通⽤寄存器组功能实现 根据通⽤寄存器组的功能要求,⼀个只有四个16位寄存器的通⽤寄存器组的框图如下图所⽰: ⑴寄存器部分: 当reset为低电平时,将四个16位寄存器R0-R3复位为0;当寄存器的write和sel 为⾼电平时,在时钟信号clk的上升沿将D端的输⼊D[15-0]写⼊寄存器,然后送到寄存器的输出Q[15-0]。

4个寄存器的允许写信号write和外部产⽣的⽬的寄存器写信号DRWr直接相连。

每个寄存器还有另⼀个选择信号sel,它决定哪⼀个寄存器进⾏写操作。

4个寄存器的选择信号分别和2-4译码器产⽣的sel00、sel01、sel10、sel11相连。

只有当⼀个寄存器被选中,才允许对该寄存器进⾏写操作。

⑵2-4译码器: 2-4译码器的输⼊sel[1-0]接DR[1-0],2-4译码器对2位的输⼊信号sel[1-0]进⾏2-4译码,产⽣4个输出sel00、sel01、sel10、sel11,分别送往4个寄存器R0、R1、R2和R3的选择端sel。

⑶4选1多路器 4选1多路选择器1从4个寄存器R0、R1、R2和R3的输出Q[15-0]选择1路送到DR_data[15-0],给算术逻辑单元提供⽬的操作数;选择信号sel[1-0]接DR[1-0]。

计算机组成原理实验报告总结寄存器的原理及操作.doc

成绩:实验报告课程名称:计算机组成原理实验项目:寄存器的原理及操作姓名:专业:计算机科学与技术班级:学号:计算机科学与技术学院实验教学中心20 16年6月20日实验项目名称:寄存器的原理及操作一、实验目的1.了解模型机中 A, W 寄存器结构、工作原理及其控制方法。

2.了解模型机中寄存器组 R0..R3 结构、工作原理及其控制方法。

3.了解模型机中地址寄存器 MAR,堆栈寄存器 ST,输出寄存器 OUT寄存器结构、工作原理及其控制方法。

二、实验内容1、A、W寄存器:利用 COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开关做为控制信号,将数据写入寄存器A, W。

2、R0、R1、R2、R3 寄存器实验:利用COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开关做为控制信号,对数据寄存器组R0..R3 进行读写。

3、MAR、ST、OUT寄存器:利用COP2000实验仪上的K16..K23 开关做为DBUS的数据,其它开关做为控制信号,将数据写入地址寄存器MAR,堆栈寄存器ST,输出寄存器OUT。

三、实验用设备仪器及材料伟福 COP2000 系列计算机组成原理实验系统四、实验原理及接线实验 1:A,W 寄存器实验实验 2 :R0,R1, R2,R3寄存器实验MAR为存储器地址寄存器,其功能是存储操作数在内存中的地址,信号MAREN的功能是将数据总线DBUS上数据 MAR,信号 MAROE的功能是将MAR的值送到地址总线ABUS上ST 堆栈寄存器的作用,是出现中断或子程序调用时,保存断点处PC 的值,以便中断或子程序结束时,能继续执行原程序。

图中,信号STEN的作用是将数据总线DBUS上数据存入堆栈寄存器ST 中五、实验操作步骤实验 1:A,W 寄存器实验将 55H写入 A 寄存器二进制开关 K23-K16 用于 DBUS[7:0] 的数据输入,置数据55H按住 CLOCK脉冲键, CLOCK由高变低,这时寄存器 A 的黄色选择指示灯亮,表明选择 A 寄存器。

《计算机组成原理》实验报告——寄存器堆

南通大学信息科学技术学院《计算机组成实验》实验报告实验寄存器堆的设计与实现一、实验目的1.熟悉Vivado软件的使用方法。

2.熟悉寄存器堆的功能。

3.掌握自顶而下的硬件模块设计方法。

4.掌握电路仿真测试方法,掌握仿真激励文件的编写,掌握仿真输出的分析方法。

二、实验任务设计一个寄存器堆,满足两路输出一路输入的功能,并完成仿真测试。

三、实验预习(1)实验电路原理及信号说明寄存器堆(REGFILE)是CPU组成的重要存储部件,也是数据通路中的重要部件,其主要功能是对数据进行存储。

在本实验中将为REGFILE构建32×32的寄存器组,即共有32个寄存器,每个寄存器的位宽都是32位。

32×32的REGFILE逻辑结构如图所示:具体设计如下:通过带有32个带使能端的D触发器实现数据的存储,5-32译码器实现地址与存储单元的连接选择,32位32选1选择器来实现输出。

(2)实验电路设计顶层文件:module REGFILE(Ra,Rb,D,Wr,We,Clk,Clrn,Qa,Qb);input [4:0]Ra,Rb,Wr;input [31:0]D;input We,Clk,Clrn;output [31:0]Qa,Qb;wire [31:0]Y;wire[31:0]Q31,Q30,Q29,Q28,Q27,Q26,Q25,Q24,Q23,Q22,Q21,Q20,Q19,Q18,Q17,Q16,Q15,Q14,Q13,Q12,Q11,Q 10,Q9,Q8,Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0;DEC5T32E dec(Wr,We,Y);REG32reg32(D,Y,Clk,Clrn,Q31,Q30,Q29,Q28,Q27,Q26,Q25,Q24,Q23,Q22,Q21,Q20,Q19,Q18,Q17,Q16,Q15,Q14,Q 13,Q12,Q11,Q10,Q9,Q8,Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0);MUX32X32select1(Q31,Q30,Q29,Q28,Q27,Q26,Q25,Q24,Q23,Q22,Q21,Q20,Q19,Q18,Q17,Q16,Q15,Q14,Q13,Q12,Q11 ,Q10,Q9,Q8,Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0,Ra,Qa);MUX32X32select2(Q31,Q30,Q29,Q28,Q27,Q26,Q25,Q24,Q23,Q22,Q21,Q20,Q19,Q18,Q17,Q16,Q15,Q14,Q13,Q12,Q11 ,Q10,Q9,Q8,Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0,Rb,Qb);Endmodule5-32地址译码器:module DEC5T32E(I,En,Y);input [4:0] I;input En;output [31:0] Y;reg [31:0] Y;always@(En or I)beginif(En)begincase(I)5'b00000:Y=32'b00000000000000000000000000000001;5'b00001:Y=32'b00000000000000000000000000000010;5'b00010:Y=32'b00000000000000000000000000000100;5'b00011:Y=32'b00000000000000000000000000001000;5'b00100:Y=32'b00000000000000000000000000010000;5'b00101:Y=32'b00000000000000000000000000100000;5'b00110:Y=32'b00000000000000000000000001000000;5'b00111:Y=32'b00000000000000000000000010000000;5'b01000:Y=32'b00000000000000000000000100000000;5'b01001:Y=32'b00000000000000000000001000000000;5'b01010:Y=32'b00000000000000000000010000000000;5'b01011:Y=32'b00000000000000000000100000000000;5'b01100:Y=32'b00000000000000000001000000000000;5'b01101:Y=32'b00000000000000000010000000000000;5'b01110:Y=32'b00000000000000000100000000000000;5'b01111:Y=32'b00000000000000001000000000000000;5'b10000:Y=32'b00000000000000010000000000000000;5'b10001:Y=32'b00000000000000100000000000000000;5'b10010:Y=32'b00000000000001000000000000000000;5'b10011:Y=32'b00000000000010000000000000000000;5'b10100:Y=32'b00000000000100000000000000000000;5'b10101:Y=32'b00000000001000000000000000000000;5'b10110:Y=32'b00000000010000000000000000000000;5'b10111:Y=32'b00000000100000000000000000000000;5'b11000:Y=32'b00000001000000000000000000000000;5'b11001:Y=32'b00000010000000000000000000000000;5'b11010:Y=32'b00000100000000000000000000000000;5'b11011:Y=32'b00001000000000000000000000000000;5'b11100:Y=32'b00010000000000000000000000000000;5'b11101:Y=32'b00100000000000000000000000000000;5'b11110:Y=32'b01000000000000000000000000000000;5'b11111:Y=32'b10000000000000000000000000000000;endcaseendelseY=32'b00000000000000000000000000000000;endendmodule32位寄存器moduleREG32(D,En,Clk,Clrn,Q31,Q30,Q29,Q28,Q27,Q26,Q25,Q24,Q23,Q22,Q21,Q20,Q19,Q18,Q17,Q16,Q15,Q14,Q1 3,Q12,Q11,Q10,Q9,Q8,Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0);input[31:0]D,En;input Clk,Clrn;output[31:0]Q31,Q30,Q29,Q28,Q27,Q26,Q25,Q24,Q23,Q22,Q21,Q20,Q19,Q18,Q17,Q16,Q15,Q14,Q13,Q12,Q11 ,Q10,Q9,Q8,Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0;wire[31:0]Qn31,Qn30,Qn29,Qn28,Qn27,Qn26,Qn25,Qn24,Qn23,Qn22,Qn21,Qn20,Qn19,Qn18,Qn17,Qn16,Qn15,Qn 14,Qn13,Qn12,Qn11,Qn10,Qn9,Qn8,Qn7,Qn6,Qn5,Qn4,Qn3,Qn2,Qn1,Qn0;D_FFEC32 q31(D,Clk,En[31],Clrn,Q31,Qn31);D_FFEC32 q30(D,Clk,En[30],Clrn,Q30,Qn30);D_FFEC32 q29(D,Clk,En[29],Clrn,Q29,Qn29);D_FFEC32 q28(D,Clk,En[28],Clrn,Q28,Qn28);D_FFEC32 q27(D,Clk,En[27],Clrn,Q27,Qn27);D_FFEC32 q26(D,Clk,En[26],Clrn,Q26,Qn26);D_FFEC32 q25(D,Clk,En[25],Clrn,Q25,Qn25);D_FFEC32 q24(D,Clk,En[24],Clrn,Q24,Qn24);D_FFEC32 q23(D,Clk,En[23],Clrn,Q23,Qn23);D_FFEC32 q22(D,Clk,En[22],Clrn,Q22,Qn22);D_FFEC32 q21(D,Clk,En[21],Clrn,Q21,Qn21);D_FFEC32 q20(D,Clk,En[20],Clrn,Q20,Qn20);D_FFEC32 q19(D,Clk,En[19],Clrn,Q19,Qn19);D_FFEC32 q18(D,Clk,En[18],Clrn,Q18,Qn18);D_FFEC32 q17(D,Clk,En[17],Clrn,Q17,Qn17);D_FFEC32 q16(D,Clk,En[16],Clrn,Q16,Qn16);D_FFEC32 q15(D,Clk,En[15],Clrn,Q15,Qn15);D_FFEC32 q14(D,Clk,En[14],Clrn,Q14,Qn14);D_FFEC32 q13(D,Clk,En[13],Clrn,Q13,Qn13);D_FFEC32 q12(D,Clk,En[12],Clrn,Q12,Qn12);D_FFEC32 q11(D,Clk,En[11],Clrn,Q11,Qn11);D_FFEC32 q10(D,Clk,En[10],Clrn,Q10,Qn10);D_FFEC32 q9(D,Clk,En[9],Clrn,Q9,Qn9);D_FFEC32 q8(D,Clk,En[8],Clrn,Q8,Qn8);D_FFEC32 q7(D,Clk,En[7],Clrn,Q7,Qn7);D_FFEC32 q6(D,Clk,En[6],Clrn,Q6,Qn6);D_FFEC32 q5(D,Clk,En[5],Clrn,Q5,Qn5);D_FFEC32 q4(D,Clk,En[4],Clrn,Q4,Qn4);D_FFEC32 q3(D,Clk,En[3],Clrn,Q3,Qn3);D_FFEC32 q2(D,Clk,En[2],Clrn,Q2,Qn2);D_FFEC32 q1(D,Clk,En[1],Clrn,Q1,Qn1);assign Q0=0;assign Qn0=0;endmodule32位32选1选择器moduleMUX32X32(Q31,Q30,Q29,Q28,Q27,Q26,Q25,Q24,Q23,Q22,Q21,Q20,Q19,Q18,Q17,Q16,Q15,Q14,Q13,Q12,Q1 1,Q10,Q9,Q8,Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0,S,Y);input[31:0]Q31,Q30,Q29,Q28,Q27,Q26,Q25,Q24,Q23,Q22,Q21,Q20,Q19,Q18,Q17,Q16,Q15,Q14,Q13,Q12,Q11,Q10, Q9,Q8,Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0;input [4:0]S;output [31:0]Y;function [31:0]select;input[31:0]Q31,Q30,Q29,Q28,Q27,Q26,Q25,Q24,Q23,Q22,Q21,Q20,Q19,Q18,Q17,Q16,Q15,Q14,Q13,Q12,Q11,Q10, Q9,Q8,Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0;input [4:0]S;case(S)5'b00000:select=Q0;5'b00001:select=Q1;5'b00010:select=Q2;5'b00011:select=Q3;5'b00100:select=Q4;5'b00101:select=Q5;5'b00110:select=Q6;5'b00111:select=Q7;5'b01000:select=Q8;5'b01001:select=Q9;5'b01010:select=Q10;5'b01011:select=Q11;5'b01100:select=Q12;5'b01101:select=Q13;5'b01110:select=Q14;5'b01111:select=Q15;5'b10000:select=Q16;5'b10001:select=Q17;5'b10010:select=Q18;5'b10011:select=Q19;5'b10100:select=Q20;5'b10101:select=Q21;5'b10110:select=Q22;5'b10111:select=Q23;5'b11000:select=Q24;5'b11001:select=Q25;5'b11010:select=Q26;5'b11011:select=Q27;5'b11100:select=Q28;5'b11101:select=Q29;5'b11110:select=Q30;5'b11111:select=Q31;endcaseendfunctionassign Y =select(Q31,Q30,Q29,Q28,Q27,Q26,Q25,Q24,Q23,Q22,Q21,Q20,Q19,Q18,Q17,Q16,Q15,Q14,Q13,Q12,Q11,Q10, Q9,Q8,Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0,S);endmoduleRTL视图如下:四、实验过程、数据记录与结果分析1.仿真测试文件:module REGFILE_Sim( );// REGFILE Inputsreg [4:0] Ra = 0 ;reg [4:0] Rb = 0 ;reg [4:0] Wr = 0 ;reg [31:0] D = 0 ;reg We = 0 ;reg Clk = 0 ;reg Clrn = 0 ;// REGFILE Outputswire [31:0] Qa ;wire [31:0] Qb ;REGFILE u_REGFILE (.Ra ( Ra [4:0] ),.Rb ( Rb [4:0] ),.Wr ( Wr [4:0] ),.D ( D [31:0] ),.We ( We ),.Clk ( Clk ),.Clrn ( Clrn ),.Qa ( Qa [31:0] ),.Qb ( Qb [31:0] ));initialbeginClk=0;We=0; D=0; Ra=0; Rb=0; Wr=1; Clrn=0;#10;endalways #10 Clk=~Clk;always #20 Ra=Ra+1;always #20 Rb=Rb+1;always #20 Wr=Wr+1;always #20 D=D+1;always #20 We=~We;always #100 Clrn=1;endmodule2.仿真测试结果:3.仿真测试结果分析开始时100ns内,Clrn=0,寄存器堆初始化清零,此期间内写入操作均无效,读出数据均为零。

寄存器堆

操作过程及结果

一,操作过程

实验过程和描述:

module shiyan4(R_Addr_A,R_Addr_B,Clk,W_Addr,W_Data,R_Data_A,R_Data_B,Reset,Write_reg);

input Clk,Reset;

姓名:吴国庆学号:13055524同组姓名:学号:

实验位置(机号):自己的笔记本

实验日期:2015年4月27日指导教师:章复嘉

实验内容(算法、程序、步骤和方法)

1、实验目的

(1)学会使用Verilog HDL进行时序电路的设计方法。

(2)掌握灵活应用Verilog HDL进行各种描述与建模的技巧和方法。

assign R_Data_B=REG_Files[R_Addr_B];

(3)读操作没有使能或者时钟信号控制,是组合逻辑电路,只要给出寄存器地址,即可独处寄存器中的数据。

所有写入操作的输入信号(包括写寄存器地址W_Addr、写入数据W_Data、写控制信号Write_Reg)必须在时钟边沿来临时已经有效。

if(Reset)

begin

for(i=0;i<=31;i=i+1)

REG_Files[i]<=32'b0;

end

else

begin

if(Write_reg) begin

if(W_Addr>3’b000) REG_Files[W_Addr]<=W_Data; end

end

end

assign R_Data_A=REG_Files[R_Addr_A];

);

initial begin

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

pbdebounce p8(clk,btn_in[8],btn_out[8]);

pbdebounce p9(clk,btn_in[9],btn_out[9]); pbdebounce p10(clk,btn_in[10],btn_out[10]);//主扳上按健作为reg写入的CLK pbdebounce p11(clk,btn_in[11],btn_out[11]);//主扳上按健作为reg读出的CLK

D0

D1

D2

D3

D4

D5

D6

D7

寄存器及寄存器堆设计

2016/3/16

5

clear

Q R

Q0

Q S R Q

Q1

Q S R Q

Q2

Q S R Q

Q3

Q S R Q

Q4

Q S R Q

Q5

Q S R Q

Q6

Q S R Q

Q7

Q

S

Cp

Cp

Cp

Cp

Cp

Cp

C

D

D

D

clk

D0

D1

D2

D3

D4

D5

寄存器及寄存器堆设计

clear, Q );

clk); D[0], D[1], D[2], D[3], D[4], D[5], D[6], D[7],

cr, cr, cr, cr, cr, cr, cr, cr,

S, S, S, S, S, S, S, S,

Q[0], Q[1], Q[2], Q[3], Q[4], Q[5], Q[6], Q[7],

实验材料

无

寄存器及寄存器堆设计

2016/3/16

3

实现含由16个16位寄存器构成的寄存器堆,要求: 支持寄存器地址选择 支持写入任意16位值 支持读取寄存器的值

加入到多功能计算器中。

寄存器及寄存器堆设计

2016/3/16

4

寄存器是计算机常用的基本器件

1 、由同一信号控制的一组相互并联的触发器构成

Data out

Data in

寄存器及寄存器堆设计

m bits bus

D

Register n-1 Q

2016/3/16

8

module register_file(clk, cr, Address, Di, Do); // ... initial CE <= 0; assign SEL = Address; assign Y = ~Yi; assign CLK = {8{clk}} && Y; register_32 rr0(CLK[0], Di, cr, Do0 ); register_32 rr1(CLK[1], Di, cr, Do1 ); register_32 rr2(CLK[2], Di, cr, Do2 ); register_32 rr3(CLK[3], Di, cr, Do3 ); register_32 rr4(CLK[4], Di, cr, Do4 ); register_32 rr5(CLK[5], Di, cr, Do5 ); register_32 rr6(CLK[6], Di, cr, Do6 ); register_32 rr7(CLK[7], Di, cr, Do7 ); decode_3_8 d(Address[2], Address[1], Address[0], CE, Yi); MUX_8_1 mux(SEL, Do0, Do1, Do2, Do3, Do4, Do5, Do6, Do7, Do); endmodule

module register_32(cl, Di, cr, Dot); // ... BUFG cck(cck,cl); always @(posedge cl) Dot <= (!cr) ? 0 : Di; endmodule

寄存器及寄存器堆设计

2016/3/16

9

实现含由16个16位寄存器构成的寄存器堆,要求: 支持寄存器地址选择 支持写入任意16位值 支持读取任意寄存器的值

Qbar[0]), Qbar[1]), Qbar[2]), Qbar[3]), Qbar[4]), Qbar[5]), Qbar[6]), Qbar[7]);

2016/3/16 6

• 锁存器由多个一位锁存器/触发器并联构成

一般采用电平控制锁存:

高电平时置入数据

低电平时锁存数据,并指示数据稳定 带使能端的RS触发器实现的锁存器

• 寄存器组是多个寄存器组成的集合

寄存器写:寄存器地址→变量译码器

寄存器读:寄存器地址→数据选择器

write clk C 0 1 D C D Register 0 Q

address log2 n

变 量 译 码 器

n-2 n-1

Register 1

Q

C D C

Register n-2 Q

数 据 选 择 器

寄存器及寄存器堆设计

置入

锁存

Q[0], Q[1], Q[2], Q[3], Q[4], Q[5], Q[6], Q[7],

Qbar[0]), Qbar[1]), Qbar[2]), Qbar[3]), Qbar[4]), Qbar[5]), Qbar[6]), Qbar[7]);

2016/3/16 7

2016/3/16

16

display m0(clk, display_num,anode[3:0], segment[7:0]); //display module display32bits m1(clk,display_num32b,anode[11:4],segment[15:8]); calculate_result m2(switch,op1, op2, result); //calculate result counter_1s m3(clk, clk_1s); //1秒程序自己编写 couter_16reversible m4(clk_1s&btn_out[8],switch[4],cnt,Rc);

逻辑与计算机设计基础实验

10

2015~2016秋冬 浙江大学计算机学院实验教学中心

掌握寄存器、锁存器的工作原理及设计方法 掌握寄存器堆的工作原理及设计方法 了解计算机中寄存器及寄存器堆的概念

寄存器及寄存器堆设计

2016/3/16

2

实验设备

装有ISE的计算机系统 Spartan III 实验板 1台 1套

regfile m7(btn_out[10],btn_out[11],switch[13:10], op2, data_out); always @(posedge btn_out[0]) op1[ 3: 0] <= op1[ 3: 0] + 4'd1; always @(posedge btn_out[1]) op1[ 7: 4] <= op1[ 7: 4] + 4'd1; always @(posedge btn_out[2]) op1[ 11: 8] <= op1[ 11: 8] + 4'd1; always @(posedge btn_out[3]) op1[ 15: 12]<= op1[15: 12] + 4'd1;

2010-12-12 13

移位寄存器设计与应用

引脚分配(2)及操作说明

类 引脚 型 btn[0] btn[1] 输 btn[2] 入 btn[3] 取值 含义

btn[0]=1(主板按健) 为计数分频器的脉冲的计数控制开关

CLK上升沿

CLK上升沿

作为移位寄存器打入脉冲

作为16个寄存器的写入脉冲 作为16个寄存器的读出脉冲 修改操作数A(扩展板上) 修改操作数B(扩展板上) 运算结果显示16位数字在Spartan-3板上的 4个七段数码

增加到多功能计算器中。

寄存器及寄存器堆设计

2016/3/16

10

寄存器及寄存器堆设计

2016/3/16

11

引脚分配(1)及操作说明

类型 引脚 输入 sw[3:0] 取值 Sw[0]=1 Sw[1]=1 Sw[2]=1 Sw[3]=1 sw[4]=1 sw[5:4] sw[4]=0 sw[5]=0/1 SW[7:6]=00 SW[7:6]=01 SW[7:6] SW[7:6]=10 SW[7:6]=11 switch[7]=0 扩展板 switch[7]=1 switch[6]=0/1 扩展板 扩展板 switch[3:0] 含义 做加法操作 做减法操作 做与操作 做或操作 正向计数 反向计数 显示操作数A和B/显示时钟。 显示运算结果。 显示计数器结果 显示并行置数/串行移位结果。 显示寄存器内容。 控制串并 控制并行 作为串行输入数据0/1。 作为16个寄存器的地址选择。

1 、设置好要读出的操作数地址。通过 switch[3:0]来设置.

2 、按btn[2]产生一个CLK信号将操作数读出显示到主板上的数码管 。 注: switch[5]=0,显示操作数A和B 通过按健修改操作数B作为寄存器输入数据 switch[7:6]=11,显示寄存器读出的内容。

寄存器及寄存器堆设计

module //... assign assign assign RS_CE lock(lock, D, clear, Q); cr = {8{clear}} | (~D); Din = D & (~{8{clear}}); lock1 = lock | clear; R0(lock1, cr[0], Din[0], R1(lock1, cr[1], Din[1], R2(lock1, cr[2], Din[2], R3(lock1, cr[3], Din[3], R4(lock1, cr[4], Din[4], R5(lock1, cr[5], Din[5], R6(lock1, cr[6], Din[6], R7(lock1, cr[7], Din[7], endmodule