西工大2017年数字集成电路设计实验课实验一

西工大cmos实验报告一

模拟CMOS集成电路实验一一、PPT示例执行示例中的仿真程序,给出仿真结果。

并在NMOS的栅源电压为1.2V时,PMOS源栅电压等于1.2V时,分别仿真得出二者漏电流特性曲线。

这种情况下,手工计算出对于NMOS,当VDS=1V时漏电流、跨导的值;对于PMOS VSD=1V 时漏电流、跨导的值。

并与仿真结果比较。

沟道长度设置为1u,观察器件的漏电流有怎样的变化?A.示例MOS管IV 漏电流特性曲线1. Hspice仿真SP文件如下:.title MOS IV characters**************model NMOS************************.MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1+TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11+MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************.MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2+TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11+MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)**************************************************************netlist***************************M1 DN GN SN BN NMOS W=1u L=0.5uM2 DP GP SP BP PMOS W=1u L=0.5u**************source****************************VDSN DN SN 0VGSN GN SN 0VSN SN 0 0VBN BN 0 0VSDP SP DP 0VSGP SP GP 0VSP SP 0 3.3VBP BP 0 3.3**************analysis**************************.DC VDSN 0 3.3 0.05 sweep VGSN 0 3 0.5.DC VSDP 3.3 0 0.05 sweep VGSN 0 3 0.5.probe i(M1) i(M2) lx7(M1) lx7(M2) .end2.仿真图B. NMOS的栅源电压为1.2V,PMOS源栅电压等于1.2V, 漏电流特性曲线1. Hspice仿真SP文件.title MOS IV characters**************model NMOS************************.MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1+TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11+MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************.MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2+TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11+MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)**************************************************************netlist***************************M1 DN GN SN BN NMOS W=1u L=0.5uM2 DP GP SP BP PMOS W=1u L=0.5u**************source****************************VDSN DN SN 0VGSN GN SN 1.2VSN SN 0 0VBN BN 0 0VSDP SP DP 0VSGP SP GP 1.2VSP SP 0 3.3VBP BP 0 3.3**************analysis**************************.DC VDSN 0 3.3 0.05.DC VSDP 3.3 0 0.05.probe i(M1) i(M2).end2.仿真图3.手工计算与分析○1对于NMOS :7.0,350u 9.02,45.01.00=====TH n F V ,,φγλ当GS V =1.2V ,DS V =1V 时,NMOS 工作在饱和区,则有:21()(1)2'D n OX GS TH DS W I C V V V L μλ=-+ ()2mNMOS n OX GS TH n NMOS W W g C V V I L L μμ=-=其中:TH V =FSB F TH V V φφγ220-++ 代入参数可计算得:454.32.1710NMOS mNMOS I A g S μ-=⎧⎨=⨯⎩○2对于PMOS :8.0,8.02,4.0,100u 2.00-=====TH F p V φγλ, SG V =1.2V,SD V =1V 时,PMOS 工作在饱和区,则:()20.5(1)PMOS p OX GS TH DS W I C V V V L μλ=--+()2mPMOS p OX GS TH p PMOS W W g C V V I L L μμ=-=代入参数计算可得:511.55.7610PMOS mNMOS I A g Sμ-=-⎧⎨=⨯⎩C.沟道长度设置为1u, 漏电流特性曲线二、课本习题2.5a.图略1.手工计算与分析:λ=0.1,γ=0.45, 2F φ=0.9,0TH V =0.7V GS =3-x V ,V DS =3-x V ,V SB =x V ,TH V =F SB F TH V V φφγ220-++①当0)9.09.0(45.07.03>-+---=-X X TH G S V V V V 时,即X V <1.97时,M1工作在饱和区:DS TH GS ox n X V V V LW C I )1()(u 212λ+-=)1.13.3()9.09.045.03.2(u 212X X X ox n V V V LW C --+--= g m =D oxn I L W C u 2=x ox n I L W C u 2 ○2 x V >1.97时, M1管将处于截止状态;x I =0; m g =0。

数电第一次实验报告_西工大

数电实验1一.实验目的1.了解掌握QuartusⅡ中原理图的设计方法2.了解掌握ED0实验开发板的使用方法二.实验设备开发环境开发板三.实验内容要求1:根据参考内容,用原理图输入方法实现一位全加器。

1)用QuartusII波形仿真验证;2)下载到DE0 开发板验证。

要求2:参照参考内容,用74138 3-8 译码器和7400 与非门,用原理图输入方法实现一位全减器。

1)用QuartusII 波形仿真验证;2)下载到DE0 开发板验证。

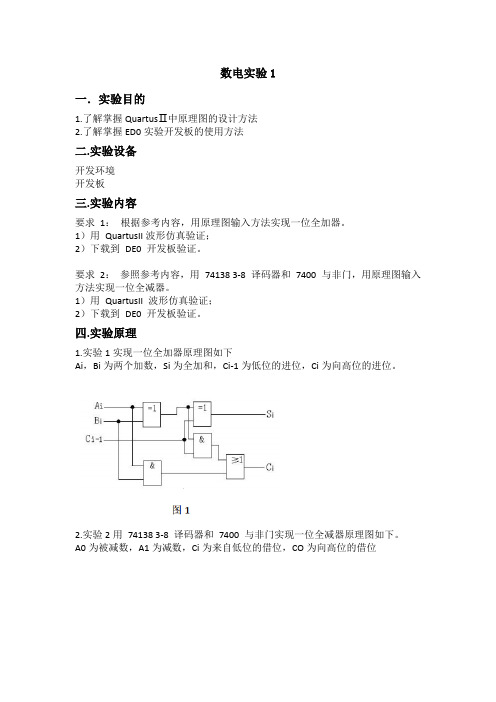

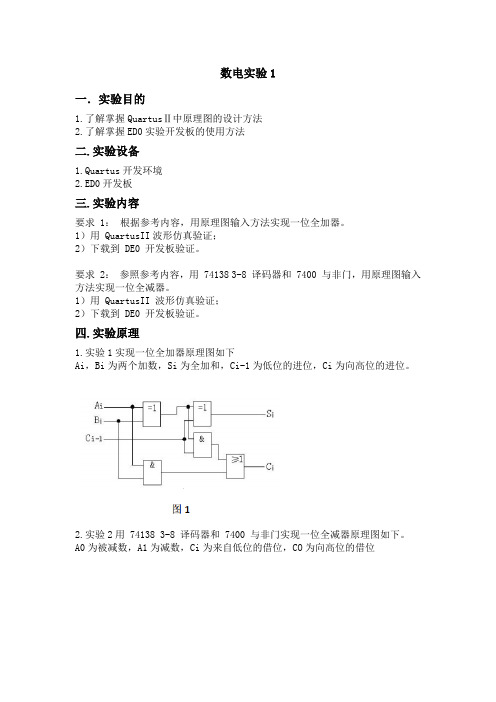

四.实验原理1.实验1实现一位全加器原理图如下Ai,Bi为两个加数,Si为全加和,Ci-1为低位的进位,Ci为向高位的进位。

2.实验2用74138 3-8 译码器和7400 与非门实现一位全减器原理图如下。

A0为被减数,A1为减数,Ci为来自低位的借位,CO为向高位的借位五.实验结果实验1:原理图输入波形仿真配置针脚在计算机上完成模拟实验之后,重新进行编译,然后将程序下载到DE0开发板上并对全加器进行验证。

验证结果无误。

实验2:原理图输入波形仿真六.故障排除&实验心得实验中,我们最大的问题就在于如何构建整个系统。

整个实验都是比较基本的一些语句和一些简单门电路的综合使用。

我们进一步的了解了整个系统的构建和编译过程,使我们对VHDL语句和Quartus的使用有了进一步的认识。

个人认为,VHDL语言不够简洁,有些表示比较麻烦。

这次实验首次让我们将数电理论运用到实践,增强了我们对于全加器和全减器的理解和运用,为我们将来的学习和工作提供了良好的基础。

西工大数字集成电路实验报告 数集实验2(1)

实验二、反相器(上)一、分析电路,解答下面的问题1.这个电路是不是反相器,为什么?该门属于有比逻辑,还是无比逻辑,为什么?是。

因为当Vin=1时,下拉网络导通,Vout=0;当Vin=0时,M1截止,Vout经RL充电至1,所以是反相器。

有比逻辑。

因为上拉网络始终导通,所以当下拉网络导通时存在竞争,所以是有比逻辑。

2.计算出这个电路的V OH V OL及V IH V IL。

(计算可先排除速度饱和的可能)V in=0时,V OH=2.5VV in=2.5时,假设NMOS 工作在临界饱和区:AI V R I vV V V A I V V L W K I D out L D T in out D T in D61142`1073.55.207.243.05.21039.7)(2/--⨯=⇒+=⎪⎩⎪⎨⎧=-=-=⨯=⇒-⨯=这样的话根据D D I I <1,器件实际工作在线性区⎪⎪⎪⎩⎪⎪⎪⎨⎧=+=--=v V V R I V V V V L W KI in OL L D OL OL T in D 5.25.2]2)[(2`6`10115-⨯=K 将, 5.0/5.1=L W,43.0=T V代入kohm R L 75=解得:=OL V 0.04633V由图得:V OH =2.5V, V OL =0.0356V. 当out in V V =时,NMOS 工作在饱和区⎪⎩⎪⎨⎧+=-⨯=outL D T in DV R I V V L W K I 5.2)(2/2`反相器阈值电压===out in M V V V 0.7932 此时-6.8978)43.0(875.255.2,)43.0(9375.125.22=--==--=in VinVoutin out V d d g V V ⎪⎪⎩⎪⎪⎨⎧=--==+=0.5458||0.9082||g V V V V g V V V M OH M IL M M IH由图得:V IH =0.881V, V IL =0.0378V. SP 文件:.TITLE 1.2UM CMOS INVERTER .options probe.options tnom=25.options ingold=2 limpts=30000 method=gear.options lvltim=2 imax=20 gmindc=1.0e-12.protect.lib'C:\synopsys\cmos25_level49.lib' TT.unprotect.global vddMn out in 0 0 NMOS W=1.5u L=0.5u *(工艺中要求尺寸最大0.5u)RL OUT V DD 75kVDD VDD 0 2.5VVIN IN 0 0.DC VIN 0 2.5V 0.1V.op.probe dc v(out).end3.分析电路噪声容限。

西北工业大学数电实验一

示波器的使用和TTL 逻辑电路设计一、 实验目的1. 加深了解TTL 逻辑门电路的结构和参数;2. 认识和掌握基本的TTL 逻辑门电路的连接方式;3. 熟悉数字型示波器的基本使用方法 二、 实验设备数字电路实验箱、数字双踪示波器、74LS20、电位器、电阻 三、 实验原理1. TTL 实现与运算AB AB F ==1该逻辑函数的逻辑电路如图a 所示:图a2. TTL 实现或运算B A B A B A F =+=+=2该逻辑函数的逻辑电路如图b 所示:(悬空)1F图b3. TTL 实现异或运算ABB AB A AB B AB A AB B AB A B A B A F 3=+=+=+=该逻辑函数的逻辑电路如图c 所示:图c四、 实验内容1. TTL 实现与运算2FAB3F A把输入信号A和B分别从引脚1和2输入,从3输出信号AB,再利用(2)中的方法,将引脚3输出的信号从引脚4输入,引脚5悬空(相当于输入高电平),从引脚6输出信号就实现了与门;2.TTL实现或运算先采用1中的方法实现A和B,分别从引脚1和4输入信号A和B,引脚2和5悬空(相当于输入高电平),引脚3和6就分别输出了信号A和B。

再将引脚3和6输出的信号分别输入到引脚9和10,由引脚8输出信号就实现了或门;3.TTL实现异或运算把输入信号A和B分别从引脚1和2输入,从3输出信号AB,再从引脚4和9分别输入信号A和B,由引脚3输出的信号AB分别从引脚5和10输入,这样引脚6和8分别输出信号A AB⋅,最后分别将⋅和B AB⊕;这两个信号从引脚12和13输入,则从引脚14输出的信号就是A B五、实验结果1.TTL实现与运算2.TTL实现或运算3.TTL实现异或运算六、故障排除1.确保74LS00和电路板接触良好,能够很好的传递电路信号;2.电路连接接口连接紧密,电位器能很好的实现电路的开闭。

七、心得体会加深了解TTL逻辑门电路的结构,认识和掌握基本的TTL逻辑门电路的连接方式,为今后的数字电路学习和实践打下坚实的基础。

西工大_数电实验_第二次实验_实验报告

数电实验2一.实验目的1.学习并掌握硬件描述语言(VHDL 或 Verilog HDL);熟悉门电路的逻辑功能,并用硬件描述语言实现门电路的设计。

2.熟悉中规模器件译码器的逻辑功能,用硬件描述语言实现其设计。

3.熟悉时序电路计数器的逻辑功能,用硬件描述语言实现其设计。

4.熟悉分频电路的逻辑功能,并用硬件描述语言实现其设计。

二.实验设备1.Quartus开发环境2.ED0开发板三.实验内容要求1:编写一个异或门逻辑电路,编译程序如下。

1)用 QuartusII 波形仿真验证;2)下载到DE0 开发板验证。

要求2:编写一个将二进制码转换成 0-F 的七段码译码器。

1)用 QuartusII 波形仿真验证;2)下载到 DE0 开发板,利用开发板上的数码管验证。

要求3:编写一个计数器。

1)用QuartusII 波形仿真验证;2)下载到 DE0 开发板验证。

要求4:编写一个能实现占空比 50%的 5M 和50M 分频器即两个输出,输出信号频率分别为 10Hz 和 1Hz。

1)下载到 DE0 开发板验证。

(提示:利用 DE0 板上已有的 50M 晶振作为输入信号,通过开发板上两个的 LED 灯观察输出信号)。

2)电路框图如下:扩展内容:利用已经实现的 VHDL 模块文件,采用原理图方法,实现 0-F 计数自动循环显示,频率 10Hz。

(提示:如何将 VHDL 模块文件在逻辑原理图中应用,参考参考内容 5)四.实验原理1.实验1实现异或门逻辑电路,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY EXORGATE ISPORT(A,B:IN STD_LOGIC;C:OUT STD_LOGIC);END EXORGATE;ARCHITECTURE fwm OF EXORGATE ISBEGINC<=A XOR B;END;2.实验2实现一个将二进制码转换成0-F的七段译码器,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sevendecoder ISPORT (data_in:IN STD_LOGIC_VECTOR(3 DOWNTO 0);dis_out:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END sevendecoder;ARCHITECTURE fwm OF sevendecoder ISBEGINPROCESS(data_in)BEGINCASE data_in ISWHEN"0000"=>dis_out<="1000000";--显示 0WHEN"0001"=>dis_out<="1111001";--显示 1WHEN"0010"=>dis_out<="0100100";--显示 2WHEN"0011"=>dis_out<="0110000";--显示 3WHEN"0100"=>dis_out<="0011001";--显示 4WHEN"0101"=>dis_out<="0010010";--显示 5WHEN"0110"=>dis_out<="0000010";--显示 6WHEN"0111"=>dis_out<="1111000";--显示 7WHEN"1000"=>dis_out<="0000000";--显示 8WHEN"1001"=>dis_out<="0010000";--显示 9WHEN"1010"=>dis_out<="0001000";--显示 AWHEN"1011"=>dis_out<="0000011";--显示 bWHEN"1100"=>dis_out<="1000110";--显示 CWHEN"1101"=>dis_out<="0100001";--显示 dWHEN"1110"=>dis_out<="0000110";--显示 EWHEN"1111"=>dis_out<="0001110";--显示 FWHEN OTHERS=> dis_out<="1111111";--灭灯,不显示END CASE;END PROCESS;END fwm;3.实验3完成一个计数器,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter ISPORT ( clk,RST : IN STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0); --四位计数COUT : OUT STD_LOGIC); --进位位END counter;ARCHITECTURE fwm OF counter ISSIGNAL Q1 : STD_LOGIC_VECTOR (3 DOWNTO 0);BEGINPROCESS(clk,RST)BEGINIF RST = '0' THEN Q1<=(OTHERS => '0'); COUT<= '0';ELSIF clk'EVENT AND clk='1' THENQ1<=Q1+1;COUT<= '0';IF Q1 >= "1001" THEN Q1<=(OTHERS => '0'); COUT<= '1';END IF;END IF;END PROCESS;DOUT<=Q1 ;END fwm;4.实验4编写一个能实现占空比 50%的 5M 和50M 分频器即两个输出,输出信号频率分别为 10Hz 和 1Hz,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY fpq ISPORT(clk:IN STD_LOGIC;clk_out,clk_out1:OUT STD_LOGIC);END fpq;ARCHITECTURE fwm OF fpq ISCONSTANT m : INTEGER:= 25000000; --50M 分频到 1Hz 时=25000000。

西工大模电实验报告记录

西工大模电实验报告记录————————————————————————————————作者:————————————————————————————————日期:模拟电子技术基础实验报告目录实验一单极共射放大电路实验二集成运算放大器的线性应用实验三多级负反馈放大电路实验四RC正弦波振荡器实验五方波发生器实验六有源滤波器综合设计实验用运算放大器组成万用表的设计实验一单极共射放大电路一、实验目的1、掌握用MultiSim仿真软件分析单级放大器主要性能指标的方法。

2、掌握晶体管放大器静态工作点的调试和调整方法,观察静态工作点对放大器输出波形的影响。

3、测量放大器的放大倍数、输入电阻和输出电阻。

4、掌握用MultiSim仿真软件分析单级放大器的频率特性的方法。

5、测量放大器的幅频特性。

二、实验原理及结果如图所示:1.静态工作点的调整和测量(1) 输入端加入1KHz 、幅度为50mV 的正弦波,如图所示。

当按照上述要求搭接好电路后,用示波器观察输出。

静态工作点具体调整步骤如下: 现象 出现截止失真 出现饱和失真 两种失真都出现 无失真 动作 减小W R增大W R减小输入信号加大输入信号根据示波器上观察到的现象,做出不同的调整动作,反复进行,使示波器所显示的输出波形达到最大不失真。

(2) 撤掉信号发生器,使输入信号电压0i V ,用万用表测量三极管的三个极分别对地的电压,,,,,E B C CEQ CQ V V V V I ,根据EQ EQ EV I R =算出CQ EQ I I =.将测量值记录于下表,并与估算值进行比较。

理论估算值实际测量值B VC VE VCE VC IB VC VE VCE VC I2.913v7.976v2.213v5.763v2.012mA2.881V8.069V2.173V5.912V1.964mA2.电压放大倍数的测量(1)输入信号为1kHz 、幅度为50mV 的正弦信号,输出端开路时,示波器分别测出i V ,o V 的大小,然后算出电压放大倍数。

数电第一次实验报告_西工大

数电实验1一.实验目的1.了解掌握QuartusⅡ中原理图的设计方法2.了解掌握ED0实验开发板的使用方法二.实验设备1.Quartus开发环境2.ED0开发板三.实验内容要求 1:根据参考内容,用原理图输入方法实现一位全加器。

1)用 QuartusII波形仿真验证;2)下载到 DE0 开发板验证。

要求 2:参照参考内容,用 74138 3-8 译码器和 7400 与非门,用原理图输入方法实现一位全减器。

1)用 QuartusII 波形仿真验证;2)下载到 DE0 开发板验证。

四.实验原理1.实验1实现一位全加器原理图如下Ai,Bi为两个加数,Si为全加和,Ci-1为低位的进位,Ci为向高位的进位。

2.实验2用 74138 3-8 译码器和 7400 与非门实现一位全减器原理图如下。

A0为被减数,A1为减数,Ci为来自低位的借位,CO为向高位的借位五.实验结果实验1:原理图输入波形仿真配置针脚在计算机上完成模拟实验之后,重新进行编译,然后将程序下载到DE0开发板上并对全加器进行验证。

验证结果无误。

实验2:原理图输入波形仿真六.故障排除&实验心得实验中,我们最大的问题就在于如何构建整个系统。

整个实验都是比较基本的一些语句和一些简单门电路的综合使用。

我们进一步的了解了整个系统的构建和编译过程,使我们对VHDL语句和Quartus的使用有了进一步的认识。

个人认为,VHDL语言不够简洁,有些表示比较麻烦。

这次实验首次让我们将数电理论运用到实践,增强了我们对于全加器和全减器的理解和运用,为我们将来的学习和工作提供了良好的基础。

数字集成电路课程实验报告

数字集成电路设计课程实验报告姓名:班级:学号:指导老师:实验时间:实验地点:实验一:设计一个反相器一、实验目的1、学习及掌握cadence 图形输入及仿真方法;2、掌握基本反相器的原理与设计方法;3、掌握反相器电压传输特性曲线VTC 的测试方法;4、分析电压传输特性曲线,确定五个关键电压OH V 、OL V 、IH V 、IL V 、TH V 。

二、实验内容本次实验主要是利用cadence 软件来设计一基本反相器(inverter),并利用仿真工具Analog Artist(Spectre)来测试反相器的电压传输特性曲线(VTC, Voltage transfer characteristic curves),并分析其五个关键电压:输出高电平OHV 、输出低电平OLV 、输入高电平IHV 、输入低电平ILV 、阈值电压THV 。

1、在cadence 环境中绘制的反相器原理图如图一所示。

值得注意的是应将NMOS 的衬底接地(GND ),而相应的应将PMOS 的衬底接电源(VDD ),这样不仅能消除体效应,而且还能够减弱闩锁效应(在NMOS 实现中并不存在)。

2、在Analog Environment 中,对反相器进行瞬态分析(tran),仿真时间设置为4ns 。

其输入输出波形如图二所示。

三、实验环境 软件:Cadence硬件:计算机四、实验结果由图可以看出:输出高电平5OH V V =、输出低电平0OL V V =、输入高电平 3.15IH V V =、输入低电平 2.24IL V V =、阈值电压 2.66TH V V =。

所以,噪声容限为:2.240 2.24L IL OL NM V V V =-=-= 53.15 1.85H OH IH NM V V V =-=-=实验二:设计一个水位控制器一、设计要求1、给出满足题目要求的电路图;2、根据设计目标,计算各MOS 管的尺寸;3、对电路进行仿真,仿真内容包括:直流输入范围、直流输出范围;4、对结果进行分析。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验四 译码器的设计及延迟估算

1、 设计译码器并估算延迟

设计一个用于16bit 寄存器堆的译码器,每一个寄存器有32bit 的宽度,每个bit 的寄存器单元形成的负载可以等效为3个单位化的晶体管(后面提到负载都为单位化后的负载)。

译码器的结构可参考典型的4-16译码器

译码器和寄存器堆的连接情况(Output 输出为1的一行寄存器被选中)

① 假定4个寄存器地址位的正反8个输入信号,每个信号的输入负载可以等效为10。

确定 译码器的级数,并计算相关逻辑努力,以此来确定每一级中晶体管的尺寸(相当于多少个单位化的晶体管)及整个译码电路的延迟(以单位反相器的延迟的本征延迟Tp0为单位)。

解: 96332,10int =⨯==ext g C C C ,9.696/10F ==⇒

假定每一级的逻辑努力:G=1,又因为分支努力(每个信号连接8个与非门):

81*8*1B ==, 路径努力8.7686.91=⨯⨯==GFB H 所以,使用最优锥形系数就可得到最佳的电路级数39.36.3ln 8.76ln 6.3ln ln ===H N ,故N 取3级。

因为逻辑努力:2121G =⨯⨯=,路径努力:6.15386.92=⨯⨯==GFB H 则使得路径延时最小的门努力 36.5)6.153(3/1===N H h 。

所以:

.

36.5136.5,68.2236.5,

36.5136.5132211=========g h f g h f g h f

故第一级晶体管尺寸为7.68

1036.5=⨯; 第二级尺寸为956.1768.27.6=⨯;

第三级尺寸为96244.9636.5956.17≈=⨯。

故延迟为:0008.22)36.5136.5436.51(p p p t t t =+++++=

② 如果在四个寄存器地址输入的时候,只有正信号,反信号必须从正信号来获得。

每个正信号的输入的等效负载为20,使用与①中同样的译码结构,在这种条件下确定晶体管的大小并评估延迟(以单位反相器的延迟的本征延迟Tp0为单位)。

解:因为输入时通过两级反相器,使这两个反相器分摊原来单个反相器的等效扇出,将两级反相器等效为一级,故其逻辑努力32.236.5h ==,

故36.5,68.2,32.2,32.24321====f f f f

所以:

第一级尺寸为:()9.2832.210=⨯;

第二级尺寸为:728.632.29.2=⨯;

第三级尺寸为:03.1868.2728.6=⨯;

第四级尺寸为:65.9636.503.18=⨯

正信号通路的延迟为:()0036.2236.5136.5436.5132.2132.2p p p t t t =++++++++= 反信号通路情况与上问相同,延迟为0008.22)36.5136.5436.51(p p p t t t =+++++=

2、 根据单位反相器(NMOS:W=0.5u L=0.5u PMOS:W=1.8u L=0.5u),设计出实

际电路,并仿真1题中第一问的路径延迟。

设计出实际电路如下:

仿真图如下:

代码如下

.title hubucmos

.options probe

.protect

.lib'D:\synopsys\Hspice_D-2010.03-SP1\lib\cmos25_level49.lib' TEST .vec'D:\Users\lenovo\Desktop\6\t1.vec'

.unprotect

.global VDD

Mng out g 0 0 NMOS w=1um l=0.5um

Mnf out f one 0 NMOS w=2um l=0.5um

Mna one a two 0 NMOS w=4um l=0.5um

Mnb two b 0 0 NMOS w=4um l=0.5um

Mnc one c three 0 NMOS w=6um l=0.5um

Mnd three d four 0 NMOS w=6um l=0.5um

Mne four e 0 0 NMOS w=6um l=0.5um

Mpg out g six vdd PMOS w=6um l=0.5um

Mpf six f vdd vdd PMOS w=6um l=0.5um

Mpa six a five vdd PMOS w=12um l=0.5um

Mpb six b five vdd PMOS w=12um l=0.5um

Mpc five c vdd vdd PMOS w=12um l=0.5um

Mpd five d vdd vdd PMOS w=12um l=0.5um

Mpe five e vdd vdd PMOS w=12um l=0.5um

CL out 0 10pf

vvdd vdd 0 2.5v

.tran 1n 2u start=0n

.measure tran tdelay1 trig v(g) val=1.25 td=0ns fall=1

+targ v(out) val=1.25 td=0ns rise=1

.measure tran tdelay2 trig v(g) val=1.25 td=0ns fall=2

+targ v(out) val=1.25 td=0ns rise=2

.measure tran tdelay3 trig v(g) val=1.25 td=0ns rise=2

+targ v(out) val=1.25 td=0ns fall=2

.measure tran tdelay4 trig v(g) val=1.25 td=0ns rise=3

+targ v(out) val=1.25 td=0ns fall=3

.print v(out) v(a) v(b) v(c) v(d) v(e) v(f) v(g)

.end

tt.vec:

radix 1111111

io iiiiiii

vname a b c d e f g

tunit us

trise 0.01

tfall 0.01

vih 2.5

vil 0.0

vol 0.25

voh 2.25

0 0000001

0.2 0000000

0.4 1111111

0.6 1011010

0.8 1111100

1 1111111

1.2 0000000

1.4 0000001。