杭电数电实验-数字电子技术第三版8章

数字电子技术基础简明教程(第三版)全

三、二进制代码 编码: 用二进制数表示文字、符号等信息的过程。 二进制代码: 编码后的二进制数。

二-十进制代码:用二进制代码表示十个数字符号 0 ~ 9,又称为 BCD 码(Binary Coded Decimal )。 8421码 2421码 5211码

几种常见的BCD代码: 余 3 码 余 3 循环码

Y2 1 0 1 0 11 0 0

& ≥1

Y3

(真值表略)

(4) 异或运算 A

=1

(Exclusive—OR) B

Y4 = A ⊕ B = AB + AB

(5) 同或运算 (异或非)

(Exclusive—NOR)

Y5 = A ⊕ B A =1 B

= AB + AB A=

= A⊙B B

Y4

A B Y4 00 0

10 1 11 1

(3)非运算:

真

A

Y

值

0

1

表

1

0

逻辑函数式 Y = A + B 逻辑符号

A B

≥1 Y 或门(OR gate)

逻辑函数式 逻辑符号

Y= A

A1

Y 非门(NOT gate)

二、逻辑变量与逻辑函数及常用复合逻辑运算

1. 逻辑变量与逻辑函数 逻辑变量:在逻辑代数中,用英文字母表示的变量称

¾ 1.3.1 几种表示逻辑函数的方法 ¾ 1.3.2 几种表示方法之间的转换

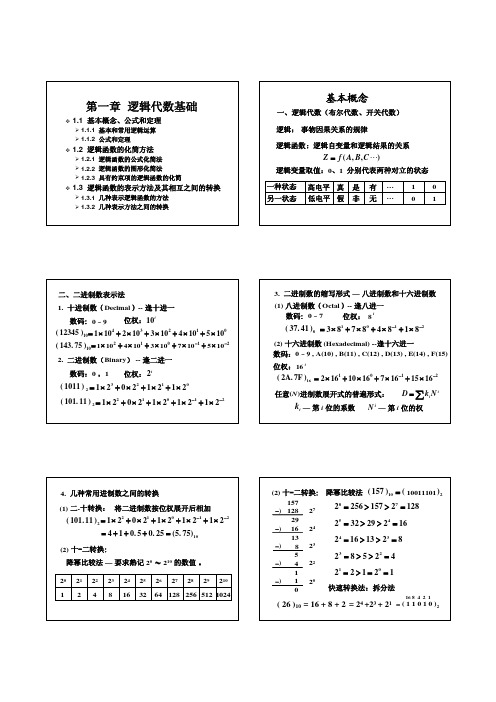

基本概念

一、逻辑代数(布尔代数、开关代数)

逻辑: 事物因果关系的规律

逻辑函数: 逻辑自变量和逻辑结果的关系 Z = f ( A, B, C L)

逻辑变量取值:0、1 分别代表两种对立的状态

数字电子技术基础(第三版 周良权)8

8.1.1 固定ROM

半导体存储器和可编程逻辑器件

地址输入线n根,又称 地址码。

相应的地址码的字线

每一根字线对应地存放一个 8位二进制数码,也就是这个字母的地 例如有 A9 ~ A0 10根地址线( n=10),通过地址译码器译 n 10 8位二进制数称为一个字。通常把一个字 址所指定存放的数,这个 字线 Wi的下标 i即对应的是地址码的十进制数。当该字线 出字线 根,为 W0 ~ W1023 若 A9 ~ A0 m 2 2 1024 中所含的位数称为字长。位数可以 1位、4位、8位、16位和32位等。 i出高电平1,其余字线为低电平 被选中, W 的地址选择为1100000000,则i=768,译出W768=1,其 把8位数的字称为一个字节。4位为半个字节,16位称为两个字节。 余字线为0 把输出位数的线称为位线。

半导体存储器和可编程逻辑器件 输出 当 CS 为0时,必须 PD / PGM 石英 也为0,数据才可输出。

玻璃 盖板

构成128 16 8位的存储单元矩阵

EPROM2716逻辑结构图

工作方式

读 出

EPROM2716引脚排列图

VDD

+5V +5V +5V 1 0 1 +25V +25V +25V

半导体存储器和可编程逻辑器件

8.2.1 RAM的电路结构和工作原理

一、六管静态存储单元电路

半导体存储器和可编程逻辑器件

T1 ~ T6

T1 ~ T6 MOS管组成 存储单元由 一列存储单元公用的门控 管T7、 T8由列选择线 Yj 控制。 T1 ~ T4 构成RS触发器双稳 态电路,存储1位二值信息0 T ~T 或1

5 6

数字电子技术章 (8)

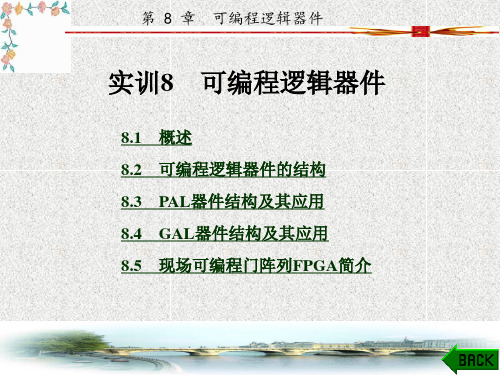

第 8 章 可编程逻辑器件

8.1 概

可编程逻辑器件(PLD)是一种标准化、 通用的数字电 路器件, 集门电路、 触发器、 多路选择开关、 三态门等 器件和电路连线于一身。 PLD使用起来灵活方便,可以根据 逻辑设计要求来设定输入与输出之间的关系, 也就是说, PLD是一种由用户配置某种逻辑功能的器件。

第 8 章 可编程逻辑器件 图 8.12 寄存器输出结构

第 8 章 可编程逻辑器件

4. 图8.13是异或输出结构的逻辑图。 这种结构是把与项之 和分成了两部分, 经异或运算后, 在CP的上升沿将异或结 果存入D触发器, 通过OE控制的三态门G6输出。 这样处理后, 它除了具有寄存器输出结构的特征外, 还能实现时序逻辑电 路的保持功能。

第 8 章 可编程逻辑器件

2. 异步I/O 图8.11是异步I/O输出结构的逻辑图。 该图的或门实现7 个与项的逻辑加, 并输出到三态门G3。 它受到与门G2输出 (第一个与项)的控制。 如果编程时使此与项常为0, 即该 与门的所有输入端都接通, 则三态门处于高阻态, 此时, I/O端可作为输入端, G4为输入缓冲器。

第 8 章 可编程逻辑器件

(4) 对GAL写入内容。 键入“2”, 将filename.JED文 件调入缓冲区。 此时, 可以通过观察缓冲区的内容来查看 待编程的GAL16V8的2048(32行×64列, 见图8.17)个可编 程单元的编程情况。 键入“P”, 开始按照缓冲区的内容对 GAL进行编程。

4. (1) GAL16V8的开发是通过编程器和相应的开发软件来 完成的。 (2) 本实训的软件是ABEL编译软件, 其作用是将在 DOS状态下编辑的ABEL源程序翻译为.JED文件, 该文件是编 程器对GAL进行硬件编程所需的数据。 这是实训步骤2)所进 行的工作。

数字电子技术第八章

VREF 取“负”则得 VO为“正”

《数字电子技术基础》第六版

实例:AD7520

《数字电子技术基础》第六版

8.2.6 具有双极性输出的DAC 当输入数字量有±极性时, 希望输出的模拟电压也对应为±。 一、原理 例:输入为3位二进制补码。最高位为符号位,正数为0, 负数为1 补码输入 对应的 要求的

输出电压: VO RF i RF ( I 3 I 2 I1 I 0 ) VREF VREF VREF VREF RF ( d3 d 2 2 d1 3 d 0 ) R 2R 2 R 2 R V 3 2 1 0 REF ( 2 d 2 d 2 d 2 d0 ) 3 2 1 4 2

8 2 1 0 ( d 2 d 2 d 2 ) 2 1 0 3 2 000 VO 0V 001 VO 1V 111 VO 7V 100 VO 4V

*将符号位反相后接至高位输入 *将输出偏移使输入为100时,输出为0

2.偏移 4V , 使输入 100 时, VO 0

111

7 =14/15(V) 6 =12/15(V) 5 =10/15(V) 4 = 8/15(V) 3 = 6/15(V) 2 = 4/15(V) 1 = 2/15(V) 0 = 0 (V)

13/15V 6 =6/8(V) 11/15V 5 =5/8(V) 9/15V 4 =4/8(V) 7/15V 3 =3/8(V) 5/15V 2 =2/8(V) 3/15V

001 010 011 100 101 110

《数字电子技术基础》第六版

8.5 抽样保持电路

!加大输入电阻 !减小输出电阻 !Av=1

《数字电子技术基础》第六版

《数字电子技术基础》第六版

精品课件-数字电子技术(第三版)(刘守义)-第1章

第1章 逻辑事件及其表示方法 图 1.4 与逻辑电路、 真值表和符号

第1章 逻辑事件及其表示方法

在逻辑电路中, 把能实现与运算的基本单元叫做与门, 其逻辑符号如图1.4(d)所示。

逻辑函数F与逻辑变量A、 B F=A·B

式中“·”为逻辑与运算符, 也可以省略。 表达式F=AB 称作逻辑变量A、 B的与非, 其真值表和逻

第1章 逻辑事件及其表示方法 图 1.3 非逻辑电路、 符号和真值表

第1章 逻辑事件及其表示方法 在逻辑电路中, 把能实现非运算的基本单元叫做非门, 其逻辑符号如图1.3(d)所示。 对逻辑变量A进行逻辑非运算的表达式为

其中, A读做A非或A反。 注意在这个表达式中, 变量(A、 F)的含义与普通代数有本质的区别: 无论输入量(A)还是 输出量(F)都只有两种取值0、 1, 没有第三种值。

1101B=1×23+1×22+0×21+1×20 可以看出, 二进制数1101B每一位的权值分别是: 23, 22, 21, 20。

第1章 逻辑事件及其表示方法

2. 十六进制数(Hex) 十六进制数是人们研究和学习二进制数的一种工具, 它 是随着计算机的发展而广泛应用的。 十六进制的基数为16, 它有0~9, A, B, C, D, E, F十六个数码, 计数规则 是“逢十六进一”, “借一当十六”, 它的位权是由基数 16的幂决定的。

3245O=3×83+2×82+4×81+5×80 同样, 八进制数3245O每一位的权值分别是: 83, 82, 81, 89

第1章 逻辑事件及其表示方法

1.1.3 常用数制间的相互转换 逻辑电路和计算机中普遍采用二进制数操作, 但人们

习惯使用十进制, 这样往往会遇到不同数制之间的转换。 图1.2表示了十进制、 二进制和十六进制数之间的转换方法。

数字电子技术基础课后习题答案第8章习题答案

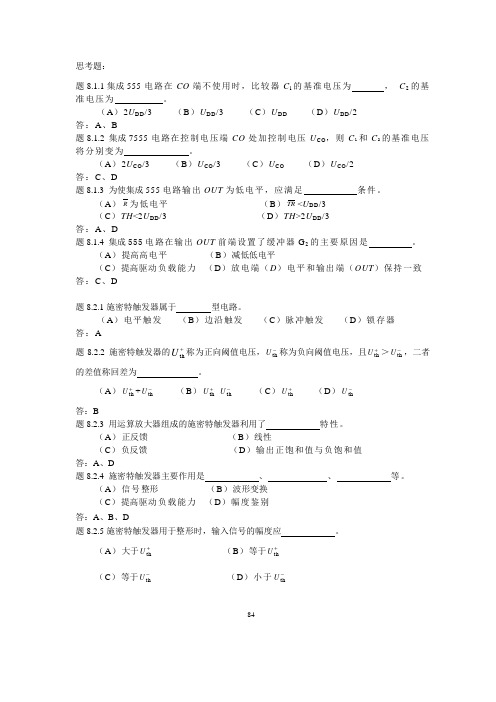

84题8.1.1集成555电路在CO 端不使用时,比较器C l 的基准电压为 , C 2的基准电压为 。

(A )2U DD /3 (B )U DD /3 (C )U DD (D )U DD /2 答:A 、B题8.1.2 集成7555电路在控制电压端CO 处加控制电压U CO ,则C 1和C 2的基准电压将分别变为 。

(A )2U CO /3 (B )U CO /3 (C )U CO (D )U CO /2 答:C 、D题8.1.3 为使集成555电路输出OUT 为低电平,应满足 条件。

(A )R 为低电平 (B )TR <U DD /3 (C )TH <2U DD /3 (D )TH >2U DD /3 答:A 、D题8.1.4 集成555电路在输出OUT 前端设置了缓冲器G 2的主要原因是 。

(A )提高高电平 (B )减低低电平(C )提高驱动负载能力 (D )放电端(D )电平和输出端(OUT )保持一致 答:C 、D题8.2.1施密特触发器属于 型电路。

(A )电平触发 (B )边沿触发 (C )脉冲触发 (D )锁存器 答:A题8.2.2 施密特触发器的+th U 称为正向阈值电压,-th U 称为负向阈值电压,且+th U >-th U ,二者的差值称回差为 。

(A )+th U +-th U (B )+th U --th U (C )+th U (D )-th U答:B题8.2.3 用运算放大器组成的施密特触发器利用了 特性。

(A )正反馈 (B )线性(C )负反馈 (D )输出正饱和值与负饱和值 答:A 、D题8.2.4 施密特触发器主要作用是 、 、 等。

(A )信号整形 (B )波形变换 (C )提高驱动负载能力 (D )幅度鉴别 答:A 、B 、D题8.2.5施密特触发器用于整形时,输入信号的幅度应 。

(A )大于+th U (B )等于+th U (C )等于-th U(D )小于-th U题8.2.6 可将变化缓慢的输入信号变换为矩形脉冲信号。

杭电数电实验-数字电子技术第三版6章

题目一:原理图:仿真结果:说明:P1开始前无初始值,所以在输入为000,001,010时,RS触发器输入为00,其保持原状(不定态),直到输入011开始,RS触发器输入为01,开始有确定输出。

毛刺:说明:在输入为001到010的时候Y[0]出现毛刺,电平拉低再迅速抬高,因为74138输入从001到010的时候74138是逐个变化,它先从001变到000,再从000变到010,所以变化到000的时候Y[0]会拉低,而造成毛刺。

题目二:原理图:仿真结果:说明:Y[0]高说明B大,Y[1]高一样大,Y[2]高A大。

毛刺:说明:7485反应慢,当B由1000000变为00100110时先变成00000000,这时比A的值小,Y[0]拉低,Y[2]变高,之后又恢复原状题目三:原理图:半加器原件:实验原理图:仿真结果:说明:C为进位位,Cj为地位进位来的数据。

S为A+B+Cj和。

毛刺:说明:在处理时,A先处理,从00000001变到00000010,而B处理处理慢于A,导致A+B+Cj为4,此时S[2]输出高电平S[1]输出低电平,随后处理B后,恢复原状题目四:原理图:仿真结果:说明:红色框表示第一位数码管可以显示内容,显示内容由Data决定,数码管导通由S决定,如7448显示译码器输入为0000显示‘0’数字,138输入000让第一位数码管导通时,则此时第一位数码管输出a~g为0111111。

而第其余位数码管显示高阻。

同理,绿色框为第二位导通时的情况毛刺:说明:在控制线S由001变成010的时候,Q1出现毛刺,因为74138在接受到输入信号由001变成010的时候,内部先从001变成000再变成010,在变成000的时候,第一位数码管输出信号,先输出原先存储的数据0111111然后变化成相应电平。

题目五:原理图:数码管元件:实验原理图:仿真结果:毛刺:说明:在输入0011变成0100的时候,输出出现毛刺,因为在0011变成0100的时候,不是一蹴而就,一位一位变成0100所以导致输出信号变化。

精品课件-数字电子技术-第8章

第8章 脉冲单元电路

图8-3 施密特触发器电路

第8章 脉冲单元电路

8.2.1 施密特触发器有两个稳态(Uo=0称为0态和Uo=1称为1

态) ,在外加信号的作用下,施密特触发器两个稳态之间可 以相互转换。施密特触发器属于波形变换电路,它可以将正弦

(1) 当输入触发信号达到一定值时,输出电平发生 变化,即由一个稳态转换到另一稳态,因而称其为电平触发电

第8章 脉冲单元电路

图8-8 施密特触发器用作光控开关

第8章 脉冲单元电路

8.3 多 谐 振 荡 器

8.3.1 1. TTL与非门构成的多谐振荡器 1) 图8-9所示为电容正反馈多谐振荡器,它由两级与非门和

电容C

第8章 脉冲单元电路

图8-9 多谐振荡器

第8章 脉冲单元电路

2) 多谐振荡器的工作,主要依靠电容C的充放电,通过引起 电压Ud的变化来完成其功能。当Ub为低电平,Ua为高电平时, 称为第一暂态;当Ub为高电平,Ua为低电平时,称为第二暂态。 设起始为第一暂态,这时Ua通过门电路的内阻R0和电阻R1对电 容C充电,工作波形如图8-9所示。随着电容C的充电, 电压Ud 不断上升。 当Ud上升到Ud>VT=1.4 V时(其中VT为门限电压) ,Ud为 高电平,电路发生翻转。Ua由原来的高电平变为低电平,Ub由

(3) 555定时器构成的施密特触发器用作光控开关。 图8-8所示电路为555定时器构成的施密特触发器用作光 控开关的电路图。图中的RL为光敏电阻,有光照时电阻值小, 无光照时阻值大。有光照时,电路设计(选取合适的可变电阻 值) 使得Ui<1/3VCC,输出Uo为高电平,继电器J不动作; 无光 照时,光敏电阻大,电路设计使得Ui>2/3VCC,输出Uo为低电平, 继电器J吸合,

精品课件-数字电子技术(第三版)(刘守义)-第9章

第 9 章 A/D、D/A转换

9.2 D/A 9.2.1 D/A转换的基本原理

图9.11为数模转换的示意图。 D/A转换器将输入的二进 制数字量转换成相应的模拟电压,经运算放大器A的缓冲, 输出模拟电压uO。

第 9 章 A/D、D/A转换 图 9.11 数模转换的示意图

第 9 章 A/D、D/A转换

第 9 章 A/D、D/A转换

4. 1) 查集成电路手册, 了解74LS161、 DAC0832和741的功能, 确定74LS161、 DAC0832的管脚排列, 了解各管脚的功能。

2) 按图9.1在实验板上安装好实验电路, 检查电路连接, 确认无误后再接电源。 注意不要将引脚接错。

第 9 章 A/D、D/A转换

图中, D0~Dn-1为输入的n位二进制数字量(其十进制最大 值为2n-1), D0为最低位(LSB), Dn-1为最高位(MSB), uO为输出模拟量, UREF为实现转换所需的参考电压(又称基 准电压)。 三者应满足下列关系式:

第 9 章 A/D、D/A转换 其中, X=Dn-12n-1+Dn-22n-2+…+D121+D020为二进制数字量所代 表的十进制数。 所以,

第 9 章 A/D、D/A转换 图 9.2 实训9输出波形

第 9 章 A/D、D/A转换

9.1 A/D转换的基本原理和类型 图9.3所示为一个典型的数字控制系统框图。 可以看出, A/D转换(模拟/数字转换)和D/A转换(数字/模拟转换)是 现代数字化设备中不可缺少的部分, 它是数字 电路和模拟电路的中间接口电路。

第 9 章 A/D、D/A转换

4) DAC0832 DAC0832是实现D/A转换的器件。 用示波器测量运放741 的输出信号, 记录输出波形的形状、 频率和幅度。 如果电 路工作正常, 其输出应为一个锯齿波。 改变输入脉冲CP的频率, 观察输出波形的频率变化; 改变数模转换器DAC0832第8脚UREF的大小, 观察输出波形的 幅值变化情况。

数字电子技术实验指导书(答案)课件

输入

输出

引脚1 L L H H

引脚2 L H L H

引脚3 L H H L

表1.3 74LS86真值表

PPT学习交流

6

二 、 TTL、HC和HCT器件的电压传输特性

(一)、实验目的

•

1.掌握TTL、HCT和 HC器件的传输特性。

•

2.掌握万用表的使用方法。

(二)、实验所用器件

•

1.六反相器74LS04片

(二)简单逻辑电路设计 根据题目要求,利用EDA工具MAX-PlusII

的原理图输入法,输入设计的电路图;建立 相应仿真波形文件,并进行波形仿真,记录 波形和输入与输出的时延差;分析设计电路 的正确性。

PPT学习交流

17

1. 设计一个2-4译码器

2-4译码器功能表如下

输入

输出

E

A1 A2 Q0

Q1

图表示一条主干公路 (东一面)与一条二级道路 的交叉点。车辆探测器沿着 A、B、C和D线放置。当没有 发现车辆时,这些敏感组件 的输出为低电平‘0”。当发 现有车辆时,输出为高电平 “1”。交叉口通行灯根据下 列逻辑关系控制:

PPT学习交流

22

交叉口通行灯逻辑问题的实现

(a)东一西灯任何时候都是绿的条件 (1)C和D线均被占用; (2)没有发现车辆; (3)当A、B线没同的占用时,C或D任一条线被占用;

从实验台上的时钟脉冲输出端口选择两个 不同频率(约 7khz和 14khz)的脉冲信号分别加 到X0和X1端。对应 B和 S 端数字信号的所有 可能组合,观察并画出输出端的波形,并由此得出 S和B(及/B)的功能。

选通选择线

SB B

X0 数据输入

数据输出

数电第三版课后答案(共19页)

数电第三版课后答案[模版仅供参考,切勿通篇使用]篇一:数电答案蔡良伟(完整版)数字电路答案第一章习题1-1(1)221*8010=2*8+6=268268=2?6?=101102010110101102=0?0010?110=1616 16(2) 10821010=1*8+5*8+4*8=15481548=1?5??4=11011002 00110110011011002=0?1101?100=6C16 6C(3)*80-110=1*8+5+1*8==1?5?.1?= 001101001=1??010= D2(4)-110=2*8+0*8+3*8+5*8==2?0?3?.5?= 010*********=1?0000??010= 83A1-2(1)1011012=1?011?01=558 551011012=0?0101?101=2D16 2D555*81+5*808==4510(2)111001012=0?111?001? 01=3458 345111001012=1?1100?101=E516 E534528=3*8+4*81+5*80=22910(3)=1??011?00= 514=0??011= 53-184=5*+81*+8-42=*851 0.1875(4)=1?001?? 01= 474=0?0100??010= 27A?4*81?7*80?5*8?1? 1-3(1)161+6*808=1*8=1410168=1?6?=1110200111011120=?11=10E16E(2)1722108=1*8+7*8+2*8=12210 1728=1?7??2=11110102 001111010 11110102?0111?1010??7A167A(3)-1-28=6*8+1*8+5*8+3*8= =6?1?.5?3?= 110001101011=0?0110??0101?100= 31AC(4)-1-28=1*8+2*8+6*8+7*8+4*8= =1?2?6?.7??4 = 001010110111100=0?1010??111= 56F1-4 (1)2A16=2??A=1010102 001010101010102=1?010?10=528 52521+2*808=5*8=4210(2)B2F16=B?2?F?=1011001011112 1011001011111011001011112=1?011?001? 011?11=54578 54575457=5*83+4*82+5*81+7*80 8=286310(3)=D?3?.E?= 110100111110=0?110?100??11= 3237-18=3*8+2*8+3*8+7*8= (4)=1?C?3?.F?9?= 00011100001111111001=1?110?000??111?100?10= 73762*81+3*80+7*8-1+6*8-2+2*8-38=7*8+=(1)A(B?C)?AB?AC左式=右式,得证。

电子科大-数电-数字逻辑设计第八章(3)

并行 数据

16

顺序脉冲发生器

CLK

Q0 Q1 Q2 Q3

利用移位寄存器构成

—— 注意自校正(环形计数器 P530)

利用计数器和译码器构成

—— 注意“毛刺”(二进制计数器的状态译码 P513)

17

序列信号发生器

—— 用于产生一组特定的串行数字信号

例:设计一个

利用触发器 利用计数器 利用移位寄存器

POj

串行比较器(P547)、串行加法器(P548)

24

同步设计中的其他问题

8.7 同步系统结构和设计方法

同步系统 分解 模块结构

data unit 数据单元 + 控制单元 control unit 寄存器、计数器、存储器 产生控制信号(状态机)

8.8 同步设计中的障碍

竞争和冒险可以不考虑(P548) 时钟偏移(P553) 选通时钟:设计合理的时钟使能端(P557) 异步输入:利用好的同步器协调异步输入

成电路(MSI)时序功能器件作为设计的基本元素完成更

为复杂的时序逻辑电路设计的方法。 学习了解钟控同步状态机电路的设计的其他问题: 组合电路与时序电路的比较,大型时序电路的结构划分, 时钟歪斜,异步输入等。

35

第8章 作业

8.13、

8.15、 8.18 8.29、 8.32 、 8. 36 、 8. 39 8. 45 、8. 59 、 8. 61、 8. 64

110100 序列信号发生器

18

利用D触发器设计一个110100序列信号发生器

1、画状态转换图

S0 /0 S5 /1 S1 S4 /1 S2 /0 S3

3、列状态转换输出表

数字电子技术(第三版)(章图文 (5)

第五章 触 发 器

图 5 – 1 时序电路框图

第五章 触 发 器

时序电路就是通过记忆元件的不同状态,来记忆以

前的状态。设时间t时刻记忆元件的状态输出

为 Q1n (t), Q2n (t), Qln (t) , 称为时序电路的现态。那么,

在该时刻的输入

x及n (现t) 态

Q的ln (共t) 同作用下,组合

图 5 – 4 例 1、例 2 (a) 米里型; (b) 莫尔型

第五章 触 发 器

表5–5 真 值 表

Qn x1 x2

Q n+1

F

000

0

1

001

0

0

010

1

0

011

1

1

100

1

1

101

0

0

1101011101

第五章 触 发 器

解 表 5-5 是某时序逻辑电路的真值表, 其左边是 时序电路的现态和输入信号, 均作为时序电路的输入来 处理, 中间和右边表示该电路的次态和输出。 作出对应

第五章 触 发 器

表 5 – 9 钟控RS触发器真值表

R S Qn

000 001 010 011 100 101 110 111

Q n+1

0 1

1 1

0 0 × ×

说明

保持 Q n+1=Qn

置1 Q n+1=1

置0 Q n+1=0

禁止

第五章 触 发 器

2. 状态表、状态图及特征方程

Q n 1

S

_

表 5 – 10 D触发器真值表

D

Qn

0

0

0

1

1

数字电子技术基础简明教程第三版课件

01

添加章节标题

02

课件概述

课件简介

ቤተ መጻሕፍቲ ባይዱ

课件名称:数字 电子技术基础简 明教程第三版

课件目标:帮助 学生掌握数字电 子技术基础知识, 提高分析和解决 问题的能力

课件内容:包括 数字电路基础、 逻辑门电路、组 合逻辑电路、时 序逻辑电路等章 节

课件特点:采用 图文并茂的方式, 结合实例和案例 分析,使抽象的 理论更加生动形 象,便于学生理 解和掌握

验证功能:通过仿真或实验验证电路的功能是否正确

数字电路的故障诊断与排除

添加项标题

数字电路故障诊断方法:通过观察、测试和分析等手段,确定数 字电路中存在的问题和故障点。

添加项标题

数字电路故障排除方法:根据诊断结果,采取相应的措施排除故 障,恢复数字电路的正常工作。

添加项标题

数字电路故障诊断与排除的注意事项:在操作过程中要注意安全, 避免对电路和设备造成二次损坏。

计算机领域的应用

数字电路设计

计算机接口技术

添加标题

添加标题

计算机组成结构

添加标题

添加标题

计算机控制技术

控制领域的应用

数字电子技术在 控制领域的应用 背景

数字电子技术在 控制领域的应用 范围

数字电子技术在 控制领域的应用 案例

数字电子技术在 控制领域的未来 发展趋势

汽车电子领域的应用

发动机控制系统:通过数字电子技术实现发动机的精确控制,提高燃油经 济性和排放性能。

03

知识

数字信号与模拟信号的区别

定义:数字信号是离散的,模拟信号是连续的。

幅度取值:数字信号的幅度取值通常只有两种 可能,即0或1。而模拟信号的幅度可以取任意 值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

14072119 王健

题目一:用74161构建十二进制加法计数器。

用反馈清零法和反馈置数法原理图:

上面为反馈置数法,下面为反馈清零法。

仿真结果:

说明:上面为反馈置数法波形,下面方框为反馈清零法波形

如图,其反馈置数法从4计数到15,反馈清零法从0置数到11,都实现了十二进制

毛刺:

分析:在反馈清零法出现毛刺,且在DOUT由1变为0时,Q[2]出现一次翻转。

因为反馈清零法在清零时有一个瞬间态,从1011计数变成1100时,瞬间从1100跳到0000。

这是由电路构造决定的

题目二:用74160构建35位进制十位加法器

原理图:

仿真结果:

如图,其在计数到34时DOUT为高,之后回低电平,Q变为0,完成了35进制

题目三:设计一般模型的十进制加法计数器

原理图:

CNT10原件:

DFF4原件

实验原理图:

仿真结果:

如图,其在计数到1001时DOUT为高,之后回低电平,Q变为0,完成了10进制。