3-8线译码器的74HC138芯片课程设计

用译码器设计组合逻辑电路例题分析

用译码器设计组合逻辑电路例题一、用3线-8线译码器74HC138和门电路实现逻辑函数ABC BC A C B A Y ++=/////。

(要求写出过程,画出连接图) (本题10分)解:(1)74HC138的输出表达式为: (2分))7~0(//==i m Y i i(2)将要求的逻辑函数写成最小项表达式:(2分)//7/1/0720/////)(m m m m m m ABC BC A C B A Y =++=++=(3)将逻辑函数与74HC138的输出表达式进行比较:设A= A 2、B= A 1、C= A 0,得://7/2/0//7/1/0)()(Y Y Y m m m Y == (2分)(4)可用一片74HC138再加一个与非门就可实现函数。

其逻辑图如下图所示。

(4分)三、公司A、B、C三个股东,分别占有50%、30%和20%的股份,试用一片3线-8线译码器74HC138和若干门电路设计一个三输入三输出的多数表决器,用于开会时按股份大小记分输出通过、平局和否决三种表决结果。

通过、平局和否决,分别用X、Y、Z表示(股东赞成和输出结果均用1表示)。

(12分)解:ABC XYZ000 001001 001010 001011 010100 010101 100110 100111 100//7/6/5765//)(m m m m m m ABC ABC C AB X =++=++= //4/343///)(m m m m ABC C AB BC A Y =+=++=//2/1/0210///////)(m m m m m m BC A C B A C B A Z =++=++=(3)画连线图(4分)令74HC138的地址码210,,A A A B A C ===四、某学校学生参加三门课程A 、B 、C 的考试,根据课程学时不同,三门课程考试及格分别可得2、4、5分,不及格均为0分,若总得分大于等于7分,便可结业。

用与非门组成的3线-8线译码器课程设计

哈尔滨理工大学软件学院课程设计报告课程数字IC设计(双语)题目 3线-8线译码器班级集成12—1专业集成电路设计与集成系统学生张铭学号 1214020130 指导教师陆学斌2014年12月31日目录1、课程设计目的介绍………………………………………………2、课程设计题目介绍………………………………………………3、课程设计报告内容………………………………………………4、体会总结…………………………………………………………5、参考书目…………………………………………………………1.课程设计目的训练学生综合运用学过的数字集成电路的基本知识,独立设计相对复杂的数字集成电路的能力。

2.课程设计题目用与非门组成的3线-8线译码器3.课程设计报告内容3.1 设计要求按题目要求的逻辑功能进行设计,电路各个组成部分须有设计说明;必须采用网表输入法;3.2 设计内容拿到题目后首先进行电路设计。

然后在微机上进行HSPICE网表输入、编译和软件仿真,满足设计要求。

3.3 查找有关书籍设计电路原理图3.4 根据原理图编写网表*74 HC138.include 'd:\lib\180nm_bulk.l'.param Supply=1.8.global Vdd Gnd.opt scale=0.1uVdd Vdd Gnd 'Supply'.subckt nand ina inb inc ind outmpa out ina Vdd Vdd PMOS l=2 w=8 ad=8 pd=8 as=40 ps=40 mpb out inb Vdd Vdd PMOS l=2 w=8 ad=8 pd=8 as=40 ps=40 mpc out inc Vdd Vdd PMOS l=2 w=8 ad=8 pd=8 as=40 ps=40 mpd out ind Vdd Vdd PMOS l=2 w=8 ad=8 pd=8 as=40 ps=40 mna out ina x Gnd NMOS l=2 w=16 ad=16 pd=16 as=80 ps=80 mnb x inb y Gnd NMOS l=2 w=16 ad=16 pd=16 as=80 ps=80 mnc y inc z Gnd NMOS l=2 w=16 ad=16 pd=16 as=80 ps=80 mnd z ind Gnd Gnd NMOS l=2 w=16 ad=16 pd=16 as=80 ps=80 .ends.subckt nor ina inb inc outmpa out ina x Vdd PMOS l=2 w=12 ad=12 pd=12 as=60 ps=60 mpb x inb y Vdd PMOS l=2 w=12 ad=12 pd=12 as=60 ps=60 mpc y inc Vdd Vdd PMOS l=2 w=12 ad=12 pd=12 as=60 ps=60 mna out ina Gnd Gnd NMOS l=2 w=2 ad=2 pd=2 as=10 ps=10 mnb out inb Gnd Gnd NMOS l=2 w=2 ad=2 pd=2 as=10 ps=10 mnc out inc Gnd Gnd NMOS l=2 w=2 ad=2 pd=2 as=10 ps=10 .ends.subckt Inverter in outmpa out in Vdd Vdd PMOS l=2 w=4 ad=4 pd=4 as=20 ps=20 mpb out in Gnd Gnd NMOS l=2 w=2 ad=4 pd=4 as=10 ps=10 .endsx1 s1 s1b Inverterx2 s1b s2b s3b s norx3 a0 a0b Inverterx4 a1 a1b Inverterx5 a2 a2b Inverterx6 a0b a0bb Inverterx7 a1b a1bb Inverterx8 a2b a2bb Inverterx9 a0b a1b a2b s y0b nandx10 a0bb a1b a2b s y1b nandx11 a0b a1bb a2b s y2b nandx12 a0bb a1bb a2b s y3b nandx13 a0b a1b a2bb s y4b nandx14 a1b a2bb a0bb s y5b nandx15 a0b a2bb a1bb s y6b nandx16 a1bb a0bb a2bb s y7b nandCinv y1b Gnd 6000fVs1 s1 Gnd pulse 0 'Supply' 7.5ns 200ps 200ps 130ns 140ns Vs2b s2b Gnd pulse 'Supply' 0 0ns 200ps 200ps 100ns 110ns Vs3b s3b Gnd pulse 'Supply' 0 0ns 200ps 200ps 65ns 75ns Va0 a0 Gnd pulse 0 'Supply' 0ns 200ps 200ps 17.5ns 35ns Va1 a1 Gnd pulse 0 'Supply' 0ns 200ps 200ps 40ns 80ns Va2 a2 Gnd pulse 0 'Supply' 0ns 200ps 200ps 70ns 140ns .tran 100ps 140ns.plot tran V(s1).end3.5画图编写3线—8线译码器的功能表说明:s1 s2b s3b 为附加的控制端,当s1 = 1,s2b + s3b = 0时,译码器处于工作状态,否则译码器被禁止,所有的输出端被封锁在高电平。

3 8译码器

试验一组合逻辑3线-8线译码器设计试验一、试验目的1、了解并初步掌握ModelSim软件的使用;2、了解使用ModelSim进行组合数字电路设计的一般步骤;3、掌握组合逻辑电路的设计方法;4、掌握组合逻辑电路3线-8线译码器的原理;5、掌握门级建模的方法;二、试验原理译码器(Decoder)的逻辑功能是将每个输入的二进制代码译成对应得输出高、低电平或另外一个代码。

因此,译码是编码的反操作。

常用的译码器电路有二进制译码器、二-十进制译码器和显示译码器等。

二进制译码器的输入是一组二进制代码,输出是一组与输入代码一一对应得高、低电平信号。

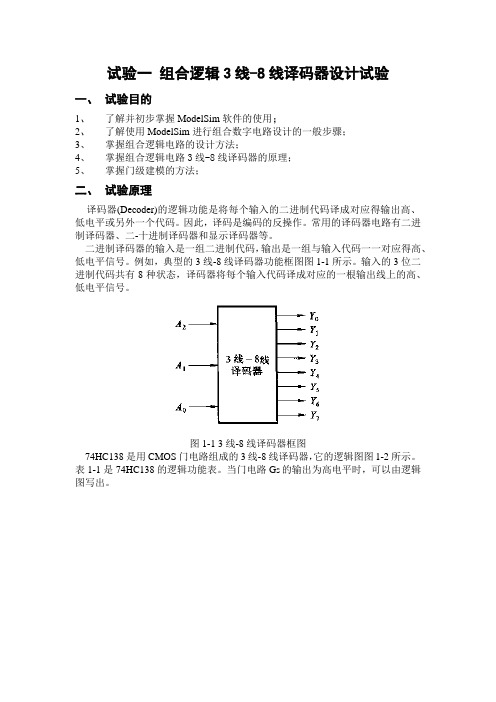

例如,典型的3线-8线译码器功能框图图1-1所示。

输入的3位二进制代码共有8种状态,译码器将每个输入代码译成对应的一根输出线上的高、低电平信号。

图1-1 3线-8线译码器框图74HC138是用CMOS门电路组成的3线-8线译码器,它的逻辑图图1-2所示。

表1-1是74HC138的逻辑功能表。

当门电路G S的输出为高电平时,可以由逻辑图写出。

图1-2 74HC138逻辑功能图表1-1 74HC138逻辑功能表由上式可以看出,由''07Y Y -同时又是210,,A A A 这三个变量的全部最小项的译码输出,所以也将这种译码器称为最小项译码器。

74HC138有3个附加的控制端''123,S S S 和。

当''123S 1,S S 0=+=时,s G 输出为高电平,译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁为高电平。

这3个控制端也称为“片选”输入端,利用片选的作用可以将多片连接起来以扩展译码器的功能;三、 预习要求1、数字电子技术基础组合逻辑电路设计一般设计方法;2、74HC138的逻辑功能;3、门级建模的一般方法和基本语句;4、ModelSim 软件的一般使用方法(ModelSim SE Tutorial);四、 实验步骤(一)、熟悉ModelSim 软件环境 1、建立一个新Project1-1双击左面快捷方式或者电击[程序]/[ModelSim SE 6.1f]/[ModelSim]启动ModelSim 6.1(如图1-3);注意:必须首先关闭IMPORTANT Information 对话框才能开始其它操作;图1-31-2 [File]/[New]/[Project…]新建一个project,会弹出Create Project对话框(如图1-4);图1-4⏹Project Name(项目名称)需要填入你所建立的项目的名称;⏹指定项目所在路径;如果所指定的目录不存在,会弹出对话框提示是否建立这个目录;一般选择是;⏹缺省的工作库名;注意:1、路径一般不应包含汉字;2、逻辑应在ModelSim的安装目录下指定;3、缺省的工作库的名称一般不需要改动;2、载入HDL元文件2-1设定好1-2步骤的每项内容后,点击OK,弹出Add items to the Projects对话框;如图1-5所示。

范文4.3常用组合逻辑电路(3线—8线译码器138)

最新.

19

【例2】设计一个用3个开关控制灯的逻辑电路, 要求任一个开关都能控制灯的由亮到灭或由灭 到亮。要求用74HC138和必要的门电路实现。

最新.

20

A

B

C

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

Ym 1m 2m 4m 7

Y

0 1 m1 1 m2 0 1 m4

全减器,设A为被减数,B为减数,CI为来自低位的 借位,D为差,CO为向高位的借位。

00

11

11

01

10 00

00

11

最新.

23

用译码器设计组合逻辑电路

பைடு நூலகம்

步骤:

1、首先将逻辑函数表示成最小项和的形式。

2、将逻辑函数表示成3-8译码器的输出 信号的形式。

3、画出电路图,注意译码器的片选端的 连接。

最新.

用中规模集成电路设计逻辑电路,可 以减少连线、提高可靠性。

任何一个逻辑函数都可以表示成最小 项和的形式,而3-8译码器的输出对应于 不同的最小项,因此,可用3-8译码器方 便的实现任意3三变量逻辑函数。

最新.

16

例1:利用74HC138设计一个多输出的组合逻辑电 路,输出逻辑函数式为:

Z1 AC ' A'BC AB'C Z2 BC A'B'C Z3 A'B AB'C Z4 A'BC ' B'C ' ABC

组合逻辑3-8译码器

G1

G2A

G2B

C

B

A

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

X

1

X

X

X

X

1

1

1

1

1

1

1

1

X

X

1

X

X

X

1

1

1

1

1

1

1

1

0

X

X

X

X

X

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

0

1

1

1

1

1

1

1

0

0

0

1

0

1

1

0

1

1

1

1

1

1

0

0

0

1

1

1

1

1

0

1

1

1

1

1

0

0

1

0

0

1

1

1

0

1

1

1

1

0

0

1

when "110"=>y<=”10111111";

when "111”=>y<="01111111” ;

when others=>y<="XXXXXXXX”;

实验一74HC138 译码器实验

实验一 74HC138 译码器实验一、实验目的与要求:1、掌握74HC138 译码器的工作原理,熟悉74HC138 译码器的具体运用连接方法,了解74HC138 是如何译码的。

2、认真预习本节实验内容,尝试自行编写程序,填写实验报告二、实验设备:STAR 系列实验仪一套、PC 机一台三、实验内容:1、编写程序:使用82C55 的PC0、PC1、PC2 控制74HC138 的数据输入端,通过译码产生8选1 个选通信号,轮流点亮8 个LED 指示灯。

2、运行程序,验证译码的正确性。

四、实验步骤:1、连线说明:C3 区:A、B、C —— B4 区:PC0、PC1、PC2C3 区:G1、G2A、G2B —— C1 区:VCC、GND、GNDC3 区:JP35 —— G6 区:JP65(LED 指示灯)B4 区:CS、A0、A1 —— A3 区:CS1、A0、A12、调试程序,查看运行结果是否正确。

.MODEL TINYCon_8255 EQU 0F003H ;8255控制口PC_8255 EQU 0F002H ;8255 PC口.STACK 100.CODESTART: MOV DX,Con_8255MOV AL,80HOUT DX,AL ;8255初始化,PC口作输出用MOV DX,PC_8255MOV AL,0START1: OUT DX,ALCALL DelayINC ALJMP START1Delay PROC NEAR ;延时Delay1: XOR CX,CXLOOP $RETDelay ENDPEND START五、实习总结:通过今天一上午的实习,总算有了成果,在STAR ES598PC实验仪上,根据实习指导书上的要求,把该连的线都连上。

之后又打开程序以及实验仪的开关,运行程序,实验仪上的8个指示灯就会按照顺序依次闪亮。

刚开始要实习的时候心里特别的紧张,因为自己感觉这门课学的不好。

不过幸好刚开始的实习都有现成的代码,我们需要做的就是对已有的代码测试一下,并观察实验仪上的LED灯是否会正确显示,然后就是读代码,分析代码,并从中学习别人的编程思路。

数电课程设计_五人表决器设计

数电部分五人表决器设计一、设计任务与要求1•设计一个五人表决器,通过红绿两种不同颜色的灯来代表表决是否通过,并用数码管显示出同意的人数。

2•使用74HC138译码器芯片进行控制,按照少数服从多数的原则,多数人同意则通过,少数人同意则被否决。

用绿灯亮表通过,红灯亮表示否决。

3•学会根据已学知识设计具有某一特定功能的电路,学会基本电路的组装与调试。

二、方案设计与论证当按下开关时,代表同意赞成,开关没有按下去时,表示不赞成。

评委按照自己的意愿投票,选择是否按下开关,即选择逻辑电位。

对逻辑电位进行译码,对译码后芯片的输出进行显示。

对于五人表决器,首先设五人分别为ABC D E,设丫为表决的结果。

其中有三人或三人以上同意(同意用“ 1”表示,不同意用“ 0”表示)则绿灯亮(绿灯用“ 1”表示),红灯亮(红灯用“ 0”表示)。

五人表决器真值表如果绿灯亮了,则表示表决通过,若红灯亮了,表示不通过。

三、单元电路设计与参数计算芯片74HC138是典型的集成译码器。

它是3线-8线译码器,该译码器有3位二进制输入A B C,它们共有8种状态的组合,即可译出八个输出信号,输出为低电平有效此外,还设置了3个使能端G1G2A G2B为电路的扩展提供了方便。

74HC138集成译码器功能表输入输出G G>A 非G B非C B AY0非Y i非Y2非Y3非Y4非丫 5非Y,非丫7非* H * * * * H H H H H H H H * * H * * * H H H H H H H H L * * * * * H H H H H H H H H L L L L L L H H H H H H H H L L L L H H L H H H H H H H L L L H L H H L H H H H H H L L L H H H H H L H H H H H L L H L L H H H H L H H H H L L H L H H H H H H L H H H L L H H L H H H H H H L H H L L H H H H H H H H H H L15141312^97 0 12 3 4 5 6 7 YYYYYYYY 7 ABC G7—74HC138外围引脚分布图芯片74HC139是双2线-4线译码器,它的输出也是低电平有效,符号匡内部的输 入、输出变量表示其内部的逻辑关系。

实验六 3线8线译码器及其应用

实验六 3线8线译码器及其应用一、实验目的1、掌握中规模集成电路译码器的工作原理及逻辑功2、学习译码器的灵活应用。

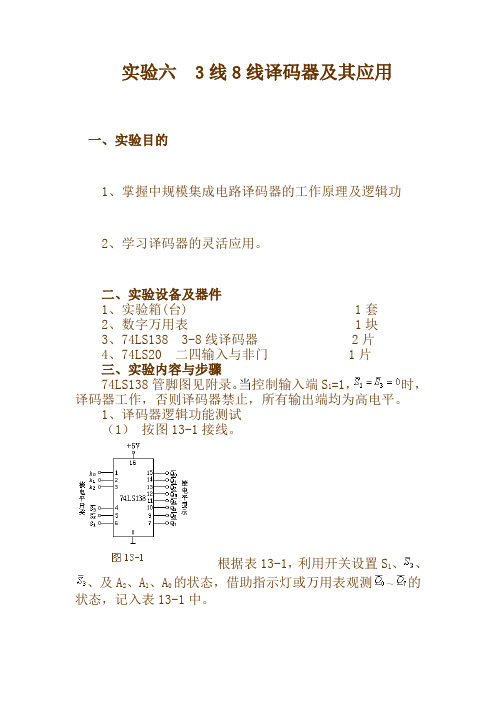

二、实验设备及器件1、实验箱(台) 1套2、数字万用表 1块3、74LS138 3-8线译码器 2片4、74LS20 二四输入与非门 1片三、实验内容与步骤74LS138管脚图见附录。

当控制输入端S1=1,时,译码器工作,否则译码器禁止,所有输出端均为高电平。

1、译码器逻辑功能测试(1)按图13-1接线。

根据表13-1,利用开关设置S1、、、及A2、A1、A0的状态,借助指示灯或万用表观测~的状态,记入表13-1中。

2、用两片74LS138组成4-16线译码器按图13-2接线,利用开关改变输入D0-D3的状态,借助指示灯或万用表监测输出端,记入表13-2中,写出各输出端的逻辑函数。

图13-2表13-2 输入输出D 3D2D1D0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 13、利用译码器组成全加器线路用74LS138和74LS20按图13-3接线,74LS20芯片14脚接 +5v,7脚接地。

利用开关改变输入A i、B i、C i-1的状态,借助指示灯或万用表观测输出S i、C i的状态,记入表13-3中,写出输出端的逻辑表达式。

图13-3表13-3 输入输出S 1AiBiCi-1SiCi0ΦΦΦ10001001101010111100110111101111四、实验要求:1、整理各步实验结果,列出相应实测真值表。

2、总结译码器的逻辑功能及灵活应用情况。

3、交出完整的实验报告。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计课程名称集成电路课程设计题目名称 74HC138芯片3-8线译码器学生学院材料与能源学院专业班级学号学生姓名指导教师2015年7 月 11 日目录【摘要】...........................................................................................................................................................1. 设计目的与任务....................................................................................................................................- 1 -2. 设计要求及内容....................................................................................................................................- 1 -3. 设计方法及分析....................................................................................................................................- 2 -3.1 74HC138芯片简介 ......................................................................................................................- 2 -3.2 工艺和规则及模型文件的选择 .................................................................................................- 3 -3.3 电路设计......................................................................................................................................- 4 -3.3.1 输出级电路设计.............................................................................................................- 4 -3.3.2.内部基本反相器中的各MOS 尺寸的计算................................................................- 6 -3.3.3.四输入与非门MOS尺寸的计算.................................................................................- 7 -3.3.4.三输入与非门MOS尺寸的计算.................................................................................- 8 -3.3.5.输入级设计...................................................................................................................- 9 -3.3.6.缓冲级设计.................................................................................................................- 10 -3.3.7.输入保护电路设计................................................................................................... - 11 -3.4. 功耗与延迟估算.......................................................................................................................- 13 -3.4.1. 模型简化........................................................................................................................- 13 -3.4.2. 功耗估算........................................................................................................................- 14 -3.4.3. 延迟估算........................................................................................................................- 14 -3.5. 电路模拟...................................................................................................................................- 15 -3.5.1 直流分析.........................................................................................................................- 16 -3.5.2 瞬态分析.......................................................................................................................- 18 -3.5.3 功耗分析.......................................................................................................................- 20 -3.6. 版图设计...................................................................................................................................- 21 -3.6.1 输入级的设计...............................................................................................................- 21 -3.6.2 内部反相器的设计.......................................................................................................- 22 -3.6.3 输入和输出缓冲门的设计 ...........................................................................................- 22 -3.6.4 三输入与非门的设计...................................................................................................- 23 -3.6.5 四输入与非门的设计...................................................................................................- 24 -3.6.6 输出级的设计...............................................................................................................- 24 -3.6.7 调用含有保护电路的pad元件 ...................................................................................- 25 -3.6.8 总版图...........................................................................................................................- 25 -3.7. 版图检查...................................................................................................................................- 25 -3.7.1 版图设计规则检查(DRC).......................................................................................- 25 -3.7.2 电路网表匹配(LVS)检查........................................................................................- 26 -3.7.3 后模拟...........................................................................................................................- 26 -4. 经验与体会..........................................................................................................................................- 27 -5. 参考文献..............................................................................................................................................- 28 - 附录A:74HC138电路总原理图 ...........................................................................................................- 29 - 附录B:74HC138 芯片版图....................................................................................................................- 30 -【摘要】现代社会正在飞速的发展,集成电路已经成为现代科技发展的支柱产业,现代技术产业的心脏,可以说,没有集成电路,就没有现代社会。