具有抗干扰能力的嵌入式系统设计与实现

嵌入式机电设备硬件与软件系统抗干扰措施探讨

出现动作 的时候形成的 回流对 系统产生冲击 。针对于扰 ①选择具有优 良导电性 的金属 当作屏蔽盒 ,并进行 元器件采用相应 的抑制措施 ,针对敏感的元器件采用隔 接地 ,从而使得 电磁 产生 的辐射不会对所控制部件造成 离 以及 对 应 的保 护措 施 。

影响。

②选择具备差动输入功能 的测量放 大器使得微弱信 号加大 , 再进行传输 。 21 信 号 采 集 的抗 干 扰 措 施 . ③模拟和开关 的信号检测线能够选择 屏蔽双胶线 , 在信号采集 当中,通常传感器 中所采集到的信号的 以预防静 电以及电磁产生的干扰 。 往往会有干扰信号存在 ,在硬件方面一般选择滤波器对 13 电源 抗 干扰 的技 术 . 信号完成 空间频率滤波 ,在软件方面利用程序多次采 集 ①选择模 拟电源或者稳压电源模块作为供 电电源。 模拟信号 , 并且 以此利用软件算法获得非 常逼真 的数据 。 ②能 够在 电源端通过 磁珠 以及 电容器构 成滤波 电 在 同一点 的数据进行多次采集 , 出它们 的均值 , 算 其均值 路, 从而出现滤波电路浪涌电压 。 就是采样 的最终结果 ,能够有效降低干扰信号对于采样 14 正确 接 地 . 结果产生的影响 。 假如发现采样数据波动较大 , 就必须对 ①使 电缆 的屏蔽层 和机 电设 备 的金属外 壳正确 接 同一采集点持续采集数个信号 ,然后按照中值 的计算方 地, 可以防止漏 电以及起 到屏蔽的作用 , 预防干扰源从外 法 , 取其 中值 当作采样的最终结果 。 通过程序判断滤波法 部侵入 , 能够增加系统 的有效抗干扰作用 。 选择软件方法取代硬件 R C无源滤波器。一旦 在持续采 ② 接地线和 电源线尽量短而粗。 并且采取隔离措施 , 集 的数据间插进延时加载程序 ,还可以预防比较宽的信 也就是使得机 电设备的地线和其余设施 的地线彻底隔离 号 干扰 。 开来 , 而将外部的干扰源隔断 。 从 2 . 系统中的软件看 门狗技术 2 ③ 把未使用悬空 的引脚处置好。将未使用 的引脚进 看 门狗 电路在系统一旦 出现操 作失误 、死 机或者是 行 接地 。 整个系统崩溃等状况 ,看 门狗 电路 就会 自动发出复位信 1 . 印制 板 电路 抗 干 扰 5 号, 从而使得系统能够重新恢复运行。 这种技术是软件有 ① 电路布线科学合理 。合理对抗干扰电路进行布局 效 结合硬件的一种抗程序 “ 飞” 跑 的技术措施 , 通过引导 指令将被捕捉到 的失控程序 强制引到 ( 下转第 13页) 0

嵌入式系统中的芯片设计与实现

嵌入式系统中的芯片设计与实现嵌入式系统是一种专门设计的计算机系统,它能够完成特定的功能并以可控的方式与其他系统交互。

嵌入式系统通常具有小型化、低功耗、高可靠性和实时性等特点,因此被广泛应用于汽车电子、医疗设备、智能家居、工业控制等领域。

而芯片则是嵌入式系统的核心组成部分,其设计和实现的质量直接影响着整个系统的性能和稳定性。

本文将从芯片设计的基础知识、常用工具、设计流程和实现技巧等方面,为读者介绍嵌入式系统中的芯片设计与实现。

一、芯片设计的基础知识芯片设计需要掌握的基础知识包括模拟电路、数字电路、计算机体系结构和嵌入式系统原理。

其中,模拟电路主要涉及到电压、电流、电阻等物理量,需要掌握放大器、滤波器、运算放大器等基本电路的设计和分析方法。

数字电路则是以二进制逻辑运算为基础,涉及到逻辑门、寄存器、计数器、存储器等数字电路的设计和分析方法。

计算机体系结构是嵌入式系统的核心,需要掌握CPU、存储器、总线以及相关的编程语言和开发环境。

嵌入式系统原理则强调对应用场景的理解和特定解决方案的设计,需要掌握具体的硬件和软件实现方法。

二、常用芯片设计工具芯片设计通常需要使用电路仿真、绘图和物理设计等工具。

电路仿真工具能够帮助芯片设计师模拟电路的工作状态和性能,常用的仿真工具有SPICE、PSPICE、HSPICE等。

绘图工具主要用于绘制原理图、布局和连线图,常用的工具有Altium Designer、OrCAD、PCB Artist等。

物理设计工具则是将电路布局转换为物理结构,包括各层电路的布局和相对位置等,常用的工具有Virtuoso Layout Suite、Cadence 等。

三、芯片设计流程芯片设计流程一般包括芯片规格确认、电路设计、验证和测试等步骤。

首先,需要对芯片的规格进行详细的确认,包括输入输出接口、运算速度、功耗和封装方式等方面。

其次,进行电路设计,包括电路原理图绘制、电路布局和连线的确定等工作。

设计完成后,需要进行仿真验证,以确保电路的功能、性能和稳定性。

单片机在嵌入式系统应用中的抗干扰措施

中 图 分 类 号 : P 6 . T 382 文献 标识 码 : A

Ant — i t r e e c e s e o h p i a i n o i. n e f r n e M a ur s f r t e Ap l to f - c M i r c n r le s i c o o t o l r n Em b d e y t m s e d d S se

Ab tac :n te a p ia in o c c n rle si mb d e y t ms,t e a t — itree c e fr a c fmi sr t I h p lc t fmir o t lr n e e d d s se o o o h n i n e r n e p rom n e o — f c c n r l r sali o tn n e o he s se rla ii o r o tol si l mp ra ti d x frt y tm eib lt e y,t u e d sg o n i— i tree c s e s nil h s t e in fra t h ne fr n e i s e ta o e e rh a e eo me to c o o t lr y t m Ac o d n o w r i g e p in e,t e a t os ds frte r sa c d d v l p n fmirc n rle ss se . c r i g t o k n x re c h n o e h u r i— h C S h n — it dee c s u n t e a p iai n o c c n rle i m b d d sse d p o i e s me U S te a d ne r n e is e i h p lc t fmir o t lm n e e de y tm a r vd o s o o o s n me s r sf rte d i fa misb e er ra d ei n tv Fo . a ue e g o d si l ro o h s n n lmi aie e rr K e r s: irc n r l r Emb d e y tm ;Ant i tre n e; mi il ro ; Reib l y y wo d M c o t l ; o o e e d d s se i— ne r c Ad s be e rr fe la ii t

本科专业认证《嵌入式系统设计综合实训》教学大纲

《嵌入式系统设计综合实训》教学大纲课程名称:嵌入式系统设计综合实训英文名称:Embedded System Design Training课程编号:0812200395课程性质:必修学分/学时:3/3周(15天)课程负责人:先修课程:C语言、接口技术A、嵌入式系统(上)、嵌入式系统(下)、嵌入式系统一、课程目标嵌入式系统是以应用为中心,以计算机技术为基础,并且软硬件可裁剪,适用于应用系统对功能、可靠性、成本、体积、功耗有严格要求的专用计算机系统。

嵌入式系统融合了计算机软硬件技术、半导体技术、电子技术和通信技术,与各行业的具体应用相结合。

自诞生之日起,就被广泛应用于军事、航空航天、工业控制、仪器仪表、汽车电子、医疗仪器等众多领域。

信息技术和网络的飞速发展,消费电子、通信网络、信息家电等的巨大需求加速了嵌入式技术的发展,扩大了嵌入式技术的应用领域。

《嵌入式系统设计综合实训》是学生学习了《嵌入式系统设计》等课程后的一次实际训练课程。

本课程要求学生选择一些比较重要的项目,进行实际的编程训练,以帮助学生巩固先修课程的知识,提高自己的动手能力,为以后从事相关专业技术工作、科学研究工作打好坚实的基础。

通过本课程的学习,达到以下教学目标:1.工程知识1.1 掌握必要的嵌入式系统设计知识。

1.2 能够应用嵌入式系统设计知识解决复杂的系统设计问题。

2.问题分析2.1 能够理解并恰当表述系统设计中的实际问题。

2.2 能够找到合适的解决方法。

3.设计/开发解决方案能够运用嵌入式系统设计知识进行产品规划与设计并体现创新意识。

4.研究能够采用嵌入式系统设计知识进行研究并合理设计实验方案。

5.使用现代工具能够有效使用嵌入式系统设计软件对实际问题进行分析与实现。

6. 终身学习6.1具有自觉搜集阅读与整理资料的能力。

6.2了解本专业发展前沿。

二、课程内容及学时分配本课程采取案例式学习,如表1所示。

三、教学方法作为一门实际训练课程,该课程以实验教学、综合讨论、动手实现等共同实施。

嵌入式系统的例子(一)

嵌入式系统的例子(一)嵌入式系统什么是嵌入式系统嵌入式系统(Embedded System)是集成了计算机硬件和软件,专门用来控制特定功能的计算机系统。

它通常被嵌入到一些特定的物理设备或系统中,不像常见的通用计算机系统那样具备多样化的功能。

嵌入式系统在现代科技中起着重要的作用,应用广泛,包括但不限于:- 汽车 - 手机 - 家电 - 医疗设备 - 无人机 - 工业控制设备等。

嵌入式系统的重要性嵌入式系统之所以如此重要,主要有以下几个原因:1. 特定功能由于嵌入式系统被设计用来控制特定功能,它们可以通过集成硬件和软件满足特定需求。

例如,汽车中的嵌入式系统可以控制车辆的引擎、导航系统和娱乐系统等。

这种特定功能使得嵌入式系统能够在各种复杂的设备中发挥作用。

2. 节省成本和空间相比于传统的计算机系统,嵌入式系统通常更简化、更紧凑。

它们通常集成在设备中的电路板上,不需要额外的外部连接。

这样可以节省空间,并减少设备的成本。

此外,嵌入式系统大多数时候不需要高速处理器和大容量存储器,这也降低了成本。

3. 实时性要求很多嵌入式系统需要实时响应,以满足特定应用的需求。

例如,在工业自动化中,嵌入式系统需要及时地接收和处理传感器数据,从而控制设备的运行。

这种实时性要求使得嵌入式系统能够在高压力、高并发的环境下稳定运行。

嵌入式系统的例子嵌入式系统有非常多的应用场景,下面列举几个常见的例子:1. 智能手机智能手机是目前最常见的嵌入式系统之一。

它们集成了处理器、操作系统、存储器、传感器和通信模块等组件,可以实现通话、上网、拍照和娱乐等功能。

智能手机的嵌入式系统需要满足性能稳定、省电和安全性等要求。

2. 家电现代家电产品如电视、空调、冰箱等,都配备了嵌入式系统。

这些嵌入式系统可以通过用户界面和传感器来实现智能控制和自动化。

例如,智能冰箱中的嵌入式系统可以监测食物的存储情况并提醒用户补货。

3. 无人机无人机也是一种广泛应用嵌入式系统的设备。

基于STM32的嵌入式PLC的设计

基于STM32的嵌入式PLC的设计嵌入式PLC(Programmable Logic Controller)是一种常见的工业自动化设备,用于控制和监测机械和工业过程。

基于STM32的嵌入式PLC设计具有高性能、低功耗和可靠性的特点。

本文将介绍基于STM32的嵌入式PLC的设计原理和关键特性。

一、设计原理嵌入式PLC基于STM32是通过使用STM32系列微控制器实现的。

STM32是意法半导体公司推出的一款32位微控制器,具有高性能、低功耗和丰富的外设接口。

嵌入式PLC利用STM32的高性能处理能力和丰富的外设接口,可以实现高速响应和多种输入输出功能。

设计过程包括以下几个步骤:1.硬件设计:选择合适的STM32微控制器作为主控芯片,设计电路板,包括与外部设备的连接和电源电路的设计。

2.软件开发:使用C语言或者其他高级语言开发PLC控制程序。

该程序控制输入输出设备并响应外部输入信号。

3.调试和测试:将开发好的软件烧录到STM32微控制器中,连接外部输入输出设备进行调试和测试。

二、关键特性1.高性能:STM32微控制器具有高性能处理能力,可以快速响应外部输入信号并实时控制输出设备。

2.多种输入输出接口:STM32系列微控制器具有多个通用输入输出引脚,可以连接各种传感器和执行器。

同时,也可以使用外扩IO板来扩展输入输出接口的数量。

3.丰富的通信接口:基于STM32的嵌入式PLC支持多种通信接口,如UART、SPI、I2C等。

这使得PLC可以与其他外部设备进行通信,实现数据交换和远程控制。

4. 实时操作系统支持:STM32系列微控制器支持实时操作系统(RTOS),如FreeRTOS和uC/OS等。

这些操作系统可以帮助开发人员更好地管理任务和处理中断。

5.低功耗:STM32微控制器具有低功耗特性,可以降低系统的能耗。

这对于一些对能耗要求较高的应用场景非常有利。

6.可靠性:STM32微控制器具有良好的抗干扰能力和稳定性,可以经受恶劣的工作环境和高负载情况。

嵌入式系统硬件抗干扰技术研究

4元 器件提 可靠性的 和方法 高 措施

构成系 统电 路的基本单 元是元器件, 选择 质量好合适的元器件是抑制千扰的基本保证。 4. 1 微处理器的 选择 目 为了 前, 提高硬件系 统自 身的可靠性, 各 制造商在单片机设计上采取了 一系列措施: ( 1 ) 降低外时钟频率,) 低噪声系 (2 列单片 (3 机; ) 时钟监测电 路、“ 狗”技术与低电 位。 看门 压复 (4 EFT 整形技术等。而且各种先进技术还在 ) 不断地发展和应用之中。因此, 要选用抗干扰 能力 较强, 有看门狗的微处理器。

2 硬件电路可靠性和抗干扰性设计 通常来自 供电系 信号传输通道的干扰 统和

是影响整个系统可靠性的主要因素, 因此硬件 抗干扰设计应将重点放在这里。硬件抗干扰 设计得好可将绝大部分干扰拒之门外, 使系统

的稳定 幅度提高. 性大

2. 1 供电系统抗干扰设计 电源在向系 统供电 也将其噪声祸合到 时, 系统电源上, 电源祸合的干扰对电路的影响非 常大, 统提供优质 给系 稳定的电源是保证系统 可靠性能的关键之一。为防止从电源系统引 入干扰, 可用隔离变压器接入电网, 防止电网 干扰侵入微机系统, 同时可作各种滤波器滤 波。 2.2 信号传输通道抗千扰设计 信号传 输通道包 统的前向 括系 通道和后向 通道, 对信号传输通道的可靠性设计可从以下 几个方面着手: ( 1 ) 利用光电祸合器及滤波器 对输入、 信号采用光电 输出 隔离措施, 可 将微处理器与前向通道、后向通道及其他部

嵌入式系统设计规范

嵌入式系统设计规范1. 引言嵌入式系统作为一种在特定应用领域中执行特定任务的计算机系统,其设计涉及到硬件和软件的紧密结合。

为了保证嵌入式系统的稳定性、可靠性和可维护性,设计规范在系统的开发过程中起着重要的指导作用。

本文将介绍一些嵌入式系统设计规范的要点,以帮助开发人员更好地进行嵌入式系统设计。

2. 硬件设计规范2.1. 电路板设计- 电路板应具备良好的布线和散热设计,以确保信号的传输质量和系统的稳定性。

同时,合理布局元器件和电路板层次,减少电磁干扰和噪声。

- 电路板应有足够的供电和接地,充足的电源和地线可以提高系统的抗干扰能力,并提供稳定的电源给各个模块。

- 在电路板设计中,还应注意信号完整性和时序约束的处理,保证信号的正确传输和时序的准确性。

2.2. 元器件选择和布局- 在选择元器件时,应优先考虑性能和可靠性。

选用具有良好性价比的元器件,并结合实际需求进行合理选择。

- 元器件的布局要合理,避免产生干扰和短路等问题。

尽可能避免元器件之间的相互干扰,减少串扰和电磁辐射。

2.3. 散热设计- 合理的散热设计对嵌入式系统的稳定性至关重要。

应根据系统功耗和工作环境条件选择适当的散热方式,如散热片、散热风扇等,确保系统在高负载下的正常工作。

3. 软件设计规范3.1. 系统架构设计- 首先需明确系统的功能需求和性能指标,进行系统的整体架构设计。

采用模块化设计思想,将系统分割为各个独立模块,提高系统的可维护性和易扩展性。

- 在模块之间的接口设计上,应尽量降低耦合度,减少模块之间的依赖关系。

3.2. 编码规范- 在编码规范上,应使用统一的命名规范、缩进格式和代码注释,提高代码的可读性和可维护性。

- 合理选择数据结构和算法,优化代码性能。

避免冗长的代码和重复的计算,提高系统的效率。

3.3. 异常处理和错误处理机制- 在软件设计中,应考虑系统可能出现的异常情况和错误。

合理设计异常处理和错误处理机制,提高系统的稳定性和可靠性。

《嵌入式指纹识别系统的设计与实现》范文

《嵌入式指纹识别系统的设计与实现》篇一一、引言随着科技的进步和安全需求的提高,指纹识别技术因其高精度、非接触式、不易伪造等优点,在身份验证、安全控制等领域得到了广泛应用。

本文将详细介绍嵌入式指纹识别系统的设计与实现过程。

二、系统设计目标本系统设计的主要目标是实现一个高效、稳定、安全的嵌入式指纹识别系统。

该系统应具备高识别率、低误报率的特点,同时应具备小型化、易集成、便于使用的优势。

三、系统设计原理本系统采用嵌入式处理器和指纹传感器相结合的设计方式,通过采集指纹信息,利用算法进行特征提取和比对,实现身份验证。

系统设计包括硬件设计和软件设计两部分。

(一)硬件设计硬件部分主要包括嵌入式处理器、指纹传感器、存储模块和接口电路等。

嵌入式处理器是系统的核心,负责运行指纹识别算法和控制整个系统的运行。

指纹传感器负责采集指纹信息,其性能直接影响到系统的识别率。

存储模块用于存储指纹信息和系统数据,接口电路则负责系统与其他设备的连接。

(二)软件设计软件部分主要包括操作系统、指纹识别算法和驱动程序等。

操作系统负责管理系统的软硬件资源,提供多任务处理和实时响应的能力。

指纹识别算法是系统的核心,负责提取指纹特征和比对指纹信息。

驱动程序则负责控制指纹传感器的采集和数据的传输。

四、系统实现过程(一)硬件实现硬件实现主要包括嵌入式处理器的选择和配置、指纹传感器的选型和连接、存储模块的选型和安装以及接口电路的设计和制作等。

在选择嵌入式处理器时,应考虑其性能、功耗、成本等因素。

指纹传感器的选型应考虑其采集精度、抗干扰能力、稳定性等因素。

存储模块的选择应根据系统的需求和成本考虑。

接口电路的设计应保证数据的稳定传输和系统的可靠性。

(二)软件实现软件实现主要包括操作系统的选择和配置、指纹识别算法的实现和优化以及驱动程序的编写和调试等。

在选择操作系统时,应考虑其兼容性、实时性、稳定性等因素。

指纹识别算法的实现应采用先进的算法和技术,保证高识别率和低误报率。

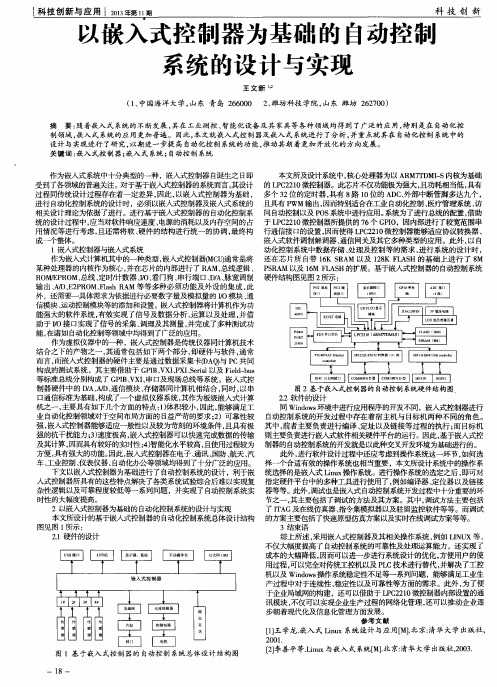

以嵌入式控制器为基础的自动控制系统的设计与实现

科 技 创 新

以嵌入 式控制器 为基础 的 自动控制 系统 的设 计与实现

王 文新 0

( 1 、 中国海洋大学, 山东 青岛 2 6 6 0 0 0 2 、 潍坊科技 学院, 山 东 潍坊 2 6 2 7 0 0 )

摘 要: 随着嵌 入 式 系统 的 不 断发 展 , 其在 工 业 测控 、 智 能化 设 备 及其 家具 等 各 种领 域 均 得 到 了广泛 的 应 用 , 特 别是 在 自动 化控 制 领域 , 嵌 入 式 系统 的应 用更 加普 遍 。 因此 , 本 文就 嵌 入 式控 制 器及 嵌 入 式 系统进 行 了分析 , 并重 点就 其 在 自动化 控 制 系统 中的 设 计 与 实现进 行 了研 究 , 以期进 一 步提 高 自动 化控 制 系统的 功 能 , 推 动 其 朝 着更 加 开放 化 的 方 向发展 。

关键词: 嵌 入 式控 制 器 ; 嵌入 式 系的一种 , 嵌 入式 控制器 自诞生之 日即 受到了各领域的普遍关注。 对于基于嵌入式控制器的系统而言, 其设计 过程同传统设计过程存在着一定差异, 因此 , 以嵌入式控制器为基础 , 进行 自动化 控制 系统 的设 计时 , 必 须 以嵌 入式控 制器及 嵌入式 系统 的 相关 设计 理论为依 据 了进 行 。进行 基于嵌 入式控 制器 的 自动化 控制 系 统的设计过程中, 应当对软件响应速度、 电源的消耗以及内存空间的占 用 情况 等进 行考 虑 , 且还需 将 软 、 硬 件 的结构 进行 统一 的协 调 , 最 终构 成—个整体。

本 文所及设 计系统 中 , 核 心处理 器为 以 A R M7 T D MI - S内核为基 础 的L P C 2 2 1 0 微控制器。此芯片不仅功能极为强大 , 且功耗相当低 , 具有 多个 3 2 位 的定 时器 , 具有 8 路1 0 位的 A D C 、 外部 中断 管脚 多 达九 个 , 目 . 具有 P WM输 出, 因而特 别适合在 工业 自动化控制 、 医疗管 理系统 、 访 问自动控制以及 P O S 系统 中进行应用。 系统为了进行总线的配置 , 借助 于L P C 2 2 1 0 微控制器所提供的 7 6 个G P I O,因内部进行了较宽范围串 行 通信接 口的设置 , 因而使 得 L P C 2 2 1 0 微 控制器 能够适应协 议转换 器 、 嵌入式软件调制解调器 、 通信网关及其它多种类型的应用。此外 , 以自 1嵌入式控制 器与嵌入式 系统 动化控 制 系统 中数 据存 储 、 处 理及 控制 等 的需 求 , 进 行 系统 的设计 时 , 作为嵌 ^ 式计算机其中的一种类型, 嵌入式控制器( MC U ) 通常是将 还 在 芯 片所 自带 1 6 K S R A M 以及 1 2 8 K F L A S H 的基 础 上 进行 了 8 M 某种 处理器 的 内核作 为核心 , 并 在 芯片 的内部进 行 了 R A M、 总线 逻辑 、 P S R A M以及 1 6 M F L A S H的扩 展。基于嵌 人 式控制 器的 自 动控 制系统 R O M / E P R O M、 总线、 定时计 数器、 、 看门狗 、 串行端口、 D / A、 脉宽调制 硬件结构 图 见图 2所示 : 输出、 A / D、 E 2 P R O M、 F l a s h R A M等 等 多种 必须 功 能及 外 设 的集 成 , 此 外, 还需要一具体需求为依据进行必要数字量及模拟量的 I / O模块、 通 信模块、 运动控制模块等的添加和设置。 嵌入式控制器将计算机作为功 能强大的软件系统 , 有效实现了信号及数据分析、 运算以及处理 , 并借 助于 接 口实现了信号 的采集、 调理及其测量 , 并完成了多种测试功 能, 在诸如自动化控制等领域中均得到了广泛的应用。 作为虚拟仪器中的一种 ,嵌入式控制器是传统仪器同计算机技术 结 合之下 的产物之 一 , 其通 常包 括如 下两 个部 分 , 即硬件 与 软件 , 通常 而言 , 而嵌 入式 控制 器 的硬 件 主要是通 过数 据采集 卡( D A Q ) 与P C共 同 构成 的测试 系统 ,其主要 借 助于 G P I B 、 V X I 、 P X I 、 S e r i a l 以及 F i e 1 d _ b u s 等标准 总线分别 构成 了 G P I B 、 V X I 、 串 口及现场 总线等 系统 。嵌 入式控 制器硬件中的 D / A 、 A / D 、 通信模块 、 存储器同计算机相结合 , 同时, 以串 图 2基 于嵌 入式控 制器的 自动控 制 系统 硬件结 构图 口通信标准为基础, 构成了一个虚拟仪器系统 , 其作为板级嵌入式计算 2 . 2软 件的设计 机之一 , 主要具 有如下几 个方 面的特点 : 1 ) 体 积较 小 , 因此 , 能够 满足工 同 Wi n d o w s 环境 中进 行应用程 序 的开发 不同 ,嵌入 式控制器 进行 业 自动化 控制领 域对 于空 间布局方 面的 日 益严 苛 的要 求 ; 2 )可 靠性较 自动控 制系 统 的开发过 程 中存 在着 宿 主机 与 目标机 两种 不 同的角 色 。 强, 嵌入式控制器能够适应一般性以及较为苛刻的环境条件 , 且具有极 其中, 前者主要负责进行编译 、 定址 以及链接等过程的执行 ; 而目标机 强的抗干扰能力; 3 ) 速度极高, 嵌入式控制器可 以快速完成数据的传输 则主要负责进行嵌 入式软件相关硬件平台的运行。因此, 基于嵌 入 式控 及其计算 , 因而具有较好的实时 l 生; 4 ) 智能化水平较高 , 且使用过程较为 制器的自动控制系统的开发就是以此种交叉开发环境为基础进行的。 方便 , 具有强大的功能。 因此 , 嵌入式控制器在电子、 通讯 、 国防、 航天、 汽 此外 , 进行软件设计过程中还应考虑到操作系统这一环节 , 如何选 车、 工业控制 、 仪表仪器、 自动化办公等领域均得到了十分广泛的应用。 择一个合适有效的操作系统也相当重要,本文所设计系统中的操作系 下文以嵌 ^式控制器为基础进行了 自动控制系统的设计,利于嵌 统选择 的是嵌 ^ 、 式L i n u x 操作 系统 。进行操作 系统 的选 定之 后 , 即可 对 入式 控制器所 具有 的这些特 点解决 了各类 系统试验 综合后 难以实 现复 指定 ̄4  ̄ - V台中的多种工具进行使用了, 例如编译器、 定位器以及链接 杂性 逻辑 以及可靠程 度较低 等一 系列问题 ,并实现 了 自 动 控制 系统实 器等等。此外 , 调试也是嵌 人式自动控制系统开发过程中十分重要的环 时性 的大幅度提 高。 节之 一 , 其主要 包括 了调试 的方法及 其方 案。其 中 , 调试方 法 主要包 括 2以嵌 入式控制器 为基础 的 自动化控制 系统 的设 计与实现 了I T A G及在 线仿真器 、 指 令集模拟器 以及驻 留监控软 件等等 。而调 试 本文 昕没计的基于嵌 人式控制器的 自动化控制系统总体设计结构 的方 案主要包 括了快速原 型仿真 方案以及实 时在线调试 方案等 等。

WindowsXPEmbedded嵌入式操作系统

WindowsXPEmbedded嵌⼊式操作系统内蒙古财经学院本科毕业论⽂Windows XP Embedded 嵌⼊式操作系统⾃助查询终端的定制⽅法作者张洋院系计算机信息管理学院专业计算机科学与技术年级08计科1班学号802102129指导教师唐建平导师职称教授内容提要嵌⼊式计算机系统作为计算机应⽤的⼀个重要领域,应⽤⼴泛。

Windows XP Embedded(XPE)具备XP与诸多嵌⼊式系统的优点。

针对嵌⼊式⼯控机的开发要求,设计了基于⼯控机硬件平台、采⽤XPE进⾏嵌⼊式系统开发的技术路线。

⾸先简单介绍XPE 操作系统的特点,其次详细说明了使⽤Windows XP Embedded Studio 设计⼯具构建XPE 操作系统的开发流程。

最后讨论XPE操作系统相对于原有的Windows XP Professional 操作系统的突出特点。

关键词:嵌⼊式操作系统、Windows XP Embedded、Windows XP Embedded StudioAbstractThe embedded computer system takes an important domain in computer application, so it is widely applied. Windows XP Embedded (XPE) has some advantages of XP and many embedded system. According to the requirement of a Industrial Personal Computer, a new method was put forward that develop the embedded system based on the Industrial Personal Computer and windows XP embedded. This article firstly introduces the characteristics of XPE operating system, and than it explained how to use Windows XP Embedded Studio T ools to construct XPE operating system in details, at last it provides the outstanding characters that XPE operating system had compared to Windows XP Professional.Key words: embedded operating system XPE operating system Windows XP Embedded Studio⽬录⼀、引⾔ (3)1.1 ⾃助式查询终端开发背景 (3)1.2 XPE的优势 (4)⼆、XPE重要组件说明 (4)2.1 防⽕墙组件 (4)2.2 ⽂件保护组件 (5)2.3 系统克隆组件 (5)三、针对⾃助式查询终端的XPE操作系统的定制流程 (7)3.1 ⾃助式查询终端的定制需求 (7)3.2 开发环境 (8)3.3 XPE操作系统配置 (9)3.4 测试XPE系统 (11)四、总结 (13)致谢 (15)⼀、引⾔1.1⾃助式查询终端开发背景校园⾥所应⽤的⼀卡通⾃主机,采⽤微型电脑⾃助查询⽅式,校园师⽣只要将感应卡在查询机的感应区确认⾝份后,便可以查询到您“校园卡”的信息:学校有关信息、维护业务、使⽤指南、申请挂失、更改密码和个⼈理财等有关信息。

《基于ARM+FPGA的嵌入式安全PLC设计与实现》

《基于ARM+FPGA的嵌入式安全PLC设计与实现》一、引言随着工业自动化程度的不断提高,可编程逻辑控制器(PLC)作为工业控制的核心设备,其安全性和可靠性显得尤为重要。

传统的PLC设计往往依赖于单一的处理器架构,难以满足日益增长的安全和性能需求。

因此,本文提出了一种基于ARM+FPGA的嵌入式安全PLC设计与实现方案,旨在提高PLC的安全性和性能。

二、系统架构设计1. 硬件架构本设计采用ARM+FPGA的异构计算架构,其中ARM处理器负责运行操作系统和高级算法,而FPGA则负责实现高速数据处理和实时控制。

这种架构可以充分发挥ARM的高性能计算能力和FPGA的高并行处理能力,从而提高系统的整体性能。

2. 软件架构软件架构包括操作系统、通信协议、安全机制等部分。

操作系统采用实时操作系统(RTOS),以保证系统的实时性和稳定性。

通信协议采用工业以太网协议,以实现与其他设备的无缝连接。

安全机制包括加密算法、访问控制、故障恢复等,以保证系统的数据安全和故障容错能力。

三、关键技术实现1. ARM处理器应用设计ARM处理器运行操作系统和高级算法,包括PLC的基本功能、数据处理、通信等。

通过优化算法和程序,提高系统的运行效率和响应速度。

2. FPGA硬件加速设计FPGA实现高速数据处理和实时控制,包括数字信号处理、滤波、控制算法等。

通过硬件加速技术,提高系统的处理速度和实时性。

3. 安全机制实现安全机制包括加密算法、访问控制、故障恢复等。

加密算法采用先进的加密技术,保证数据传输和存储的安全性。

访问控制采用角色权限管理,保证系统的授权访问。

故障恢复采用冗余设计和容错技术,保证系统的可靠性和稳定性。

四、系统测试与验证为了验证本设计的可行性和有效性,我们进行了系统测试和验证。

测试结果表明,基于ARM+FPGA的嵌入式安全PLC具有以下优点:1. 高性能:ARM+FPGA的异构计算架构可以充分发挥两者的优势,提高系统的整体性能。

单片机在嵌入式系统应用中的抗干扰技术

Vo1 0, 6 . No. 2 No , 00 v. 2 7

单片机在嵌 入式 系统应用 中的 院 机 电 工 程 学 院 ,浙 江 台卅I 1 0 0 . 江 临海 海 宏 集 团 ,浙 江 台 卅 3 7 0 ) 1台卅 职 3 8 0 ;2浙 I 10 0

源 干 扰造 成 单 片机 程 序失 控 的可 能性 减 小 。压敏 电压 的

计 算公 式 为 : I V MA= . x 2 V ( ~: 流 电压 有效 值 ) 163x ~V 交 5 ( )滤 波 器抑 制 高频 干 扰 。市 电 中含 有 多种 高 次谐 2

可靠性 、 安全 性就 成为 了一 个 大 问题 。 实验 室运 行正 常 在 的程序 到 了工业 现 场却 不能 运行 ,或者 出现运 行 不稳 定

经 常死 机等 。单 片机 应用 系 统 的抗 干扰 设 计是 系 统设 计

的重要 内容 之一 。抗 干扰 性 能 的好 坏将 决定 系 统 能否 在 复杂 的电磁 环境 下稳 定 可靠 地 工作 ,从 而决 定 了系统 的 实际使 用价 值 。 别是 在各 种 实时控 制 的远 距 离系 统 中 , 特 由于现 场环 境恶 劣 。 扰 因素较 多 . 干 系统 不 可避 免地 要 受 到其他 电磁 设备 的干 扰 ,若 仅按 常规 设 计 就很 难保 证 系 统 的正 常运 行 。 因此 . 干扰 问题 是设 计者 必须 充 分考 虑 抗 和解 决 的 , 面从 硬 件 和软件 两 个方 面谈 谈抗 干 扰设 计 。 下

摘 要 :嵌 入 式 系统 中, 干扰 性 能是 系统 可靠 性 的重要 指 标 ,结 合 自身的 实践 ,介 绍 电源 、 空间 电磁 、信 号 抗 传 输 通道 、 印制板 等 方 面抗 干扰 的几 种行 之 有 效 的办 法 。同 时提 出正 确 选择 元 器件 的 重要 性 ,探 讨

嵌入式系统设计及开发实践

嵌入式系统设计及开发实践随着信息技术的不断发展,嵌入式系统应用越来越广泛。

比如,电话、电视、NUM钱箱、智能家居、工业自动化、医疗器械、交通运输等领域。

嵌入式系统设计及开发是一个复杂的过程,需要对硬件设计、软件编程、系统集成等方面有深刻理解。

硬件设计嵌入式系统的硬件设计包括电路设计、PCB布线等。

电路设计是嵌入式系统硬件设计的核心环节,需要合理地选用芯片、模块及其他配件,建立起合理、高效、低功耗的电路系统。

例如,对于工业控制系统,需要选择高精度、低噪声、抗干扰能力强的模拟信号处理器和ATMEL单片机等芯片,配合使用各种传感器和执行器,从而构建出一个功能强大、性能稳定、可靠性高的系统。

PCB布线是指对电路板上各个元器件连接的专业设计,具有很高的技术含量。

电路板上的每个元器件都需要对应的连接方式,必须按照一定的规则进行布线才能保证性能可靠稳定。

例如,对于高速板卡设计,需要采用分层布线、阻抗匹配等技术,均衡地分配各个信号的层间跳数和长度,控制时钟抖动等问题,确保高速信号的传输品质。

软件编程嵌入式系统的软件编程包括底层驱动程序设计、应用层程序开发等。

底层驱动程序是指芯片、模块等底层硬件设备的驱动程序,需要根据硬件手册编写各个寄存器的操作方式、位域定义、时序规格等内容,确保硬件与软件相互配合,实现特定功能。

例如,对于USB外设的驱动程序,需要详细了解USB总线协议,理解设备驱动模型,了解传输数据包的格式,才能通过USB口与上位机通信。

应用层程序是指根据业务需求编写的应用程序,可以为用户提供各种服务。

例如,针对智能家居,需要编写支持人机交互的语音识别程序、图形界面程序等,以及实现家电的控制、监测、报警等功能。

系统集成嵌入式系统的系统集成包括硬件开发和软件开发的整合过程。

在硬件开发过程中,需要考虑适合软件驱动程序的硬件平台;在软件开发过程中,需要考虑驱动程序和应用程序之间的接口问题。

在整合过程中,需要将驱动程序与应用程序进行整合,并进行各种集成测试,以确保系统的稳定性和可靠性。

表面肌电信号检测电路的嵌入式系统设计与实现

表面肌电信号检测电路的嵌入式系统设计与实现在运动科学、医学康复和人机交互等领域,表面肌电信号(Surface Electromyography,简称sEMG)被广泛用于肌肉活动的监测和分析。

为了提高sEMG的采集和处理效果,嵌入式系统的设计与实现成为关键技术之一。

本文将介绍sEMG检测电路的嵌入式系统设计与实现过程。

一、嵌入式系统概述嵌入式系统是一种特定功能的计算机系统,需要实时性能和高度集成性。

在sEMG检测中,嵌入式系统可以实现信号的采集、滤波、放大和数字化等功能,为后续的信号处理提供高质量的原始数据。

二、硬件设计1. 信号采集电路为了保证sEMG信号的准确性和稳定性,采集电路需要合理设计。

一般采用差分放大器和预处理电路对信号进行放大和滤波处理。

同时,应采用抗干扰设计,如地线隔离、滤波器和屏蔽等手段,以提高信号质量。

2. 转换电路采集到的模拟信号需要经过模数转换器转换为数字信号。

根据系统要求,选择合适的模数转换器,通常考虑分辨率、采样频率和功耗等因素。

3. 控制电路嵌入式系统需要一套稳定可靠的控制电路来实现对硬件的控制和数据的传输。

常见的控制电路包括微处理器、存储器和外设等。

三、软件设计1. 系统架构设计根据嵌入式系统的硬件设计,确定系统的总体架构。

包括各个功能模块的划分和接口定义。

2. 信号处理算法sEMG信号的处理涉及到滤波、特征提取和模式识别等算法。

合理选择和优化算法可提高嵌入式系统的实时性和准确性。

3. 嵌入式软件开发根据系统需求,使用合适的嵌入式开发工具进行软件开发。

编写低级驱动、任务调度和应用层代码,保证系统的稳定性和高效性。

四、系统实现与优化在完成软硬件设计后,进行系统实现与优化是必要的。

首先进行功能测试,验证系统的稳定性和可靠性。

然后可以对系统进行优化,包括降低功耗、提高采样频率和增强数据传输效率等。

五、应用展望基于表面肌电信号检测的嵌入式系统在康复辅助、智能运动装备和虚拟现实等领域具有广阔的应用前景。

基于P1C18F2455单片机的网络嵌入式系统设计与实现

位域清零 (F ) B C

11 O

a aa aa

dddd ddd

下 面 以读 缓 冲器 为 例 , 明 E 2 J 0的 控 制 说 NC 8 6 和数 据通 信 的软件 实 现过程 。读缓 冲器 命令 可 以让

主控 制器 由 S KB及 接 收缓 冲器 中读 取 字 节 。先 把

C S引脚 拉 至 低 电平 以启 动 R M 命 令 ; 把 R M B 再 B 操作 码 和 随 后 的 5位 常量 发 送 至 E 2 J O 接 下 NC 8 6 ; 来从 S 引脚 中把 E DP O R T对 应 的存 储 器 中的数 据 移 出 ; 时如 果 主控制 器继 续 在 S K 引脚 提供 时 钟 此 C 信号 , E P 所 对 应 的 字 节 就 会 再 次 由 S 引 则 RD T O 脚移 出 。一 旦 ARTO NC被 使用 时 , 过 这种 方 法 I 通 不用 多余 的 S I P 指令 就可 以连 续 地 由缓 冲存 储 器 中 顺序 读取 字 节 。 在实 现 E 2 J 0缓 冲 器 R M 程 序 代 码 时 , NC 86 B 可 以调用 S I P 通信 函数 , 1 1 F 4 5中所 存放 数 据 PC 8 2 5

新技 术新 工艺

21 0 2年

第 7 期

2 3 实 现 S 通 信 . PI

化 的基础 , 抗干 扰能 力与 可靠性 均可 有所 提高 。 其

2 2 主 处 理 器 的 软 件 设 计 .

2 3 1 E 2 J O的 S I 序 . . Nc 86 P 时

2 2 1 合理 利用 程序 存储 器 .. 要 提 高程 序 的设 计 质 量 , 先要 了解 处 理器 的 首

嵌入式系统可靠性设计与实现

嵌入式系统可靠性设计与实现嵌入式系统是一种广泛应用于各种领域的计算机系统,集成了处理器、存储器、输入输出接口等组件,用于控制和执行各种任务。

随着嵌入式系统使用场景的不断扩大,对其可靠性的要求也日益提高。

在嵌入式系统开发中,如何设计和实现可靠性成为关键问题。

为了保证嵌入式系统的可靠性,需要从多个方面进行设计和实现,包括硬件设计、软件设计、测试验证等。

下面将对这些方面进行详细探讨。

硬件设计硬件设计是嵌入式系统可靠性的基础,主要包括电路板设计、信号处理、电源设计等。

在硬件设计过程中,应该考虑以下几个方面:电路板设计方面,应该采用高质量的材料,如高温FR-4材料、高精度电容电阻、金属化框架等,以提高硬件的抗干扰能力和稳定性。

信号处理方面,应该采用合适的滤波器、抗干扰措施等,以保证输入输出信号的稳定性和精度。

电源设计方面,应该采用稳定可靠的电源设计,避免过压、欠压情况,以减少硬件故障的发生。

同时,在硬件设计过程中,还应该进行严格的电磁兼容性测试和抗干扰测试,以保证硬件的可靠性。

软件设计软件设计是嵌入式系统的核心,主要包括操作系统设计、应用程序开发等。

在软件设计过程中,应该进行以下几个方面的考虑:操作系统设计方面,应该选择合适的实时操作系统,具有高度的可靠性和稳定性,如Linux、VxWorks等。

应用程序开发方面,应该采用高可靠的程序设计方法,如面向对象编程、模块化设计等,提高程序的可维护性和可靠性。

同时,在软件设计过程中,还应该进行严格的代码审查、单元测试和集成测试等,以保证软件的可靠性。

测试验证测试验证是嵌入式系统可靠性验证的关键。

测试验证包括功能测试、性能测试和可靠性测试等。

在测试验证过程中,应该进行以下几个方面的测试:功能测试方面,应该覆盖所有的功能点,进行全面的测试,保证功能的正确性和完整性。

性能测试方面,应该考虑系统的响应速度、资源占用情况等,以保证系统的稳定性和可靠性。

可靠性测试方面,应该模拟各种可能的故障场景,进行系统的应急响应和恢复测试等,以保证系统的可靠性和稳定性。

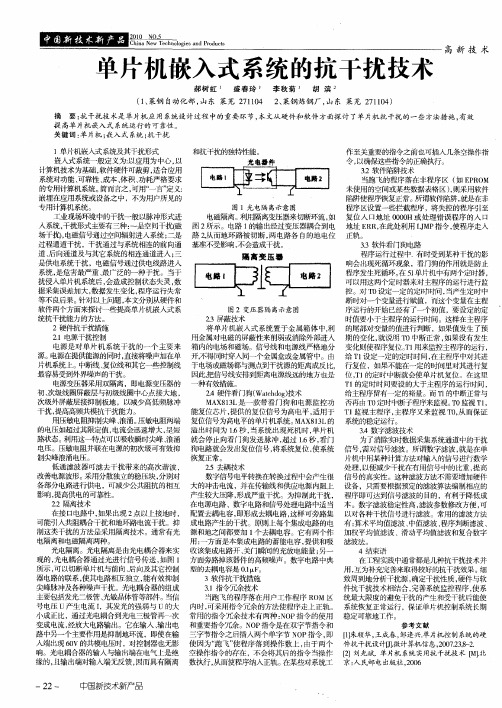

单片机嵌入式系统的抗干扰技术

C ia N w T c n lge n rd cs h n e e h oo isa d P o u t

Hale Waihona Puke 高 新 技 术 单片机嵌入式系统的抗 干扰技术

郝 树 虹 盛 春 玲 李 秋 菊 胡 滨

(、 1 莱铜 自动 化部 , 东 菜芜 2 10 2 莱钢 炼钢 厂 , 东 莱芜 2 1 0 ) 山 7 14 、 山 7 14 摘 要 : 干扰技 术是单 片机 应 用 系统设 计过 程 中的 重要 环节 , 文从硬 件 和软 件 方面探 讨 了单 片机抗 干扰 的一 些方 法措施 , 效 抗 本 有 提 高单 片机 嵌入 式 系统运 行 的可 靠性 。 关键 词 : 片机 ; 单 嵌入 式 系统 ; 干扰 抗 1 片机嵌入式系统及其干扰形式 单 和抗 干扰 的独特 性能。 作至关重要的指令之前也可插入几条空操作指 嵌入式系统 一般 定义为: 以应用为 中心 , 以 光 魁器件 令, 以确保这些指令的正确执行。 计算机技术为基础 , 软件硬件可裁剪 , 应用 适合 3 l 2软件陷阱技术 系统对功能 、 可靠性 、 、 、 成本 体积 功耗严格 要求 当跑 飞 的程序 落在非程序 区 ( E R M 如 PO 的专用计算机 系统 。 简而 言之 , 可用“ 一言” 义: 定 未使用 的空间或某些数据表格 区)则采用软件 , 嵌 埋在应 用系统或设备之 中,不为用户所见 的 陷阱使程序恢复正常。 所谓软件陷阱 , 就是在非 专用计算机 系统 。 图 1光电隔 离示意图 程序 区设置一些拦截 程序 , 将失控 的程 序引至 工业现场环境 中的干扰一般 以脉 冲形式 进 电磁隔离 。 利用隔离变压器来切断环流 , 如 复位 人 口地址 00H或 处理错 误程 序 的入 口 00 入 系统 , 干扰形式主要有三种 : ~是空 间干扰 磁 图 2 所示 。电路 1 的输 出经过 变压器耦合到 电 地址 E R 在此处利用 LM R, J P指令 , 序走人 使程 场干扰) , 信号通过空 间辐射进入 系统 ; 是 路 从而地 环路被 切断 , 电路 各 自的地 电位 正轨 。 电磁 二 两 过程通道干扰 , 干扰通过 与系统相连 的前 向通 基准不受影响 , 不会造成 干扰 。 3 - 3软件看 门狗 电路 道 、 向通道及与其它 系统 的相连通道进入 ; 后 三 程序运行过程 中. 时受到某种干扰 的影 有 隔 离受 蓬器 是供 电系统 干扰 ,电磁信 号通 过供电线路进入 响会 现死循环现象 , 门狗 的作用就是 防止 看 系统 , 是危害最 严重 、 最广泛 的一 种于扰 。当干 程 序发生死 循环。 5单片机中有两个定时器 , 在 1 扰侵入单片机系统后 , 会造成控制状 态失灵 , 数 可以用这两个定时器来对 主程序 的运行进 行监 据采集误差加大 , 数据发生变化 , 运行失常 程序 控。对 T 设定一定 的定 时时间 , O 当产生定 时中 等不 良 果。 后 针对 以上问题 , 本文分别从硬件和 断时对一个变量进行赋值 ,而这个变量在 主程 软件两个方面来探讨一些 提高单片机嵌入式系 图 2 变压 器 隔 离示 意 图 序运行的开始 已经有 了一个初值 , 要设定 的定 统抗 干扰能力 的方法 。 2 - 3屏蔽技术 时值要 小于主程序 的运行时 间。这样在主程序 2硬件抗干扰措施 将单 片机 嵌入式 系统置 于金 属箱 体 中, 利 的尾 部对变量的值进行判断 ,如果值发生 了预 2 . 1电源干扰控制 用金 属对电磁的屏蔽性来削弱或 消除外 部进入 期 的变化 , 就说 明 T 0中断 正常 , 如果没 有发生 电源是对 单 片机 系统 干扰 的一个 主要 来 箱 内的电场和磁场 。信号线和 电源线严 格地分 变化 则使程 序复位 。 1 T 用来 监控主程序的运行 , 源。 电源在提供能源 的同时 , 直接将噪声加在单 开 , 不得同时穿人 同一个金属盒或金属 管中。 由 给 T 设 定一定 的定时时 间, l 在主程序 中对其进 片机 系统上 。 中断线 、 复位线和其它一些控制线 于 电场或磁场都与测点到干扰源的距离成反 比, 行复位 , 如果 不能在一定的时间里对其进行复 最容易受到外界噪声的干扰。 因此, 把信号线安排 到距离 电源线远 的地方也 是 位 ,1 T 的定时 中断就 会使单片机 复位 。在这里 电源变压器采用双隔离 ,即电源变 压器 的 种有效措施 。 T 的定时 时间要设的大于 主程序 的运行时间 , 1 初、 次级线圈屏蔽层与初级线 圈中心点接大地 , 2 - 4硬件看 门狗 ( t dg技术 Wa ho) c 给主程序 留有一定的裕量 。而 T 的中断正常与 l 次级外屏蔽 层接抑 制板 地 ,以减少高低频脉 冲 M X 1L A 83 是一 款带看 门狗 和 电源监 控功 否再 由 _】 r 定时 中断子程序来监视。 O ( T 监视 T , 1 干扰 , 提高高频共模抗 干扰能力 。 能复位芯片 , 的复位信号 为高电平 , 于 T 监视主程 序 , 序又来监视 T , 提供 适用 1 主程 O从而保证 用压敏电阻抑制尖 峰 、 。 浪涌 压敏 电阻两端 复位信号为高电平 的单片机 系统 。 A 8 M X L的 系统的稳定运行。 1 3 的电压如超过其 限定值 , 电流会迅速 增大 , 呈短 溢出时 间为 1 秒 , . 6 当系统 出现 死机 时 , 片机 单 3 A数字滤波技术 路状态。 利用这一特 点可以吸收瞬时尖峰 、 浪涌 就会停止 向看 门狗发送脉 冲 , 超过 1 秒 , 门 . 看 6 为了消除实时数 据采集 系统通道中的干扰 电 压。压敏电阻并联在 电源 的初 次级 可有效抑 狗电路就会发 出复位信号 , 系统 复位 , 将 使系统 信号 , 需对信号滤波 。所谓数字滤波 , 在单 就是 制尖峰浪涌电压。 恢复正常。 片机 中用某种计算方法对输人 的信号进行 数学 低通 滤波器 可滤去 干扰带来 的高次谐 波 , 2 . 5去耦技术 处理, 以便减 少干扰在有用信号 中的比重 , 提高 改善 电源波形 。 采用分散独立 的稳压块 , 对 分别 数字信号 电平转换在转换过程 中会产生很 信 号的真实性 。这种滤波方法不需要增加硬件 各部分电路进行供 电,可减少公共阻抗 的相互 大 的冲击电流 , 在传输线和供应 电源 内阻上 设 备 ,只需要 根据预定的滤波算法编制相应 的 并 影响 , 提高供电的可靠 陛。 产生较 大压 降 , 成严 重干扰 。为抑制 此干扰 , 程序即可达到信号滤波 的 目的,有利于 降低成 形 2 . 2隔离技术 在 电源 电路 、数字 电路 和信 号处理 电路 中适 当 本 。数字 滤波稳定性高 , 滤波参数修改方便 , 可 在接 口电路 中 , 出现 2 以上接 地时 , 配置去耦 电容 , 如果 点 即形成去耦 电路 , 这样可旁路集 以对各 种干扰信号进行滤波 。常用 的滤波方法 可能 引入共 阻耦 合干扰和地环路 电流干扰 。抑 成 电路产生 的干扰 。原则 上每个集成 电路 的电 有 : 算术平 均值滤波 、 中值滤波 、 程序判断滤 波 、 制这类 干扰 的方法 是采用隔离技术 。通常有光 源和地之 间都要加 1 个去耦 电容 。它有两个作 加权平 均值滤波 、滑动平均值滤波和复合数字 电隔离和电磁隔离 两种 。 用: 一方面是本集成 电路 的蓄 能电容 , 提供和 吸 滤波法 。 光电隔离。光 电隔离是 由光 电耦合器来实 收该集成 电路开 、 门瞬 间的充 放电能量 ; 关 另一 4结束语 现 的, 电耦合 器通过光进行 信号传 送 , 图 1 方面旁路掉该器件 的高频 噪声。数字电路 中典 光 如 在 r程实践中通常都是几种抗干扰技术并 】 _ = = = 所示 , 可以切断单片机与前 向 、 向及其 它控制 型的去耦 电容是 0 F 后 . 。 1 I x 用 , 为补 充完善来 取得较好 的抗干扰效果。 互 细 器电路的联系, 使其电路相互独立, 能有效抑制 3软件抗 干扰措施 致周到地分析干扰源 , 确定干扰 洼质 , 与软 硬件 尖峰脉冲及各种噪声干扰。光电耦合器的组成 3 . 1指令冗余技术 件抗干扰技术相结合 , 完善系统监控程序, 使系 主要包括发光 二极管 、 光敏品体管等部件。 当信 跑 飞的程序落 在用户工作 程序 R M 区 统最大限度 的避免 干扰的产生和受干扰后能使 O 号电压 U产生 电流 I ,其发光 的强弱与 u的大 内时 , 可采用 指令 冗余的方法使程序走 上正轨 。 系统 恢复正常运行 , 保证单 片机控 制系统长期 小成 正 比, 过光电耦合到光 电三极管再一 次 常用 的指令冗余 技术有 两种 : O 通 N P指令 的使 用 稳定可靠地丁作 。 变成 电流 , 大电路 输出。它在输入 、 出电 和重要指令冗余。N P 经放 输 O 指令是在双字节指令和 参 考 文献 路中另一个 主要作用是抑制地环流 ,即使在输 三字节指令之 后捅人两个单字 节 N P O 指令 , 即 f朱顺华 , 1 】 王成春 , 邹逢兴. 单片机控制 系统的硬 入端 出现 6 V的共模 电压时 , 0 对控制器也无影 使 因为“ 跑飞 ” 序落 到操作 数上 , 两个 件 抗干扰 设计 微计算机信 息,07 3 . 使程 由于 20. , 2 响。光 电耦合器 的输入 与输 }端在 电气上是绝 空操作指令 的存在 , H 不会将其 后的指令 当操作 『 刘光斌. 2 1 单片机 系统 实用抗干扰技术 [】 M. 北 缘 的, 出端对输入端无反馈 , 且输 因而具 有隔离 数执行 , 而使程序纳入正轨 。 从 在某些对 系统工 京 : 民邮 电出版社 ,0 6 人 2 0

嵌入式系统软件可靠性和抗干扰技术

片 例 , 各种软件 机为 对 抗干扰 进行总 技术 结。 2 指 令 冗余 设 计

处理 器指令 出操作码 和操作数弼 部分组成 区 别 操作 码和操作数 则由取指令 的顺 序决定.操 作时

序 由程 序 计 数 器 P C控 制 I。C U 取 指 令 时 先 取 操 P L l

维普资讯

电 子 产 品 可 靠 性 与 环 境 试 验

̄t 4№ 4Au .2 0 . 2 g. 0 6

嵌入式 系统软件可靠性和抗干扰技术

伍 伟 杰

( 广东 工 贸 职业 技 术 学 院 .广 东 广州 501) 15 0

摘 要 :针对嵌入式控制 系统在工程应用 中存在的干抗现象 比较硬件和软件抗干扰的特点 . 述了各种系 综

Ab t a t Ai d a itr rn e pe o n fe b d e o t lss m npa ta mje, sr c : me t ne ee c h nme ao m e dd c nr yt i rci lp el f o e c

t e h r ceit s o h r w r n sf r a t - ne e e c e i ae c mp r d Vaiu h c aa trs c f a d a e a d o wae n i itr rn e d sg r o ae . i t f n r s o

Ke r s:e e d ds se y wo d mb e y tm;a t i t ee c ;rd n a c ;s f r a ;f tr d ni n e rn e e u d n y ot et p i e — 可 靠 性 和 抗 干 扰设 计 可分 为

作 者 筒 介 : 伍伟 杰 ( 97 ) 男 ,广 末韶 关 人 . 广 东 2 贸职 hr 术 学 院助 教 .硕 士 ,主 要 从 事 敷 控 技 术 、 制 造 自动 化 与机 电 17一 + - r -t

单片机嵌入式系统的抗干扰技术探讨

引言 近年来 ,单片机嵌入式系统在工业测控系统领域得到了广泛应用 , 但是这种微控制器在工业 现场 的环境下就会 出现运行不稳定 , 经常死机 等问题 , 特别是在各种实 时控制 的远距离系统中 , 现场环境条件差 , 干 扰 因素较多 , 系统 自然就会受到其他 电磁设备 的干扰 , 所 以单片机嵌入 式系统的抗干扰设计是非常重要 的, 抗干扰性能好才能使系统在复杂环 境 中正常工作。 下面就常见 的干扰源和抗 干扰的两种软硬件技术做了简 要探讨分析。

3 、软件 抗干扰技术

3 . 1软件看 门狗技术 程序在运行过程 中经常受到干扰 而出现死循环现象 , 而看门狗的作 用 就是预 防死循环现象的发生 。在常见 的 5 1 单 片机 中一般都有两个定 时器 , 这两个定时器可以对主程 序的运行进行监控 。当对 T 0 设定了一 定的定时时间, 如果在产生定时 中断时对 其中的一个变量赋值 , 而该变 量已经有 了一个初值 , 那么主程序就会对 变量 的值进行判断 , 要是判断 该值发生变化 , 则T 0 中断正 常,若没有发生变化 , 程序则复位 。 T 1 是 监控 主程序 的,当对 T 1 设定一定的定时时间,如果主程序没有在一定 的时间内进行复位 , 那么 T 1 的定时中断就会使单片机复位。 T 1 是否中 断正 常是 由 定时 中断子程序监 控的,所 以 T 0 、T 1 和主程序之间有 着互相监控 的循环 ,从 而维持 系统 的正常运行 。 3 . 2数 字 滤 波 技 术 数字滤波的定义是在单 片机 中用其他计算方法处 理数字 , 减 少有用

2 、硬件抗干扰技术

2 . 1 控 制 电 源干 扰

如上文所述 , 对单片机嵌入式系统的干扰 主要是来 自电源干扰 , 所 以只要控制好 电源干扰 , 那么单片机嵌入式系统所受 的影 响就会大大减 少。 对 于控制 电源 的干扰主要有以下三个措施 : 用压敏 电阻抑制尖峰 以及 浪涌 。 压敏 电阻两端 的实际 电压如果超过 了限定值 , 电流就会增大 导致短路 。 于是 , 压敏 电阻 的这一特性可以用作 吸收瞬间尖峰和浪涌 电 压。 将压敏 电阻并联在电源变压器的初 次级 , 就可抑制尖峰和浪涌 电压 电压 , 从而减少电源干扰 。 用低涌滤波器阻碍高频电阻。 许多高次谐 波很容易通过电源进入单 片机 嵌入式 系统 , 而其 它的一些 电磁波也会通 过 电源线感应进入系统 , 从而对系统造成 干扰和影响 , 如果在 电源 电路 中加入低涌滤波器 , 就可以过滤干扰带来 的高次谐波 , 抑制高频信号干 扰 ,还能采用独立的稳 压块对各部分 电路提供 电能 ,提高供 电可靠性 。 电源变压器用双隔离方式 。 双隔离方式是说将 电源变压器的初级线圈 的中心和初级线圈的屏蔽层 与大地 连接 ,次级外屏蔽层 与抑制板地相 接 ,这种做法就可以减少 高低频脉 冲的干扰

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

具有抗干扰能力的嵌入式系统设计与实现

近年来,嵌入式系统得到越来越广泛的应用,从智能家居到工业自动化、智能

交通等各种领域都离不开嵌入式系统的支持。

然而,在实际使用中,嵌入式系统常常会受到各种干扰,如电磁干扰、温度干扰、噪声干扰等,导致系统不稳定,功能异常。

因此,如何设计和实现具有抗干扰能力的嵌入式系统,成为了嵌入式系统工程师面临的一个重要问题。

一、设计具有抗干扰能力的嵌入式系统的导则

1.硬件抗干扰设计。

在硬件设计阶段,应采取一系列措施,以减小噪声干扰和

电磁干扰对系统的影响。

首先,在电路设计时应遵循短接、走线平行等原则,尽量避免布线交叉引起的

耦合干扰。

同时,应选用合适的传输线和阻抗匹配技术,减少信号传输中的反射、串扰等现象。

其次,应选用合适的电源方案,如DC/DC转换器或电源滤波器,以减小电源

噪声对系统的干扰。

最后,在PCB设计时,应采用多层板设计,以减少地面和电源面之间的干扰,同时合理布置各种元器件,减少干扰引入。

2.软件抗干扰设计。

在软件设计阶段,应采取一系列措施,以提高系统的稳定

性和抗干扰能力。

首先,应采用可靠的操作系统和程序框架,如RTOS、ARM嵌入式开发框架等,以提高系统的稳定性和可靠性。

其次,在软件设计时应注重程序的健壮性和可靠性,避免死循环、空指针等错

误出现。

最后,应采用独立的中断处理程序和中断优先级机制,保障系统对各种异常情况的响应能力,并在程序中设置软件看门狗机制,确保系统能够及时恢复。

二、案例分析:一种基于FPGA的抗干扰嵌入式系统设计和实现

为了更好地解决嵌入式系统抗干扰问题,我们设计并实现了一种基于FPGA的抗干扰嵌入式系统。

该系统采用FPGA作为主控芯片,并通过专用电路和程序架构提高了系统的稳定性和抗干扰能力。

具体来说,在硬件设计方面,我们采用了多项措施,如电路浪涌保护、电磁屏蔽、信号滤波等,以减小噪声干扰和电磁干扰对系统的影响。

在软件设计方面,我们则采用了可靠性高、稳定性强的FreeRTOS操作系统和ARM嵌入式开发框架,并通过中断处理程序和中断优先级机制保障系统对异常情况的响应能力。

通过多组实验数据的对比,我们发现,该系统较传统嵌入式系统在稳定性和抗干扰性方面有了显著的提升,满足了实际应用的需求。

三、未来展望

作为嵌入式系统开发领域的一项重要研究课题,抗干扰嵌入式系统在未来的应用前景非常广阔。

随着社会的不断发展和科技的不断进步,对嵌入式系统的稳定性和可靠性要求也越来越高。

因此,如何设计和实现具有更强抗干扰能力的嵌入式系统,成为了未来嵌入式系统研究的一个重点方向。

总之,具有抗干扰能力的嵌入式系统设计和实现是一项非常重要的工程任务。

只有在硬件和软件两个方面都加以重视和改进,才能够设计出更加稳定、可靠的嵌入式系统。

相信在未来,抗干扰嵌入式系统将会得到更广泛的应用和不断的突破。