电感的升压、降压原理

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

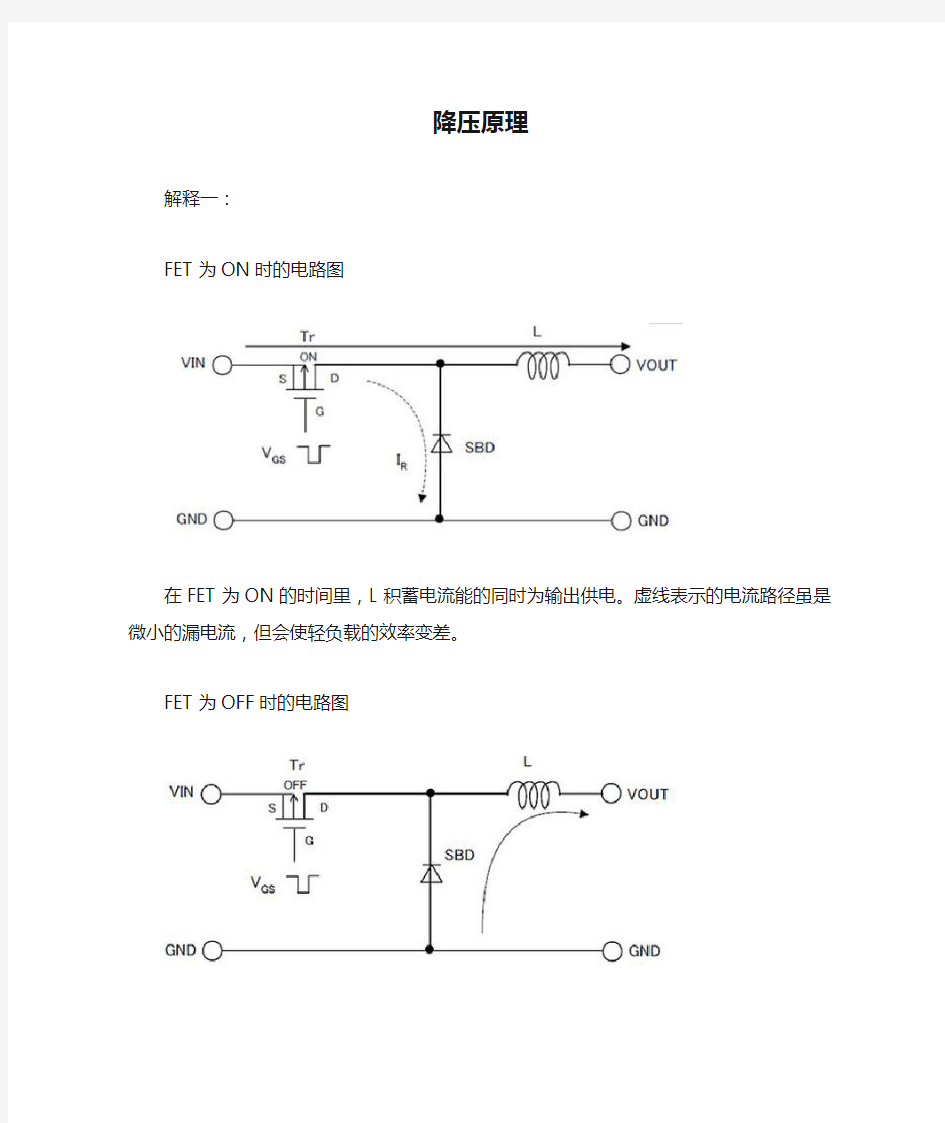

降压原理

解释一:

FET为ON时的电路图

在FET为ON的时间里,L积蓄电流能的同时为输出供电。虚线表示的电流路径虽是微小的漏电流,但会使轻负载的效率变差。

FET为OFF时的电路图

在FET为OFF时,L要保持OFF前的电流值,使SBD为ON。此时,由于线圈的左端被强制性地降到0V以下,VOUT的电压下降,即降压电路原理。

由此,FET的ON时间长L里积蓄的电流能越大,越能获得大功率电源,降压的幅度越小。

降压时,由于FET为ON时也要给输出供电,所以不需要限制占空比的最大值。

解释二:

降压式DC/DC 变换器基本工作原理电路如图所示。VT1 为开关管,当VT1 导通时,输入电压Vi 通过电感L1向负载RL供电,与此同时也向电容C2 充电。在这个过程中,电容C2及电感L1中储存能量。当VT1 截止时,由储存在电感L1中的能量继续向RL供电,当输出电压要下降时,电容C2中的能量也向RL放电,维持输出电压不变。二极管VD1为续流二极管,以便构成电路回路。输出的电压V o经R1和R2组成的分压器分压,把输出电压的信号反馈至控制电路,由控制电路来控制开关管的导通及截止时间,使输出电

压保持不变。

控制电路和VTI,VD1是一体的都是RT8024

升压原理

解释一:

FET为ON时的电路图

在FET为ON的时间里在L积蓄电流能。虚线表示的电流路径虽是微小的漏电流,但会使轻负载的效率变差。

FET为OFF时的电路图

在FET为OFF时,L要保持OFF前的电流值,相当于在输入回路增加了一个“电源”。由于线圈的左端被强制性固定于VIN,因此输出VOUT的电压要大于VIN,即升压电路原理。由此,FET的ON时间越长(FET的触发占空比D越大),L里积蓄的电流能越大,越能获得电源功率,于是升压就越高。但是,FET的ON时间太长的话,给输出侧供电的时间就极为短暂,FET为ON时的损失也就增大,变换效率变差。因此,通常要限制占空比的最大值,不超过适宜的占空比D。

解释二: