《组原》习题课

〖语 文〗第7课《散文诗二首》习题课件 -2024-2025学年统编版语文七年级上册

1 2 3 4 5 6 7 8 9 10

返回目录

5. 文章以“母亲的花园”为题,有什么作用?(4分) 内容上,点明了本文的写作对象是母亲的花园,交代了文章的主要内

容;(2分)结构上,贯串全文,是全文的叙事线索。(2分)

6. 联系语境,揣摩人物心理。(3分)

“哪儿没花?还要专门种?我这门口一年四季都有花儿!” 这句话表现了母亲反驳时不容置疑的心理;(2分)表现了母亲觉得

1 2 3 4 5 6 7 8 9 10

返回目录

⑥ 母亲要回家,我们都清楚,她就是舍不得老家房前屋后的“一 亩三分地”。

⑦ 春风拂面时我们回家,母亲大手一挥:“去门口树上找几枝 香椿芽,中午给你们上时鲜——香椿蒸鸡蛋!”我们这才惊觉为啥 到处烟翠弥漫,唯独这两棵光杆儿树仅在顶端支棱着几片嫩芽,让 人不忍直视。

① 父亲给我发消息:海棠开了,你妈问要不要给你送过去。 ② 消息下方是图片:富贵典雅、两人合围的大花盆内,一株垂丝 海棠花开正艳。虬枝盘旋、花团锦簇,挂满枝头的一朵朵花儿娇艳欲 滴,隔着屏幕都能感觉到她们在枝头的颤动,比当初从花市买来时枝干 更显粗壮、花儿也更繁盛,着实惹眼,让人心欢。

1 2 3 4 5 6 7 8 9 10

⑨ 我哭笑不得:“妈,门口种些花花草草不好吗?”“哪儿没

花?还要专门种?我这门口一年四季都有花儿!”是的,春天蚕豆

花儿,夏天黄瓜花儿,秋天扁豆花儿……冬天花儿倒是少,可豌豆

苗、莴苣叶从雪堆里冒出头,绿莹莹地直往人心里钻,也的确是养

眼养心的佳品。

1 2 3 4 5 6 7 8 9 10

返回目录

⑩ 母亲的菜园子就是她的大花园。我的海棠回去可没有资格抢占

欹.斜(qǐ)

莲蓬.(penɡ)

5、3《应用二元一次方程组》 一课一练 21-22学年北师大版 八年级数学上册

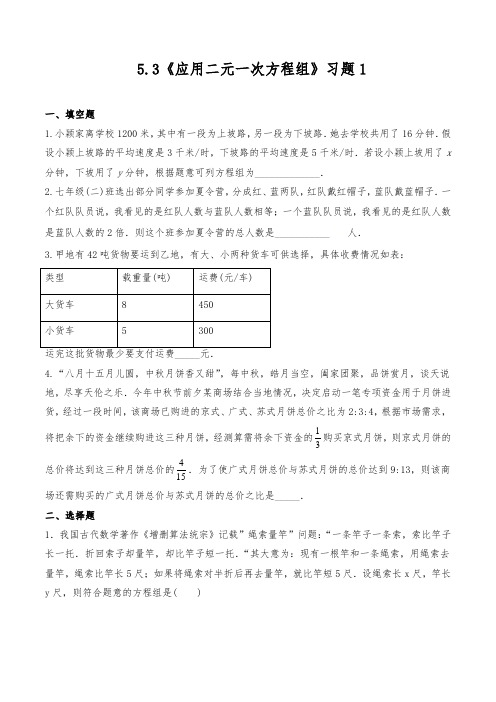

5.3《应用二元一次方程组》习题1一、填空题1.小颖家离学校1200米,其中有一段为上坡路,另一段为下坡路.她去学校共用了16分钟.假设小颖上坡路的平均速度是3千米/时,下坡路的平均速度是5千米/时.若设小颖上坡用了x 分钟,下坡用了y分钟,根据题意可列方程组为_____________.2.七年级(二)班选出部分同学参加夏令营,分成红、蓝两队,红队戴红帽子,蓝队戴蓝帽子.一个红队队员说,我看见的是红队人数与蓝队人数相等;一个蓝队队员说,我看见的是红队人数是蓝队人数的2倍.则这个班参加夏令营的总人数是___________人.3.甲地有42吨货物要运到乙地,有大、小两种货车可供选择,具体收费情况如表:4.“八月十五月儿圆,中秋月饼香又甜”,每中秋,皓月当空,阖家团聚,品饼赏月,谈天说地,尽享天伦之乐.今年中秋节前夕某商场结合当地情况,决定启动一笔专项资金用于月饼进货,经过一段时间,该商场已购进的京式、广式、苏式月饼总价之比为2:3:4,根据市场需求,将把余下的资金继续购进这三种月饼,经测算需将余下资金的13购买京式月饼,则京式月饼的总价将达到这三种月饼总价的415.为了使广式月饼总价与苏式月饼的总价达到9:13,则该商场还需购买的广式月饼总价与苏式月饼的总价之比是_____.二、选择题1.我国古代数学著作《增删算法统宗》记载”绳索量竿”问题:“一条竿子一条索,索比竿子长一托.折回索子却量竿,却比竿子短一托.“其大意为:现有一根竿和一条绳索,用绳索去量竿,绳索比竿长5尺;如果将绳索对半折后再去量竿,就比竿短5尺.设绳索长x尺,竿长y尺,则符合题意的方程组是( )A .5152x y x y =+⎧⎪⎨=-⎪⎩B .5152x y x y =-⎧⎪⎨=+⎪⎩C .525x y x y =+⎧⎨=-⎩D .525x y x y =-⎧⎨=+⎩2.如图,射线OC 的端点O 在直线AB 上,∠AOC 的度数比∠BOC 的2倍多10度.设∠AOC 和∠BOC 的度数分别为x ,y ,则下列正确的方程组为( )A .18010x y x y +=⎧⎨=+⎩B .180210x y x y +=⎧⎨=+⎩C .180102x y x y +=⎧⎨=-⎩D .180210x y y x +=⎧⎨=-⎩3.甲、乙两人骑自行车同时从相距65 km 的两地相向而行,2 h 相遇,若甲比乙每小时多骑2.5 km ,则乙的速度是每小时( )A .12.5 kmB .15 kmC .17.5 kmD .20 km4.“阅读与人文滋养内心”,重庆一中初二年级正掀起一股阅读《红星照耀中国》的浪潮.小明4天里阅读的总页数比小颖5天里阅读的总页数少100页,小颖平均每天阅读的页数比小明平均每天阅读的页数的2倍少10页.若小明、小颖平均每天分别阅读x 页、y 页,则下列方程组正确的是( )A .41005210x y y x -=⎧⎨=-⎩B .41005210x y y x +=⎧⎨=+⎩C .45100210x y y x =-⎧⎨=-⎩D .45100210x y y x =+⎧⎨=+⎩5.某文具店一本练习本和一支中性笔的单价合计为3元,小妮在该店买了20本练习本和10支中性笔,共花了40元.若设练习本每本为x 元,中性笔每支为y 元,则下面所列方程组正确的是( )A .3201040x y x y -=⎧⎨+=⎩B .3201040x y x y +=⎧⎨+=⎩C .3201040y x x y -=⎧⎨+=⎩D .3102040x y x y +=⎧⎨+=⎩6.我国古代数学名著《孙子算经》中记载了一道题,大意是:100匹马恰好拉了100片瓦,已知1匹大马能拉3片瓦,3匹小马能拉1片瓦,问有多少匹大马、多少匹小马?若设大马有x匹,小马有y匹,则可列方程组为( )A.100131003x yx y+=⎧⎪⎨+=⎪⎩B.100131003x yx y+=⎧⎪⎨+=⎪⎩C.1003100x yx y+=⎧⎨+=⎩D.1003100x yx y+=⎧⎨+=⎩7.我国明代数学读本《算法统宗》一书中有这样一道题:一支竿子一条索,索比竿子长一托,对折索子来量竿,却比竿子短一托,如果一托为5尺,那么索长( )尺.A.25 B.20 C.15 D.108.元宵节又称灯节,我国各地都有挂灯笼的习俗.灯笼又分为宫灯,纱灯等.若购买1个宫灯和1个纱灯共需75元,小田用690元购买了6个同样的宫灯和10个纱灯.若根据题意可得二元一次方程组75610690x yx y+=⎧⎨+=⎩,则方程组中,x y分别表示为( )A.每个宫灯的价格,每个纱灯的价格B.每个纱灯的价格,每个宫灯的价格C.宫灯的数量,纱灯的数量D.纱灯的数量,宫灯的数量9.某中学现有学生500人,计划一年后女生在校人数增加3%,男生在校人数增加4%,这样,在校学生总数将增加3.4%.问该校现有女生和男生的人数分别是( )A.女生180和男生320 B.女生320和男生180C.女生200和男生300 D.女生300和男生20010.某超市为促销,决定对A,B两种商品进行打折出售.打折前,买6件A商品和3件B商品需要54元,买3件A商品和4件B商品需要32元.打折后,买50件A商品和40件B商品仅需364元,则比打折前少花( )A.56元B.116元C.420元D.480元11.甲乙丙三人做一项工作,三人每天的工作效率分别为a、b、c,若甲乙一天工作量和是丙2天的工作量,乙丙一天的工作量和是甲5天的工作量,下列结论正确的是( )A.甲的工作效率最高B.丙的工作效率最高C.c=3a D.b:c=3:2 12.把一张50元的人民币换成10元或5元的人民币,共有()A.4种换法B.5种换法C.6种换法D.7种换法13.现有如图(1)的小长方形纸片若干块,已知小长方形的长为a,宽为b.用3个如图(2)的全等图形和8个如图(1)的小长方形,拼成如图(3)的大长方形,若大长方形的宽为30cm,则图(3)中阴影部分面积与整个图形的面积之比为( )A.15B.16C.17D.1814.已知、、A B C三地顺次在同-直线上,甲、乙两人均骑车从A地出发,向C地匀速行驶.甲比乙早出发5分钟;甲到达B地并休息了2分钟后,乙追上了甲.甲、乙同时从B地以各自原速继续向C地行驶.当乙到达C地后,乙立即掉头并提速为原速的54倍按原路返回A地,而甲也立即提速为原速的二倍继续向C地行驶,到达C地就停止.若甲、乙间的距离y(米)与甲出发的时间t(分)之间的函数关系如图所示,则下列说法错误的是( )A.甲、乙提速前的速度分别为300米/分、400米/分.B.A C、两地相距7200米C.甲从A地到C地共用时26分钟 D.当甲到达C地时,乙距A地6075米三、解答题1.学校开展了以感恩为主题的有奖征文活动,并为获奖的同学颁发奖品.小红与小明去文化商店购买甲、乙两种笔记本作为奖品.若买甲种笔记本20个,乙种笔记本10个,共用110元;且买甲种笔记本30个比买乙种笔记本20个少花10元.求甲、乙两种笔记本的单价各是多少元?2.课间活动时,小英、小丽和小华在操场上一起玩投沙包游戏,沙包投到A区域所得分值与投到B区域所得分值不同,当每人各投沙包四次时,其落点和四次总分如图所示.小英小丽小华总分:34分总分:32分总分:?(1)请求出小华的四次总分;(2)如果小明在看完她们三个的投掷后也加入了这个游戏,并且最终赢得了胜利,请你说出小明投沙包的结果和所得分数.3.我国古代算书《四元玉鉴》记载“二果问价”问题:“九百九十九文钱,甜果苦果买一千;甜果九个十一文,苦果七个四文钱.试问甜苦果几个,又问各该几个钱?”其大意是:“现有九百九十九文钱,共买甜果和苦果一千个;九个甜果十一文钱,七个苦果四文钱.请问甜果和苦果各买多少个,各花多少文钱?”(1)每个甜果文钱,每个苦果文钱.(2)求甜果和苦果各买多少个,各花多少文钱?4.某家商店进行装修,若请甲、乙两个装修组同时施工,8天可以完成,需付两组费用共3520元,若先请甲组单独做6天,再请乙单独做12天可以完成,需付费用3480元.(1)甲、乙两组工作一天,商店各应付多少钱?(2)已知甲组单独完成需12天,乙组单独完成需24天,单独请哪个组,商店所付费用较少?(3)在(2)的条件下,现有三种施工方案:①单独请甲组装修;②单独请乙组装修;③请甲、乙两组合做.若装修过程中,商店不但要支付装修费用,而且每天因装修损失收入200元,你认为如何安排施工更有利于商店?请你帮助商店决策.(可用(1)(2)问的条件及结论)5.某运动品牌对第一季度甲、乙两款运动鞋的销售情况进行统计,两款运动鞋的销售量及总销售额如图所示,已知一月份乙款运动鞋的销售量是甲款的35,第一季度这两款运动鞋的销售单价保持不变(销售额=销售单价×销售量)(1)求一月份乙款运动鞋的销售量.(2)求两款运动鞋的销售单价(单位:元)(3)请补全两个统计图.(4)结合第一季度的销售情况,请你对这两款运动鞋的进货,销售等方面提出一条建议.6.小明家需要用钢管做防盗窗,按设计要求,其中需要长为0.8米的钢管100根,还需要长为2.5米的钢管32根,两种长度的钢管粗细必须相同;并要求这些用料不能是焊接而成的.经市场调查,钢材市场中符合这种规格的钢管每根长均为6米.(1)试问:把一根长为6米的钢管进行裁剪,有下面几种方法,请完成填空(余料作废).方法①:只裁成为0.8米的用料时,最多可裁7根;方法②:先裁下1根2.5米长的用料,余下部分最多能裁成为0.8米长的用料根;方法③:先裁下2根2.5米长的用料,余下部分最多能裁成为0.8米长的用料1 根.(2)分别用(1)中的方法②和方法③各裁剪多少根6米长的钢管,才能刚好得到所需要的相应数量的材料;(3)试探究:除(2)中方案外,在(1)中还有哪两种方法联合,所需要6米长的钢管与(2)中根数相同.7.学习整式乘法时,老师拿出三种型号的卡片,如图1:A型卡片是边长为a的正方形,B型卡片是边长为b的正方形,C型卡片是长和宽分别为a,b的长方形。

计算机组成原理习题课2

10. 32位字长的浮点数,其中阶码8位(含1位阶符),尾数24位(含 1位数符),则其对应的最大正数为 ① ,最小负数为 ② ,最小 的绝对值为 ③ ;若机器数采用补码表示,且尾数为规格化形式, 则对应的最大正数为 ④ ,最小正数为 ⑤ ,最小负数为 ⑥ 。

A.2127(1-2-23) D.-2+127 B.-2127(1-2-23) E. 2-128×2-23 C. 2-129 F. 2-127×2-23

41.小数(0. 65625)十 等于_______。 A.(0. 11101)二 B.(0. 10101)二 C.(0. 00101)二 D.(0. 10111)二 答案:B 42. (84)十 等于______。 A.(10100100)二 B.(224)八 C.(054)十六 D.(1210)四 答案:C 44 二进制数11001011 等于十进制的_____。 A.395 B.203 C.204 D.394 答案:B 47. (20.8125)十 = ( ________ ) 二 。 A. 1010.1101 B. 10100.1011 C. 10100.1101 D.1010.1011 答案:C 48.补码10110110代表的是十进制负数____。 A. -74 B. -54 C. -68 D. -48 答案:A

9. 用n+1位字长表示定点数(其中1位为符号位),它所能表示的 整数范围是 ① ,它所能表示的小数范围是 ② 。

A.0≤ |N| ≤ 2n-l

C. 0≤ |N| ≤ 1- 2-(n+l) ②D 答案: ① A

B. 0≤ |N| ≤ 2n+1 -l

D. 0≤ |N| ≤ 1-2-n (此处为真值表示)

C. -263 ~ 263(1-2-9)

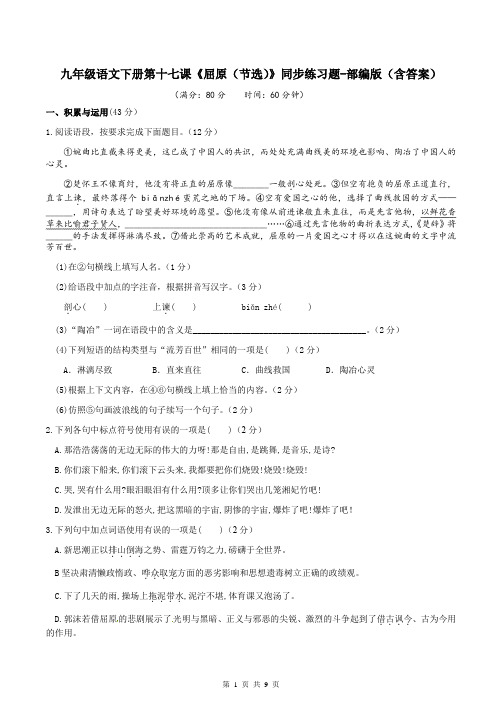

九年级语文下册第十七课《屈原(节选)》同步练习题-部编版(含答案)

九年级语文下册第十七课《屈原(节选)》同步练习题-部编版(含答案)(满分:80分时间:60分钟)一、积累与运用(43分)1.阅读语段,按要求完成下面题目。

(12分)①婉曲比直截来得更美,这已成了中国人的共识,而处处充满曲线美的环境也影响、陶冶了中国人的心灵。

②楚怀王不像商纣,他没有将正直的屈原像________一般剖.心处死。

③但空有抱负的屈原正道直行,直言上谏.,最终落得个biǎnzhé蛮荒之地的下场。

④空有爱国之心的他,选择了曲线救国的方式——______,用诗句表达了盼望美好环境的愿望。

⑤他没有像从前进谏般直来直往,而是先言他物,以鲜花香草来比喻君子贤人,________________________________……⑥通过先言他物的曲折表达方式,《楚辞》将______的手法发挥得淋漓尽致。

⑦借此崇高的艺术成就,屈原的一片爱国之心才得以在这婉曲的文字中流芳百世。

(1)在②句横线上填写人名。

(1分)(2)给语段中加点的字注音,根据拼音写汉字。

(3分)剖.心( ) 上谏.( ) biǎn zhé( )(3)“陶冶”一词在语段中的含义是_______________________________________。

(2分)(4)下列短语的结构类型与“流芳百世”相同的一项是( )(2分)A.淋漓尽致B.直来直往C.曲线救国 D.陶冶心灵(5)根据上下文内容,在④⑥句横线上填上恰当的内容。

(2分)(6)仿照⑤句画波浪线的句子续写一个句子。

(2分)2.下列各句中标点符号使用有误的一项是( )(2分)A.那浩浩荡荡的无边无际的伟大的力呀!那是自由,是跳舞,是音乐,是诗?B.你们滚下船来,你们滚下云头来,我都要把你们烧毁!烧毁!烧毁!C.哭,哭有什么用?眼泪眼泪有什么用?顶多让你们哭出几笼湘妃竹吧!D.发泄出无边无际的怒火,把这黑暗的宇宙,阴惨的宇宙,爆炸了吧!爆炸了吧!3.下列句中加点词语使用有误的一项是( )(2分)A.新思潮正以排山倒海....之势、雷霆万钧之力,磅礴于全世界。

《习题课》教案

名句名篇默写竞赛

参加者

高一部分学生

活动时间

5.14—5.18

指导思想

中华古诗文是我国历史长河中一颗璀璨的明珠,学习健康向上的古诗文,不仅能够增进个人的文学素养,更有利于提升人的思想品格的境界。

活动目的

近年来,高考加大了对过诗文的考查力度,增加了难度和分值。而一些学生还缺乏对古诗文学习的兴趣,忽视了对名句名篇背诵默写能力的培养,再考试时失分较为严重。为了激发学生学习中华古诗文的兴趣,提升学生古诗文名句名篇的默写能力,提高语文学科的成绩,同时,为了强化任课教师对学生名句名篇默写的督促力度,特举办高一学生名句名篇默写大赛。

名句名篇默写活动案

高一语文组

②同学自己背诵。

③同学互背。

④教师试出名句,学生填写,强调字形。

⑤教师反复训练学生,进行巩固,达到一定的熟练程度。

活动总结

此次比赛为期一周,教导处领导及高一语文组教师认真布置,精心选题、仔细批阅,使高一全体学生对教材所选的名句名篇加深了理解与识记。本次比赛试题形式多样,有按照“描写山水”、“歌颂友谊”、“边塞生活”、“科学哲理”、“爱国篇章”、“友人送别”等分类的诗句填空;有古诗文名句的上下文填写;有根据提供的语言环境进行古诗文的运用考查,有借用古人的诗句来描写指定的事物。通过比赛不仅能够增进学生的文学素养,更有利于提升学生的思想品格的境界,达到了预期效果。

活动反思

本次活动取得了较好的效果,高一全体学生积极参加,比赛前充分准备,比赛时认真答题,比赛后及时总结教训。确实在高一年级组掀起了读背名句名篇的大潮,激发了学生阅读中华好诗词的兴趣。

在此次比赛中我们发现学生失误较多,其原因主要有两方面:

(1)字词写错:这类现象是默写失活动过程

《结构分析中的有限元法》2015-有限元习题-参考答案

4、列表给出有限元几类基本单元的图形、结点数、结点自由度数和单元总自由 度数(包括杆单元、梁单元、平面三角形单元、平面四边形单元、轴对称问题三 角形单元、四边形壳单元、四面体单元)。

单元 类型 杆单

(1)单元的类型和形式 为了扩大有限元法的应用领域,新的单元类型和形式不断涌现(等参元,梁板 壳,复合材料) (2)有限元法的理论基础和离散格式 将 Hellinger-Reissner、Hu—Washizu(多场变量变分原理)应用于有限元分析, 发展了混合模型、杂交型的有限元表达格式,应研究了各自的收敛条件;将加权 余量法用于建立有限元的表达格式;进一步研究发展有限元解的后验误差估计和 应力磨平方法。 (3)有限元方程的解法(大型复杂工程结构问题——静态, 特征值, 瞬态等) (4)有限元法的计算机软件(专用软件, 通用软件)

弹性力学中的虚功原理可表达为:在外力作用下处于平衡状态的弹性体,如

果发生了虚位移,那么所有的外力在虚位移上的虚功(外力功)等于整个弹性体内

应力在虚应变上的虚功(内力功)。

根据虚功原理得到 ( εT uT F )d uTTd 0

p

(1 T uT F)d 2

uT

Td

0

其中的 p 即为总势能泛函。由上面变分为零式表明:在所有区域内满足几 何关系,在边界上满足给定位移条件的可能位移中,真实位移使系统的总势能取 驻值(可证明此驻值为最小值)。此即总势能泛函的极值条件。

10, 0

3 2, 0

解:根据拉格朗日插值基函数:

u(x, y) l1(x, y)u1 l2 (x, y)u2 l3(x, y)u3 l4 (x, y)u4

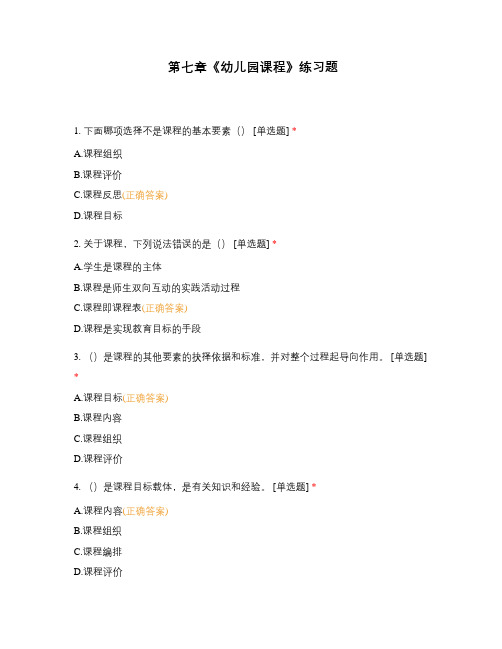

第七章《幼儿园课程》练习题

第七章《幼儿园课程》练习题1. 下面哪项选择不是课程的基本要素() [单选题] *A.课程组织B.课程评价C.课程反思(正确答案)D.课程目标2. 关于课程,下列说法错误的是() [单选题] *A.学生是课程的主体B.课程是师生双向互动的实践活动过程C.课程即课程表(正确答案)D.课程是实现教育目标的手段3. ()是课程的其他要素的抉择依据和标准,并对整个过程起导向作用。

[单选题] *A.课程目标(正确答案)B.课程内容C.课程组织D.课程评价4. ()是课程目标载体,是有关知识和经验。

[单选题] *A.课程内容(正确答案)B.课程组织C.课程编排D.课程评价5. 幼儿园课程以()基础,让幼儿获得直接经验为主。

[单选题] *A.教师讲授B.幼儿自学C.幼儿的间接经验D.幼儿的直接经验(正确答案)6. 课程的基本要素是() [单选题] *A.课程目标课程内容课程形式B.课程内容课程要素课程评价C课程目标课程内容课程组织课程评价(正确答案)D.课程方法课程内容课程组织课程评价7. 幼儿园阶段主要是打基础,特别是为()打基础。

[单选题] *A.小学教育(正确答案)B.初中教育C.高中教育D.成人教育8. ()是为整个人生打根基。

[单选题] *A.幼儿阶段(正确答案)B.儿童阶段C.婴儿阶段D.青年阶段9. 幼儿看电视的时间越长,获得()经验的机会越少。

[单选题] *A.直接经验(正确答案)B.间接经验C.内部经验D.和新阶段10. 下列关于幼儿园课程性质的说法不正确的是() [单选题] *A.幼儿园课是终身教育的根基课程B.幼儿园课程是基础素质教育课程C.幼儿园课程是基础教育的根基部分D.幼儿园课程是义务教育课程(正确答案)11. 关于“幼儿园课程是基础教育课程的基础部分”说法不正确的是() [单选题] *A.我国的基础教育由幼儿园教育、小学教育、初中教育、高中教育,这四个联系的阶段构成(正确答案)B.幼小衔接工作应由幼儿园和小学共同完成C.幼儿园教育和小学教育都必须站在整个基础教育甚至终生D.以上说法均不对12. 幼儿园课程是非义务教育教育课程,理解错误的是() [单选题] *A.幼儿园课程不是义务教育课程,不是免费的B.幼师在幼儿园中不需要强迫幼儿学习C.幼儿园课程不可留作业,进行考试或对因故未上幼儿园的幼儿进行补习D.幼儿园课程是非强制的,教师对孩子的和谐发展没有教育、引导和促进责任(正确答案)13. 幼儿园课程实施的基本形式是() [单选题] *A.游戏(正确答案)B.生活C.上课D.专门组织的教学活动14. 幼儿园课程以促使幼儿获得对生活环境的()为主要目的幼儿园课程中,幼儿学习的主要是来源于生活环境的。

部编版四年级上册语文第十八课《牛和鹅》课文原文及练习题

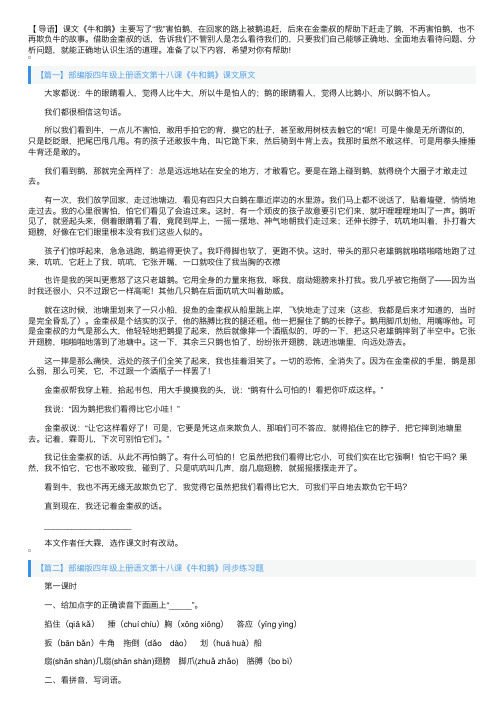

【导语】课⽂《⽜和鹅》主要写了“我”害怕鹅,在回家的路上被鹅追赶,后来在⾦奎叔的帮助下赶⾛了鹅,不再害怕鹅,也不再欺负⽜的故事。

借助⾦奎叔的话,告诉我们不管别⼈是怎么看待我们的,只要我们⾃⼰能够正确地、全⾯地去看待问题、分析问题,就能正确地认识⽣活的道理。

准备了以下内容,希望对你有帮助!【篇⼀】部编版四年级上册语⽂第⼗⼋课《⽜和鹅》课⽂原⽂ ⼤家都说:⽜的眼睛看⼈,觉得⼈⽐⽜⼤,所以⽜是怕⼈的;鹅的眼睛看⼈,觉得⼈⽐鹅⼩,所以鹅不怕⼈。

我们都很相信这句话。

所以我们看到⽜,⼀点⼉不害怕,敢⽤⼿拍它的背,摸它的肚⼦,甚⾄敢⽤树枝去触它的*呢!可是⽜像是⽆所谓似的,只是眨眨眼,把尾巴甩⼏甩。

有的孩⼦还敢扳⽜⾓,叫它跪下来,然后骑到⽜背上去。

我那时虽然不敢这样,可是⽤拳头捶捶⽜背还是敢的。

我们看到鹅,那就完全两样了:总是远远地站在安全的地⽅,才敢看它。

要是在路上碰到鹅,就得绕个⼤圈⼦才敢⾛过去。

有⼀次,我们放学回家,⾛过池塘边,看见有四只⼤⽩鹅在靠近岸边的⽔⾥游。

我们马上都不说话了,贴着墙壁,悄悄地⾛过去。

我的⼼⾥很害怕,怕它们看见了会追过来。

这时,有⼀个顽⽪的孩⼦故意要引它们来,就吁哩哩哩地叫了⼀声。

鹅听见了,就竖起头来,侧着眼睛看了看,竟爬到岸上,⼀摇⼀摆地、神⽓地朝我们⾛过来;还伸长脖⼦,吭吭地叫着,扑打着⼤翅膀,好像在它们眼⾥根本没有我们这些⼈似的。

孩⼦们惊呼起来,急急逃跑,鹅追得更快了。

我吓得脚也软了,更跑不快。

这时,带头的那只⽼雄鹅就啪嗒啪嗒地跑了过来,吭吭,它赶上了我,吭吭,它张开嘴,⼀⼝就咬住了我当胸的⾐襟 也许是我的哭叫更惹怒了这只⽼雄鹅。

它⽤全⾝的⼒量来拖我,啄我,扇动翅膀来扑打我。

我⼏乎被它拖倒了——因为当时我还很⼩,只不过跟它⼀样⾼呢!其他⼏只鹅在后⾯吭吭⼤叫着助威。

就在这时候,池塘⾥划来了⼀只⼩船,捉鱼的⾦奎叔从船⾥跳上岸,飞快地⾛了过来(这些,我都是后来才知道的,当时是完全昏乱了)。

《幼儿园课程》练习题(含答案)

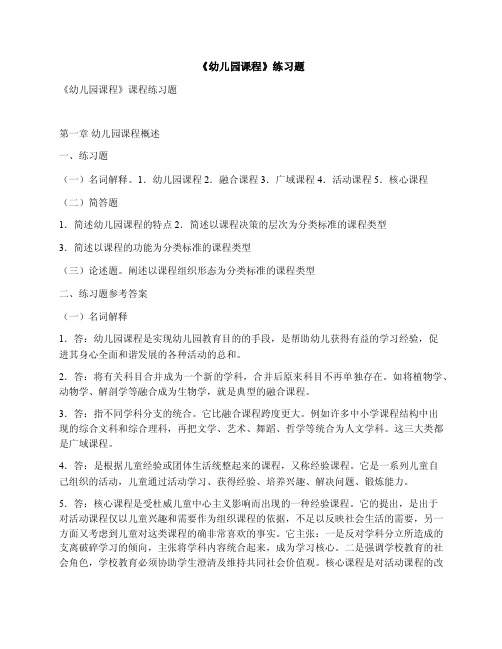

《幼儿园课程》练习题《幼儿园课程》课程练习题第一章幼儿园课程概述一、练习题(一)名词解释。

1.幼儿园课程 2.融合课程 3.广域课程 4.活动课程 5.核心课程(二)简答题1.简述幼儿园课程的特点 2.简述以课程决策的层次为分类标准的课程类型3.简述以课程的功能为分类标准的课程类型(三)论述题。

阐述以课程组织形态为分类标准的课程类型二、练习题参考答案(一)名词解释1.答:幼儿园课程是实现幼儿园教育目的的手段,是帮助幼儿获得有益的学习经验,促进其身心全面和谐发展的各种活动的总和。

2.答:将有关科目合并成为一个新的学科,合并后原来科目不再单独存在。

如将植物学、动物学、解剖学等融合成为生物学,就是典型的融合课程。

3.答:指不同学科分支的统合。

它比融合课程跨度更大。

例如许多中小学课程结构中出现的综合文科和综合理科,再把文学、艺术、舞蹈、哲学等统合为人文学科。

这三大类都是广域课程。

4.答:是根据儿童经验或团体生活统整起来的课程,又称经验课程。

它是一系列儿童自己组织的活动,儿童通过活动学习、获得经验、培养兴趣、解决问题、锻炼能力。

5.答:核心课程是受杜威儿童中心主义影响而出现的一种经验课程。

它的提出,是出于对活动课程仅以儿童兴趣和需要作为组织课程的依据,不足以反映社会生活的需要,另一方面又考虑到儿童对这类课程的确非常喜欢的事实。

它主张:一是反对学科分立所造成的支离破碎学习的倾向,主张将学科内容统合起来,成为学习核心。

二是强调学校教育的社会角色,学校教育必须协助学生澄清及维持共同社会价值观。

核心课程是对活动课程的改造,它努力达到以社会功能和社会问题为核心的学科内容的统合,属于社会本位的课程类型。

(二)简答题1.答:幼儿园课程特点(在以下基础上做简要阐述);(1)幼儿园课程的基础性、启蒙性;(2)幼儿园课程的全面性、生活性;(3)幼儿园课程的整合性;(4)幼儿园课程的活动性与直接经验性;(5)幼儿园课程的潜在性2.答:美国学者古德莱德提出以课程决策的层次为标准把课程分为五种类型。

《幼儿园课程》练习题库参考答案

《幼儿园课程》练习题库参考答案一、选择题1.幼儿园课程的核心目标是(B)A.提升幼儿的智力水平B.促进幼儿全面发展C.培养幼儿的艺术才能D.提高幼儿的社交能力答案:BA.教育活动B.游戏活动C.生活活动D.家庭作业答案:DA.系统性原则B.发展性原则C.主体性原则D.实践性原则答案:CA.幼儿的学习成绩B.幼儿的全面发展C.教师的授课水平D.家长的满意度答案:BA.课堂教学B.游戏活动C.主题活动D.学生竞赛答案:D二、填空题1.幼儿园课程的目标体系包括三个方面:认知目标、情感目标、________目标。

答案:行为目标答案:发展性原则3.幼儿园课程的评价方法包括:观察法、________法、问卷调查法、访谈法。

答案:作品分析法4.幼儿园课程的实施途径有:集体教学、________活动、个别辅导、家庭教育。

答案:小组活动5.幼儿园课程的管理包括:课程计划的制定、________、课程评价。

答案:课程实施三、判断题1.幼儿园课程应以教师为主导,幼儿为辅助。

(×)2.幼儿园课程的评价应注重幼儿的个体差异。

(√)3.幼儿园课程的内容应包括五大领域:健康、语言、社会、科学、艺术。

(√)4.幼儿园课程的实施过程中,教师应注重幼儿的自主学习。

(√)5.幼儿园课程的评价应以幼儿的学习成绩为主要依据。

(×)四、简答题1.请简述幼儿园课程的基本特点。

答案:幼儿园课程的基本特点包括:适宜性、生活化、活动性、游戏性、综合性、发展性。

2.请简述幼儿园课程评价的原则。

答案:幼儿园课程评价的原则包括:客观性原则、全面性原则、发展性原则、导向性原则、动态性原则。

3.请简述幼儿园课程实施的基本途径。

答案:幼儿园课程实施的基本途径包括:集体教学、小组活动、个别辅导、家庭教育。

4.请简述幼儿园课程内容的选择原则。

答案:幼儿园课程内容的选择原则包括:适宜性原则、发展性原则、全面性原则、生活化原则。

5.请简述幼儿园课程目标的作用。

部编版语文八年级上册第22课 《孟子三章》习题课件(共54张幻灯片)

第22课 《孟子三章》

知识导航

(3)域民不以封疆之界,固国不以山溪之险,威天 下不以兵革之利。 _使__人__民__定__居__下__来__(_而__不__迁__到__别__的__地__方__去__)_,__不__能__靠____ _疆__域__的__边__界__;__巩__固__国__防__不__能__靠__山__河__的__险__要__;__震__慑____ _天__下__不__能__靠__武__器__的__锋__利__。________________________ (4)得道者多助,失道者寡助。 _能__够__施__行__治__国__的__正__道__的__君__主__,__帮__助__他__的__人__很__多__;__不__ _能__够__施__行__治__国__的__正__道__的__君__主__,__帮__助__他__的__人__很__少__。____

第22课 《孟子三章》

知识导航

女子之嫁也,母命之, 往送之门,戒.①( 警告。)之 曰:‘往之女. ( 同“汝”,你。 )家,必敬必戒. ② ( 谨慎。),无违夫子!’以顺为正. ( 准则,标准。) 者,妾妇之道也。居天下之广. 居. ( 仁。),立天下之 正. 位. ( 礼。),行天下之大.道.( 义。)。得志,与民 由. ( 遵从。)之;不得. ( 实现。)志,独行其道。富

第六单元

第22课 《孟子三章》

第22课 《孟子三章》

第22课 《孟子三章》

1

知识导航 ……………

2

课外赏读 ……………

3

新题专列 ……………

第22课 《孟子三章》

知识导航

【字音字形】

衍. (yǎn) 傅说. (yuè) 曾. 益(zēng)

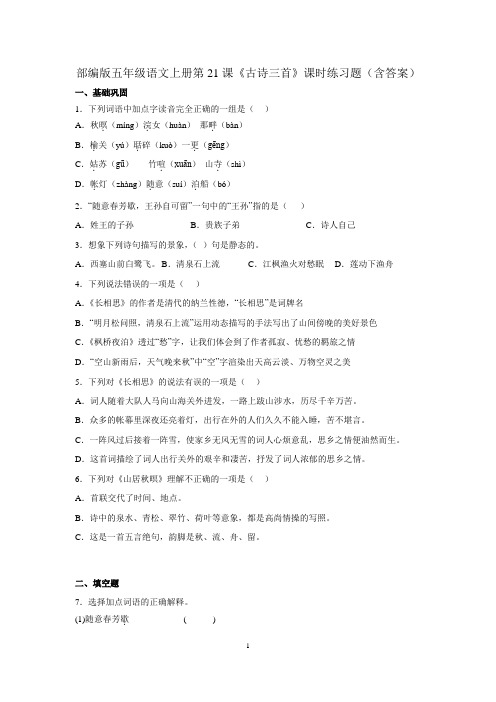

部编版五年级语文上册第21课《古诗三首》课时练习题(含答案)

部编版五年级语文上册第21课《古诗三首》课时练习题(含答案)一、基础巩固1.下列词语中加点字读音完全正确的一组是()A.秋暝.(míng)浣.女(huàn)那畔.(bàn)B.榆.关(yú)聒.碎(kuò)一更.(gēng)C.姑.苏(gū)竹喧.(xuān)山寺.(shì)D.帐.灯(zhàng)随.意(suí)泊.船(bó)2.“随意春芳歇,王孙自可留”一句中的“王孙”指的是()A.姓王的子孙B.贵族子弟C.诗人自己3.想象下列诗句描写的景象,()句是静态的。

A.西塞山前白鹭飞。

B.清泉石上流C.江枫渔火对愁眠D.莲动下渔舟4.下列说法错误的一项是()A.《长相思》的作者是清代的纳兰性德,“长相思”是词牌名B.“明月松问照,清泉石上流”运用动态描写的手法写出了山间傍晚的美好景色C.《枫桥夜泊》透过“愁”字,让我们体会到了作者孤寂、忧愁的羁旅之情D.“空山新雨后,天气晚来秋”中“空”字渲染出天高云淡、万物空灵之美5.下列对《长相思》的说法有误的一项是()A.词人随着大队人马向山海关外进发,一路上跋山涉水,历尽千辛万苦。

B.众多的帐幕里深夜还亮着灯,出行在外的人们久久不能入睡,苦不堪言。

C.一阵风过后接着一阵雪,使家乡无风无雪的词人心烦意乱,思乡之情便油然而生。

D.这首词描绘了词人出行关外的艰辛和凄苦,抒发了词人浓郁的思乡之情。

6.下列对《山居秋暝》理解不正确的一项是()A.首联交代了时间、地点。

B.诗中的泉水、青松、翠竹、荷叶等意象,都是高尚情操的写照。

C.这是一首五言绝句,韵脚是秋、流、舟、留。

二、填空题7.选择加点词语的正确解释。

(1)随意春芳歇. ( )①停止②休息③尽(2)故园..无此声( )①故乡②祖国(3)风一更,雪一更. ( )①改变②旧时夜间的计时单位,一夜为五更③经历8.古诗词理解山居秋暝①[唐]王维空山新雨后,天气晚来秋。

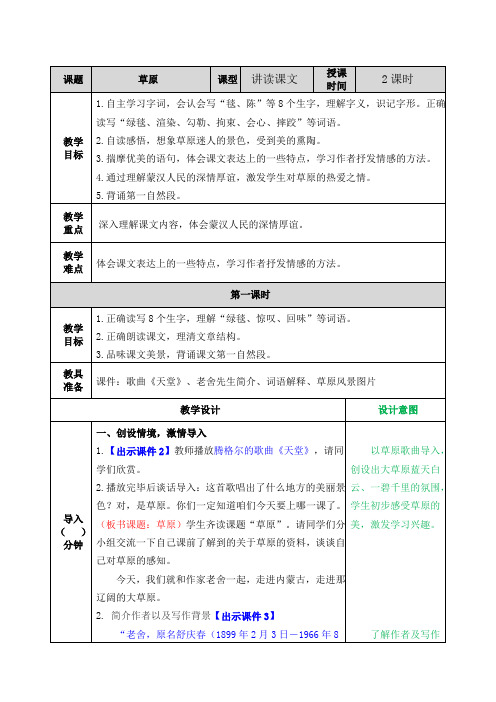

部编版六年级语文上册一单元第1课《草原》教案+课后习题附答案

备课素材【教材分析】这篇散文,字里行间浸润着浓郁的草原风情:那一碧千里的草原风光,那欢迎远客、盛情款待、深情话别的动人情景,都令人难以忘怀。

本文是作者第一次访问内蒙古大草原时的所见、所闻、所感,并通过这些所见、所闻、所感,赞美了草原的美丽风光和民族之间的团结。

本文层次井然,作者按照事情的发展顺序叙述,先描写草原秀美的景色,再描写草原迎客场面和草原联欢的情形。

作者移步换景,由景及人,最后以简明有力、含义丰富的诗句结束。

全文安排有序,脉络清楚,衔接紧密,推进自然。

课文写景语言优美,善于运用比喻和拟人的写法,不但形似而且神似,生动贴切,同时又不失纯朴简练,生动感人。

三是情景交融,无论是描写自然风光还是主客相见、联欢、惜别,处处流露出作者的赞美之情。

【作者介绍】舒庆春(1899年2月3日-1966年8月24日),字舍予,笔名老舍,满族正红旗人,本名舒庆春,生于北京,中国现代小说家、著名作家,杰出的语言大师、人民艺术家,新中国第一位获得“人民艺术家”称号的作家。

著有长篇小说《小坡的生日》《猫城记》《牛天赐传》《骆驼祥子》等,短篇小说《赶集》等。

老舍的文学语言通俗简易,朴实无华,幽默诙谐,具有较强的北京韵味。

1966年8月24日,中国作家老舍因不堪忍受红卫兵的暴力批斗,在北京太平湖投湖自尽。

1978年初,老舍得到平反,恢复了“人民艺术家”的称号。

【与文章相关的资料介绍】奶茶:奶茶原为中国北方游牧民族的日常饮品,至今最少已有千年历史。

自元朝起传遍世界各地,目前在中国、印度、阿拉伯、英国、马来西亚、新加坡等地区都有不同种类奶茶流行。

中国境内的的维吾尔族、乌孜别克族、哈萨克族、柯尔克孜族、藏族和蒙古族等均有制作奶茶的习惯。

新疆奶茶的原料是茶和牛奶或羊奶。

乌孜别克族烧奶茶一般用铜壶或铝锅,先将茶水煮沸,然后加入牛奶烧煮,搅匀,待茶乳完全交融后,再加适量的食盐即成。

饮时把奶茶盛入碗中,稍加酥油或羊油、胡椒即可。

藏族、蒙古族的奶茶以砖茶、羊奶或牛奶、和以酥油煮成,加盐调理使味道偏咸。

高中数学选择性必修一(人教版)《习题课 直线与圆》课件

化简得 7x+y+22=0.

高频考点三圆的方程 [例 3] 在平面直角坐标系中,已知△ABC 的三个顶点的坐 标分别为 A(-3,0),B(2,0),C(0,-4),经过这三个点的圆记为 M. (1)求 BC 边的中线 AD 所在直线的一般式方程; (2)求圆 M 的方程.

[解] (1)法一:由 B(2,0),C(0,-4),知 BC 的中点 D 的 坐标为(1,-2).

[集训冲关]

1.直线 ax+2y-1=0 与直线 2x-3y-1=0 垂直,则 a 的值为

()

A.-3

B.-43

C.2

D.3

解析:由 2a-6=0 得 a=3.故选 D. 答案:D

2.已知直线 x+2ay-1=0 与直线(a-1)x+ay+1=0 平行,则

a 的值为

()

A.32

B.32或 0

C.0

又 A(-3,0),所以直线 AD 的方程为-y-2-00=x1++33, 即中线 AD 所在直线的一般式方程为 x+2y+3=0. 法二:由题意,得|AB|=|AC|=5, 则△ABC 是等腰三角形, 所以 AD⊥BC. 因为直线 BC 的斜率 kBC=2, 所以直线 AD 的斜率 kAD=-12, 由直线的点斜式方程,得 y-0=-12(x+3), 所以直线 AD 的一般式方程为 x+2y+3=0.

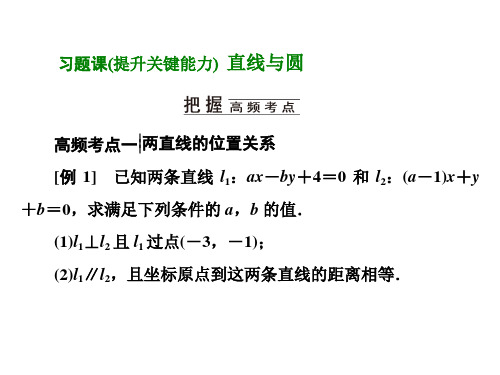

习题课提升关键能力 直线与圆

高频考点一两直线的位置关系 [例 1] 已知两条直线 l1:ax-by+4=0 和 l2:(a-1)x+y +b=0,求满足下列条件的 a,b 的值. (1)l1⊥l2 且 l1 过点(-3,-1); (2)l1∥l2,且坐标原点到这两条直线的距离相等.

[解] (1)∵l1⊥l2,

(2)因为直线 l∥OA,所以直线 l 的斜率为42--00=2. 设直线 l 的方程为 y=2x+m,即 2x-y+m=0,则圆心 M 到直 线 l 的距离 d=|2×6-57+m|=|m+55|. 因为 BC=OA= 22+42=2 5, 而 MC2=d2+B2C2, 所以 25=m+5 52+5,解得 m=5 或 m=-15. 故直线 l 的方程为 2x-y+5=0 或 2x-y-15=0.

《计算机组成原理》习题课:判断

同步5.1. 执行指令时,指令在内存中的地址存放在指令寄存器 中。 答案:错。执行指令时,指令在内存中的地址存放在程序计数器 中。 2.没有设置乘、除法指令的计算机系统中,就不能实现乘、除 法运算。 答案:错。在没有设置乘、除法指令的计算机系统中,可通过加、 减、移位等运算实现乘、除法运算。 3.计算机指令是指挥CPU进行操作的命令,指令通常由操作码 和操作数的地址码组成。 答案:对。 4.不设置浮点运算指令的计算机,就不能用于科学计算。 答案:错。不设置浮点运算指令的计算机,仍可用于科学计算, 只是要增加编程量且速度不很快。 5.采用RISC技术后,计算机的体系结构又恢复到早期的比较简 单的情况。 答案:错。RISC计算机的体系结构只是相对CISC机要简单些。 12

3

同步3.1.定点补码运算时,其符号位不参与运算。 答案:错 2.尾数部分只进行乘法和除法运算。 答案:错 3.浮点数的正负由阶码的正负符号决定。 答案:错 4.在定点小数一位除法中,为了避免溢出,被除数的绝对值一定 要小于除数的绝对值。 答案:对 5.浮点运算器的阶码部件可实现加、减、乘、除4种运算。 答案:错。阶码部件只进行阶码相加、相减和比较操作。 6.浮点数的取值范围由阶码的位数决定,而浮点数的精度由尾 数的位数决定。 答案:对。 7.加法器是构成运算器的基本部件,为提高运算速度,运算器 一般都采用串行加法器。 答案:错。加法器是构成运算器的基本部件,为提高运算速度, 4 加法器一般都采用并行加法器。

强化6.1.在主机中,只有内存能存放数据。 答案:错。寄存器也可存放数据。 2.引入微程序机器级,使CPU的硬件电路更为简单, 可以使CPU的指令系统功能更强。 答案:对。 3.微程序技术是今后计算机技术的发展方向。 答案:错。 目前高性能的计算机中普遍采用硬布线技 术。 4.在CPU中,译码器主要用在运算器中挑选多路输入 数据中的某一路数据送到ALU。 答案:错。在CPU中,译码器主要用于指令的译码、 寻址模式的译码及操作数地址的译码。 5.对一个并行寄存器来说,只要时钟脉冲到来,便可 从输出端同时输出各位的数据。 答案:错。时钟脉冲到来,数据便被置入寄存器忆设备,它只是用来存放程序。 答案:错。 存储器是计算机中存放程序和数据的设备。 2.动态RAM和静态RAM都是易失性半导体存储器。 答案:对。 3.CPU访问存储器的时间是由存储器的容量决定的,存储器容 量越大,访问存储器所需的时间越长。 答案:错。CPU访问存储器的时间是基本固定的,与容量无关, 而是由存储元的材料决定的。4.因为半导体存储器加电后才 能存储数据,断电后数据就丢失了,因此EPROM做成的存储器, 加电后必须重写原来的内容。 答案:错。半导体存储器加电后才能存储数据,断电后数据丢失, 这是指RAM。而EPROM是只读存储器,断电后数据不会丢失, 因此,加电后不必重写原来的内容。 5.目前大多数个人计算机中可配置的内存容量仅受地址总线位 数限制。 答案:错。内存容量不仅受地址总线位数限制,还受寻址方式、 5 操作系统的存储管理方式等限制。

组织行为学课程考试习题(含答案)

1、什么是组织?答:组织是对完成特定使命的人的系统性安排.1、是由人组成的集合;2、组织是适应于目标的需要;3、组织通过专业分工和协调来实现目标。

2、组织行为研究的三个层面各包括哪些内容?答:第一:把组织看成是个人的集合:有关人性、需要、动机和激励等方面的理论是用来说明单个组织成员的行为和绩效的。

对诸如价值观、知觉、态度、个性、意志和情感这些因素也予以考虑,并对他们在工作中的个体行为与绩效的影响进行研究。

第二:把重点放在组织成员的小组、群体上,研究其相互作用和相互影响:人们在一起工作的常规方式是小组、部门、委员会这些组织形式。

因此,在组织行为学中,一个可选择的富有成效的方法是分析工作群体的功能,如规范、凝结力、士气、沟通、人际、合作与竞争等. 第三:把组织看成是一个整体来研究:力求理解组织结构和组织设计如何影响组织效率温和氛,如何影响有效沟通和信息传递,认识组织与环境之间的关系及其影响,认识组织变革和发展的规律,从而尽可能提高组织的有效性,改进组织气氛。

1、组织行为学发展过程中产生了哪些主要学说?受到哪些学科发展的影响?答:组织行为学是随着管理的发展而产生和发展的。

(一)古典理论时期(1900—1930 年) ,受管理科学发展的影响; (二)人力资源理论,受心理学研究的影响; (三)权变理论进入管理领域-—组织行为学的形成,受哲学思想发展与社会学发展的影响; (四)组织文化研究的兴起—-组织行为学的深入,行为科学发展的影响。

2 、21 世纪组织行为学面临的挑战有哪些?答:一、经济全球化对组织行为学研究的影响;二、高新科技,特殊是信息技术的发展,对组织行为学研究的影响. (网络化、扁平化、灵便性、多元化、全球化)1、行为研究中的原则?答:1949 年,行为科学命名大会上的四项决定: 1、理论的肯定和证明必须靠公众都能够观察了解的客观事实,不能单凭学者个人的经验;2、尽量使用数理化的方式来说明假设,以便精密地测试和修正;3、尽量使各种论述精确,以便能用严密的试验予以肯定或者否定;4、使用自然科学所惯用的“厘米—克—秒”制作为度量工具。

清华计算机组成原理习题课课件提高题1-6章

2019/6/28

计算机组成原理

18

5.9 基址寄存器的内容为2000H,(H表示十六 进制),变址寄存器的内容为030AH,指令的地 址码为3FH,当前正在执行的指令所在地址为 2B00H,请求出变址值(考虑基址)和相对编址 两种情况下的访存有效地址(实际地址)。

解答:

采用变址方式时,

EA=2000H+030AH+3FH=2349H

6

3.13 设X=2-011×0.110100,Y=2-100×-0.101110。按 下列运算步骤求[X+Y]补 ,其中阶码4位(含1位符号 位),尾数7位(含 1位符号位)。

①求阶差

②对阶 ③尾数运算

④结果规格化

解答:

①阶差△E为1。

②对阶。

Y的阶码小,应使Y的尾数右移1位,阶码加1。此 时X的阶码为11101,尾数为11.101001。

• 4.6 比较静态存储器和动态存储器的存储原 理和特点。

2019/6/28

计算机组成原理

10

• 5.1A 某指令系统指令定长12位,每个地址段3位。 试提出一种分配方案,要求该指令系统有4条三 地址指令,8条二地址指令,180条单地址指令。

第12课《〈论语〉十二章》习题课件-2024-2025学年统编版语文七年级上册(2024)

意愿,不越过法度。

123456

返回目录

(3) 饭疏食,饮水,曲肱而枕之,乐亦在其中矣。 吃粗粮,喝冷水,弯着胳膊当枕头,乐趣也就在其中了。

(4) 博学而笃志,切问而近思,仁在其中矣。 广泛地学习,坚定志向,恳切地发问求教,多思考当前的事情,仁德就

至,然心乡往之。余读孔氏书,想见其为人。适鲁,观仲尼庙堂、车 服、礼器,诸生以时习礼其家,余祗①回留之,不能去云。天下君王至 于贤人众矣,当时则荣,没则已焉。孔子布衣,传十余世,学者宗之。 自天子王侯,中国言六艺②者,折中于夫子,可谓至圣矣!

(节选自《史记·孔子世家》)

一

二

返回目录

[注释] ① 祗:敬。 ② 六艺:儒家的六经,即《诗》《书》 《礼》《乐》《易》《春秋》。

123456

返回目录

(4) 《论语》中,论述复习是学习的重要方法,且对学习者有重要的 意义的句子: 温故而知新 , 可以为师矣 。

(5) 孔子在《述而》篇中论述君子对富贵的正确态度的句子: 不义

而富且贵 , 于我如浮云 。

(6) 唐太宗有一句名言:“以人为鉴,可明得失。”由此我们可以联 想到《论语》中孔子的话: 择其善者而从之 , 其不善者而改之 。

一二ຫໍສະໝຸດ 返回目录4. 阅读甲、乙两文,简要说说学者们敬仰孔子的原因。(4分) 因为孔子传授良好的学习方法,有谦虚的学习态度、宽广的心胸和循循

善诱的教育情怀,所以学者们都很敬仰他。(4分)

一

二

返回目录

二、 [关联点:诚信交友]阅读下面两篇文章,完成题目。(12分) [甲] 《<论语>十二章》(原文略) [乙] 诸葛靓①在吴,于朝堂②大会,孙皓③问:“卿字仲思,为何所

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(3)四路组相联,故Cache共分了512/4 = 128组,所以组地址位 数为:log2128 = 7位 主存字块标记位数为:18-7-2=9位,所以主存地址格式为

主存区块标记 9 组地址 7 字块内地址 2

(4)全相联映射方式下,主存地址格式分为主存字块标记和字块 内地址两部分,主存地址总位数为18位,而字块内地址位数 为2位,所以主存地址格式为

[A]补

+ [– B]补 [A]补 + [– B]补

= 0, 0001111

= 1, 1101000 = 1, 1110111 = [A – B]补 (2分)

因为[A - B]补为负数,所以[A –B]原=[[A - B]补]补=1,0001001, 所以A - B = -9。 (2分)

大连理工大学 软件学院 赖晓晨

主存区块标记 7 区内块号 9 字块内地址 4

四路组相联映射方式下,组地址表示位数依然不变,故主存 块标记的表示位数为: 20–4–7 =9位,主存地址格式为:

主存区块标记 9 组地址 7 字块内地址 4

全相联映射方式下,主存块标记的表示位数为: 20–4 =16 位,主存地址格式为:

主存字块标记 16 字块内地址 4

主存字块标记 16 字块内地址 2

(5)若存储字长为32位,存储器按字节寻址的话,将题中已知条 件用字节表示:主存容量=256k字=28×210×32位 = 220 B, Cache容量为:2k=2×32位= 2×210×32/8 B = 213 B, Cache块长为4个字,即:4字 = 4×32位/8 = 24 B , 所以块内地址可以用4位(2位表示4个字,2位表示每字32), 字块地址位数无论是按字寻址还是字节寻址都不变 直接映射方式下主存字块标记位数为:20–4–9 =7位,主 存地址格式为

4

∴ 0011 的汉明码为 1000011

8.已知接收到的汉明码为 0100111,(按配偶原则 配置)试问要求传送的信息是什么? 解:纠错过程如下

P1= 1 P 2= 2 P 4= 4 3

5 6 6

7 = 0 无错 7 = 1 有错

3

5

7 = 1 有错

∴ P4P2P1 = 110

第 6 位出错,可纠正为 0100101, 故要求传送的信息为 0101

原 码 反 码 1.001 1010 1.110 0101 0.001 1101 0.001 1101 0,110 0100 0,110 0100 1,101 0111 1,010 1000

补 码 1.110 0110 0.001 1101 0,110 0100 1,010 1001

2.将 写成二进制定点数、浮点数及在定点机和浮点机中的 机器数形式。其中数值部分均取 10 位,数符取 1 位,浮点数阶 码取 5 位(含1位阶符)。

解: (1)Cache中可装入数据块:2k/4 = 2×1024 / 4 = 512块。 (2)直接映射方式下的主存地址格式为

主存区块标记 区内块号 字块内地址

Cache一共有512块,故字块地址位数为:log2512 = 9 位 块长为4,故表示块长的地址位数为:log24 = 2 位 主存地址位数为:log2256k=18位,故标记区位数=18-9-2=7位 所以直接映射方式下,主存地址格式为

6.已知 x = – 0.1110 y = 0.1101 求[x • y]原 解:

+

逻辑右移

部分积

乘数

说明 部分积 初态 z0 = 0 + x*

+

逻辑右移

ห้องสมุดไป่ตู้

+

逻辑右移

+

逻辑右移

0.0000 0.1110 0.1110 0.0111 0.0000 0.0111 0.0011 0.1110 1.0001 0.1000 0.1110 1.0110 0.1011

4.半导体存储器芯片的译码驱动方式有几种?各自有 什么特点?

解: 半导体存储器芯片的译码驱动方式有:线选法和重合法。 线选法:地址译码信号只选中同一个字的所有位,结构简 单,费器材; 重合法:地址分行、列两部分译码。行、列译码线的交叉 点即为所选单元。这种方法通过行、列译码信号的重合来选 址,也称矩阵译码。可大大节省器材用量,是最常用的译码 驱动方式。

解: 存储器的带宽指单位时间内从存储器进出信息的最大数。 存储器带宽=1/200ns × 32位 =160M位/秒=20MB/S=5M字/秒

3.某机字长为32位,其存储容量是64KB,按字编址 其寻址范围是多少?若主存以字节编址,试画出主 存字地址和字节地址的分配情况。

解: 存储容量是64KB时,按字节编址的寻址范围就是64KB, 则按字寻址范围= 64K×8 / 32 = 16K字 按字节编址时的主存地址分配图如下: 字地址 HB —————字节地址—————LB 0 0 1 2 3 4 4 5 6 7 8 …… …… …… …… …… 65528 65532 65533 65534 65535 65532

6 1

7 1

名称

C1 C2 C4 C8

C1 C2

0

C4

0

检测的 g1 小组包含第 1,3,5,7,9,11… C1 = 3 5 7 = 1 检测的 g2 小组包含第 2,3,6,7,10,11… C2=g3 3 小组包含第 6 7= 0 检测的 4,5,6,7,12,13… 检测的 8,9,10,11,12,13,14,15,24… C =g4 5 小组包含第 6 7= 0

2.在一个32位的总线系统中,总线的时钟频率为 66MHz,假设总线最短传输周期为4个时钟周期,试计 算总线的最大数据传输率。若想提高数据传输率,可采 取什么措施?

解法1: 总线宽度 =32位/8 =4B 时钟周期 =1/ 66MHz =0.015µs 总线最短传输周期 =0.015µs×4=0.06µs 总线最大数据传输率=4B/0.06µs=66.67MB/s 解法2: 总线工作频率 = 66MHz/4=16.5MHz 总线最大数据传输率=16.5MHz×4B=66MB/s

5. 某8位微型机地址码为18位,若使用4K×4位的 RAM芯片组成模块板结构的存储器,试问: (1)该机所允许的最大主存空间是多少? (2)若每个模块板为32K×8位,共需几个模块板? (3)每个模块板内共有几片RAM芯片? (4)共有多少片RAM? (5)CPU如何选择各模块板?

解: (1)218 = 256K,则该机所允许的最大主存空间是 256K×8位(或256KB); (2)模块板总数 = 256K×8 / 32K×8 = 8块; (3)板内片数 = 32K×8位 / 4K×4位 = 8 × 2 = 16片; (4)总片数 = 16片× 8 = 128片; (5)CPU通过最高3位地址译码选板,次高3位地址译码 选片。地址格式分配如下: 17 3 15 14 3 12 11 片内地址 12 0

第六章

计算机的运算方法

1.设机器数字长为8位(含1位符号位在内),写出对应下列各 真值的原码、补码和反码。 -13/64,29/128,100,-87 解:真值与不同机器码对应关系如下:

真

十进制

值

二进制

-13/64 29/128 100 -87

-0.00 1101 0.001 1101 110 0100 -101 0111

3.一个容量为16K×32位的存储器,其地址线和数据 线的总和是多少?当选用下列不同规格的存储芯片 时,各需要多少片? 1K×4位,2K×8位,4K×4位,

16K×1位,4K×8位,8K×8位 解: 地址线数 = log216k = 14条,数据线数 = 32条 所以地址线和数据线总和=14+32=46条 由已知条件可知各需要的片数为: 1K×4:16K×32 /1K×4 = 16×8 = 128片 2K×8:16K×32 /2K × 8 = 8 × 4 = 32片 4K×4:16K×32 /4K × 4 = 4 × 8 = 32片 16K×1:16K × 32 / 16K × 1 = 32片 4K×8:16K×32 /4K×8 = 4 × 4 = 16片 8K×8:16K×32 / 8K × 8 = 2X4 = 8片

浮点机中

[x]反 = 1, 1101; 0. 1001100000

3.将–58表示成二进制定点数和浮点数,并写出它在定点机和浮 点机中的三种机器数的形式(其他要求同上例)。

解: 设 x = –58 二进制形式 定点表示 浮点规格化形式 定点机中 [x]原 = 1, 0000111010 [x]补 = 1, 1111000110 [x]反 = 1, 1111000101 x = – 111010 x = – 0000 111010 x = – (0.1110100000) × 2110 浮点机中 [x]原 = 0, 0110; 1. 1110100000 [x]补 = 0, 0110; 1. 0001100000 [x]反 = 0, 0110; 1. 0001011111

= 0.1011

= 1.1011

[A]补 + [B]补

= 1 0 . 0 1 1 0 = [A + B]补 (2分)

因为[A + B]补为正数,所以A + B = [A + B]补= 0 . 0 1 1 0 (2分)

5.设机器数字长为 8 位(含 1 位符号位),且 A = 15, B =

24,用补码运算规则求 A – B。 解: 由已知条件:A=15=0001111(1分),B=24=0011000(1分), A 原 =A 补 =0,0001111(2 分 ) , [-B] 原 =1,0011000(1 分 ),[-B] 补 =1,1101000(1分),由公式[A-B]补=[A]补+[-B]补(2分)计算如下: