射频电路设计讲义(关键知识点)

无线电技术中的射频电路设计技术

无线电技术中的射频电路设计技术在无线电通信领域中,射频电路设计是至关重要的一环,因为射频电路设计直接决定了无线电信号的质量和传输距离。

因此,研究和掌握射频电路设计技术,对于无线电技术的发展和应用具有重要意义。

射频电路设计技术是一种纵向整合的技术,它涉及到无线电通信的多个领域,包括:无线电频率、信噪比、电路参数和电压等。

在射频电路设计中需要考虑的问题是如何将信号从一个系统传输到另一个系统,而无损地传输这些信号并提供高品质的信号传输特性。

下面将从射频电路设计的基础知识、射频电路设计的流程、射频电路设计的工具以及射频电路设计中具体的技术应用进行讲述。

一、射频电路设计的基础知识1.无线电频率射频电路设计中最基本的知识点就是无线电频率。

在无线电通信中,无线电信号需要在一个特定的频率范围内传输,而这个频率范围就是无线电频率范围。

因此,在射频电路设计中需要考虑在何种频率范围内传输无线电信号。

2.电路参数电路参数在射频电路设计中非常重要,因为不同的电路参数对射频电路的传输特性有所不同。

在射频电路设计中,需要对电路参数进行合理的选择和优化,以便实现所需要的传输特性。

3.信噪比信噪比是射频电路设计的另一个重要的概念,它用于描述信号质量和噪声水平之间的关系。

在射频电路设计中,需要考虑如何优化信噪比以提高信号传输的质量。

4.功率放大器在射频电路设计中,功率放大器是一个非常重要的部件,因为它能够增加信号的功率,使得信号能够在更远的距离传输。

在射频电路设计中,需要考虑如何选择和设计功率放大器以获得所需的信号传输特性。

二、射频电路设计的流程射频电路设计的流程往往包含以下四个步骤:1.需求分析需求分析是射频电路设计的第一步,它主要涉及到了解客户要求和目标,将其转化为技术规格书,以便于项目进一步开展。

2.电路设计电路设计是射频电路设计的核心步骤。

在电路设计中,需要考虑信号传输的频率范围、信号功率、信噪比等因素,从而选择合适的电路结构和元件,设计电路并进行分析和仿真。

射频电路的重要知识点总结

射频电路的重要知识点总结一、射频电路的基本概念1. 射频信号射频信号通常指频率在300千赫兹至300千兆赫兹之间的信号,是一种高频信号。

射频信号通常用来进行无线通信、雷达、卫星通信等。

射频信号相对于低频信号来说,具有传输距离远、穿墙能力强、信息容量大等优点。

2. 射频电路射频电路是一种用于处理射频信号的电路,主要包括射频放大器、射频混频器、射频滤波器、射频功率放大器、射频开关、射频调制解调器、射频天线等组成。

3. 射频电路的特点射频电路与常规低频电路相比,具有频率高、传输损耗大、抗干扰能力强、器件参数要求高等特点。

二、射频电路的设计流程1. 确定需求射频电路的设计首先需要明确需求,包括工作频率、输入输出阻抗、幅度和相位平衡要求、抗干扰能力、工作环境等。

2. 选择器件根据需求选择合适的射频器件,如射频放大器、射频混频器、射频滤波器等。

选择器件时需要考虑器件的工作频率范围、增益、线性度、稳定性、耦合度等参数。

3. 电路设计根据需求和选择的器件,进行射频电路的整体设计,包括电路拓扑结构设计、参数计算、仿真验证等。

4. 电路布局和布线射频电路的布局和布线对电路的性能有很大的影响,需要考虑信号的传输路径、防止反射和耦合、尽量减少信号损耗等。

5. 电路调试和优化射频电路设计完成后需要进行调试和优化,对功耗、线性度、稳定性、抗干扰能力等进行测试和改进。

6. 电路验证射频电路设计完成后需要进行电路性能验证,包括工作频率范围测试、输入输出阻抗匹配测试、幅度和相位平衡测试、抗干扰能力测试等。

三、射频电路中的常见器件1. 射频放大器射频放大器是射频电路中的重要器件,用于放大射频信号。

根据工作频率和功率要求可以选择不同的射频放大器,包括晶体管放大器、集成射频放大器、功率放大器等。

2. 射频混频器射频混频器用于将射频信号和局部振荡信号进行混频,产生中频信号。

射频混频器的性能对整个混频系统的性能影响很大。

3. 射频滤波器射频滤波器主要用于滤除非目标频率的信号,保证接收机的选择性和抗干扰能力。

射频电路设计理论与应用课件

二端口网络与S参数

二端口网络定义

描述射频电路中两个端口之间的 输入与输出关系,可采用Z参数、

Y参数、S参数等表示。

S参数含义与应用

S参数(散射参数)描述端口入射 波与反射波之间的关系,常用于射 频电路性能分析、设计与测试。

S参数测量与仿真

通过矢量网络分析仪等设备测量射 频电路的S参数,利用电路仿真软件 进行S参数仿真,指导电路设计优化。

射频电路设计理论与应用课 件

• 射频电路设计概述 • 射频电路设计基础理论 • 射频电路核心组件设计 • 射频电路应用技术 • 射频电路设计案例分析与实践

01

射频电路设计概述

射频电路的定义与应用领域

定义

射频电路是指工作在射频频段的 电路,通常包括无线收发系统、 微波电路、射频放大器、混频器等。

稳定工作。

04

射频电路应用技术

射频电路在无线通信中的应用

移动通信

射频电路在移动通信系统中起到关键的作用。它包括接收和发送信号的天线接 口、功率放大器、混频器等,实现信号的无线传输和接收。

无线局域网(WLAN)

射频电路在WLAN中用于实现无线信号的发送和接收。它包括射频收发器、滤 波器、振荡器等,确保数据的可靠传输。

射频电路设计案例分析与实践

案例一:基于ADS的射频滤波器设计

设计目标:利用ADS(Advanced Design System)软 件设计一款符合特定频率响应要求的射频滤波器。

2. 利用ADS的滤波器设计工具,输入滤波器参数,生成 初始电路图。

设计步骤

3. 对电路图进行仿真优化,如调整元件值,以满足频率 响应、带宽、带内波动等性能要求。

03

射频电路核心组件设计

滤波器设计

射频集成电路设计

射频集成电路设计1. 引言射频集成电路(RFIC)是一种专门用于射频信号处理的集成电路。

射频信号在无线通信、雷达和无线电频段的应用中至关重要。

射频集成电路设计是关于将射频电子设备集成到单个芯片上的过程。

它要求设计师具备深入的电子工程知识和专业技能。

本文将重点介绍射频集成电路设计的基本概念、设计流程和常用技术。

通过对每个主题的详细讲解,读者将能够全面地了解射频集成电路设计领域的最新动态和发展趋势。

2. 射频集成电路设计基础2.1 射频电路概述射频电路是指工作频率在几百千赫兹(kHz)到几千兆赫兹(GHz)范围内的电路。

射频电路通常用于无线通信系统、雷达系统和广播系统等领域。

与低频电路相比,射频电路的设计更加复杂,需要考虑很多特殊因素,如频率选择、阻抗匹配和信号传输等。

2.2 射频集成电路分类根据功能和工作频率的不同,射频集成电路可以分为不同的分类。

常见的射频集成电路包括功率放大器、混频器、振荡器和滤波器等。

每个分类都有各自的特点和用途。

2.3 射频集成电路设计流程射频集成电路设计流程是指从需求分析到最终产品实现的一系列环节。

它包括系统规划、电路设计、性能仿真和验证测试等步骤。

设计流程的每个环节都需要设计师仔细分析和设计,以确保最终产品能够满足设计要求和性能指标。

3. 射频集成电路设计常用技术3.1 频谱分析频谱分析是一种用于分析射频信号频率成分和幅度的技术。

通过频谱分析,设计师可以了解信号的频率分布情况,并基于此进行设计优化。

3.2 阻抗匹配技术阻抗匹配是指在输入输出端口之间实现匹配的技术。

阻抗匹配可以提高信号传输效率,减少信号反射和损耗,从而提高系统的性能。

3.3 射频集成电路建模和仿真射频集成电路建模和仿真是用计算机模拟射频电路的工作过程。

通过建模和仿真,设计师可以评估不同的设计方案,并优化设计参数,以满足特定的性能要求。

3.4 射频功率放大器设计射频功率放大器是射频集成电路中最常用的组件之一。

RF(射频)电路理论与设计精品PPT课件

13、无耗传输线上通过任意点的传输功率等于该点的入 射波功率与反射波功率之差。

14、TEM传输线(即传输TEM波的传输线)无色散。色 散是指电磁波的传播速度与频率有关。TEM传输线上 电磁波的传播速度与频率无关。

2

2

其中

是由终端算起的坐标 I (z' ) V2 I2Z0 e jz' V2 I2Z0 e jz'

2Z0

2Z0

z' l z, z'

在已知传输线始端电压 和始端电流 的前提下:

V (z) V1 I1Z0 e jz V1 I1Z0 e jz

2

2

5、反射系数

I (z) V1 I1Z0 e jz V1 I1Z0 e jz

ZC

ABCD

YA

1 YB

YC

YB

YAYB YC

1

1

YC YA

YC

写在最后

经常不断地学习,你就什么都知道。你知道得越多,你就越有力量 Study Constantly, And You Will Know Everything. The More

You Know, The More Powerful You Will Be

析。

4、互易网T络仅适用于含有线性双向阻抗的无源网络,满

足该条件的无源网络可含有电阻、电容、电感或变压器 等线性无源器件。由铁氧体各项异性媒质构成的元件及 有源电路不是互易网络。对称网络是互易网络的一个特 例。对称网络中电子元件的大小及尺寸位置对称分布。 对称网络首先是互易网络。

射频电路的基础知识介绍

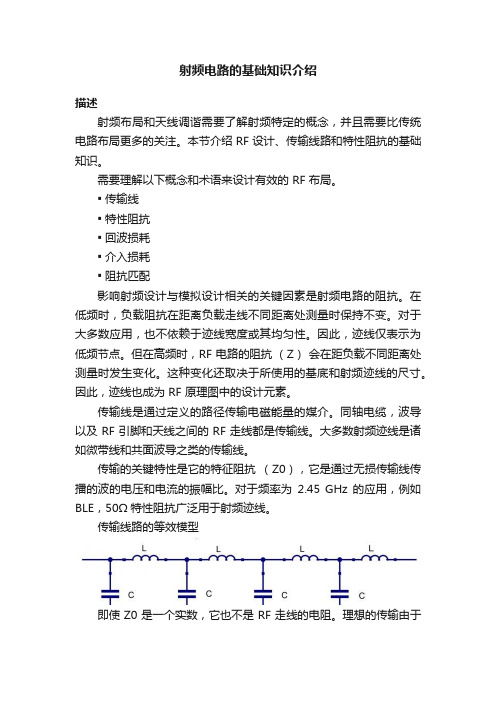

射频电路的基础知识介绍描述射频布局和天线调谐需要了解射频特定的概念,并且需要比传统电路布局更多的关注。

本节介绍 RF 设计、传输线路和特性阻抗的基础知识。

需要理解以下概念和术语来设计有效的 RF 布局。

▪传输线▪特性阻抗▪回波损耗▪介入损耗▪阻抗匹配影响射频设计与模拟设计相关的关键因素是射频电路的阻抗。

在低频时,负载阻抗在距离负载走线不同距离处测量时保持不变。

对于大多数应用,也不依赖于迹线宽度或其均匀性。

因此,迹线仅表示为低频节点。

但在高频时,RF 电路的阻抗(Z)会在距负载不同距离处测量时发生变化。

这种变化还取决于所使用的基底和射频迹线的尺寸。

因此,迹线也成为 RF 原理图中的设计元素。

传输线是通过定义的路径传输电磁能量的媒介。

同轴电缆,波导以及 RF 引脚和天线之间的 RF 走线都是传输线。

大多数射频迹线是诸如微带线和共面波导之类的传输线。

传输的关键特性是它的特征阻抗(Z0),它是通过无损传输线传播的波的电压和电流的振幅比。

对于频率为2.45 GHz 的应用,例如BLE,50Ω特性阻抗广泛用于射频迹线。

传输线路的等效模型即使 Z0 是一个实数,它也不是 RF 走线的电阻。

理想的传输由于其特性阻抗不消耗能量或具有任何损耗。

传输线的等效模型如上图所示。

它是表示传输线分布式串联电感与分布式并联电容之比的属性。

其中 L 和 C 分别是沿传输线任意长度的分布电感和分布电容。

特性阻抗(Z0)取决于 PCB 材料,基底厚度,迹线宽度,迹线厚度以及 RF 迹线和接地填充物之间的间隙。

这些参数在传统的布局和设计中经常被忽略,但它们在射频设计中扮演着重要的角色。

阻抗测量设置的表示上图描述了测量 RF 电路阻抗的典型测量设置。

射频走线上给定点的阻抗与走线的特征阻抗,与负载的距离和负载阻抗有关;计算方式如下面的等式:其中 Z 是在距离负载的距离为 l 处测得的阻抗,ZL是在负载(l = 0)处测得的阻抗,Z0是传输线的特性阻抗,β是相位常数。

射频电路设计要点

成功的 RF 设计必须仔细注意整个设计过程中每个步骤及每个细节,这意味着 必须在设计开始阶段就要进行彻底的、仔细的规划,并对每个设计步骤的进展 进行全面持续的评估。而这种细致的设计技巧正是国内大多数电子企业文化所 欠缺的。

近几年来,由于蓝牙设备、无线局域网络(WLAN)设备,和移动电话的需求与成 长,促使业者越来越关注 RF 电路设计的技巧。从过去到现在,RF 电路板设计 如同电磁干扰(EMI)问题一样,一直是工程师们最难掌控的部份,甚至是梦魇。 若想要一次就设计成功,必须事先仔细规划和注重细节才能奏效。

(11)不同电源层在空间上要避免重叠。主要是为了减少不同电源之间的干 扰,特别是一些电压相差很大的电源之间,电源平面的重叠问题一定要设法避 免,难以避免时可考虑中间隔地层。

(12)PCB 板层分配便于简化后续的布线处理,对于一个四层 PCB 板(WLAN 中常用的电路板),在大多数应用中用电路板的顶层放置元器件和 RF 引线,第 二层作为系统地,电源部分放置在第三层,任何信号线都可以分布在第四层。 第二层采用连续的地平面布局对于建立阻抗受控的 RF 信号通路非常必要,它 还便于获得尽可能短的地环路,为第一层和第三层提供高度的电气隔离,使得

使用星型拓扑 Vcc 引线时,还有必要采取适当的电源去耦,而去耦电容存在一 定的寄生电感。事实上,电容等效为一个串联的 RLC 电路,电容在低频段起主 导作用,但在自激振荡频率(SRF):

之后,电容的阻抗将呈现出电感性。由此可见,电容器只是在频率接近或低于 其 SRF 时才具有去耦作用,在这些频点电容表现为低阻。

给出了不同容值下的典型 S11 参数,从这些曲线可以清楚地看到 SRF,还可以 看出电容越大,在较低频率处所提供的去耦性能越好(所呈现的阻抗越低)。

射频电路设计

射频电路设计是无线通信领域中的关键技术,它与无线通信的性能和特性直接相关。

的目的是为了实现高效的信号传输、抗干扰能力强、信噪比高、频谱资源利用效率高、低功耗等性能优异的无线通信系统。

一、的基本概念射频电路是指在无线通信系统中用于调制、解调、放大、滤波和发射、接收无线信号的电路。

由于无线通信系统中信号的频率一般在几百万赫兹到几千兆赫兹之间,因此射频电路工作在高频范围内,其特点是频率高、电压小、电流大、噪声大、传输距离短等。

的主要任务是实现信号的滤波、放大、混频、调制等操作,从而完成信号的处理和传输。

一般来说,需要考虑以下方面的因素:1.频段和带宽:确定射频电路工作的频率范围和工作带宽。

2.信号处理的功能:确定射频电路要实现的信号处理功能,如滤波、放大、混频、调制等。

3.电路结构和拓扑:确定射频电路的具体拓扑结构和电路元件,并进行系统级的优化设计。

二、中的关键技术1.滤波技术:滤波是射频信号处理中最常用的技术之一,它的主要作用是将所需的信号从噪声和干扰中分离出来。

滤波器一般分为低通、带通、高通和带阻滤波器。

在设计射频电路时,需要根据实际情况进行合理的滤波器选择和设计。

2.放大技术:放大器是中最常用的元件之一,它的主要功能是将信号增强到足够的水平以便在后续处理中进行正常传输。

在中,需要根据具体设计要求选择合适的放大器拓扑结构和参数。

3.混频技术:混频器用于将两个不同频率的信号相乘,产生出新的频率,这个过程叫做混频。

在接收端,混频器主要用于将接收到的高频信号转换为中频信号,同时滤波器用于去除混频后的高频信号。

4.调制技术:调制用于将基带信号(低频)和射频信号(高频)结合起来。

在通信系统中,调制技术是实现高效传输的关键。

常见的调制方式包括振幅调制、频率调制和相位调制等。

5.射频功率放大技术:射频功率放大器是一种用于放大射频信号的放大器,通常要求具有高效、大功率、尽可能小的失真等特点。

在中,功率放大器的设计是一个非常关键的环节,其设计的好坏直接影响整个无线通信系统的性能。

《射频电路设计一》课件

为确保信号传输效率,设计合适的信号源和负载 匹配网络。

3

设计滤波器、功分器等辅助电路

根据系统需求,设计相应的滤波器、功分器等辅 助电路。

电路版图绘制与仿真验证

使用专业软件绘制电路版图

使用专业软件,如Cadence、Mentor Graphics等,绘制射频电路 的版图。

进行电磁仿真验证

《射频电路设计一 》ppt课件

目 录

• 射频电路概述 • 射频电路的基本元件 • 射频电路的分析方法 • 射频电路的设计流程 • 射频电路的调试与优化 • 案例分析

01

射频电路概述

定义与特点

定义

射频电路是指工作在射频频段的 电子电路,通常用于无线通信、 雷达、导航等领域。

特点

射频电路具有高频率、高带宽、 高灵敏度等特点,能够实现高速 、远距离的无线信号传输。

具有通直流阻交流的特性,常用于滤波、 振荡、延迟等电路中。

种类

包括空心电感、磁芯电感、变压器等。

应用

在射频电路中,电感常用于调谐、匹配、 滤波等电路中。

电阻

定义

导体对电流的阻碍作用称为电阻,是一个物理量,符号为R。

特性

具有消耗电能的作用,常用于限流、分压等电路中。

种类

包括碳膜电阻、金属膜电阻、线绕电阻等。

传输线近似分析法

总结词

传输线近似分析法适用于分析传输线和微波网络,通过将电路简化为传输线模型 ,便于理解和计算。

详细描述

传输线近似分析法主要应用于传输线和微波网络的射频电路设计。该方法将电路 简化为传输线模型,通过求解传输线和微波网络的参数来分析电路性能。该方法 计算简便,精度较高,适用于对信号传输特性要求较高的场合。

射频基础知识

1mW 1mW 10 lg 0 dBm 1mW

1.26mW 1.26mW 10 lg 1dBm 1mW

功率和增益差损

30000mW 30W 10 lg 44.77 dBm 1mW

30W 30W 10 lg 14.77 dBW 1W

表示传输线长度。 z

'

驻波比和传输功率、Smith圆图

根据最大功率传输条件下的阻抗匹配,在使用公式时 往往涉及复数运算,比较麻烦,使用不方便。利用史密斯 圆图(Smith Chart)可简便求解,并且容易看出准确结果 的趋向,而其作图误差在工程允许范围内,常用于复杂网 络的初调计算。 要使信号源传送到负载的功率最大,需要负载匹配。 用smith圆图设计匹配网络,即使得负载阻抗变换到源端时 匹配到源特性阻抗如50欧姆。这就等于要求信号源经过匹 配网络到负载的输出阻抗必须等于负载的共轭阻抗,即:

• 传输媒介相对介电常数 r大于1时,电磁波传播速度小 内于真空中传输的距离。

C f 3 10 m / s

8

于光速为:

V r f

C

r 为传输媒介中电磁波的等效传输线波长。

• 真空中BD发射波长约为18.5cm,接收波长约为12cm。 • 实际传输线中以上两项的传输波长要略小于所给值。

- 10lg 1

2

0.52dB

驻波比和传输功率、Smith圆图

在非理想状态下,由于源阻抗、传输线上的特性阻抗、负 载阻抗都不可能是纯粹的50欧姆。因此存在源阻抗与负载 阻抗的失配。 根据最大功率传输定理:工作于正弦稳态的单口网络向一 个负载 Z L RL jX L 供电,如果该单口网络可用戴维宁等 效电路(其中 Zo Ro jX o 为源输出阻抗)代替,则在负载 * 阻抗等于含源单口网络输出阻抗的共轭复数(即 Z Z ) L o 时,负载可以获得最大平均功率。

射频电路设计(RF_Circuit_design)

+jx |Γ|=0.5

|Γ|=0.1

r=0

r=0.5

r=1

r=2

r=∞

- jx

1.05

x=-0.5

x=-1

x=-2

1.05

1.05 r r( 0 ) r r( 0.5 ) r r( 1 ) r r( 2 ) x r( 2 ) x r( 1 ) x r( 0.5 ) x r( 0.5 ) x r( 1 ) x r( 2 ) i( 0.1 ) i( 0.5 )

设计工具: winsmith.exe

Zs

ZL

Smith Chart8

设计工具: Smith V2.00 winsmith.exe

Zo=75

与并联传输线长度有关

圆心 Zo=50

Zs

ZL

Smith Chart9 射频操

射频操

1.串电感

3.並电感

4.並电容

5.串传输线

2.串电容

设计工具 : winSMITH®

Smith Chart5

阻抗导纳圆图(ZY-圆图) 在许多实际设计和应用中,需 要频繁地从阻抗表达式转换到 导纳表达式,反之亦然。为了 应用方便,常将阻抗( Z )圆 图和导纳( Y )圆图叠加成一 个组合圆图称其为阻抗导纳圆 图或ZY-圆图。 阻抗圆图是大家所熟悉的(如 图示),导纳原图是怎样呢?

Zs

Vg

a1

b2

2-Port Network

ZL

b2=S21a1+S22a2

b1

a2 IRL 20 log S11

b1 s11 a1 b2 s22 a2

a2 0

射频电路的重要知识点

射频电路的重要知识点射频电路是电子学中的一个重要分支,主要研究高频信号的传输、放大、调制和解调等技术。

射频电路广泛应用于通信领域,包括无线电、卫星通信、雷达系统等。

在本文中,我们将介绍射频电路的一些重要知识点,帮助读者对射频电路有更深入的了解。

1.射频电路的基本概念–射频(Radio Frequency)是指频率范围在3kHz到300GHz之间的电磁波信号。

–射频电路是指处理射频信号的电路,包括信号的放大、滤波、调制和解调等功能。

2.射频电路的特点–射频信号具有高频率和高频率变化速度的特点,因此对电路的稳定性要求较高。

–射频电路的元器件和设计需考虑高频信号的传输特性,如电缆、电感、电容等。

–射频电路的传输和放大会引入噪声,需要采取相应的噪声抑制和增益控制措施。

3.射频电路的基本元器件–高频电阻:用于限制电流流过的路径,常用材料有炭化钨和碳膜电阻。

–电感器:用于储存和释放电能的元件,常用材料有铁氧体和氧化铁等。

–电容器:用于储存和释放电能的元件,常用材料有陶瓷和铝电解电容等。

4.射频电路的滤波器–射频滤波器用于选择特定频率范围内的信号,并削弱或抑制其他频率的信号。

–常见的射频滤波器包括低通滤波器、高通滤波器、带通滤波器和带阻滤波器。

5.射频电路的放大器–射频放大器用于放大射频信号的幅度,以保证信号的传输质量和稳定性。

–常见的射频放大器包括共射放大器、共基放大器和共集放大器等。

6.射频电路的调制和解调–调制是将基带信号转换为射频信号的过程,常见的调制方式有幅度调制、频率调制和相位调制等。

–解调是将射频信号转换为基带信号的过程,常见的解调器有包络检波器、鉴频器和相干解调器等。

7.射频电路的射频封装技术–射频封装技术是射频电路研究中的一个重要环节,用于保护电路元件和提高电路的性能。

–常见的射频封装技术包括微带线封装、贴片封装和球栅阵列封装等。

总结:射频电路作为通信领域的重要组成部分,其理论和应用领域十分广泛。

射频电路基本原理与设计技巧

射频电路基本原理与设计技巧射频(Radio Frequency,简称RF)电路在现代通信系统中起着至关重要的作用。

它涵盖了从天线到射频前端的信号处理、放大、调制和解调等一系列技术,直接影响到通信质量和性能。

本文将介绍射频电路的基本原理和设计技巧,以帮助读者理解和应用于实际工程中。

一、射频电路的基本原理1. 频率和波长射频电路的特点之一是工作频率较高,通常在几十千赫兹到几百吉赫兹之间。

在理解射频电路的基本原理时,我们首先需理解频率和波长的关系。

频率和波长互为倒数,即频率越高,波长越短。

在射频电路设计中,理解和掌握频率和波长之间的转换关系是十分重要的。

2. 传输线理论传输线是射频电路中常用的元件之一,它用于在不同器件和部件之间传输射频信号。

传输线理论是研究射频信号在传输线中的传输和反射特性等的理论基础。

对于不同类型的传输线,如同轴线、微带线等,都有相应的理论模型和设计指导规则,需要根据具体的应用场景选择合适的传输线类型。

3. 射频放大器设计射频放大器用于增强射频信号的幅度,提高信号的传输距离和质量。

在射频放大器设计中,常用的设计技巧包括选择合适的放大器类型(如共射放大器、共基放大器等)、优化放大器的工作点、控制反馈和稳定等。

同时,射频放大器的稳定性和线性度等也是设计中需要特别注意的问题。

4. 混频器和调制解调器设计混频器用于将不同频率的射频信号进行变频处理,常见的有单、双、多、平衡等类型。

调制解调器则用于对射频信号进行调制和解调,实现信号的调制、解调和解码等功能。

在设计混频器和调制解调器时,需要考虑到信号的频率对齐、幅度平衡以及相位一致等问题。

5. 滤波器设计滤波器用于对射频信号进行频率选择性处理,滤除不需要的频段,保留感兴趣的频段。

常见的滤波器类型包括带通滤波器、带阻滤波器和全局反馈滤波器等。

在滤波器设计中,需要根据实际需求选择合适的滤波器类型,通过优化滤波器参数来达到所期望的滤波特性。

二、射频电路的设计技巧1. 良好的功率分配与返回路径布局射频电路设计中,良好的功率分配与返回路径布局是至关重要的。

射频基础知识讲座PPT课件

• 频综

• 耦合

• 检测(功率)

•57

射频电路的基本功能部件

• 频综的组成 ▽ VCO、VCXO 、TCXO、OCXO ▽ PLL(锁相环)

•58

射频电路的基本功能部件

• 频综的主要参数 ▽频率 ▽相噪 ▽功率

•59

射频电路的基本功能部件

• 放大

• 衰减

• 混频 RF

IF LO

• 滤波

• 频综

算

10*log(2)=3dB

10*log(4)=6dB

级联增益=2*4=8倍

10*log(8)=9dB

级联增益=3+6=9dB

•24

射频的一些基本概念

• dBm ▽是一个功率的单位 ▽10*log(功率/mW) ▽1W=10*log(1W/1mW) =10*log(1000) =30dBm

•25

射频的一些基本概念

▽压控衰减器

▽AGC(自动增益控制)

•48

射频电路的基本功能部件

• 衰减器的主要参数 ▽衰减量 ▽IP3(P1dB) ▽输入输出阻抗

•49

射频电路的基本功能部件

• 放大

• 衰减

• 混频 RF

IF LO

• 滤波

• 频综

• 耦合

• 检测(功率)

•50

射频电路的基本功能部件

• 混频 ▽无源混频 ▽有源混频

RFE

TRx

DIV

RFE功能示意框图

•16

基站射频系统的基本组成与架构

天 线1

BT M注 入 获 取

R FCM

LNA

4分

路器

TE ST TR X

天 线0

BTM 注入 获取

射频电路需要什么知识点

射频电路需要什么知识点在设计和理解射频(Radio Frequency,RF)电路时,需要掌握一系列的知识点。

本文将从基础知识到高级概念逐步介绍射频电路设计所需的知识点。

1.电路基础知识首先,要理解射频电路,需要掌握电路基础知识。

这包括电压、电流、电阻、电感和电容等基本概念。

了解欧姆定律、基本电路分析方法和电路元件的特性对射频电路的设计至关重要。

2.信号与频谱分析了解信号与频谱分析是射频电路设计的关键。

射频信号是高频信号,需要掌握频谱分析的基本原理和方法。

掌握傅里叶变换和频谱分析工具的使用能够帮助我们理解和分析射频信号的特性。

3.射频器件特性了解常用的射频器件特性对射频电路设计非常重要。

例如,掌握二极管和晶体管的特性,了解它们的非线性特性、频率响应和功率特性等。

4.射频放大器设计射频放大器是射频电路中的核心组件之一。

掌握射频放大器的设计原理、放大器级数和匹配网络设计的基本方法。

5.射频滤波器设计射频滤波器用于剔除不需要的频率分量,保留感兴趣的射频信号。

了解射频滤波器的基本原理、滤波器类型和设计方法对射频电路的性能至关重要。

6.射频混频器设计射频混频器用于将一个射频信号与一个局部振荡信号相互作用,产生新的频率组合。

了解射频混频器的工作原理、类型和设计方法是进行频率转换和调制的关键。

7.射频天线设计射频天线用于发送和接收无线电信号。

了解射频天线的基本原理、天线参数和天线设计方法对射频通信系统的性能至关重要。

8.射频布线与阻抗匹配在射频电路设计中,良好的布线和阻抗匹配能够减少信号损耗和反射。

掌握射频布线技巧和阻抗匹配方法对射频电路的性能具有重要影响。

9.射频电路仿真与优化现代工具如电磁场仿真、电路仿真和优化软件等可以帮助设计师验证和优化射频电路设计。

了解射频电路仿真和优化方法可以提高设计效率和性能。

总结起来,射频电路设计需要掌握电路基础知识、信号与频谱分析、射频器件特性、射频放大器设计、射频滤波器设计、射频混频器设计、射频天线设计、射频布线与阻抗匹配以及射频电路仿真与优化等知识点。

模拟电子技术基础知识射频电路设计与优化

模拟电子技术基础知识射频电路设计与优化射频(Radio Frequency,简称RF)电路设计是在模拟电子技术中具有重要地位和应用前景的领域。

正确、高效地进行射频电路设计与优化能够提高射频系统的性能,实现更好的信号传输和接收效果。

本文将介绍射频电路设计与优化的基础知识,并探讨相关的设计方法和技巧。

1. 射频电路设计基础知识1.1 无线通信系统简介:随着无线通信技术的迅猛发展,人们对无线通信系统的需求也逐渐增加。

无线通信系统主要包括发送端和接收端两个部分,其中射频电路是发送端和接收端之间的关键连接。

射频电路的设计与优化直接关系到整个无线通信系统的性能和稳定性。

1.2 射频电路的特点:射频电路的工作频率范围通常在几十千赫兹到几百兆赫兹之间,其特点主要包括高频、宽带、低噪声和高增益等。

因此,在设计射频电路时需要考虑电磁干扰、串扰以及信号的衰减等问题。

2. 射频电路设计方法2.1 电路规划和布局设计:在进行射频电路设计之前,需要进行电路规划和布局设计。

首先,需要根据系统要求确定电路的拓扑结构、工作频率和带宽。

然后,合理布局电路的各个元器件,避免电路中的零部件相互干扰。

2.2 射频电路元器件的选择:在射频电路设计中,选择合适的元器件是至关重要的。

常用的射频电路元器件包括功率放大器、低噪声放大器、混频器和滤波器等。

选用合适的元器件能够提高电路的性能和稳定性。

2.3 射频电路仿真和优化:在射频电路设计过程中,仿真和优化是必不可少的步骤。

利用专业的软件工具进行电路仿真,可以通过参数调整和优化,得到更好的电路性能。

常用的仿真软件有ADS、CST等。

3. 射频电路设计的常见问题和解决方法3.1 电磁干扰与排布问题:射频电路中常常存在电磁干扰和排布问题,这些问题直接影响着电路的性能和稳定性。

为解决这些问题,可以采取合理的电路布局、增加地线等措施,降低电路中的干扰。

3.2 信号衰减与放大问题:射频电路中,信号衰减和放大是常见的问题。

射频电路设计知识点总结

射频电路设计知识点总结嘿呀!今天咱们来好好唠唠射频电路设计的那些知识点!首先呢,咱们得明白啥是射频电路呀?哎呀呀,简单说就是能处理高频信号的电路啦!这在通信、雷达等领域那可是相当重要呢!1. 射频元件的特性哇!这可是基础中的基础呀!像电阻、电容、电感这些常见元件,在射频领域可就有大不同啦!电阻在高频下会有寄生电感和电容的影响,电容的寄生电感也不能忽视呀!电感的自谐振频率更是关键呢!这要是搞不清楚,设计出来的电路可就容易出问题啦!2. 传输线理论哎呀呀!这可是射频电路的核心理论之一呢!微带线、同轴线、波导,它们的特性和应用都得好好掌握!比如说,微带线的特性阻抗怎么计算?同轴线的损耗咋考虑?这些都要心里有数呀!3. 匹配网络嘿!这可是保证信号传输效率的关键哟!什么是阻抗匹配?为啥要匹配?怎么进行匹配?这里头的学问可不少呢!通过电感电容的组合,或者用变压器,都能实现匹配,但是得选对方法呀!4. 滤波器设计哇塞!滤波器在射频电路里太重要啦!低通、高通、带通、带阻,各种类型的滤波器都有各自的特点和设计方法。

比如说,用集总元件还是分布元件来设计?这得根据频率和性能要求来决定呢!5. 放大器设计哎呀呀!放大器可是增强信号的利器呀!小信号放大器和大信号放大器的设计方法可不一样哟!稳定性、增益、噪声系数,这些指标都得兼顾好呀!6. 混频器嘿!混频器能实现频率变换,这在通信系统里可少不了呢!怎么保证混频器的性能?寄生参数的影响咋处理?这些都得认真研究呀!7. 射频电路的仿真哇!现在有好多仿真软件可以用呢,ADS、HFSS 等等。

通过仿真,可以提前预测电路的性能,少走好多弯路呀!总之呢,射频电路设计可不是一件简单的事儿呀!需要掌握好多知识和技能,不断地学习和实践才行呢!哎呀呀,希望这次的总结能对大家有所帮助呀!。

射频电路设计第一章

噪声系数

01

噪声系数

描述了电路内部噪声对信号的影响 程度,通常用噪声系数表示。

灵敏度

描述了电路能够检测到的最小信号 强度,通常用灵敏度表示。

03

02

信噪比

描述了信号与噪声之间的比例关系, 通常用信噪比表示。

选择性

描述了电路对不同频率信号的选择 能力,通常用选择性表示。

04

05

射频电路的设计流程

系统指标分析

动态范围

描述了电路能够处理的信号强度范围,通常 用动态范围表示。

功率增益

功率增益

描述了电路对输入信号的功率放大能力,通 常用功率增益表示。

效率

描述了电路将直流功率转化为射频功率的能 力,通常用效率表示。

稳定性

描述了电路在不同工作条件下的性能稳定性, 通常用稳定性表示。

可靠性

描述了电路在不同工作条件下的寿命和可靠 性,通常用可靠性表示。

匹配网络

为避免信号反射和能量损失,需要 设计合适的匹配网络,使元件与传 输线之间达到良好的阻抗匹配。

元件稳定性

考虑元件在射频频率下的稳定性, 以及温度、湿度等环境因素对元件 性能的影响。

电路仿真与优化

电路模型建立

根据实际电路结构和元件参数,建立精确的电路模型。

仿真分析

利用仿真软件对电路模型进行分析,预测电路性能。

感谢观看

THANKS

射频电路的应用领域

无线通信

雷达与导航

广播

物联网

手机、基站、无线局域 网等。

气象雷达、卫星定位系 统等。

电视广播、调频广播等。

传感器节点、智能家居 等。

射频电路的发展趋势

01

02

03

射频电路设计课程内容提要

第3章 射频功率放大器电路设计

内容提要

射频功率放大器用来产生足够大的射频输出功率,并馈送 到天线上辐射出去。射频功率放大器的主要技术指标是输 出功率与效率。其电路通常由放大器件和阻抗匹配网络组 成,按工作状态分类可分为线性放大电路和非线性放大电

在调制中,载波信号的幅度随调制信号而变,称为幅 度调制(AM);载波信号的频率随调制信号而变,称 为频率调制或调频(FM);载波信号的相位随调制信 号而变,称为相位调制或调相(PM)。

数字信号对载波振幅调制称为振幅键控(ASK),对载 波频率调制称为频移键控(FSK),对载波相位调制称 为相移键控(即相位键控)(PSK)。

可利用所掌握的调制与解调电路的分析方法,对实例 电路结构形式进行研究。

可根据教学需要,对应用电路和印制电路板设计实例 展开讨论。有关芯片的技术指标、内部结构、引脚功 能和封装尺寸等可以作为作业,登录相关网站查询, 进一步加深对电路实例的理解。

第5章 混频器电路设计

内容提要

混频(变频)是将载频为fC的已调波变换为载频为fI的 已调波。将已调波载频搬至高于本振频率L,称为上 变频;把已调波载频搬至低于本振频率L,称为下变

知识要点

锁相环路(PLL),鉴相器(PD),压控振荡器 (VCO),环路滤波器,分频器,锁定,捕获,跟踪,

窄带滤波特性。

教学建议

本章的重点是掌握锁相环路(PLL)电路的一些基本概 念,锁相环路(PLL)的结构和分析方法,锁相环路 (PLL)应用电路结构形式和特点,基于单片集成电路 的锁相环路(PLL)电路、VCO电路、缓冲放大器电路 和前置分频器电路设计实例。建议学时数为4学时。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

y0=1

yL

• 基本设计步骤

– 在圆图上将归一化的阻抗 zL 转换成归一化 的导纳 yL (how?),阻抗圆图也就成为导纳 圆图 – 画出 zL 或 yL 所对应的反射系数圆,找出其 与单位电导圆的交点,通常存在两个交点 1+jb 和 1-jb (b>0),可以选择一个进行设计

射频集成电路设计基础 > 补充内容 > 短截线 (Stub) 阻抗匹配举例

射频集成电路设计基础 > 补充内容 > 关于层叠式电感

<< >> <

>

↵

8 of 14

• 层间电容与自谐振频率 [3]

C1

C2 1 ------C eq ≈ 2 4 ∑ C i + C n 3n i=1

n–1

(1)

C3

– n 为层数,层间电容 C1, C2 比底层到地电容 C3 对 总电容的影响更大,因此为了提高自谐振频率, 需要考虑拉开各层间的距离

t=0.8µm tox=7µm

f=40GHz

射频集成电路设计基础 > 补充内容 > 硅衬底上的传输线

<< >> <

>

↵

12 of 14

• 共面波导 (Coplanar Waveguid, CPW) [2]

Ground

Ground w s SiO2 t tox

Si Substrate

– 信号电场主要集中在信号线与接地平面之间,仅有部分进入衬底 – 对固定特征阻抗, W/S 之比固定,减小导线宽度必须同时减小间距 S,于是 一方面趋肤效应增大了导线电阻,另一方面导线与地平面耦合得更紧密,减 小了衬底损耗;与电感的情况类似,需要根据工作频率选择尺寸以减小损耗

0.327λ y0=1 yL

zL

j0.2

0

0.2

0.5

θ1

1

2

−j0.2

yL

−j0.5 −j1

接入点 2

−j2

l2

−j2

射频集成电路设计基础 > 补充内容 > 短截线 (Stub) 阻抗匹配举例

<< >> <

>

↵

5 of 14

– Stub 可以短路或开路,用来获 得一个纯归一化电纳 −j2 ;假 设 Stub 特征阻抗与主传输线相 同,并且使用短路线,从图中 可得 θ 2 = 53.1 ° ,因此 l 2 = 0.074 λ

射频集成电路设计基础 > 补充内容 > 硅衬底上的传输线

<< >> <

>

↵

13 of 14

Table 1: 金属厚度为 2µm 时给定阻抗和 宽度对应的间距 S (µm)

Z0 \ W

5µm 10µm 20µm 40µm

40Ω 1.25 2.5 5 10

60Ω 5 10 20 40

90Ω 20 40 80 160

–j θ1

0 e

–j θ2

b1 b2

0 e 0 e

–j θ2

0

, 则 [ θ –1 ] = e

0 , 上式可写成

j θ2

0

0 e

[ a ′ ] = [ θ –1 ] [ a ] , [ b ′ ] = [ θ ] [ b ] 如果无传输线时网络的 S 参数是 [S],加上传输线后的 S 参数是 [S'],则 [b] = [S][a] , [b′] = [S′][a′] 于是 [ θ ] [ b ] = [ S ′ ] [ θ –1 ] [ a ] , [ b ] = [ θ –1 ] [ S ′ ] [ θ –1 ] [ a ] 亦即 [ S ] = [ θ –1 ] [ S ′ ] [ θ –1 ] , [ S ′ ] = [ θ ] [ S ] [ θ ]

Ceq

Ltot

射频集成电路设计基础 > 补充内容 > 关于层叠式电感

<< >> <

>

↵

9 of 14

有源电感

• 回转器+电容 (Gyrator-C) 的实现方式

V1 V1 Z in = ---- = ------------I1 gm2 V2 1 V 2 = g m 1 V 1 ----sC sC - = sL Z in = --------------gm1 gm2 C L = --------------gm1 gm2

V1 I1 gm1 gm2 I2 V1 V2 I1 I2

gm2V2

gm1V1 V2

C

C

– 实际上,这里的目的是要使输入电流滞后输入电压 90°,为了达到这一目 的,使用了两次电压-电流转换:

» gm1 将 V1 转成电流对 C 充电,从而得到了滞后 V1 90° 的 V2 » gm2 将 V2 转成输入电流 I1,由于 I1 与 V2 同相,因此也滞后 V1 90°

– 微带线和共面波导可以结合起来使 用,衬底被完全屏蔽; W=S=20µm, tox=8µm 测得的损耗在 10GHz 约为 0.2dB/mm, 在 50GHz 约 为 0.5dB/mm

射频集成电路设计基础 > 补充内容 > 硅衬底上的传输线

<< >> <

>

↵

14 of 14

参考文献

[1] [2] B. Razavi, “Prospects of CMOS Technology for High-Speed Optical Communication Circuits,” IEEE J. Solid-State Circuits, vol. 37, pp. 1135-1145, Sep. 2002. B. Kleveland, C. Diaz, D. Vook, L. Madden, T. Lee and S. Wong, “Exploiting CMOS Reverse Interconnect Scaling in Multigigaherz Amplifier and Oscillator Design,” IEEE J. Solid-State Circuits, vol. 36, pp. 1480-1488, Oct. 2001. A. Zolfaghari, A. Chan and B. Razavi, “Stacked Inductors and Transformers in CMOS Technology,” IEEE J. Solid-State Circuits, vol. 36, pp. 620-628, April 2001.

[3]

射频集成电路设计基础 > 补充内容 > 参考文献

<< >> <

>

↵

<< >> < > ↵

射频集成电路设计基础 > 补充内容 线 ( St u b ) 阻 抗 匹 配 举 例

• 确定两个参数:

– Stub 的接入位置 – Stub 的长度 Stub 的特征阻抗不必与主传输线相同,但相同 的特征阻抗会带来一些方便,同时,由于 Stub 是并联接入的,更适合在导纳圆图上设计

射频集成电路设计基础 > 补充内容 >S 参数与参考平面 j θ1 j θ2

, ,

b 1' = b 1 e b 2' = b 2 e

–j θ1 –j θ2

<< >> <

>

↵

2 of 14

a1 ′ a2 ′ 令 [θ] = e

–j θ1

= e

j θ1

0

j θ2

a1 a2

,

b1 ′ b2 ′

j θ1

= e

l1 l2 a1 b1 a1' b1'

Source

[S]

a2 b2

a2' b2'

Load

– 由传输线理论可知,传输线对入射和反射波所起的是延时或移相的作用,令 θ 1 = β l 1 ,θ 2 = β l 2 ,则以下关系成立: a 1' = a 1 e a 2' = a 2 e 或者使用矩阵的形式

• 微带线 [1]

– 为阻止电场进入衬底引起损耗,可用低 层金属作为接地平面,构成微带线 – 顶层金属距离衬底的距离随工艺中金属 层数的增加而增加,因此所形成微带线 的特征阻抗不至于过小 – 增加信号线宽度使特征阻抗与衰减常数 同时减小 (why?)

SiO2 w t tox

Si Substrate

Microstrip

y0=1 1+jb

l1

yL

<< >> <

>

↵

4 of 14

– 在本例中

z L = 0.286 + j 0.795 ,

y L = 0.4 – j 1.114 ,等反射系数圆

等反射系数圆

j0.5

j1

接入点 1

j2

与单位导纳圆有两个交点 1+j2 和 1-j2,这是两个可能的 Stub 接入点 – 我们选择接入点 1,可以读出 从 yL 到 1+j2 反射系数变化了 235.2 度,由于 θ 1 = 2 β l 1 , βλ = 2 π , 所以 l 1 = 0.327 λ , 下一步求 Stub 的长度 l2

+ vgs − i vin in

gmvgs

入电压 90°,因此输入阻抗呈感性 » 实际工作受 Cgd 和 gds 很大限制

R g C gs R g ≈ ----L ≈ ------------gm ωT