一种基于FPGA的数字下变频方法

一种基于FPGA的数字下变频方法

本 文论 述 数字下 变频 技 术 的一种 F GA 实现 方 法 , 比较 低 的 系统 成本 , P 用 实现 比较 高 的谱 分 辨 率 的数

字接 收系统 , 完成 对 气象 信号 的有效 处 理 。实 际的 系统 选 用 4 MHz时钟 对 6 MHz的 雷 达 中频 信号 采样 , 8 0 然后 经过 F GA 的数字 下 变频及 其滤 波处理 , 到信 号的包 络和 相位信 息 。 P 得

【 要 】 提 出 用 FP 摘 GA 器 件 实 现 一 个 完 整 的 数 字 下 变频 系 统 的 方 法 , 出 Ve i g 给 rl HDL语 言 o

的描述 , 实现 高效的运 算 结构 , 小 了运 算量 , 高 了系统性 能。本 系统 已经在 某 型 气 象雷 达 的数 减 提 字接 收 系统 中得到 采 用 , 参数 得 到验证 , 能优 良 。 性 关键词: P F GA; r o HDL; Vei g l 欠采 样技 术 ; 字 下 变频 ; 数 多抽 样率 系统

( di Xi an Uni r iy,X i a ve s t ’ n,7 0 71 10 )

Ab t a t A s r c : met d o sng FPG A e ie t e ie d g t ldo o ve tn ys e i r s n e ho f u i - d v c O r al i ia wn c n r i g s t m s p e e t d,a d z n t srpi f hede c i ton o Ve iogHDL l n a e i i e O t a t g fii n y op r ton l t u t r i u — rl a gu g s g v n S h t he hi h e fce c e a i a s r c u e s f l fle ild,a d t pe an s r du e nd t y t m e f ma e i n nc d Thi e ho sbe n a p e n he o r d i e c d a hes s e p ror nc se ha e . sm t d ha e do t d i h gia e e v n u ys e ofa c r a n me e o o c lr da ,a d t p cfc ton r e iid a d n t e di t lr c i i g s bs t m e t i t or l gia a r n he s e iia i s a e v rfe n t e pe f r a c s p r e t h ro m n e i e f c .

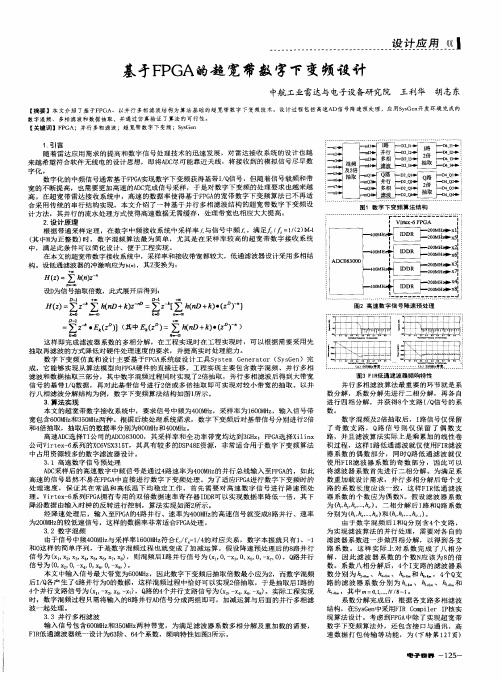

基于FPGA的超宽带数字下变频设计

1 引 言

随 着 雷 达 应 用 需 求 的 提 高和 数 字 信 号 处 理 技 术 的 迅 速 发 展 ,对 雷达 接 收 系 统 的设 计 也越 来越希望符合软件无 线电的设计思想 ,即将A D C 尽可能靠近天线 ,将接 收到的模 拟信号尽早数

字化 。 数 字 化 的 中 频信 号 通 常 基 于F P G A 实现 数 字 下 变 频 获 得 基 带 I / Q 信 号 , 但 随 着 信 号 载 频 和 带 宽 的不 断提 高 , 也 需 要 更 加 高 速 的 A D C 完 成 信 号 采 样 ,于 是 对 数 字 下 变频 的 处 理 要 求 也 越 来 越 高 。在 超 宽 带 雷 达 接 收 系 统 中 , 高速 的 数 据 率 使 得 基 于 F P G A 的宽 带 数 字 下 变 频 算 法 己 不 再 适 合 采 用 传 统 的 串 行 结 构 实 现 ,本 文 介 绍 了一 种 基 于 并 行 多 相 滤 波 结 构 的 超 宽 带 数 字 下 变 频 设 计 方法 , 其 并 行 的 流 水 处 理 方 式 使 得 高 速 数 据 无 需缓 存 , 处理 带 宽 也 相 应 大 大 提 高 。 2 . 设 计原 理 根 据 带 通 采 样 定 理 ,在 数 字 中 频 接 收 系 统 中 采样 率 与 信 号 中频 。满 足 / =1 / ( 2 ) M- 1

日 ( z ) :∑ h ( n ) z

月-

设D 为信 号 抽 取 倍 数 , 此式 展 开 后 得 到 :

D- J + ∞ D- 1 - 嘲

—4 0 0 M H I D D R _; l o 0 M H

图 2 高 一2 0 0 MH m l I  ̄ X 4

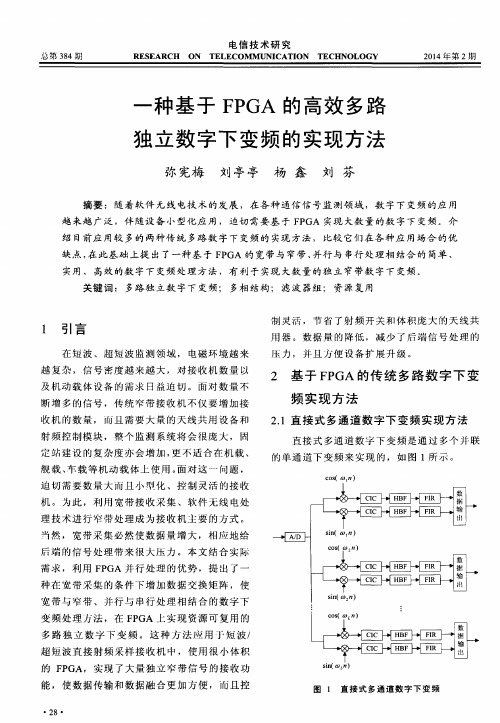

一种基于FPGA的高效多路独立数字下变频的实现方法

总第 3 8 4期 RE S E A RC H ON T E L E COMM U NI CA T I ON T EC HN oL oGY 2 0 1 4年 第 2期

一

种基于 F P G A 的高效 多路

独 立数 字 下 变 频 的实 现 方法

弥 宪梅 刘 亭 亭 杨 鑫 刘 芬

收 机 的 数 量 , 而 且 需 要 大 量 的天 线 共 用 设 备 和

射 频 控 制 模 块 , 整 个 监 测 系 统 将 会 很 庞 大 , 同 定站 建设 的复杂度亦会增 加 , 更不适 合在机载 、

舰载 、 车 载等机动载 体上使 用 。 面对这一 问题 ,

迫 切 需 要 数 量 大 而 且 小 型 化 、控 制 灵 活 的 接 收 机 。 为 此 ,利 用 宽 带 接 收 采 集 、 软 件 无 线 电处 理技 术进行 窄带处理成 为接 收机土要 的方式 。

能 , 使 数 据 传 输 和 数 据 融 合 更 加 方 便 ,而 且 控

・2 8・ s i n ( £ " )

图 1 直 接 式 多通 道 数 字下 变频

科技论文:一种基于 F P G A 的高 效 多 路 独 立 数 字 下 变 频 的 实 现 方 法

图 中共 有 £个 通 道 , 可 分 别 对 A/ D 采 样 带

种 滤波器组进 行多相分解 , 得 到 均 匀 DF T滤 波

宽 内 的 £个 信 号 ( 由 £个 本 振 频 率 l , ∞ 一

£

器 组 的 推 导

得 出均 匀 DF T滤 波 器 组 多相 结 构 如 图 3所 示 。

决 定 )进 行 接 收 处 理 。根 据 带 宽及 采 样 率 需

数字下变频FPGA实现

I

时钟 重

配置

I_W

S W

Q 2选1 I_N BUS

MUX

多相滤波结

2

构的宽带滤 Q_W 选

M c

I Q_N

波器

1B

中频

IT

S

AD 信号

C

6645

NCO Q H

BP U 接口 输

S

出

开关

S

配置

至

FPGA EP2S60F672C4

I Q

I_N W

窄带滤

I

波器组 Q_N T

C

I_N Q_N

M 参数 U DDC X 参数

…

−2π −π −ω1 0 ω1 π 2π ω

(a)下变频前实信号频谱

X (e jω )

−ω1 0

ω

(b)复本振信号频谱

X (e jω )

A

…

…

−2ω1 0 2ω1

ω

(c)混频后的信号频谱

图 4 数字下变频完成的频谱搬移

2) 数字下变频器两种典型结构

a) 传统窄带数字下变频结构

图 5 传统窄带数字下变频结构

本系统的数据流程如图 1 所示,A/D 采样的中频模拟信号输出至 FPGA, FPGA 中的 VB-DDC 将中频信号下变频至基带,再通过 McBSP 接口将基带信号 传给 DSP 进行解调、功率谱估计等数字信号处理,最后 DSP 再将结果通过以太 网送至上位机 PC 进行显示。同时,VB-DDC 可通过 McBSP 接口接受上位机 PC 传来的配置参数,实现 DDC 的动态配置。

Receivers. The Variable-Bandwidth Digital Down-Converter (VB-DDC) ,which is suitable for Wideband Digital Receiver, is implemented in FPGA chip Stratix II EP2S60F672C4. The VB-DDC combines the advantages of traditional digital down-conversion architectures and poly-phase filter architectures, realizes efficient high-speed processing for input IF signal, and could configure the bandwidth of signal processing flexibly in a large range. Hardware test result shows the effectiveness of this design.

数字下变频电路的FPGA实现

数字下变频电路的FPGA实现随着数字化时代的到来,数字信号处理技术已经成为了许多领域中不可或缺的一部分。

其中,数字下变频技术是一种非常重要的数字信号处理技术,被广泛应用于雷达、通信、音频处理等领域。

本文将介绍数字下变频电路的FPGA实现。

数字下变频电路的基本原理数字下变频电路的基本原理是将输入信号进行混频,将高频信号转换为低频信号,并对低频信号进行采样和滤波,得到一个纯净的低频信号。

数字下变频电路通常由数字信号处理器、数字乘法器和数字低通滤波器等组成。

FPGA实现数字下变频电路的优势 FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,能够根据需要实现各种数字电路。

与传统的数字信号处理芯片相比,FPGA具有以下优势:高速并行处理能力:FPGA内部具有大量的可编程逻辑器件,可以实现高速并行处理,提高处理速度和效率。

灵活性:FPGA可以通过重新编程实现不同的数字电路,方便灵活,可以快速适应不同的应用场景。

可靠性:FPGA内部具有严格的质量保证措施,保证了数字电路的可靠性和稳定性。

设计数字下变频电路的算法:根据具体应用场景和要求,利用MATLAB 等软件设计数字下变频电路的算法。

将算法转换为硬件描述语言:将设计的数字下变频电路算法转换为硬件描述语言(如VHDL或Verilog),并利用EDA工具进行仿真和验证。

将硬件描述语言编译成二进制文件:将生成的硬件描述语言编译成二进制文件,以便在FPGA上实现。

将二进制文件下载到FPGA中:将生成的二进制文件下载到FPGA中,通过调试和测试,最终实现数字下变频电路。

结论数字下变频电路的FPGA实现具有高速并行处理能力、灵活性和可靠性等优势,已经被广泛应用于雷达、通信、音频处理等领域。

通过设计算法、转换为硬件描述语言、编译成二进制文件以及下载到FPGA中等步骤,可以实现数字下变频电路的高效、快速和可靠实现。

数字下变频电路是一种重要的信号处理单元,它在通信、雷达、电子对抗等领域有着广泛的应用。

基于FPGA的DDC(数字下变频)设计与实现

在早期的雷达收发系统中,都是采用模拟器件来实现各个功能模块,设计过程中经常会出现温度漂移、增益变化等问题.相对于模拟电路来说,数字电路具有可自检、可编程等优点,上面所述的系统很多部分都已经逐步数字化.在数字化进程中,数字信号处理技术的应用也受到了雷达系统研究工作者的重视,成为相关积累(如FFT、数字滤波、脉冲压缩等)、非相关积累(视频积累)、目标检测以及图像处理等功能的技术保证。随着数字信号处理理论的不断成熟和完善,微电子技术的飞速发展,雷达技术和其它的电子信息化技术的发展,尤其是软件无线电技术的兴起,更加方便了雷达数字化系统的实现。在这样的发展趋势下,除了微波发射和射频部分,整个雷达系统将全部由数字电路实现,在数字信号处理的优势能得到全面的发挥的同时,还使具有体制标准化、系统数字化,功能模块化,低功耗,高度开放性以及灵活性等性能,这将成为了现代雷达系统的关键技术和发展趋势[]。在现今的高科技发展的时代,人们纷纷打起的信息战和电子战,雷达系统在其中扮演的角色尤为重要。为了能更好的适应现代战争的需求,对现今的雷达系统也提出抗干扰、反隐形,具有高分辨力以及强大的自我生存等能力,高要求的提出,使得雷达信号处理技术的研究也得到了快速的进步.目前雷达信号处理正在由视频处理阶段向中频处理阶段迈进,目的就是实现雷达中频以下的处理全部数字化,研究热点.

微系统设计、测试与控制

课程大作业之

基于FPGA的DDC(数字下变频)的设计与仿真

基于FPGA的数字正交混频变换算法的实现,数字正交,实时处理.

基于FPGA的数字正交混频变换算法的实现,数字正交,实时处理,多相滤波,FPGA0引言传统的正交下变频是通过对模拟I、Q输出直接采样数字化来实现的,由于I、Q两路模拟乘法器、低通模拟器本身的不一致性、不稳定性,使I、Q通道很难达到一致,并且零漂比较大,长期稳定性不好,不能满足高性能电子战设备的要求。

为此,人们提出了对中频信号直接采样,经过混频来实现正交数字下变频的方案,这种下变频的方法可以实现很高精度的正交混频,能满足高镜频抑制的要求。

采用可编程器件FPGA对该算法流程进行实现,能满足0 引言传统的正交下变频是通过对模拟I、Q输出直接采样数字化来实现的,由于I、Q两路模拟乘法器、低通模拟器本身的不一致性、不稳定性,使I、Q通道很难达到一致,并且零漂比较大,长期稳定性不好,不能满足高性能电子战设备的要求。

为此,人们提出了对中频信号直接采样,经过混频来实现正交数字下变频的方案,这种下变频的方法可以实现很高精度的正交混频,能满足高镜频抑制的要求。

采用可编程器件FPGA对该算法流程进行实现,能满足在高采样率下的信号时实处理要求,在电子战领域中有着重要的意义。

1 数字正交混频变换原理所谓数字正交混频变换实际上就是先对模拟信号x(t)通过A/D采样数宁化后形成数字化序列x(n),然后与2个正交本振序列cos(ω0n)和sin(ω0n)相乘,再通过数字低通滤波来实现,如图1所示。

为了能够详细地阐述该算法的FPGA实现流程,本文将用一个具体的设计实例,给出2种不同的实现方法(不同的FPGA内部模块结构),比较其优劣,最后给出结论。

该设计是对输入信号为中频70 MHz,带宽20 MHz的线性调频信号做数字正交混频变换,本振频率为70 MHz(即图1中的2个本振序列分别为cos(2π70Mn)和sin(2π70Mn)),将其中频搬移到0 MHz,分成实部(real)和虚部(imag)2路信号。

然后对该2路信号做低通滤波,最后分别做1/8抽取输出。

基于FPGA的宽带信号数字下变频设计与实现

De g L n,Ka g Hu i i iHo g o,Y h L n n a n a q ,L n b a i

( nv syo l t n c nea dTcn l yo C ia hn d 17 1 U i r t e r i Si c n eh o g hn ,C eg u6 1 3 ) e i fE c o c e o f

wh c a aif e u r me t fr a —i r c si g be a s fl w e o r e o c p n y r t n h r r c s i g ih c n s tsy r q ie n so e ltme p o e sn c u e o o r s u c c u a c ae a d s otp o e sn tme d l y i ea . Ke wo d y r s:p lph s le ;d srb t d a g rt m ;DDC;FPGA o y a e f tr it u e lo h i i i

1 引言

针对数字化雷达接收机采样前端 , 目前市面上 已经 出现 了很 多超 高速 多 比特 的 AI 采样 芯片 , D 其

采样 速度 可达 到几 个 Gp , 由此 带来 的 问题 就 是 ss而

搬 移 , 由低 通滤 波 器 滤 波后 , 行 多 倍 抽取 , 到 再 进 达

降速的效果 。对于宽带信 号, 经过 高速 A D采样 / 后, 数据速率可达几 Gp , ss 由于常规的数字 下变频 方法 , 工作速 率 与 A C输 出数据 的速 率一致 , D 而

FG P A器 件 无 法 达 到 如 此 高 的运 行 速 度 , 因此 采 用 常规 的数 字 下变频 方法无 法 实现对 宽带 中频信 号 的

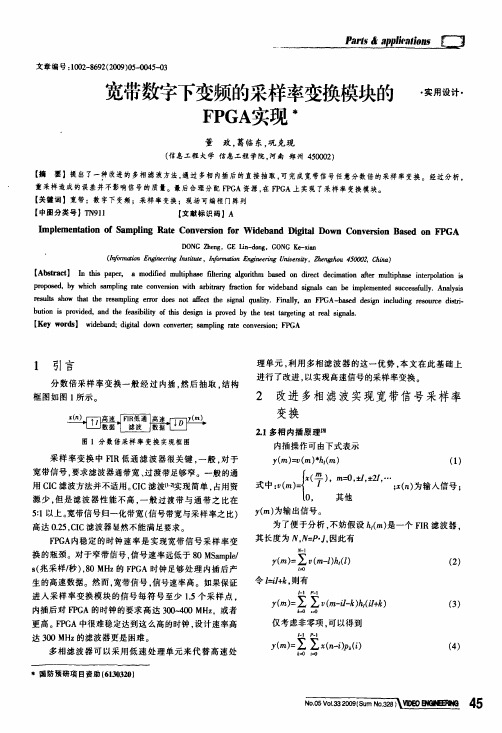

宽带数字下变频的采样率变换模块的FPGA实现

文章编号:1002—8692(2009)05-0045-03…墅塑垒型堂堂[,宽带数字下变频的采样率变换模块的FPG A实现木实用设计董政,葛临东,巩克现(信息工程大学信息工程学院,河南郑州450002)【摘要】提出了一种改进的多相滤波方法,通过多相内插后的直接抽取,可完成宽带信号任意分数倍的采样率变换。

经过分析,重采样造成的误差并不影响信号的质量。

最后合理分配FPG A资源,在FPG A上实现了采样率变换模块。

【关键词】宽带;数字下变频;采样率变换;现场可编程门阵列【中围分类号】TN911【文献标识码】AI m pl e m e nt a t i on of Sam pl i ng R at e C onve r si on f or W i deband D i gi t al D ow n C onver si on B a se d o n FPG AD O N G Zhe ng,G E“n-dol l g,G O N G K e--xian(I n f or m at i o n E喀腿e魄I nstitute。

Inform at ion E ngi neer i ng U ni v er s i t y.Zher增zhou450002,C hi M)【A bs t r act】In t hi s pa pe r,a m od i f i ed m u l t i【p ha se f il te r ing al g or i t hm bas ed o n di rect de ci m a t i o n aft er m ul t i pha se i nt erpol at i on i s pr opo sed,b y w hi ch sa m pl i n g r a te conver si on w i t h ar bit r ar y f r act ion f or w i de b a n d s i gnal s Cal l be i m pl e m e nt ed s ucces s f ul l y.A nal ys i s r esul t s show t hat t he r cs a m ph ng el T or does not a ff e ct t he s i g nal qua l i t y,F i na l l y.彻F PG A-bas ed desi gn i nc l udi ng r es o ur ce di st r i but i on i s pr ovi d ed,and t he f ea s ibi li t y of t hi s des i gn i s pr ove d by t he t est t ar get i ng at r eal s i gna l s.【K ey w ords】w i deba nd;di gi t al do w n conver t er;,s am pl i ng r at e c onve r si on;FP G A1引言分数倍采样率变换一般经过内插。

基于FPGA的数字下变频的实现

T e Re e r h o g a o e sn n I gt lRe ev r h s a c fSin l Pr c s ig i Dii c ie F a

ZHU n—h ng, Yu a DENG hi u Z —h i

( u a o eefI om t n C agh 12 0 C i ) H n nC lg n r ai , hnsa4 0 0 ,hn l o f o a

sain s se i CDMA b l o tto y tm n W mo ie c mmu i ain n t r wo l e lz h el p n in lc v r g n c to ewo k, u d r aie t e c l ho e sg a o e a e

灵 活 性

图 1 A I 、 P A、 S 能 比较 SC F G D P性

FG P A芯 片有着 规整 的 内部逻 辑 阵列 和丰 富 的

连线资 源 , 合 于 处理 数 字 系 统 的任 务 。但是 长期 适

以来 , 一直用 于 系统逻辑 或 时序控 制上 , 少有信号 很 处 理方 面 的应 用 。其原 因 主要是 因为 在 F G P A中 缺

关键词 : P A; F G 处理 ; 数字 ; 滤波

D I 码 :0 3 6 /.sn 10 2 7 . 0 0 0 . 1 O 编 1 . 9 9 ji .0 2— 2 9 2 1 .6 0 0 s

中图分 类号 : N 2 T 9

文献标 识 码 : A

文章编 号 :0 2— 2 9 2 1 0 1 0 2 7 (0 0)6—0 2 0 0 7— 3

Ab ta t B sd o h i u so fte s u tr fdgtld wn—c n es n( sr c : a e n te ds sin o h t cu eo ii o c r a o v ri DDC)i o wae o n sf r t

数字下变频的FPGA实现

1 引言数字下变频DDC(digital down lonvwrsionl作为系统前端A/D转换器与后端通用DSP器件间的桥梁,通过降低数据流的速率,将低速数据送给后端通用DSP器件处理,其性能的优劣将对整个软件无线电系统的稳定性产生直接影响。

采用专用DDC器件完成数字下变频,虽具有抽取比大、性能稳定等优点,但价格昂贵,灵活性不强,不能充分体现软件无线电的优势。

FPGA工艺发展迅速,处理能力大大增强,相对于ASIC,DSP,其具有吞吐量高、开发周期短、可实现在线重构诸多优势。

基于这些优点,FPGA在软件无线电的研发中具有重要作用。

2 数字下变频系统数字下变频器在软件无线电系统中完成的功能结构如图1所示,其中包括直接数字频率合成器DDS(direct digital synthesizer)、数字混频器、FIR滤波器、抽取等模块。

原始模拟中频信号经A/D转换器带通采样后得到数字中频信号,输入DDC后先与DDS产生的两路正交本振信号相乘(数字混频),将数字中频搬移到基带。

混频后得到的数据率和采样率一致,后级FIR滤波器要达到该处理速率。

硬件实现相当困难,因此首先通过抽取模块大大降低数据速率,然后使用高阶FIR低通滤波器对整个信道整形滤波。

滤波输出的两路正基带信号交由下一级DSP器件进行处理。

2.1 混频器的FPGA实现数字混频器将原始采样信号与查找表生成的正、余弦波形分别相乘,最终得到两路互为正交的信号。

由于输入信号的采样率较高,因此要求混频器的处理速度大于等于信号采样率。

单通道的数字下变频系统需要两个数字混频器.也就是乘法器。

XC2V1000器件内嵌64个18×18位硬件乘法器,其最高工作频率为500 MHz,因此采用硬件乘法器完全能够满足混频器的设计要求。

使用Xilinx公司的Multiplier IP核可以轻松实现硬件乘法器的配置。

该设计中采用两路14位的输入信号,输出信号也为14位。

数字下变频的设计及其在FPGA中的实现

数字下变频的设计及其在FPGA中的实现作者:王平李建海刘保华马二涛来源:《现代电子技术》2010年第01期摘要:分析数字下变频结构及其实现方法,重点研究如何基于FPGA实现数字下变频的功能,并通过仿真分析验证该实现方法的正确性。

结果表明,该实现方法可用于各类数字通信系统中频信号的数字下变频处理,具有一定的实用价值。

关键词:数字下变频;混频器;数字滤波器;FPGA中图分类号:TP274文献标识码:A文章编号:1004-373X(2010)01-055-03Design of Digital Down Converter and Its Implement Based on FPGAWANG Ping,LI Jianhai,LIU Baohua,MA Ertao(Airforce Engineering University,Xi′an,710038,China)Abstract:The configuration of digital down converter and its implement method are analysed,and how to realize digital down converter′ function based on FPGA in stress is studied,the correctness of the method is validated by simulation. The results indicate that the method can be used in many kinds of intermediate frequency digital down converter processing,thus it has definite practicality value.Keywords:digital down conversion;mixer;digital filter;FPGA0 引言自20世纪90年代以来,软件无线电技术引发了移动通信领域的一场革新,数字下变频技术是软件无线电技术实现过程中的一个重要环节,其完成的任务主要是:一方面将包含所有信道的宽带信号进行信道分离,分别提取需要的窄带信号;另一方面,对于分离的窄带信号,可以大大降低其采样速率,即降低数据量,缓解基带部分的处理压力[1]。

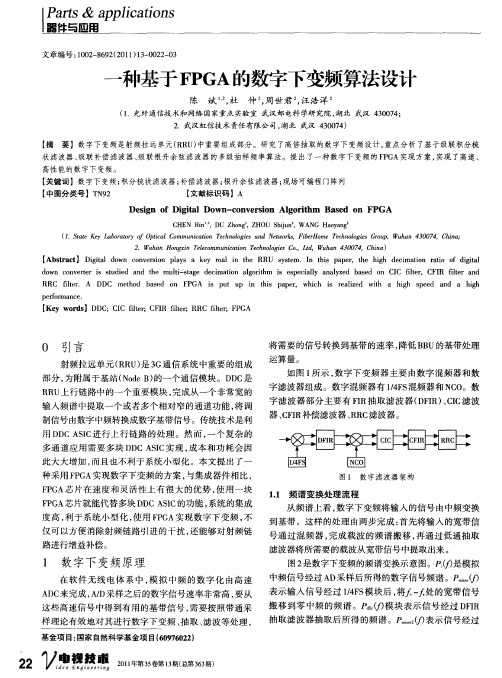

一种基于FPGA的数字下变频算法设计

样理论有效地 对其进 行数字下变频 、 抽取 、 滤波等处理 ,

基金 项 目 : 国家 自然 科 学 基金 项 目 (0 7 02 6962 )

表示输入信号经过 1 F 模块后 , /S 4 将 ~ 处的宽带信号 .

搬 移 到零 中频 的频 谱 。 () 块表 示信 号经过 D I 厂模 FR

CI FR补偿滤 波器 可以采用 Ma a t b中的 f t l l a o 工具进 行 do

…

~

~

一

…

一

一

一

~

}

、

莺

I

’

}

{

j

设计 。图4 是系统 中所采 用的 CC滤波器 的频率 响应 曲 I

线 。图5 C I 是 FR补偿滤波器的频率 响应 曲线 。 1 R . 3 RC滤波器

图2 频 谱 变 化 流 程 图

1 C C滤 波 器 和 C I  ̄偿 滤 波 器 . 2 I F R: b

CC I 滤波器是指该滤波器 的冲激响应为

坳怯 =

的 Z 换 为 变

㈩

图 5 C I 波 器 的频 率 响 应 ( 图) FR滤 截

式 中 : 表示微分延 迟。根据 Z变换 的定义 , I CC滤波器

度高 , 于系统小 型化 , 利 使用 F G P A实现数字 下变频 , 不 仅可以方便消除射频链路 引进 的干扰 , 还能够对射频链 路进行增益补偿 。

从频谱上看 , 字下变频将输 人的信号 由中频变换 数

到基带 。这样 的处 理 由两步完成 : 首先将输入 的宽带信

号通 过混频器 , 完成 载波 的频谱搬 移 , 通过低 通抽取 再

变频器考试题

变频器考试题一、选择题1、下列哪个品牌不属于变频器?(A)西门子(B)三菱(C)汇川(D)富士2、变频器的主要功能是什么?(A)调节电机速度(B)增加电机功率(C)降低电机电流(D)保护电机3、变频器的调速原理是什么?(A)改变电源频率(B)改变电源电压(C)改变电机负载(D)以上都不是4、变频器的频率范围一般是多少?(A)1到1000赫兹(B)5到500赫兹(C)20到200赫兹(D)50到5000赫兹5、变频器的加速时间是指什么?(A)电机从静止到最大速度所需的时间(B)电机从最大速度到最小速度所需的时间(C)电机从最小速度到最大速度所需的时间(D)以上都不是二、简答题6、请简述变频器在工业生产中的应用。

61、请说明变频器的主要组成部分及其作用。

611、如何正确使用和维护变频器?6111、什么是变频器的过载和过热保护?变频器的频率调整对电机有什么影响?三、综合题11.请描述一下变频器的工作流程,包括输入、输出和控制部分。

12.假设一台变频器无法正常工作,请列出可能的故障原因和相应的解决方法。

变频器培训考试题答案一、选择题1、在变频器控制中,我们通常使用哪种控制模式?A.电压控制B.电流控制C.频率控制D.转速控制答案:A.电压控制解释:变频器通过改变电源电压来控制电动机的转速,因此通常使用电压控制模式。

2、下列哪个参数是变频器的主要调节参数?A.输入电压B.输出电压C.频率D.电动机转速答案:C.频率解释:变频器的主要调节参数是频率,通过改变电源的频率来改变电动机的转速。

3、在变频器的使用过程中,我们需要注意哪些安全问题?A.避免金属导体接触电线B.避免在变频器运行时进行维修操作C.可以在潮湿的环境下使用变频器D.可以将变频器连接到直流电源上答案:B.避免在变频器运行时进行维修操作解释:在变频器运行时,其内部电路处于高电压状态,进行维修操作可能会导致触电事故。

因此,必须在变频器断电后才能进行维修操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

*收稿日期:2006-09-11文章编号:1008-8652(2007)02-84-06一种基于FPGA 的数字下变频方法涂维政 刘书明(西安电子科技大学 西安 710071)=摘要> 提出用FPGA 器件实现一个完整的数字下变频系统的方法,给出VerilogH DL 语言的描述,实现高效的运算结构,减小了运算量,提高了系统性能。

本系统已经在某型气象雷达的数字接收系统中得到采用,参数得到验证,性能优良。

关键词:FPGA ;VerilogH DL;欠采样技术;数字下变频;多抽样率系统中图分类号:T N74211 文献标识码:AA Method of Digital Down Converting Based on FPGAT u Weizheng Liu Shuming(X idian Univ ersity ,X i .an,710071)Abstract :A method of using FPGA device to realize dig ital dow n converting system is presented,and the descr iptio n of Verilog H DL language is g iv en so that the hig h efficiency operational structure is fu-l filled,and the oper and is reduced and the system perform ance is enhanced.T his m ethod has been adopted in the digital receiving subsy stem of a certain m eteoro logical radar,and the specificatio ns are verified and the perfo rmance is perfect.Keywords :FPGA;Verilog H DL;under sampling techno log y;digital dow n converter;multiple sam -pling rate system随着数字技术的飞速进步和发展,FPGA 器件因其高速、可编程、模块化的特点而被大量采用。

同时,诸如数字下变频等一系列新的数字信号处理方法的提出,为降低系统成本提供了可能,相关的多抽样率系统理论,更是大大的降低了数字系统的运算量,明显的提升了系统性能。

本文论述数字下变频技术的一种FPGA 实现方法,用比较低的系统成本,实现比较高的谱分辨率的数字接收系统,完成对气象信号的有效处理。

实际的系统选用48M H z 时钟对60MH z 的雷达中频信号采样,然后经过FPGA 的数字下变频及其滤波处理,得到信号的包络和相位信息。

1 欠采样技术为了降低对ADC 器件的要求,对于低通、带通信号,可以用带通信号的采样方法,在低于奈奎斯特采样率时进行数模转换:只要采样率不低于两倍信号带宽f h -f l ,时域的采样就不会导致信号频谱的混叠,如公式(1)所示:2f h N +1[f S [2f l N(1)其中,N 为自然数,且1[N [f l f h -f l。

84原来的信号可由公式(2)得到:f (t)=2BT s E f (nT s )@sin [P B (t -nT s )][P B (t -nT s )]@co s [2P f c (t -nT s )](2)其中,f c =12(f l +f h )为中心频率,B =f h -f l 为信号带宽,T s =1f s为采样间隔。

由此可见,可以用比信号最高频率2倍低很多的采样频率来进行欠采样。

2 数字下变频技术对AD 采样信号进行混频、低通和抽取,可得到和信号带宽匹配的基带采样信号。

设中频采样信号为:x (n)=cos [X 0nT s +U (NT s )]该中频信号与两个正交的信号cos (X 0nT s )、sin (X 0nT s )混频:cos [X 0nT s +U (nT s )]@cos (X 0nT s )=12co s [U (nT s )]+12cos [2X 0nT s +U (nT s )]=12I (nT s )+12cos [2X 0nT s +U (nT s )](3)cos [X 0nT s +U (nT s )]@sin (X 0nT s )=-12sin [U (nT s )]+12sin [2X 0nT s +U (nT s )]=-12Q(nT s )+12sin [2X 0nT s +U (nT s )](4)公式(3)、(4)的信号,经过低通滤波器滤除上变频部分,就分别得到I 、Q两路信号。

图1 数字下变频器的原理图数字下变频器(Digital Dow n Converter,DDC)的组成包括数字混频器、正交信号产生部分和低通滤波器(LPF)三部分,其原理如图1所示。

选择采样频率:f s =4f 02M -1,其中,M 是满足f s \2B 的自然数。

对本文所提及的某气象雷达系统,中频信号频率为60MH z,采样频率为48M H z ,这时乘积因子变成如公式(5)、公式(6)所示:cos (nw 0/f s )=1,0,-1,0,1,0,-1,0,,,(5)sin (nw 0/f s )=0,1,0,-1,0,1,0,-1,,,(6)这样,混频的数字运算过程,就转化成求负、求和运算,简化了乘积混频实现的难度。

当前端的AD 输出为二进制补码格式时,求负操作,就等同于原来的二进制补码全部取反后加1。

VerilogH DL 实现的部分代码如下:alw ays @(posedge clock) //Co unt 采用Gray 编码,以便减少计数时的竞争风险;begincase (Co unt)2'b 00: Count =2'b 01;2'b 01:Count =2'b 11;2'b 11:Count =2'b 10;2'b 10:Count =2'b 00;default:Count =2'b 00;endcaseendalw ay s @(posedge clock) //某型气象雷达的数字下变频正交混频算法;begincase (Co unt)852'b 00: begin ... end2'b 01: begin ... end2'b 11: begin //下面就是乘以-1的操作;I_Out =~(Signal)+1;Q_Out =0;end2'b 10:begin ... enddefault:begin ... endendcaseend3 多抽样率低通滤波在保留信号希望的有效信息时,为了降低数据率,可以对数据进行抽取。

图2 抽取前后信号的频域关系示意图设x (n 1T 1)是连续信号x a (t)的采样序列,采样频率F 1=1/T 1H z ,即x (n 1T 1)=x a (n 1T 1)。

如果希望把数据率降低到原来的1/D ,可以直接对x (n 1T 1)每D 点抽取一点,抽取的点组成新序列y (n 2T 2),则新序列的采样率变为F 2=1/T 2H z 。

且有y (n 2T 2)=x (n 2DT 1)(7)当n 1=n 2D 时,y (n 2T 2)=x (n 1T 1)。

x (n 1T 1)的频谱为:X (e j X 1)=1T 1E ]k=-]X a (j X T -j k 8s a 1)(8)式中8s a 1=2P /T 1(rad/s ),也即采样频率。

上式也可写为:X (ej 8T 1)=X (e j X 1)|X 1=8T 1=1T 1E ]k=-]X a (j 8-j k 8sal )(9)86y (n 2T 2)和x (n 1T 1)频谱之间的关系为:Y(e j X 2)=E ]n 2=-]y (n 2T 2)e -j X 2n 2=1D E D -1k=0X (e j (X 1-2P k D ))(10)即Y(e j X 2)是的D 个平移样本之和,且2P /DT 1=8s a 1/D =8s a 2。

由于时域的抽取,就相当于频域的周期性延拓,当信号截止频率过宽时,就会引起频率混叠。

图2展示抽取前后信号的频域关系,其中的|Y(e j 8T 2)|就是混叠的效果。

因此,需要采取抗混叠滤波,就是在抽取之前,先对信号进行低通滤波,限制其频带在抽取后的采样率的1/2处。

抗混叠滤波的原理如图3所示。

图3 抗混叠滤波原理图图2中|X (e j 8T 2)|的频谱波形多了个虚线的矩形框h(n 1T 1),示意所加的低通滤波器,其截止频率应该满足8c c [8sa 2/2。

加上抗混叠滤波器之后的输出为|Y c (e j 8T 1)|。

当抽样率变化较大时,多级抽取可以更加有效地进行抽样率转换,明显降低计算量和存储要求,减轻滤波器的设计难度。

比如一个I 级抽取过程,总的抽取因子为M,则M 可以表示成各级抽取因子的乘积:M i =M 1M 2,M n ,M i 代表各级抽取因子,是个整数。

其他相应指标为:通带:0[f [f p ,通带截止频率点可以放宽在其阻带之前。

阻带:(f i -f s /2M )[f [f i-1/2, i =1,2,,,I ; f i =f i-1/M i , i =1,2,,,I 。

4 用V erilogH DL 实现FPGA 设计该型气象雷达的低通滤波器,要求关于0、P 、2P 点偶对称,且幅频特性都为正。

根据其对称结构,h[(n)T]=h[(N-1-n)T ],这样可以减少一半乘法运算量。

另外,根据多抽样率理论中的多相滤波技术,把数据抽取动作放在延迟单元之后,与系数相乘之前,这样假如抽取率为D,就可以把运算量降低到原来的1/D 。

采用这两种方法之后,系统运算量降低到原来的1/((2@D1)@(2@D2))=1/(4@D1@D2)。

比如,当前系统设计为D1为4抽样,D2为6抽样,则系统计算量降低到原来的1/96,效果非常明显。

在Ver ilogH DL 实现对称结构时,对于滤波器系数相同的因式,要写成这种形式:h1*(S[n]+S[N -1-n]),才会综合成只进行1次乘法、1次加法运算的结构。

如果写成h1*S[n]+h1*S[N-1-n]),则会综合成需要2次乘法、2次加法运算的结构。

在实现多相滤波时,针对某个抽样率D,可以先对时钟进行D 分频,然后利用分频后的时钟上升沿来触发一个经常性事件,在此经常性事件段里面进行累加、乘法操作即可。