数电判断题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

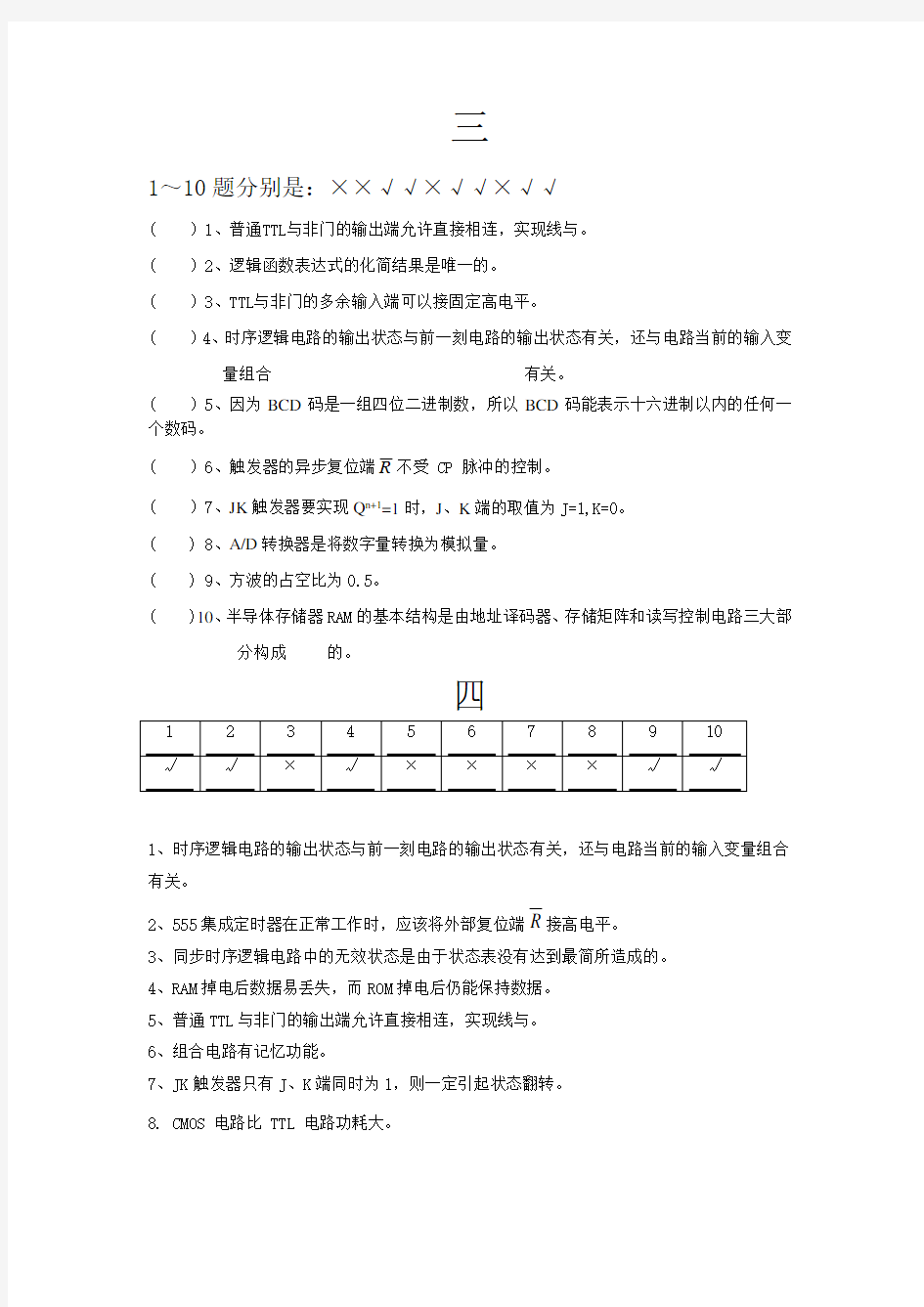

三

1~10题分别是:××√√×√√×√√

( )1、普通TTL与非门的输出端允许直接相连,实现线与。

( )2、逻辑函数表达式的化简结果是唯一的。

( )3、TTL与非门的多余输入端可以接固定高电平。

( )4、时序逻辑电路的输出状态与前一刻电路的输出状态有关,还与电路当前的输入变量组合有关。

( )5、因为BCD码是一组四位二进制数,所以BCD码能表示十六进制以内的任何一个数码。

( )6、触发器的异步复位端R不受 CP 脉冲的控制。

( )7、JK触发器要实现Q n+1=1时,J、K端的取值为J=1,K=0。

( ) 8、A/D转换器是将数字量转换为模拟量。

( ) 9、方波的占空比为0.5。

( )10、半导体存储器RAM的基本结构是由地址译码器、存储矩阵和读写控制电路三大部分构成的。

四

1、时序逻辑电路的输出状态与前一刻电路的输出状态有关,还与电路当前的输入变量组合有关。

2、555集成定时器在正常工作时,应该将外部复位端R接高电平。

3、同步时序逻辑电路中的无效状态是由于状态表没有达到最简所造成的。

4、RAM掉电后数据易丢失,而ROM掉电后仍能保持数据。

5、普通TTL与非门的输出端允许直接相连,实现线与。

6、组合电路有记忆功能。

7、JK触发器只有J、K端同时为1,则一定引起状态翻转。

8. CMOS 电路比 TTL 电路功耗大。

9. 触发器的异步复位端R不受 CP 脉冲的控制。

10. 二进制计数器既可实现计数也可用于分频。

六

1、时序逻辑电路的输出状态与前一刻电路的输出状态有关,还与电路当前的输入变量组合有关。

2、555集成定时器在正常工作时,应该将外部复位端R接高电平。

3、同步时序逻辑电路中的无效状态是由于状态表没有达到最简所造成的。

4、RAM掉电后数据易丢失,而ROM掉电后仍能保持数据。

5、普通TTL与非门的输出端允许直接相连,实现线与。

6、组合电路有记忆功能。

7、JK触发器只有J、K端同时为1,则一定引起状态翻转。

8. CMOS 电路比 TTL 电路功耗大。

9. 触发器的异步复位端R不受 CP 脉冲的控制。

10. 二进制计数器既可实现计数也可用于分频。

七

1、逻辑变量的取值,1比0大。

2、D/A转换器的位数越多,能够分辨的最小输出电压变化量就越小。

3.八路数据分配器的地址输入(选择控制)端有8个。

4、因为逻辑表达式A+B+AB=A+B成立,所以AB=0成立。

5、利用反馈归零法获得N进制计数器时,若为异步置零方式,则状态S N只是短暂的过渡状态,不能稳定而是立刻变为0状态。

6.在时间和幅度上都断续变化的信号是数字信号,语音信号不是数字信号。

7.约束项就是逻辑函数中不允许出现的变量取值组合,用卡诺图化简时,可将约束项当作1,也可当作 0。

8.时序电路不含有记忆功能的器件。

9.计数器除了能对输入脉冲进行计数,还能作为分频器用。

10.优先编码器只对同时输入的信号中的优先级别最高的一个信号编码.

九

1、格雷码具有任何相邻码只有一位码元不同的特性。

2、逻辑函数两次求反则还原,逻辑函数的对偶式再作对偶变换也还原为它本身。

3、一般TTL门电路的输出端可以直接相连,实现线与。

4、对边沿JK触发器,在CP为高电平期间,当J=K=1时,状态会翻转一次。

5、多谐振荡器有两个稳态。

6、优先编码器的编码信号是相互排斥的,不允许多个编码信号同时有效。

7、共阴接法发光二极管数码显示器需选用有效输出为高电平的七段显示译码器来驱动。

8、同步时序电路具有统一的时钟CP控制。

9、一个N位逐次逼近型A/D转换器完成一次转换要进行N次比较。

10、ROM和RAM中存入的信息在电源断掉后都不会丢失。

十

1、普通的逻辑门电路的输出端不可以并联在一起,否则可能会损坏器件。

2、D/A转换器的位数越多,能够分辨的最小输出电压变化量就越小,输出电压越精确。3.八路数据分配器的地址输入(选择控制)端有8个。

4、RAM掉电后数据易丢失,而ROM掉电后仍能保持数据。

5、触发器的异步复位端R不受 CP 脉冲的控制。

6、在时间和幅度上都断续变化的信号是数字信号,语音信号不是数字信号。

7、优先编码器的编码信号是相互排斥的,不允许多个编码信号同时有效。

8、时序电路不含有记忆功能的器件。

9、计数器除了能对输入脉冲进行计数,还能作为分频器用。

10、二进制译码器相当于是一个最小项发生器,便于实现组合逻辑电路。

十一

1、时序逻辑电路的输出状态与前一刻电路的输出状态有关,还与电路当前的输入变量组合有关。

2、若两个函数具有不同的真值表,则两个逻辑函数必然不相等。

3、优先编码器的编码信号是相互排斥的,不允许多个编码信号同时有效。

4、组合逻辑电路的竞争冒险现象是由于信号传输路径不同而使延时有差异造成的。

5、普通的逻辑门电路的输出端不可以并联在一起,否则可能会损坏器件。

6、D触发器的特性方程为Q*=D,与Q无关,所以它没有记忆功能。

7、JK触发器只要J、K端同时为1,则一定引起状态翻转。

8.石英晶体多谐振荡器的振荡频率与电路中的R、C成正比。

9. 触发器的异步复位端R不受 CLK 脉冲的控制。

10.计数器的模是指构成计数器的触发器的个数。