CM6805A中文资料

AU6805规格书英文版_(正式版)

CM6805

VDC

PWM

Ramp2

VDC

PWM

Elvis_Lin

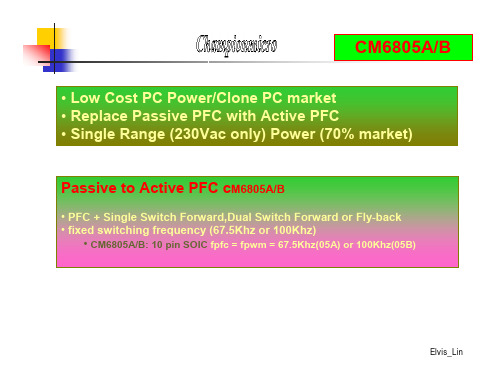

CM6805A/B/CM6903 PFC Controller:

Leading Edge Modulation with Input Current Shaping Technique

(I.C.S.T)

Elvis_Lin

Boost-converter

6 56K

470pF/250V

4 R8 330K R10 13K R6 330 C3 103 C4 102P 3

LTV817 B

PWM IS

+5V

+12V

10

1000PF

10.2K 1%

ISO1A

817C

B+

20/100V

+12V 10 1uF/450V 1000PF IA/1000V GND 39.2K 1% 2200PF 2200uF/16V

T130-18 Iron Powder

$0.6

ER806

380VDC

$0.22

20N60

$0.7

$0.7

+

180uF/450V

9N90

$0.5

CM6805A/B

Replace Passive plan gain 5% cost down

SMDA05C中文资料

SMDA05C THRU SMDA24C

Bidirectional TVS Array for Protection of Four Lines

PROTECTION PRODUCTS

Description

The SMDAxxC series of TVS arrays are designed to provide bidirectional protection for sensitive electronics from damage or latch-up due to ESD, lightning and other voltage-induced transient events. Each device will protect four data or I/O lines. They are available with operating voltages of 5V, 12V, 15V and 24V.

8

15

ã 2000 Semtech Corp.

4

元器件交易网

PROTECTION PRODUCTS Applications Information

Device Connection for Protection of Four Data Lines

The SMDAxxC series devices are designed to protect up to four data lines. The devices are connected as follows:

l The SMDAxxC are bidirectional devices and are designed for use on lines where the normal operating voltage is above and below ground. Pins 1, 2, 3, and 4 are connected to the protected lines. Pins 5, 6, 7, and 8 are connected to ground. Since the device is electrically symmetrical, these connections may be reversed. The ground connections should be made directly to the ground plane for best results. The path length is kept as short as possible to reduce the effects of parasitic inductance in the board traces.

cm5塑壳断路器选型手册

有一支以博士、硕士、本科生为主的多层次研发队伍,工程技术人员占企业员工总数

的4 5% 左 右 。 公 司 拥 有 先 进 的 模 具 制 造 、 零 部 件 自 动 化 生 产 、 断 路 器 装 配 自 动 检 测 流

水 线 等 一 大 批 先 进 的 制 造 和 试 验 检 测 设 备 ; 实 施 以E R P管 理 为 重 点 的 信 息 化 、 网 络 化

常熟开关制造有限公司 为您提供电气系统完整的解决方案

CV1-12系列 高压真空断路器

CV2-12系列 高压真空 断路器

CV1-2 4系列 高压真空 断路器

CV1-40.5系列 高压真空断路器

CW1系列 智能型万能式断路器

CW2系列 智能型万能式断路器

CM6800 中文版

CM6800/1 低启动电流PFC/PWM二合一控制器一般说明:CM6800/1是一个具有PFC(功率因素校正)之开关电源控制器。

PFC可以容许使用较小的低損耗的bulk电容,降低电源线负载与开关FET所受的压力,使电源供应器能完全符合IEC-1000-2-3之规格。

CM6800/1的目的是作为已成為工业标准的ML-4824之BICMOS版本,所以線路上包括上升緣觸發(leading edge)的平均电流控制模式的升壓型之PFC和下降緣觸發的(trailing edge)PWM。

栅級驅動(Gate-driver)电流可达1A,可以大量减少外加驱动线路。

且这颗IC消耗功率低,故可增加电源供应器整体效率并降低零件損耗。

一旦负载忽然降低,则过电压比较器立即关掉PFC。

PFC亦具有峰值電流限制(peak current limiting)與輸入電壓太低(Input voltage brownout)之保護作用。

PWM可以在電壓或電流模式下運作。

頻率可高至250KHZ,並能將工作周期准確的限制在50%之內,以防變壓器飽和。

功能:z與ML4800,FAN6800/1腳對腳完全相同互用。

z在PWM增加一組folded-back電流限制z23V Bi-CMOS制程.z VIN OK保證在2.5V時開起PWM而不是1.5V。

z在同一IC中集成了具同步的leading edge PFC 與trailing edge PWMz slew rate 使transconductance error amplifier具有超快的響應z低啟動電流(100MA),低工作電流(3MA),低諧波失真,高PFPIN DESCRIPTION1 IEAO PFC跨導電流誤差放大器輸出2 I AC PFC增益控制信號參考輸入3 I SENSE PFC電流限制比較器電流檢測信號輸入4 V RMS PFC RMS 電源電壓補償信號輸入5 SS PWM軟啟動電容接點6 VDC PWM電壓回饋輸入7 RAMP1 振盪時序,由RT,CT決定振盪周期8 RAMP2 電流模式時,此腳位作為電流檢測輸入;電壓模式時,則為PFC輸出至PWM輸入9 DC I LIMIT PWM電流限制比較器輸入10 GND11 PWM OUT PWM驅動輸出12 PFC OUT PFC驅動輸出13 V CC14 V REF 內部7.5v基准電壓之緩沖輸出15 V FB PFC跨導誤差放大器輸入16 VEAO PFC跨導誤差放大器輸出一般功能说明:(Functional Deseription)CM6800/I 包括一組具平均電流模式控制的連續升壓型PFC之前端線路(Front End)與一組同步PWM之後端線路。

CM580 CM580S高性能模块化磁通矢量控制变频器用户手册说明书

CM580/CM580S高性能模块化磁通矢量控制变频器用户手册目录目 录前 言 (3)第一章 安全及注意事项 (5)1.1安全事项 (5)1.2注意事项 (6)第二章 产品信息 (9)2.1命名规则 (9)2.2铭牌 (9)2.3CM580变频器系列 (10)2.4CM580S变频器系列 (11)2.5技术规范 (13)2.6产品外型图、安装孔位尺寸 (15)2.7选配件 (21)2.8变频器的日常保养与维护 (23)2.9变频器的保修说明 (24)2.10选型指导 (24)2.11制动组件选型指南 (25)第三章 机械和电气安装 (28)3.1机械安装 (28)3.2电气安装 (31)第四章 操作与显示 (44)4.1操作与显示界面介绍 (44)4.2变频器功能码的组织方式 (46)4.3功能码查看、修改方法说明 (46)4.4功能码菜单模式与切换说明 (47)4.5运行前准备 (49)4.6变频器的起停控制 (52)4.7变频器的运行频率控制 (57)4.8电机特性参数设置与自动调谐 (62)4.9变频器DI端口的使用方法 (64)4.10变频器DO端口的使用方法 (64)4.11AI输入信号特性及预处理 (65)4.12变频器AO端口的使用方法 (65)4.13变频器串行通讯的使用方法 (66)4.14密码设置 (67)第五章 参数说明 (68)5.1F0组基本功能参数 (68)5.2F1组启停控制功能组 (75)5.3F2组V/F控制参数 (77)5.4F3组矢量控制参数 (80)5.5F4组第一电机参数 (83)目录CM580/CM580S高性能模块化磁通矢量控制变频器用户手册5.6F5组输入端子 (85)5.7F6组输出端子 (93)5.8F7组辅助功能及键盘显示 (97)5.9F8组通信参数 (105)5.10F9组故障与保护 (106)5.11FA组PID功能 (112)5.12F B组摆频、定长和计数 (116)5.13FC组多段指令及简易PLC功能 (118)5.14F D组转矩控制参数 (122)5.15FE组AI多点曲线设定 (124)5.16FF组厂家参数 (125)5.17H0组第二电机参数设定 (125)5.18H1组第二电机参数 (126)5.19H2组第二电机VF参数设定 (127)5.20H3组第二电机矢量控制参数 (127)5.21L0组系统参数 (128)5.22L1组用户功能码定制 (128)5.23L2组优化控制参数 (129)5.24L3组AIAO校正参数 (130)5.25L4组主从控制参数 (131)5.26L5组抱闸功能参数 (133)5.27L6组休眠唤醒功能参数 (134)5.28U0组故障记录参数 (136)5.29U1组状态监控参数 (136)第六章EMC(电磁兼容性) (138)6.1定义 (138)6.2EMC标准介绍 (138)6.3EMC指导 (138)第七章 故障诊断及对策 (141)7.1故障报警及对策 (141)7.2常见故障及其处理方法 (144)第八章CM580系列变频器串行通讯协议 (145)附录A:功能参数表 (153)附录B:卡类说明 (202)A、CM580IO1扩展卡使用说明 (202)B、CM580IO2扩展卡(输出功能扩展)使用说明 (205)C、PG卡使用说明 (206)附录C 版本变更记录 (210)CM580/CM580S高性能模块化磁通矢量控制变频器用户手册前言前言首先感谢您购买我司完全自主开发的CM580/CM580S系列磁通矢量控制变频器。

CM6805AGIR中文资料

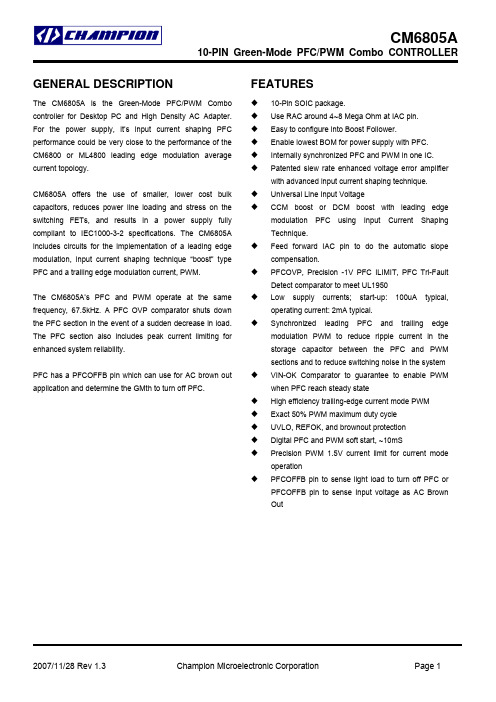

GENERAL DESCRIPTIONFEATURES10-Pin SOIC package.Use RAC around 4~8 Mega Ohm at IAC pin. Easy to configure into Boost Follower.Enable lowest BOM for power supply with PFC. Internally synchronized PFC and PWM in one IC. Patented slew rate enhanced voltage error amplifier with advanced input current shaping technique.Universal Line Input VoltageCCM boost or DCM boost with leading edgemodulation PFC using Input Current Shaping Technique. Feed forward IAC pin to do the automatic slope compensation.PFCOVP, Precision -1V PFC ILIMIT, PFC Tri-Fault Detect comparator to meet UL1950Low supply currents; start-up: 100uA typical,operating current: 2mA typical.Synchronized leading PFC and trailing edgemodulation PWM to reduce ripple current in the storage capacitor between the PFC and PWM sections and to reduce switching noise in the system VIN-OK Comparator to guarantee to enable PWM when PFC reach steady stateHigh efficiency trailing-edge current mode PWM Exact 50% PWM maximum duty cycle UVLO, REFOK, and brownout protection Digital PFC and PWM soft start, ~10mSPrecision PWM 1.5V current limit for current mode operationPFCOFFB pin to sense light load to turn off PFC or PFCOFFB pin to sense Input voltage as AC Brown OutThe CM6805A is the Green-Mode PFC/PWM Combo controller for Desktop PC and High Density AC Adapter. For the power supply, it’s input current shaping PFC performance could be very close to the performance of the CM6800 or ML4800 leading edge modulation average current topology.CM6805A offers the use of smaller, lower cost bulk capacitors, reduces power line loading and stress on the switching FETs, and results in a power supply fully compliant to IEC1000-3-2 specifications. The CM6805A includes circuits for the implementation of a leading edge modulation, input current shaping technique “boost” type PFC and a trailing edge modulation current, PWM.The CM6805A’s PFC and PWM operate at the same frequency, 67.5kHz. A PFC OVP comparator shuts down the PFC section in the event of a sudden decrease in load. The PFC section also includes peak current limiting for enhanced system reliability.PFC has a PFCOFFB pin which can use for AC brown out application and determine the GMth to turn off PFC.TYPICAL PERFORMANCE CHARACTERISTIC5764717885929910611312012722.1 2.2 2.3 2.4 2.5 2.6 2.7 2.8 2.93VFB (V)T r a n s c o n d u c t a n c e (u m h o )Voltage Error Amplifier (GMv) TransconductanceFunctional DescriptionThe CM6805A consists of an ICST (Input Current Shaping Technique), CCM (Continuous Conduction Mode) or DCM (Discontinuous Conduction Mode) boost PFC (Power Factor Correction) front end and a synchronized PWM (Pulse Width Modulator) back end. The CM6805A is designed to replace FAN4803 (8 pin SOP package), whichis the second generation of the ML4803 with 8 pin package.It is distinguished from earlier combo controllers by its low count, innovative input current shaping technique, and very low start-up and operating currents. The PWM section is dedicated to peak current mode operation. It uses conventional trailing-edge modulation, while the PFC uses leading-edge modulation. This patented Leading Edge/Trailing Edge (LETE) modulation technique helps to minimize ripple current in the PFC DC bus capacitor.The main improvements from ML4803 are:1. Add Green Mode Functions for both PFC and PWM2. Remove the one pin error amplifier and add back theslew rate enhancement GMv, which is using voltageinput instead of current input. This transconductanceamplifier will increase the transient response 5 to 10times from the conventional OP3. VFB PFC OVP comparator4. PFC Tri-Fault Detect for UL1950 compliance andenhanced safety5. A feed forward signal from IAC pin is added to do theautomatic slope compensation. This increases thesignal to noise ratio during the light load; therefore,THD is improved at light load and high input linevoltage.6. CM6805A does not require the bleed resistor and ituses the more than 800k ohm resistor between IACpin and rectified line voltage to feed the initial currentbefore the chip wakes up.7. VIN-OK comparator is added to guaranteed PWMcannot turn on until VFB reaches 2.5V in which PFCboost output is about steady state, typical 380V.8. A 10mS digital PWM soft start circuit is added9. 10 pin SOP package10. No internal Zener and VCCOVP comparatorThe CM6805A operates both PFC and PWM sections at 67.5kHz. This allows the use of smaller PWM magnetic and output filter components, while minimizing switching lossesin the PFC stage.Several protection features have been built into the CM6805A. These include soft-start, redundant PFC over voltage protection, PFC Tri-Fault Detect, VIN-OK, peak current limiting, duty cycle limiting, under-voltage lockout, reference ok comparator PFCOFFB.Detailed Pin DescriptionsIAC (Pin 2)Typically, it has a feed-forward resistor, RAC, 4Mega~10Mega ohm resistor connected between this pin and rectified line input voltage.The current of RAC will program the automatic slope compensation for the system. This feed-forward signal can increase the signal to noise ratio for the light load condition or the high input line voltage condition.ISENSE (Pin 3)This pin ties to a resistor which senses the PFC input current. This signal should be negative with respect to the IC ground. It internally feeds the pulse-by-pulse current limit comparator and the current sense feedback signal. The ILIMIT trip level is –1V. The ISENSE feedback is internally multiplied by a gain of four and compared against the internal programmed ramp to set the PFC duty cycle. The intersection of the boost inductor current down-slope with the internal programming ramp determines the boost off-time.It requires a RC filter between ISENSE and PFC boost sensing resistor.VEAO (Pin 4)This is the PFC slew rate enhanced transconductance amplifier output which needs to connected with a compensation network Ground.VFB (Pin 5)Besides this is the PFC slew rate enhanced transconductance input, it also tie to a couple of protection comparators, PFCOVP, and PFC Tri-Fault DetectV + I (Pin 6)This pin is tied to the primary side PWM current sense resistor or transformer. It provides the internal pulse-by-pulse current limit for the PWM stage (which occurs at 1.5V) and the peak current mode feedback path for the current mode control of the PWM stage. Besides current information, the photo-couple also goes into V + I pin. Therefore, it is the SUM Amplifier input.Soft Start is around 10mS after the startup(VCC is greater than 13V).PFC Control: Leading Edge Modulation with Input Current Shaping Technique (I.C.S.T.)The only differences between the conventional PFC control topology and I.C.S.T. is:the current loop of the conventional control method is a close loop method and it requires a detail understanding about the system loop gain to design. With I.C.S.T., since the current loop is an open loop, it is very straightforward to implement it.The end result of the any PFC system, the power supply is like a pure resistor at low frequency. Therefore, current is in phase with voltage.In the conventional control, it forces the input current to follow the input voltage. In CM6805A, the chip thinks if a boost converter needs to behave like a low frequency resistor, what the duty cycle should be.The following equations is CM6805A try to achieve:inine I V R =(1)in l I I =(2)Equation 2 means: average boost inductor current equals to input current.d out l in I V I V ×≈×∴ (3)Therefore, input instantaneous power is about to equal to the output instantaneous power.For steady state and for the each phase angle, boost converter DC equation at continuous conduction mode is:)1(1d V V inout−= (4)Rearrange above equations, (1), (2),(3), and (4) in term of Vout and d, boost converter duty cycle and we can get average boost diode current equation (5):eoutd R V d I ×−=2)1( (5)Also, the average diode current can be expressed as:dt t I T I offT d swd ⋅=∫)(10(6)If the value of the boost inductor is large enough, we canassumed d I t I ~)(. It means during each cycle or wecan say during the sampling, the diode current is a constant. Therefore, equation (6) becomes:)1('d I d I T t I I d d swoffd d −×=×=×=(7)Combine equation (7) and equation (5), and we get:swoffe out d eoutd eoutd T t R V I R V d I R V d d I ×=∴×=∴×=×'2'')( (8)From this simple equation (8), we implement the PFC control section of the CM6805ALeading/Trailing ModulationConventional Pulse Width Modulation (PWM) techniques employ trailing edge modulation in which the switch will turn ON right after the trailing edge of the system clock. The error amplifier output is then compared with the modulating ramp. When the modulating ramp reaches the level of the error amplifier output voltage, the switch will be turned OFF. When the switch is ON, the inductor current will ramp up. The effective duty cycle of the trailing edge modulation is determined during the ON time of the switch. Figure 2 shows a typical trailing edge control scheme.In case of leading edge modulation, the switch is turned OFF right at the leading edge of the system clock. When the modulating ramp reaches the level of the error amplifier output voltage, the switch will be turned ON. The effective duty-cycle of the leading edge modulation is determined during OFF time of the switch. Figure 3 shows a leading edge control scheme.One of the advantages of this control technique is that it required only one system clock. Switch 1(SW1) turns OFF and switch 2 (SW2) turns ON at the same instant to minimize the momentary “no-load” period, thus lowering ripple voltage generated by the switching action. With such synchronized switching, the ripple voltage of the first stage is reduced. Calculation and evaluation have shown that the 120Hz component of the PFC’s output ripple voltage can be reduced by as much as 30% using this method, substantially reducing dissipation in the high-voltage PFC capacitor.Typical ApplicationsPFC Section:PFC Voltage Loop Error Amp, VEAOThe ML4803 utilizes an one pin voltage error amplifier in the PFC section (VEAO). In the CM6805A, it is using the slew rate enhanced transconductance amplifier, which is the same as error amplifier in the CM6800. The unique transconductance profile can speed up the conventional transient response by 10 times. The internal reference of the VEAO is 2.5V. The input of the VEAO is VFB pin.PFC Voltage Loop CompensationThe voltage-loop bandwidth must be set to less than 120Hz to limit the amount of line current harmonic distortion. A typical crossover frequency is 30Hz.The Voltage Loop Gain (S)CVV DC EAO 2OUTDC IN FBEAOOUT FB EAO OUT Z *GM *C *S *V *V V5.2*P V V *V V *V V Δ≈ΔΔΔΔΔΔ=Z CV : Compensation Net Work for the Voltage Loop GMv: Transconductance of VEAO PIN : Average PFC Input PowerV OUTDC : PFC Boost Output Voltage; typical designed value is 380V.C DC : PFC Boost Output CapacitorΔV EAO : This is the necessary change of the VEAO to deliver the designed average input power. The average value is 6V-3V=3V since when the input line voltage increases, the delta VEAO will be reduced to deliver the same to the output. To over compensate, we choose the delta VEAO is 3V.Internal Voltage RampThe internal ramp current source is programmed by way of VEAO pin voltage. When VEAO increases the ramp current source is also increase. This current source is used to develop the internal ramp by charging the internal 30pF +12/ -10% capacitor. The frequency of the internal programming ramp is set internally to 67.5kHz.Design PFC ISENSE FilteringISENSE Filter, the RC filter between Rs and ISENSE:There are 2 purposes to add a filter at ISENSE pin:1.) Protection: During start up or inrush currentconditions, it will have a large voltage cross Rs, which is the sensing resistor of the PFC boost converter. It requires the ISENSE Filter to attenuate the energy.2.) Reduce L, the Boost Inductor: The ISENSE Filteralso can reduce the Boost Inductor value since the ISENSE Filter behaves like an integrator before going ISENSE which is the input of the current error amplifier, IEAO.The I SENSE Filter is a RC filter. The resistor value of the I SENSE Filter is between 100 ohm and 50 ohm. By selecting R FILTER equal to 50 ohm will keep the offset of the IEAO less than 5mV. Usually, we design the pole of I SENSE Filter at fpfc/6, one sixth of the PFC switching frequency. Therefore, the boost inductor can be reduced 6 times without disturbing the stability. Therefore, the capacitor of the I SENSE Filter, C FILTER, will be around 283nF.IAC, R AC, Automatic Slope Compensation, DCM at high line and light load, and Startup currentThere are 4 purposes for IAC pin:1.) For the leading edge modulation, when the dutycycle is less than 50%, it requires the similar slopecompensation, as the duty cycle of the trailingedge modulation is greater than 50%. In theCM6805A, it is a relatively easy thing to design.Use an more than 800K ohm resistor, R AC toconnect IAC pin and the rectified line voltage. Itwill do the automatic slope compensation. If theinput boost inductor is too small, the R AC mayneed to be reduced more.2.) During the startup period, Rac also provides theinitial startup current, 100uA;therefore, the bleedresistor is not needed.3.) Since IAC pin with R AC behaves as a feedforwardsignal, it also enhances the signal to noise ratioand the THD of the input current.4.) It also will try to keep the maximum input power tobe constant. However, the maximum input powerwill still go up when the input line voltage goes up.Start Up of the system, UVLO, VREFOK and Soft Start During the Start-up period, R AC resistor will provide the start up current~100uA from the rectified line voltage to IAC pin. During the Start up, the soft start function is triggered and the duration of the soft start will last around 10mS.PFC section wakes up after Start up periodAfter Start up period, PFC section will softly start since VEAO is zero before the start-up period. Since VEAO is a slew rate enhanced transconductance amplifier (see figure 3), VEAO has a high impedance output like a current source and it will slowly charge the compensation net work which needs to be designed by using the voltage loop gain equation.Before PFC boost output reaches its design voltage, it is around 380V and VFB reaches 2.5V, PWM section is off. PWM section wakes up after PFC reaches steady state PWM section is off all the time before PFC VFB reaches 2.25V. Then internal 10mS digital PWM soft start circuit slowly ramps up the soft-start voltage.PFC OVP ComparatorPFC OVP Comparator sense VFB pin which is the same the voltage loop input. The good thing is the compensation network is connected to VEAO. The PFC OVP function is a relative fast OVP. It is not like the conventional error amplifier which is an operational amplifier and it requires a local feedback and it make the OVP action becomes very slow.The threshold of the PFC OVP is 2.5V+10% =2.75V with 250mV hysteresis.PFC Tri-Fault Detect ComparatorTo improve power supply reliability, reduce system component count, and simplify compliance to UL1950 safety standards, the CM6805A includes PFC Tri-Fault Detect. This feature monitors VFB (Pin 5) for certain PFC fault conditions.In case of a feedback path failure, the output of the PFC could go out of safe operating limits. With such a failure, VFB will go outside of its normal operating area. Should VFB go too low, too high, or open, PFC Tri-Fault Detect senses the error and terminates the PFC output drive.PFC Tri-Fault detect is an entirely internal circuit. It requires no external components to serve its protective function.VCC over voltage and generate VCCFor the CM6805A system, if VCC is generated from a source that is proportional to the PFC output voltage. The PFC OVP will avoid the VCC over voltage. Given that 16V on VCC corresponds to 380V on the PFC output, 17.6V on VCC corresponds to an acceptable level of 18V.Typically, there is a bootstrap winding off the boost inductor.The VCC isn’t built in the VCC OVP function. For the VCC maximum rating, an external zener clamp is desirable and proposed to limit VCC over voltage.It is a necessary to put RC filter between bootstrap winding and VCC. For VCC=15V, it is sufficient to drive either a power MOSFET or a IGBT.UVLOThe UVLO threshold is 13V providing 3V hysteresis. PFCOUT and PWMOUTBoth PFCOUT and PWMOUT are CMOS drivers. They both have adaptive anti-shoot through to reduce the switching loss. Its pull-up is a 30ohm PMOS driver and its pull-down is a 15ohm NMOS driver. It can source 0.5A and sink 1A if the VCC is above 15V.PWM SectionAfter 10mS digital soft start, CM6805A’s PWM is operating as a typical current mode. It requires a secondary feedback, typically, it is configured with CM431, and photo couple.Since PWM Section is different from CM6800 family, it needs the emitter of the photo couple to connected with V+ I instead of the collector. The PWM current information also goes into V+I. Usually, the PWM current information requires a RC filter before goes into the V + I.Therefore, V+I actually is a summing node from voltage information which is from photo couple and CM431 and current information which is from one end of PWM sensing resistor and the signal goes through a single pole, RC filter then enter the V+I pin.This RC filter at V+I also serves several functions:1.) It protects IC.2.) It provides level shift for voltage information.3.) It filters the switching noise from currentinformation.At normal operation, the threshold voltage of the V + I pin is 1.5V. When the V + I is greater than 1.5V, PWM output driver will turn off the PWM Power MOSFET.When the Soft Start is triggered, the V+I threshold is around 150mV.Soft Start Can be triggered by the following conditions:1.) During the startup (VCC is less than 10V)2.) Vfb is below ~ 1.1VDuring above 2 conditions, the V + I threshold is around 150mV until the conditions have been removed.After above 2 conditions have been removed, the internal Soft Start D to A will ramp up the voltage from ~150mV to 2V. Each Soft Start Ramp can last around 10mS. Component ReductionComponents associated with the VRMS and IEAO pins of a typical PFC controller such as the CM6800 have been eliminated. The PFC power limit and bandwidth does vary with line voltage.。

CM6805A中文版

这个管脚需要连接一个补偿地,是 PFC 转换速率增强型跨导放大器输出端。 VFB(5 脚)

9

这个管脚除了是 PFC 转换速率增强型跨导放大器输入端之外,也连接了一对保护比较 器:PFC OVP 和 PFC 三重故障检测。 V+I(6 脚)

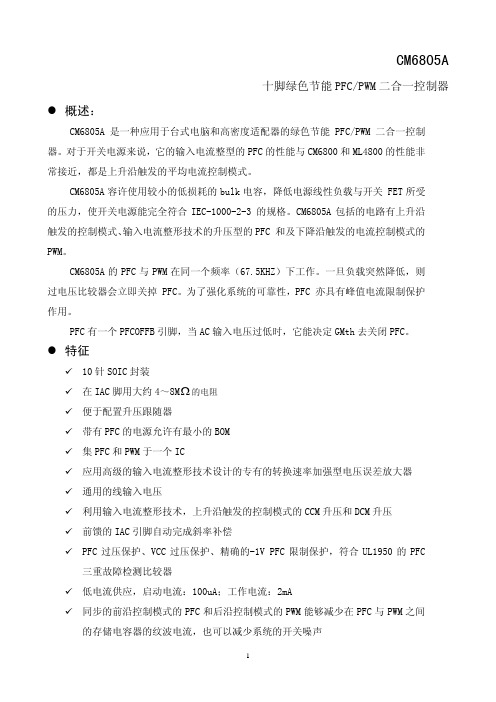

CM6805A

十脚绿色节能 PFC/PWM 二合一控制器

z 概述:

CM6805A 是一种应用于台式电脑和高密度适配器的绿色节能 PFC/PWM 二合一控制 器。对于开关电源来说,它的输入电流整型的 PFC 的性能与 CM6800 和 ML4800 的性能非 常接近,都是上升沿触发的平均电流控制模式。

CM6805A 的 PFC 和 PWM 都在 67.5 KHZ 下运行。在 PFC 阶段,最小化开关损耗的同 时可以使用更小的磁性 PWM 和输出滤波器件。

M6805A 内部具有一些保护功能,包括软启动、PFC 过压保护、PFC 三重故障检测、 VIN-OK、峰值电流限制、、占空比限制,欠压锁定、REF OK 比较器 OKPFCOFFB 和 VCCOCP。 管脚详细描述 IAC(2 脚)

改善了轻载及高线性输入电压时的总谐波失真。

6、CM6805A 不需要漏电阻,在 IAC 脚与整流线性电压间用一 800k Ω 电阻来补偿启动前

的初始电流。 7、增加 VIN-OK 比较器确保在 VFB 达到 2.5V,亦即典型值为 380V,PFC 处于稳态时,PWM

才会启动。 8、增加了一个 10ms PWM 数字软启动电路。 9、10 脚 SOP 封装。 10、无内部齐纳稳压二极管,具备 VCC OVP 比较器。

3

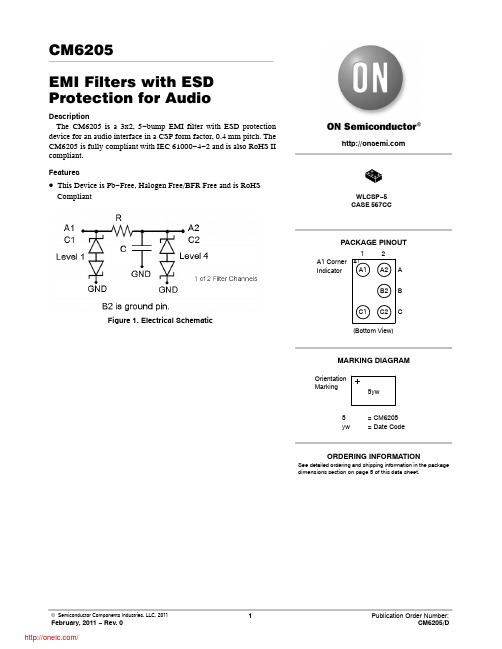

CM6205;中文规格书,Datasheet资料

CM6205EMI Filters with ESD Protection for AudioDescriptionThe CM6205 is a 3x2, 5−bump EMI filter with ESD protection device for an audio interface in a CSP form factor, 0.4 mm pitch. The CM6205 is fully compliant with IEC 61000−4−2 and is also RoHS II compliant.Features•This Device is Pb −Free, Halogen Free/BFR Free and is RoHSCompliantFigure 1. Electrical SchematicSee detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.ORDERING INFORMATIONWLCSP −5CASE 567CCMARKING DIAGRAM5= CM6205yw = Date CodePACKAGE PINOUT(Bottom View)A1A2B2C1C2Orientation Marking21A B CA1 Corner IndicatorA1Pin InformationTable 1. PIN DESCRIPTIONSPin Description Pin DescriptionA1Channel 1 Internal A2Channel 1 ExternalB2GNDC1Channel 2 Internal C2Channel 2 ExternalElectrical Specifications and ConditionsTable 2. PARAMETERS AND OPERATING CONDITIONSParameter Rating Units Storage Temperature Range−55 to +150°C Operating Temperature Range−40 to +85°C Power Dissipation per Channel100mWTable 3. ELECTRICAL OPERATING CHARACTERISTICS (Note 1)Symbol Parameter Conditions Min Typ Max Units R1, R2Resistance13.51516.5W C1, C2Pin Capacitance At 1 MHz, V IN= 0 V456nFI LEAK Leakage Current per Channel V IN= 5 V, other pins floating 1.0100nAV BR Breakdown Voltage (Positive)I R = +1 mA14V Breakdown Voltage (Negative)I R = −1 mA−14VV ESD ESD Protection Peak Discharge Voltage at A2 and C2 pinsa) Contact discharge perIEC 61000−4−2 standardb) Air discharge perIEC 61000−4−2 standard (Note 2)±15±15kVESD Protection Peak Discharge Voltage at A1 and C1 pinsa) Contact discharge perIEC 61000−4−2 standardb) Air discharge perIEC 61000−4−2 standard (Note 2)±2±2kV1.All parameters specified at T A = 25°C unless otherwise noted.2.Standard IEC 61000−4−2 with C Discharge = 150 pF, R Discharge = 330 W.Performance InformationFigure 2. Typical Insertion Loss (Bias = 0 V, T A = 25°C; 50 W Environment)Vertical Structure Specification*Figure 3. Sectional View*Daisy Chain CM6004VERTICAL STRUCTURE DIMENSIONS (nominal) Ref.Parameter Material Dimensiona Die Thickness Silicon396 m m h Repassivation Polyimide10 m m d UBM−(Ti/Cu)Plated Cu7.0 m mSputtered Cu0.4 m mSputtered Ti0.1 m m e UBM Wetting AreaDiameter240 m m b Bump Standoff194 m mf Solder Bump Dia-meter after BumpReflow270 m mc Metal Pad Height AlSiCu 1.5 m m g Metal Pad Diameter284 m m D20.406 mm D1Finished Thickness0.600 mmTable 4. CSP TAPE AND REEL SPECIFICATIONS †Part Number Chip Size (mm)Pocket Size (mm)B0 X A0 X K0Tape WidthW Reel Dia.Qty Per Reel P0P1CM6205 1.20 X 0.80 X 0.60 1.35 X 0.95 X 0.708 mm178 mm (7″)5000 4 mm 4 mm †For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.Figure 4. Tape and Reel Mechanical DataPACKAGE DIMENSIONSWLCSP5, 0.80x1.20CASE 567CC −01ISSUE OSEATING PLANENOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.COPLANARITY APPLIES TO SPHERICAL CROWNS OF SOLDER BALLS.2XDIM A MIN MAX 0.57MILLIMETERS A1D 0.80 BSC E b 0.240.29e0.40 BSC0.630.170.241.20 BSC DIMENSIONS: MILLIMETERS*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*0.40TOP VIEWBOTTOM VIEWA20.41 REF RECOMMENDEDOrdering InformationTable 5. PART NUMBERING INFORMATIONBumps Package Ordering Part Number (Note 3)Part Marking (Date Code)5CSP −SAC105CM62055yw3.Parts are shipped in Tape and Reel form unless otherwise specified.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION分销商库存信息: ONSEMICM6205。

AT680说明书

2

中国总代理:深圳市朗普电子科技有限公司 Email:Lp@

TEL:0755-88851600 FAX:0755-88850515

中国总代理:深圳市朗普电子科技有限公司 Email:Lp@

安全须知

TEL:0755-88851600 FAX:0755-88850515

不可 打开仪器外壳

非专业维护人员不可打开仪器外壳,以试图维修仪器。仪器在关机后一段 时间内仍存在未释放干净的电荷,这可能对人身造成电击危险。

不要 使用已经损坏的仪器

如果仪器已经损害,其危险将不可预知。请断开电源线,不可再使用,也 不要试图自行维修。

不要 使用工作异常的仪器

如果仪器工作不正常,其危险不可预知,请断开电源线,不可再使用,也 不要试图自行维修。

本项保证是 Applent 提供唯一保证,也是对您唯一的补偿,除此之外没有任何明示或暗示的保证(包 括保证某一特殊目的的适应性),亦明确否认所有其他的保证。Applent 或其他代理商并没有任何口头或书 面的表示,用以建立一项保证或以任何方式扩大本保证的范围。凡因对在规格范围外的任何原因而引起的 特别、间接、附带或继起的损坏、损失(包括资料的损失),Applent 将一概不予负责。如果其中某条款与 当地法规相抵触或由于某些司法不允许暗示性保证的排除或限制,以当地法规为主,因此该条款可能不适 用于您。但该条款的裁定不影响其他条款的有效性和可执行性。

不要超出本说明书指定的方 超出范围,仪器所提供的保护措施将失效。

式使用仪器

本仪器符合电子工业部标准GB6587.1《电子测量仪器环境试验总纲》中的第II组要求,额定使用条件: A. 环境温度:0~40°C B. 相对湿度:20~80%RH C. 大气压强:86~106Kpa D. 仪器在使用中允许受到一般的振动和冲击。

广州致远电子股份有限公司 产品用户手册 PA 功率分析仪用户手册说明书

广州致远电子股份有限公司 产品用户手册PA 功率分析仪用户手册 功率分析仪User Manual UM01010101 V1.00 Date: 2014/07/03类别内容 关键词PA7000、PA6000、PA3000、功率测量、技术指标 摘 要 介绍PA7000、PA6000、PA3000系列功率分析仪的使用及其技术参数修订历史版本日期原因V1.00 2014/07/03 正式发布目录1. 文档说明 (8)2. 产品简介 (9)2.1简介 (9)2.2功能特性 (10)2.3应用系统 (10)3. 安全须知 (12)3.1警示标志 (12)3.2安全信息 (12)3.2.1一般注意事项 (12)3.2.2连接电源和地 (13)3.2.3仪器安置注意事项 (13)3.2.4连接测量回路 (14)4. 功能概述 (15)4.1主要功能概览 (15)4.2测量功能列表 (15)4.3工作模式 (16)4.4通信接口 (16)4.5显示界面 (17)4.6测量分析功能 (19)4.6.1波形显示 (19)4.6.2趋势分析 (20)4.6.3谐波分析功能 (21)4.6.4FFT功能 (22)4.6.5IEC谐波测量 (23)4.6.6向量显示 (24)4.6.7闪变分析 (24)4.6.8周期分析 (25)4.6.9常规分析模式 (26)4.6.10波形运算 (26)4.6.11电机测量 (27)4.7补充阅读 (28)4.7.1输入单元 (28)4.7.2接线组 (29)5. 面板介绍 (30)5.1前面板 (30)5.1.1面板组件 (30)5.1.2显示界面 (30)5.1.3功能按键区 (33)5.2后面板 (44)5.3左侧面板 (45)5.4右侧面板 (46)6. 开始测量之前 (47)6.1概述 (47)6.2系统设置 (47)6.3调零 (47)6.3.1功能简介 (47)6.3.2操作步骤 (47)6.4电压/电流模式 (48)6.4.1功能简介 (48)6.4.2操作步骤 (48)6.4.3注意事项 (49)6.5输入通道连接与配置 (49)6.5.1测量方法选择 (49)6.5.2测量回路配置 (50)6.6阈值设置 (56)6.7频率测量模式 (56)6.8随机采样设置 (56)6.9数字滤波设置 (56)6.10设定接线补偿、效率补偿 (57)6.10.1功能简介 (57)6.10.2操作步骤 (57)6.11量程和区间设定 (58)6.11.1设置量程 (58)6.11.2测量区间设定 (60)6.12功率测量参数初始化 (62)6.12.1设定视在功率、无功功率和修正功率的运算公式 (62)6.12.2设定效率公式 (64)6.13平均功能 (66)6.13.1功能简介 (66)6.13.2操作步骤 (67)6.14用户自定义功能 (68)6.14.1功能简介 (68)6.14.2操作步骤 (70)6.15配置向导 (71)6.16精确测量 (73)6.17补充阅读 (74)6.17.1PT和CT (74)6.17.2电流传感器的种类 (74)6.17.3接线方式 (74)7. 数值数据显示 (80)7.1数值数据分屏显示 (80)7.1.1功能简介 (80)7.1.2操作步骤 (80)7.2显示项目配置 (81)7.2.1操作简介 (81)7.3相位差显示格式 (83)7.3.1功能简介 (83)7.3.2操作步骤 (83)7.3.3注意事项 (83)8. 波形显示与运算 (84)8.1波形显示 (84)8.1.1全屏/分屏显示 (84)8.1.2波形显示开关 (85)8.1.3设定时间轴长度 (86)8.1.4波形触发显示 (87)8.1.5波形垂直缩放/移动 (89)8.1.6波形显示参数设置 (93)8.1.7波形显示的分配 (96)8.2波形运算 (97)8.2.1功能简介 (97)8.2.2操作步骤 (99)8.2.3注意事项 (100)8.2.4补充阅读 (100)9. 趋势显示 (102)9.1功能简介 (102)9.2操作步骤 (103)9.2.1趋势显示模式 (103)9.2.2趋势显示参数配置 (103)9.2.3趋势功能参数配置 (106)10. 谐波测量 (108)10.1简介 (108)10.1.1概述 (108)10.1.2测量功能种类 (108)10.1.3功能限制 (109)10.2常规谐波测量 (110)10.2.1功能简介 (110)10.2.2操作步骤 (110)10.3IEC谐波测量 (115)10.3.1功能简介 (115)10.3.2操作步骤 (120)10.4补充阅读 (122)10.4.1相关术语 (122)10.4.2常规测量值和总波值 (122)10.4.3谐波测量功能的求法 (123)11. FFT (127)11.1功能简介 (127)11.2操作步骤 (127)11.2.1FFT数据组合显示 (127)11.2.3配置FFT功能参数 (130)11.2.4其它配置 (132)11.3补充阅读 (133)11.3.1FFT功能 (133)11.3.2谐波测量与FFT运算的差异 (134)12. Delta测量 (135)12.1功能简介 (135)12.2Delta测量的求法 (136)12.3操作步骤 (137)12.3.1概述 (137)12.3.2接线组设置 (137)12.3.3选择运算类型 (137)12.3.4Δ测量结果的显示 (137)13. 周期分析测量 (139)13.1功能简介 (139)13.2操作步骤 (141)13.3注意事项 (146)14. 积分运算 (149)14.1功能简介 (149)14.2操作步骤 (149)14.3规格 (152)14.3.1掉电保存 (152)14.3.2有效频率范围 (152)14.3.3显示分辨率 (152)14.3.4溢出时显示 (152)14.3.5限制执行 (152)14.4补充阅读 (153)14.4.1积分模式 (153)14.4.2HOLD操作和积分功能 (156)15. 常规分析模式 (158)15.1功能简介 (158)15.2操作步骤 (158)15.2.1概述 (158)15.2.2测量功能初始化 (158)15.2.3进入常规分析模式菜单 (158)15.2.4常规分析模式/测量切换 (158)15.2.5查看数据 (158)15.2.6自动回放测量数据 (159)16. 向量显示 (160)16.1功能简介 (160)16.1.1向量图示例 (160)16.2操作步骤 (162)16.3注意事项 (164)17. 光标测量 (165)17.1功能简介 (165)17.2操作步骤 (165)17.2.1概述 (165)17.2.2进入光标测量菜单 (165)17.2.3光标测量初始化 (168)17.2.4开启/关闭光标测量 (169)17.2.5光标移动 (170)17.3注意事项 (170)18. 闪变测量 (171)18.1功能简介 (171)18.2操作步骤 (172)18.2.1进入闪变测量模式 (172)18.2.2测量方法设置 (173)18.2.3闪变测量参数设置 (173)18.2.4判断条件设置 (175)18.2.5常规闪变测量操作 (176)18.2.6手动闪变测量操作 (180)18.3补充阅读 (183)18.3.1相关术语 (183)18.3.2对功能的限制 (185)19. 电机测量 (186)19.1功能简介 (186)19.2操作步骤 (186)19.2.1输入转速和扭矩信号 (186)19.2.2进入电机设置菜单 (186)19.2.3选择转速和扭矩信号的类型 (186)19.2.4选择模拟量程 (186)19.2.5配置线路滤波器和同步源 (187)19.2.6设定脉冲量程、脉冲数和脉冲额定值 (188)19.2.7设定比例系数和单位 (190)19.2.8设定用于计算滑差和同步速度的电机极数和频率测量源 (192)19.2.9选择测量电机输入电压和电流的输入单元 (193)19.2.10电机测量结果显示 (193)19.3注意事项 (195)20. 系统功能 (196)20.1日期/时间 (196)20.2按键锁和按键配置 (197)20.2.1按键锁 (197)20.2.2按键配置 (198)20.3显示器 (199)20.4语言 (199)20.5电源管理 (199)20.6触摸屏校准 (199)20.7软件更新 (199)20.8配置管理 (200)20.9网络 (201)20.10文件管理 (201)20.11系统信息 (201)20.12捕获 (202)20.13存储数据 (204)20.13.1功能简介 (204)20.13.2操作步骤 (204)21. 异常处理 (215)22. 规格 (216)22.1输入参数 (216)22.1.1输入端子类型 (216)22.1.2输入类型 (216)22.1.3输入单元数量 (216)22.1.4电压测量量程 (216)22.1.5电流测量量程 (217)22.1.6输入带宽 (218)22.1.7共模电压 (218)22.1.8滤波器 (218)22.1.9量程切换 (218)22.1.10A/D转换器 (219)22.2显示器 (219)22.3精度 (219)22.4测量模式 (220)22.5测量项目 (220)22.6测量功能/测量条件 (221)22.7电机功能 (222)22.7.1模拟量输入参数 (222)22.7.2脉冲频率输入参数 (222)22.8谐波测量 (222)22.9常规谐波/谐波/IEC谐波 (223)22.10FFT运算功能 (223)22.11周期分析功能 (223)22.12积分功能 (224)22.13波形采样数据保存功能 (224)22.14存储 (224)22.15常规特性 (224)22.16外观尺寸 (224)23. 免责声明 (226)附录A 测量功能符号及含义 (227)附录B 测量功能求法 (229)1. 文档说明本PA功率分析仪用户手册文档介绍PA7000、PA6000、PA3000系列功率分析仪的使用方法和技术规格。

CM6802_文档

TYPICAL PERFORMANCE CHARACTERISTIC5764717885929910611312012722.1 2.2 2.3 2.4 2.5 2.6 2.7 2.8 2.93VFB (V)T r a n s c o n d u c t a n c e (u m h o )Voltage Error Amplifier (g mv ) Transconductance20406080100120140160180200220-500-400-300-200-100100200300400500ISENSE (mV)T r a n s c o n d u c t a n c e (u m h o )Current Error Amplifier (g mi ) Transconductance0.050.10.150.20.250.30.350.400.511.522.533.544.55VRMS (V)V a r i a b l e G a i n B l o c k C o n s t a n t (K )Gain Modulator Transfer Characteristic (K)1-AC OFFSET GAINMOD mV 0.625)-(6 x I I I K −=0.20.40.60.811.21.41.61.822.200.51 1.52 2.533.544.55VRMS (V)G a i nGainACOFFSETSENSE I I I Gain −=Functional DescriptionThe CM6802 consists of an average current controlled, continuous boost Power Factor Correction (PFC) front end and a synchronized Pulse Width Modulator (PWM) back end. The PWM can be used in either current or voltage mode. In voltage mode, feedforward from the PFC output buss can be used to improve the PWM’s line regulation. In either mode, the PWM stage uses conventional trailing edge duty cycle modulation, while the PFC uses leading edge modulation. This patented leading/trailing edgemodulation technique results in a higher usable PFC error amplifier bandwidth, and can significantly reduce the size of the PFC DC buss capacitor.The synchronized of the PWM with the PFC simplifies the PWM compensation due to the controlled ripple on the PFC output capacitor (the PWM input capacitor). The PWM section of the CM6802 runs at the same frequency as the PFC.In addition to power factor correction, a number ofprotection features have been built into the CM6802. These include soft-start, PFC overvoltage protection, peak current limiting, brownout protection, duty cycle limiting, and under-voltage lockout.Oscillator (RAMP1)The oscillator frequency is determined by the values of R T and C T , which determine the ramp and off-time of the oscillator output clock:f OSC =DEADTIMERAMP t t 1+ which is the internal clock frequency, fosc=2 x fpwm= 4 x fpfcThe Clock period of the oscillator is derived from the following equation:t RAMP = C T x R T x In 3.75V 1.25V REF REF −−at V REF = 7.5V:t RAMP = C T x R T x 0.51The dead time of the oscillator may be determined using:t DEADTIME = 5.5mA2.5V xC T = 450 x C TEXAMPLE:For the application circuit shown in the datasheet, with the oscillator running at:f OSC = 280kHz =RAMPt 1= 2 x fpwm = 4 x fpfc. Here, fpwm=140KHz and fpfc=70KHz.Selecting standard components values, C T = 1.0nF, and R T = 5.0k ΩGreen Mode FunctionBoth PFC Green Mode and PWM Green Mode can be set separately by selecting proper external value of the external components. These 2 external components are CT on the pin 7, RAMP1 pin and the filter resistor at pin 3, ISENSE pin.Both Blue Angel and Energy Star spec. can be easily met without shutting off PFC because in CM6802, both PFC and PWM can set the green mode thresholds. Once the green mode threshold is triggered, the section will go to pulse skipping mode.To Disable PFC Green Mode, a 1 Mega ohm resistor is needed between IEAO(pin1) and VREF(pin14).PFC Green Mode ThresholdDuring the light load, VEAO voltage will reduce. When VEAO is less than 0.5V, It will turn off PFC. It has 0.25V hysteresis. If the light load condition continues, the PFC section will stay at pulse skipping condition without audible noise since the input power is minimal because VEAO is around 0.75V.PFC Green Mode Threshold is set by selecting proper Rs which is the resistor of the RC filter at Isense pin. Its typical value is from 30 ohm to 300 ohm. If the Rs value is below 30 ohm, and if a 1 Mega ohm resistor is needed between IEAO(pin1) and VREF(pin14), PFC will not pulse skipping. During the pulse skipping, the reading of the power meter can not be trust. It will need to integrate the real power than average it with the time to get the average power.To further reduce the power and improve the light loadefficiency, the values of resistor dividers at VFB and VRMS need to be doubled or tripled. However, it will increase the layout sensitivity.To Disable PFC Green Mode, a 1 Mega ohm resistor is needed between IEAO(pin1) and VREF(pin14).PWM Green Mode ThresholdDuring the light load, PWM section duty cycle also reduces. When the PWM section duty cycle is less than the internal clock duty cycle which is set by the CT at RAMP1, pin 7, the PWM section will start pulse skipping. By selecting the proper CT, user can program the PWM Green Mode Threshold. Usually, CT is 1nF.Power Factor CorrectionPower factor correction makes a nonlinear load look like a resistive load to the AC line. For a resistor, the current drawn from the line is in phase with and proportional to the line voltage, so the power factor is unity (one). A common class of nonlinear load is the input of most power supplies, which use a bridge rectifier and capacitive input filter fed from the line. The peak-charging effect, which occurs on the input filter capacitor in these supplies, causes brief high-amplitude pulses of current to flow from the power line, rather than a sinusoidal current in phase with the line voltage.Such supplies present a power factor to the line of less than one (i.e. they cause significant current harmonics of the power line frequency to appear at their input). If the input current drawn by such a supply (or any other nonlinear load) can be made to follow the input voltage in instantaneous amplitude, it will appear resistive to the AC line and a unity power factor will be achieved.To hold the input current draw of a device drawing power from the AC line in phase with and proportional to the input voltage, a way must be found to prevent that device from loading the line except in proportion to the instantaneous line voltage. The PFC section of the CM6802 uses aboost-mode DC-DC converter to accomplish this. The input to the converter is the full wave rectified AC line voltage. No bulk filtering is applied following the bridge rectifier, so the input voltage to the boost converter ranges (at twice line frequency) from zero volts to the peak value of the AC input and back to zero. By forcing the boost converter to meet two simultaneous conditions, it is possible to ensure that the current drawn from the power line is proportional to the input line voltage. One of these conditions is that the output voltage of the boost converter must be set higher than the peak value of the line voltage. A commonly used value is 385VDC, to allow for a high line of 270VAC rms. The other condition is that the current drawn from the line at any given instant must be proportional to the line voltage. Establishing a suitable voltage control loop for the converter, which in turn drives a current error amplifier and switching output driver satisfies the first of these requirements. The second requirement is met by using the rectified AC line voltage to modulate the output of the voltage control loop. Such modulation causes the current error amplifier to command a power stage current that varies directly with the input voltage. In order to prevent ripple, which will necessarily appear at the output of boost circuit (typically about 10VAC on a 385V DC level), from introducing distortion back through the voltage error amplifier, the bandwidth of the voltage loop is deliberately kept low. A final refinement is to adjust the overall gain of the PFC such to be proportional to 1/VIN2, which linearizes the transfer function of the system as the AC input to voltage varies.Since the boost converter topology in the CM6802 PFC is of the current-averaging type, no slope compensation is required.PFC SectionGain ModulatorFigure 1 shows a block diagram of the PFC section of the CM6802. The gain modulator is the heart of the PFC, as it is this circuit block which controls the response of the current loop to line voltage waveform and frequency, rms line voltage, and PFC output voltages. There are three inputs to the gain modulator. These are: 1. A current representing the instantaneous input voltage(amplitude and waveshape) to the PFC. The rectified AC input sine wave is converted to a proportional current via a resistor and is then fed into the gain modulator at I AC.Sampling current in this way minimizes ground noise, as is required in high power switching power conversionenvironments. The gain modulator responds linearly to this current.2. A voltage proportional to the long-term RMS AC linevoltage, derived from the rectified line voltage after scaling and filtering. This signal is presented to the gain modulator at VRMS. The gain modulator’s output is inverselyproportional to V RMS2 (except at unusually low values of V RMS where special gain contouring takes over, to limitpower dissipation of the circuit components under heavy brownout conditions). The relationship between V RMS and gain is called K, and is illustrated in the TypicalPerformance Characteristics.The output of the voltage error amplifier, VEAO. The gain modulator responds linearly to variations in this voltage.The output of the gain modulator is a current signal, in the form of a full wave rectified sinusoid at twice the line frequency. This current is applied to the virtual-ground (negative) input of the current error amplifier. In this way the gain modulator forms the reference for the current error loop, and ultimately controls the instantaneous current draw of the PFC form the power line. The general for of the output of the gain modulator is:I GAINMOD =2RMSACVVEAOI×x 1V (1)More exactly, the output current of the gain modulator is given by:I GAINMOD = K x (VEAO – 0.625V) x I ACWhere K is in units of V-1Note that the output current of the gain modulator is limited around 228.47µA and the maximum output voltage of the gain modulator is limited to 228.47uA x 3.5K=0.8V. This 0.8V also will determine the maximum input power.However, I GAINMOD cannot be measured directly from I SENSE.I SENSE = I GAINMOD-I OFFSET and I OFFSET can only be measured when VEAO is less than 0.5V and I GAINMOD is 0A. TypicalI OFFSET is around 60uA.IACTypically, it has a feedforward resistor, RAC, less than 500K ohm resistor connected between this pin and rectified line input voltage.During the startup condition, it supplies the startup current; therefore, the system does not require additional bleed resistor to start up the chip.Selecting R AC for IAC pin IAC pin is the input of the gain modulator. IAC also is a current mirror input and it requires current input. Byselecting a proper resistor R AC , it will provide a good sine wave current derived from the line voltage and it also helps program the maximum input power and minimum input line voltage.R AC =Vin peak x 7.9K. For example, if the minimum line voltage is 80VAC, the R AC =80 x 1.414 x 7.9K=894Kohm.Current Error Amplifier, IEAOThe current error amplifier’s output controls the PFC duty cycle to keep the average current through the boostinductor a linear function of the line voltage. At the inverting input to the current error amplifier, the output current of the gain modulator is summed with a current which results from a negative voltage being impressed upon the I SENSE pin. The negative voltage on I SENSE represents the sum of all currents flowing in the PFC circuit, and is typically derived from a current sense resistor in series with the negative terminal of the input bridge rectifier. In higher powerapplications, two current transformers are sometimes used, one to monitor the IF of the boost diode. As stated above, the inverting input of the current error amplifier is a virtual ground. Given this fact, and the arrangement of the duty cycle modulator polarities internal to the PFC, an increase in positive current from the gain modulator will cause the output stage to increase its duty cycle until the voltage on I SENSE is adequately negative to cancel this increasedcurrent. Similarly, if the gain modulator’s output decreases, the output duty cycle will decrease, to achieve a less negative voltage on the I SENSE pin.To Disable PFC Green Mode, a 1 Mega ohm resistor is needed between IEAO(pin1) and VREF(pin14).This 1 Mega ohm resistor will reduce the DC gain but it will not impact the performance. Cycle-By-Cycle Current Limiter and Selecting R SThe I SENSE pin, as well as being a part of the current feedback loop, is a direct input to the cycle-by-cycle current limiter for the PFC section. Should the input voltage at this pin ever be more negative than –1V, the output of the PFC will be disabled until the protection flip-flop is reset by the clock pulse at the start of the next PFC power cycle.R S is the sensing resistor of the PFC boost converter. During the steady state, line input current x R S = I GAINMOD x 3.5K. Since the maximum output voltage of the gain modulator is I GAINMOD max x 3.5K= 0.8V during the steady state, R S x line input current will be limited below 0.8V as well. Therefore, to choose R S , we use the following equation:R S =0.7V x Vinpeak/(2x Line Input power)For example, if the minimum input voltage is 80VAC, and the maximum input rms power is 200Watt, R S = (0.7V x 80V x 1.414)/(2 x 200) = 0.197 ohm.PFC OVPIn the CM6802, PFC OVP comparator serves to protect the power circuit from being subjected to excessive voltages if the load should suddenly change. A resistor divider from the high voltage DC output of the PFC is fed to VFB. When the voltage on VFB exceeds 2.75V, the PFC output driver is shut down. The PWM section will continue to operate. The OVPcomparator has 250mV of hysteresis, and the PFC will not restart until the voltage at VFB drops below 2.50V. The VFB power components and the CM6802 are within their safe operating voltages, but not so low as to interfere with the boost voltage regulation loop. Also, VCC OVP can be served as a redundant PFCOVP protection. VCC OVP threshold is 19.4V with 1.5V hysteresis.Figure 1. PFC Section Block DiagramError Amplifier Compensation The PWM loading of the PFC can be modeled as anegative resistor; an increase in input voltage to the PWM causes a decrease in the input current. This response dictates the proper compensation of the twotransconductance error amplifiers. Figure 2 shows the types of compensation networks most commonly used for the voltage and current error amplifiers, along with theirrespective return points. The current loop compensation is returned to V REF to produce a soft-start characteristic on the PFC: as the reference voltage comes up from zero volts, it creates a differentiated voltage on I EAO which prevents the PFC from immediately demanding a full duty cycle on its boost converter.PFC Voltage LoopThere are two major concerns when compensating the voltage loop error amplifier, V EAO ; stability and transient response. Optimizing interaction between transient response and stability requires that the error amplifier’s open-loop crossover frequency should be 1/2 that of the line frequency, or 23Hz for a 47Hz line (lowest anticipated international power frequency). The gain vs. input voltage of the CM6802’s voltage error amplifier, V EAO has aspecially shaped non-linearity such that under steady-state operating conditions the transconductance of the erroramplifier is at a local minimum. Rapid perturbation in line or load conditions will cause the input to the voltage error amplifier (V FB ) to deviate from its 2.5V (nominal) value. If this happens, the transconductance of the voltage error amplifier will increase significantly, as shown in the Typical Performance Characteristics. This raises thegain-bandwidth product of the voltage loop, resulting in a much more rapid voltage loop response to suchperturbations than would occur with a conventional linear gain characteristics.The Voltage Loop Gain (S)CVV DC EAO 2OUTDC IN FBEAOOUT FB EAO OUT Z *GM *C *S *V *V V5.2*P V V *V V *V V ∆≈∆∆∆∆∆∆=Z CV : Compensation Net Work for the Voltage Loop GM v : Transconductance of VEAO P IN : Average PFC Input PowerV OUTDC : PFC Boost Output Voltage; typical designed value is 380V.C DC : PFC Boost Output CapacitorPFC Current LoopThe current amplifier, I EAO compensation is similar to that of the voltage error amplifier, V EAO with exception of thechoice of crossover frequency. The crossover frequency of the current amplifier should be at least 10 times that of thevoltage amplifier, to prevent interaction with the voltage loop. It should also be limited to less than 1/6th that of theswitching frequency, e.g. 16.7kHz for a 100kHz switching frequency.The Current Loop Gain (S)CII S OUTDC SENSEEAOEAO OFF OFF ISENSE Z *GM *V 5.2*L *S R *V I I *I D *D V ≈∆∆∆∆∆∆=Z CI : Compensation Net Work for the Current Loop GM I : Transconductance of IEAOV OUTDC : PFC Boost Output Voltage; typical designed value is 380V and we use the worst condition to calculate the Z CI R S : The Sensing Resistor of the Boost Converter2.5V: The Amplitude of the PFC Leading Modulation Ramp L: The Boost InductorThere is a modest degree of gain contouring applied to the transfer characteristic of the current error amplifier, toincrease its speed of response to current-loop perturbations. However, the boost inductor will usually be the dominant factor in overall current loop response. Therefore, this contouring is significantly less marked than that of the voltage error amplifier. This is illustrated in the Typical Performance Characteristics.I SENSE Filter, the RC filter between R S and I SENSE :There are 3 purposes to add a filter at I SENSE pin:1.) Protection: During start up or inrush currentconditions, it will have a large voltage cross Rs which is the sensing resistor of the PFC boostconverter. It requires the I SENSE Filter to attenuate the energy.2.) To reduce L, the Boost Inductor: The I SENSE Filteralso can reduce the Boost Inductor value since the I SENSE Filter behaves like an integrator before going I SENSE which is the input of the current error amplifier, IEAO.3.) By selecting the proper Rs, it can change the PFCGreen Mode threshold. Typical value is from 50 ohm (No Skipping) to 100 ohm.The I SENSE Filter is a RC filter. The resistor value of the I SENSE Filter is between 100 ohm and 50 ohm because I OFFSET x the resistor can generate an offset voltage of IEAO. By selecting R FILTER equal to 50 ohm will keep the offset of the IEAO less than 5mV. Usually, we design the pole of I SENSE Filter at fpfc/6, one sixth of the PFC switching frequency. Therefore, the boost inductor can be reduced 6 times without disturbing the stability. Therefore, the capacitor of the I SENSE Filter, C FILTER , will be around 283nF.PWM SectionPulse Width ModulatorThe PWM section of the CM6802 is straightforward, but there are several points which should be noted. Foremost among these is its inherent synchronization to the PFC section of the device, from which it also derives its basic timing. The PWM is capable of current-mode orvoltage-mode operation. In current-mode applications, the PWM ramp (RAMP2) is usually derived directly from a current sensing resistor or current transformer in the primary of the output stage, and is thereby representative of the current flowing in the converter’s output stage. DCI LIMIT, which provides cycle-by-cycle current limiting, is typically connected to RAMP2 in such applications. Forvoltage-mode, operation or certain specialized applications, RAMP2 can be connected to a separate RC timing network to generate a voltage ramp against which V DC will be compared. Under these conditions, the use of voltage feedforward from the PFC buss can assist in line regulation accuracy and response. As in current mode operation, the DC I LIMIT input is used for output stage overcurrent protection.No voltage error amplifier is included in the PWM stage of the CM6802, as this function is generally performed on the output side of the PWM’s isolation boundary. To facilitate the design of optocoupler feedback circuitry, an offset has been built into the PWM’s RAMP2 input which allows V DC to command a zero percent duty cycle for input voltages below 1.25V. PWM Current LimitThe DC I LIMIT pin is a direct input to the cycle-by-cycle current limiter for the PWM section. Should the input voltage at this pin ever exceed 1V, the output flip-flop is reset by the clock pulse at the start of the next PWM power cycle. Beside, the cycle-by-cycle current, when the DC ILIMIT triggered the cycle-by-cycle current, it also softly discharge the voltage of soft start capacitor. It will limit PWM duty cycle mode. Therefore, the power dissipation will be reduced during the dead short condition.V IN OK ComparatorThe V IN OK comparator monitors the DC output of the PFC and inhibits the PWM if this voltage on V FB is less than its nominal 2.45V. Once this voltage reaches 2.45V, which corresponds to the PFC output capacitor being charged to its rated boost voltage, the soft-start begins.PWM Control (RAMP2)When the PWM section is used in current mode, RAMP2 is generally used as the sampling point for a voltage representing the current on the primary of the PWM’s output transformer, derived either by a current sensing resistor or a current transformer. In voltage mode, it is the input for a ramp voltage generated by a second set of timing components (R RAMP2, C RAMP2), that will have a minimum value of zero volts and should have a peak value of approximately 5V. In voltage mode operation, feedforward from the PFC output buss is an excellent way to derive the timing ramp for the PWM stage.Soft Start Start-up of the PWM is controlled by the selection of the external capacitor at SS. A current source of 20µA supplies the charging current for the capacitor, and start-up of the PWM begins at 1.25V. Start-up delay can be programmed by the following equation:C SS = t DELAY x1.25VA 20µwhere C SS is the required soft start capacitance and the t DEALY is the desired start-up delay.It is important that the time constant of the PWM soft-start allow the PFC time to generate sufficient output power for the PWM section. The PWM start-up delay should be at least 5ms.Solving for the minimum value of C SS :C SS = 5ms x1.25VA 20µ = 80nFCaution should be exercised when using this minimum soft start capacitance value because premature charging of the SS capacitor and activation of the PWM section can result if VFB is in the hysteresis band of the V IN OK comparator at start-up. The magnitude of V FB at start-up is related both to line voltage and nominal PFC output voltage. Typically, a 1.0µF soft start capacitor will allow time for VFB and PFC out to reach their nominal values prior to activation of the PWM section at line voltages between 90Vrms and 265Vrms.Generating V CCAfter turning on CM6802 at 15V, the operating voltage can vary from 10V to 19.4V. The threshold voltage of VCC OVP comparator is 19.4V. The hysteresis of VCC OVP is 1.5V. When VCC see 19.4V, PFCOUT will be low, and PWMsection will not be disturbed. That’s the two ways to generate VCC. One way is to use auxiliary power supply around 15V, and the other way is to use bootstrap winding to self-bias CM6802 system. The bootstrap winding can be either taped from PFC boost choke or from the transformer of the DC to DC stage.The ratio of winding transformer for the bootstrap should be set between 18V and 15V. A filter network is recommended between VCC (pin 13) and bootstrap winding. The resistor of the filter can be set as following.R FILTER x I VCC ~ 2V, I VCC = I OP + (Q PFCFET + Q PWMFET ) x fsw I OP = 3mA (typ.)If anything goes wrong, and VCC goes beyond 19.4V, the PFC gate (pin 12) drive goes low and the PWM gate drive (pin 11) remains function. The resistor’s value must be chosen to meet the operating current requirement of the CM6802 itself (3mA, max.) plus the current required by the two gate driver outputs.EXAMPLE: With a wanting voltage called, V BIAS ,of 18V, a VCC of 15V and the CM6802 driving a total gate charge of 90nC at 100kHz (e.g. 1 IRF840 MOSFET and 2 IRF820 MOSFET), the gate driver current required is:I GATEDRIVE = 100kHz x 90nC = 9mA R BIAS =GCC CC BIAS I I V V +−R BIAS = 9mA5mA 15V 18V +−Choose R BIAS = 214ΩThe CM6802 should be locally bypassed with a 1.0µF ceramic capacitor. In most applications, an electrolytic capacitor of between 47µF and 220µF is also required across the part, both for filtering and as part of the start-up bootstrap circuitry.Leading/Trailing ModulationConventional Pulse Width Modulation (PWM) techniques employ trailing edge modulation in which the switch will turn on right after the trailing edge of the system clock. The error amplifier output is then compared with the modulating ramp up. The effective duty cycle of the trailing edge modulation is determined during the ON time of the switch. Figure 4 shows a typical trailing edge control scheme.In case of leading edge modulation, the switch is turned OFF right at the leading edge of the system clock. When the modulating ramp reaches the level of the error amplifier output voltage, the switch will be turned ON. The effective duty-cycle of the leading edge modulation is determined during OFF time of the switch. Figure 5 shows a leading edge control scheme.One of the advantages of this control technique is that itrequired only one system clock. Switch 1(SW1) turns off and switch 2 (SW2) turns on at the same instant to minimize the momentary “no-load” period, thus lowering ripple voltage generated by the switching action. With such synchronized switching, the ripple voltage of the first stage is reduced. Calculation and evaluation have shown that the 120Hz component of the PFC’s output ripple voltage can be reduced by as much as 30% using this method.IMPORTANT NOTICEChampion Microelectronic Corporation (CMC) reserves the right to make changes to its products or to discontinue any integrated circuit product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.A few applications using integrated circuit products may involve potential risks of death, personal injury, or severe property or environmental damage. CMC integrated circuit products are not designed, intended, authorized, or warranted to be suitable for use in life-support applications, devices or systems or other critical applications. Use of CMC products in such applications is understood to be fully at the risk of the customer. In order to minimize risks associated with the customer’s applications, the customer should provide adequate design and operating safeguards.HsinChu Headquarter Sales & Marketing5F, No. 11, Park Avenue II, Science-Based Industrial Park, HsinChu City, Taiwan 11F, No. 306-3, Sec. 1, Ta Tung Rd., Hsichih, Taipei Hsien 221Taiwan, R.O.C.T E L: +886-3-567 9979 T E L: +886-2-8692 1591 FAX: +886-3-567 9909 F A X: +886-2-8692 1596 。

GC65_硬件设计手册_V1.0(1)

e tia 3.3.3. 供电参考电路............................................................................................................... 20

上海移远通信技术有限公司

1 / 68

GC65 硬件设计手册

文档历史

修订记录

版本 1.0

日期

CQouneficdteenl tial 2013-09-16

作者 郝竹青

变更表述 初始版本

上海移远通信技术有限公司

2 / 68

GC65 硬件设计手册

目录

文档历史 ........................................................................................................................................................ 2 目录 ............................................................................................................................................................... 3 表格索引 ........................................................................................................................................................ 5 图片索引 ........................................................................................................................................................ 6

夏普M160M205零件手册中文_部分2

O第二纸盒给纸组件 (AR-M205)O第二纸盒给纸组件AR-RP6 MODEL目 录为确保安全性、可靠性,更换部品务必使用正规品。

指定的部品。

本手册仅供维修人员进行售后服务用,本手册内容如有更改,恕不通告。

SHARP CORPORATION部 品 手 册1234■外观给纸组件输送组件包装及附属品索引数码复合机选购件双面原稿输送器(RSPF)1外观1外观3输送组件3输送组件4包装及附属品4包装及附属品AR-D24单层纸盒AR-D25双层纸盒MODEL目 录为确保安全性、可靠性,更换部品务必使用正规品。

指定的部品。

本手册仅供维修人员进行售后服务用,本手册内容如有更改,恕不通告。

SHARP CORPORATION部 品 手 册123456■单层纸盒外观 (AR-D24)单层纸盒给纸组件 (AR-D24)双层纸盒外观 (AR-D25)双层纸盒给纸组件 (AR-D25)250页纸盒组件包装材料及附属品索引数码复合机选购件进纸组件1单层纸盒外观 (AR-D24)1单层纸盒外观 (AR-D24)2单层纸盒给纸组件 (AR-D24)2单层纸盒给纸组件 (AR-D24)4双层纸盒给纸组件 (AR-D25)4双层纸盒给纸组件 (AR-D25)5250页纸盒组件5250页纸盒组件6包装材料及附属品6包装材料及附属品■索引– 12 –COPYRIGHT © 2003 BY SHARP CORPORATION版权所有 翻印必究夏普办公设备(常熟)有限公司上海经营部中国上海浦东新金桥路28号新金桥大厦1601室 2003年10月中国印刷。

ESJ680操作手册v1.4.1_General_ Chinese

喷码机操作及维修手册目录⏹技术参数 (5)✧电气规格 (5)✧重量 (5)✧尺寸 (5)✧环境规格 (6)✧墨水的用量 (6)✧喷码机耗材容量 (6)⏹喷码原理 (7)✧喷码机的应用特点 (7)✧喷印字符的形成 (7)✧工作原理简述 (8)喷墨打印原理 (8)墨路工作原理 (10)✧影响喷印质量及稳定性的因素 (11)✧主要组成部件及功能 (11)⏹喷码机描述 (12)✧外观及主要部件 (12)✧墨路系统组件 (13)✧喷头 (13)✧外部连接 (14)✧操作面板描述 (15)✧液晶屏 (16)⏹喷码机操作 (17)✧操作界面架构图 (18)✧新机器开机流程 (19)✧正常开机 (22)✧正常关机 (22)✧停机流程表 (23)✧快速关机 (25)✧整机清洗流程 (25)✧查看喷码机状态参数 (26)✧编辑信息 (27)清除屏幕 (27)选择字体 (27)字符间距 (28)字符方向 (28)字符加粗 (28)插入项目 (28)●插入时钟 (29)●插入序列号 (30)●插入班次: (31)●插入信息: (32)●插入二维码: (33)●插入条形码: (35)●插入串口随机号 (36)●插入磁盘字符串 (38)打印信息 (40)保存信息 (40)另存信息 (40)显示模式 (40)✧选择信息 (41)✧喷印设置 (42)喷印延时 (42)喷印速度 (42)喷印高度 (43)信息方向 (43)粗体喷印 (45)电眼控制 (45)●有效状态 (45)●滤波间隔 (45)●响应方式 (46)速度模式 (46)●内同步 (46)●外同步 (47)重复喷印 (48)充电算法 (49)计米喷印 (49)✧序列号 (50)✧功能限制 (51)✧系统设置 (52)时钟设置 (53)密码设置 (54)计数器 (55)外部接口 (56)事件记录 (56)系统恢复 (56)软件升级 (56)配置信息 (57)通讯设置 (57)特殊设置 (58)✧墨路维护 (59)喷头维护 (59)喷头结构图 (60)黏度标定 (61)手动控制 (61)墨路系统原理图 (63)墨路引灌 (64)墨路排空 (64)飞行时间校准 (64)自动清洗 (64)帮助 (64)✧系统维护 (65)墨线开关 (65)高压开关 (65)喷印测试 (66)喷嘴调制 (67)相位测试 (67)高压监测 (68)黏度监测 (68)压力设置 (68)转速设置 (68)运行时间 (68)✧更多功能 (69)⏹技术参数✧电气规格✧重量喷码机净重量为30Kg。

CY7C68013A_CY7C68014A_CY7C68015A_CY7C68016A_cn

用特定功能的嵌入式微控制器的限制,缩短开发时间以确保 USB 的兼容性。

通用可编程接口 (GPIF) 和主控 / 从器件端点 FIFO(8 位或 16 位数据总线)提供简易的无缝接口,可以与其他通用接口连接, 例如, ATA、UTOPIA、EPP、PCMCIA 和许多 DSP/ 处理器。

FX2LP 消耗的电流低于 FX2 (CY7C68013),具有双倍片上代码 / 数据 RAM,在适用性、外观和功能上与 56、100 和 128 引脚 FX2 一致。

逻辑框图

24 MHz 外部 XTAL

FX2LP

高性能微控制器 使用标准工具 (带有较低功耗选项)

数据 (8)

地址 (16)

/0.5 VCC x20 /1.0

PLL /2.0

1.5k 全速 连接

8051 内核 12/24/48 MHz, 4 个时钟 / 周期

D+

D–

集成 全速和

高速 XCVR

USB 2.0 XCVR

■ 可在商业级和工具级温度下使用 (除 VFBGA 以外的所有封装)

特性 (仅限 CY7C68013A/14A)

■ CY7C68014A: 适用于电池供电应用 ❐ 暂停电流: 100 μA (典型)

■ CY7C68013A: 适用于非电池供电应用 ❐ 暂停电流: 300 μA (典型)

■ 适用于 5 个高达 40 GPIO 的无铅封装 ❐ 128 引脚 TQFP (40 GPIO)、100 引脚 TQFP (40 GPIO)、56 引脚 QFN (24 GPIO)、56 引脚 SSOP (24 GPIO) 和 56 引脚 VFBGA (24 GPIO)

■ CONTROL 传输设置和数据部分的单独数据缓冲区 ■ 集成式 I2C 控制器,运行频率达 100 或 400 kHz

C.A 6550 或 C.A 6555绝缘电阻测试仪用户手册说明书

10 kV/15kV高壓絕緣電阻測試儀14感謝您購買了絕緣電阻測試儀C.A 6550或C.A 6555。

為了從儀器得到最好效果:n仔細閱讀本操作指南,n遵守使用預防措施。

警告,有危險的可能!操作人員無論在任何這個符號出現的時候必須參照本指南。

雙重絕緣保護設備注意!電擊的危險。

USB插口。

接地。

CE標記表示遵照歐洲法規,特別是LVD和EMC。

Chauvin Arnoux公司採用生態設計途徑以設計本設備。

完整生命週期的分析允許我們控制並優化環保方面產品的效果。

特別在回收和再利用方面本設備超出規定所要求。

在垃圾桶上劃線表示在歐盟,產品必須經歷。

本產品不能作為家居廢物處理。

測量種類的定義:n測量種類IV對應低壓設備源的測量。

舉例:電力饋線,電腦和保護設備。

n測量種類III對應建築設備的測量。

舉例:分布面板,電路斷路器,機器或固定工業設備。

n測量種類II對應直接連接到低壓設備的電路的測量。

舉例:供電電源到家用電器和便攜工具。

使用預防措施此儀器和附件符合安全標準IEC 61010-1, IEC 61010-031, and IEC 61010-2-030的低於2000m海拔高度,室內污染程度不超過2級的IV類1000V電壓。

沒有遵守安全指南可能導致電擊,火災,爆炸和儀器設備的損壞。

n操作人員和/或負責機構必須仔細閱讀並清晰理解使用中的預防措施。

使用儀器需要有扎實的知識和電擊的敏銳感官。

n如果你沒有按照說明使用儀器,儀器提供的保護可能被損壞,從而危及到你。

n不要使用那些超出所提到的電壓和類別的電網上的儀器。

n如果儀器看起來損壞,不完整或沒有關好就不要使用。

n每次使用前,檢查導線,外殼,和附件上的絕緣狀況,任何部件絕緣惡化(即使是部分)也必須留待維修或報廢。

n只使用提供的導線和附件。

使用更低壓或類別的導線(或附件)會減少組合儀器+導線(或附件)的電壓或類別。

n系統地使用個人保護設備。

n將雙手遠離已啟動終端。

n操作導線,測試探頭,鱷魚夾時,保持手指在物理防護裝置後面。

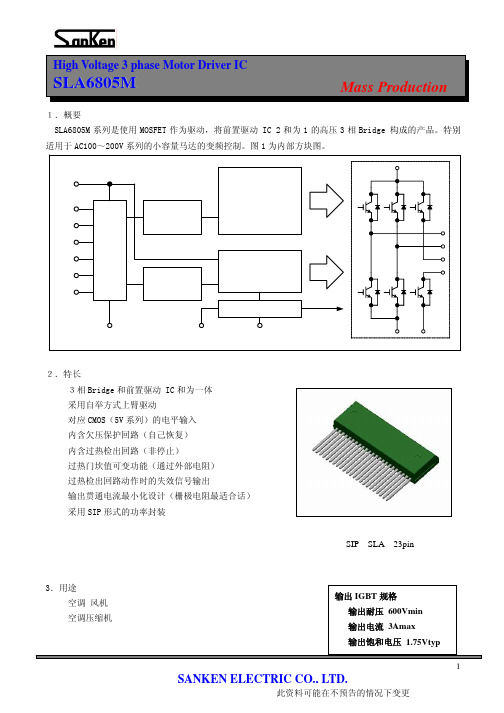

SLA6805M应用手册

10

SANKEN ELECTRIC CO., LTD.

此资料可能在不预告的情况下变更

High Voltage 3 phase Motor Driver IC

SLA6805M

静特性

Mass Production

11

SANKEN ELECTRIC CO., LTD.

此资料可能在不预告的情况下变更

干扰在重新导通时发生误动作,在重新导通起

的设定时间 保持时间 保持时间

的设定时

7

SANKEN ELECTRIC CO., LTD.

此资料可能在不预告的情况下变更

High Voltage 3 phase Motor Driver IC

SLA6805M

6.使用上的注意点 (1)电源时序 电源为序列自由设定。 (2)短路保护

SIP

SLA

23pin

3.用途 空调 风机 空调压缩机

输出 IGBT 规格 输出耐压 600Vmin 输出电流 3Amax 输出饱和电压 1.75Vtyp 1

SANKEN ELECTRIC CO., LTD.

此资料可能在不预告的情况下变更

High Voltage 3 phase Motor Driver IC

调制率 90% 95%

推荐电容容量 三相 PWM 调制方式 120 度通电方式

4.7UF 6.8UF

4.7UF 4.7UF

希望加大自举电流电阻的情况,一定需要扩大电容容量。 另外,开始运转之前,一定先导通Low Side侧,充分让自举电容充电。

◆自举二极管DBOOT 自举二极管使用耐压600V以上,并且逆恢复时间在Trr 100ns以下的产品。二极管的平均电流推荐 1A的产品。

广州谷尔中控C-680系列投标参数

类别:680系列多媒体中央控制系统型号:C-680A(标准型)参数:1.主机与控制面板为分体式设计;主机为标准1.5U全金属机箱,能更好地屏蔽外围信号,抗干扰,可安装在机柜;▲2.主机面板和控制面板都为豪华铝合金面板;▲3.控制方式为感应式按键;▲4.防盗报警功能:支持投影机防盗报警;5.门禁功能:电子锁控制,支持门禁开关机,实现开门即用,关门即走功能;6.开放式控制编程软件:可编程一键切换及开关机功能,用可编程串口码来控制投影机或触控一体机;7.延时断电功能:内置投影机保护功能,防止突然关机切断投影机电源,更好地保护投影机寿命,编程软件可自由设置自动延时断电时间;8.内嵌式红外学习功能,无须配置专业学习器,使用更简单,存储更可靠;9.特有ESD静电保护功能,带电插拔不会损坏内部元器件;10.主机端口:VGA信号4路输入(带音频同步输入), 1路显示器VGA输出,2路投影机VGA 输出(矩阵功能,输出显示器和投影机图像可同步和异步),视频信号2路输入,视频信号2 路输出,6路立体声输入,2路立体声输出,1路RS485网络接口,2路音量可调话筒输入;2组可编程RS232接口,2路可编程红外输出,2路可编程I/O接口,1路门禁接口;2组可控电源输出(银幕电源和投影机电源);▲11.控制面板前置端口:2路USB接口输入,1路RJ45网络接口输出,1路笔记本VGA接口输入(带音频同步输入),1路立体声输入,1路HDMI接口输入,2路话筒接口输入(1路可接鹅颈咪,带按键切换);▲12.控制面板后置端口:2路USB接口输出,1路RJ45网络接口输入,1路笔记本VGA接口输出,1路立体声输出,1路HDMI接口输出, 1路话筒接口输出;▲13.特有智能矩阵功能(预览/投射功能),可实现本机信号及VGA外部输入信号与外接两个VGA 显示设备同步及异步两种显示模式,当异步显示模式时,老师显示器可一边呈现台式电脑内容,另一显示设备呈现展示台或笔记本电脑内容给学生;▲14.主机尺寸:482×67×210mm;控制面板尺寸:200×150×50mm;控制面板开孔尺寸185×131mm;15.资质部份:提供厂家对项目的授权书原件;通过ISO9001质量体系认证;通过ISO14001环境体系认证;通过OHSMS18001职业健康安全管理体系认证;通过3C认证;通过CB认证;计算机软件著作权证书;广东省教育装备行业学会会员单位;中国教育装备行业学会会员单位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。