EDA原理_第12章_通用异步接收发送器的设计与实现41页PPT

异步通信与同步通信课件

异步通信与同步通信的未来融合

融合发展的必要性

异步通信和同步通信各有优劣,未来 将更多地呈现出融合发展的趋势,以 满足不同场景和需求。

技术层面的融合

在技术层面,异步通信和同步通信将 相互借鉴优点,如异步通信的灵活性 和同步通信的高效性。

异步通信与同步通 信课件

目 录

• 通信基础概念 • 异步通信 • 同步通信 • 异步通信与同步通信的比较 • 异步通信与同步通信的发展趋势

01

CATALOGUE

通信基础概念

通信的定义与重要性

通信的定义

通信是信息传输和交换的过程, 通过各种媒介和设备实现信息的 传递。

通信的重要性

通信是现代社会的重要基础设施 ,是人们日常交流、工作、学习 和生活的基础。

05

CATALOGUE

异步通信与同步通信的发展趋势

异步通信的发展趋势

5G/6G技术的推动

异步通信协议的优化

随着5G/6G技术的不断发展和普及, 异步通信将获得更快的传输速度和更 低的延迟,满足更多场景的需求。

为了提高异步通信的性能和效率,相 关协议和标准将不断得到优化和完善 。

云计算和边缘计算的融合

03

CATALOGUE

同步通信

同步通信的定义与特点

同步通信定义

在通信过程中,发送方和接收方的时钟信号保持一致,数据在固定的时间间隔内 传输。

同步通信特点

需要精确的时钟同步,数据传输效率高,适用于高速、大数据量通信。

同步通信的GPS或网络时间协议)实现时

钟同步。

应用层面的融合

在应用层面,异步通信和同步通信将 共同服务于各类场景,如物联网、云 计算、大数据等。

EDA书上和PPT整理的讲解

1、EDA的定义:EDA全称为Electronic Design Automation,是以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及试验开发系统为设计工具,通过有关开发软件,自动完成从软件方式设计电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、逻辑布局布线、逻辑仿真,直至对于特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专用集成芯片的一门新技术。

2、EDA进行电子设计特点:①软件方式的硬件设计②软件到硬件的转换由开发软件自动完成③设计过程中可用软件仿真④在线可编程isp⑤单芯片集成系统,高集成可靠性、低功耗3、EDA三个发展阶段(并介绍时代特点):计算机辅助设计Computer Aided Design计算机辅助工程设计Computer Aided Engineering Design电子设计自动化Electronic Design Automation1)计算机辅助设计阶段(20世纪70年代):选用中小规模集成电路把设计繁杂劳动如布线布图用2D图形编辑与分析的CAD工具替代系统调试在组装好的PCB上进行2)计算机辅助工程设计阶段(20世纪80年代):EDA工具以逻辑模拟、定时分析、故障仿真、自动布局和布线为核心重点解决设计完成之前的功能检测等问题具有自动综合能力的EDA工具大部分原理图出发的工具不适应复杂系统设计3)电子设计自动化阶段(20世纪90年代):设计芯片,使用硬件转向设计硬件,片上系统集成,单片系统SOC工具的抽象设计能力,框图、状态图与流程图编辑,具有硬件描述语言(VHDL, ABEL, AHDL),标准元件库超越电子设计范畴进入其他领域,基于EDA的单片系统SOC,软硬核功能库,基于VHDL自顶向下的设计理念4、EDA的软件系统构成(书P6)完整的EDA软件系统应包括:设计输入、设计数据库、分析验证、综合仿真、布局布线等模块设计输入:接受设计输入,语义分析及检查设计数据库:存放系统库单元、用户设计描述及中间设计结果分析验证:各层次模拟验证、设计规则检查、故障检查等综合仿真:各层次综合工具,理想状况为高层次到低层次综合仿真全部由EDA工具自动实现。

集成电路设计的EDA系统.pptx

第12页/共75页

逻辑模拟

• 逻辑模拟的基本概念:将逻辑设计输入到计算机,用软件方法形成硬件的模型, 给定输入波形,利用模型算出各节点和输出端的波形,判断正确否

• 主要作用:验证逻辑功能和时序的正确性

• 分类:根据所模拟逻辑单元规模的大小

• 整个设计过程就是把高层次的抽象描述逐级向下进行综合、验证、实现,直到物理级的低层次描述,即掩 膜版图。

• 各设计阶段相互联系,例如,寄存器传输级描述是逻辑综合的输入,逻辑综合的输出又可以是逻辑模拟和 自动版图设计的输入,版图设计的结果则是版图验证的输入。

• ICEDA系统介入了包括系统功能设计、逻辑和电路设计以及版图设计等在内的集成电路设计的各个环节

• 分配:给定性能、面积/功耗条件下,确定相应的RTL级单元来实现各种操 作,产生相应的数据通道,即将行为(如数据处理、存储、传输等)与元件 对应起来

• 调度:确定这些操作单元的次序 • 结果:与工艺无关的通用RTL级单元组成的结构描述

第8页/共75页

逻辑综合

• 概念:通过逻辑综合器结合单元库,将RTL级描述转换成逻辑级描述 • 核心:由给定的功能和性能要求,在一个包含许多结构、功能、性能已知的逻辑

• VHDL • Verilog HDL

第6页/共75页

综合

• 概念:通过附加一定的约束条件,结合相应的单元库,从设计的高层次向低层 次转换的过程,是一种自动设计的过程

• 分类: • 高级综合:从算法级到寄存器传输(RTL)级 • 逻辑综合:从寄存器传输级到逻辑级

第7页/共75页

高级综合

• 概念:结合RTL级单元库,将算法级描述转换成RTL级描述 • 核心:分配(ALLOCATION)和调度(SCHEDULING)

EDA原理及应用 共263页PPT资料

EDA技术发展历史

EDA技术随着计算机、集成电路、电子系统设 计的发展,经历了三个发展阶段:

1、计算机辅助设计(CAD) 2、计算机辅助工程设计(CAE) 3、电子设计自动化(EDA)

1、计算机辅助设计(CAD)

硬件设计发展的初级阶段。在此阶段,大量选用中 小规模标准集成电路,将产品设计过程中高度重复 性的布图布线工作,采用二维图形编辑与分析的 CAD工具。由于PCB布图布线工具受到计算机工作 平台的制约,其支持的设计工作有限且性能比较差。

广义EDA技术,是通过计算机及其电子系统的辅助 分析和设计软件,完成电子系统某一部分的设计过 程。因此,广义EDA技术除了包含狭义的EDA技术 外,还包括计算机辅助分析CAA技术(如PSPICE, EWB,MATLAB等),印刷电路板计算机辅助设计 PCB-CAD技术(如PROTEL,ORCAD等)和其它高 频和射频设计和分析的工具等。

2、设计输入 设计输入是将所设计的系统或电路以开发软件要求 的某种形式表示出来,并输入EDA工具的过程。常 用的方法有硬件描述语言(HDL)和原理图输入方 法等。 原理图输入方式是一种最直接的描述方式,在可编 程芯片发展的早期应用较广,它将所需的器件从元 件库中调出来,画出原理图。这种方法虽然直观并 易于仿真,但效率低,且不易维护。更主要的缺点 是可移植性差。 HDL语言输入法利用文本描述设计,主要使用行为 级HDL,其主流语言是Verilog HDL和VHDL。

6、大多数EDA软件都具有仿真和模拟功能;

EDA技术的主要内容

基于狭义EDA技术进行可编程逻辑器件的设计应掌 握以下几个方面的内容: 1、大规模可编程逻辑器件PLD,是利用EDA技术 进行电子系统设计的载体; 2、硬件描述语言HDL,是利用EDA技术进行电子 系统设计的主要表达手段; 3、EDA设计软件EDAS:是利用EDA技术进行电 子系统设计的自动化设计工具; 4、相关的硬件平台,是利用EDA技术进行电子系 统设计的下载工具及硬件验证工具;

EDA课件

电子与通信工程系

ARCHITECTURE dff_ck_en OF dff_ck_en IS BEGIN PROCESS(clk,reset,en) BEGIN IF reset=‘0’ THEN q<=‘0’; ELSIF clk’event AND clk=‘1’ THEN IF en=‘1’ THEN q<=data; END IF; END IF; END PROCESS; END dff_ck_en;

电子与通信工程系

4位加法计数器

(课本P84)

ENTITY CNT4 IS PORT ( CLK : IN BIT ; Q : BUFFER INTEGER RANGE 15 DOWNTO 0 ) ; --不推荐使用BUFFER END ; ARCHITECTURE bhv OF CNT4 IS BEGIN PROCESS (CLK) BEGIN IF CLK'EVENT AND CLK = '1' THEN Q <= Q + 1 ; END IF; END PROCESS ; END bhv;

电子与通信工程系

带同步复位的上跳沿D触发器

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL;

ENTITY dff_syn_reset IS PORT ( data :IN clk :IN reset :IN q :OUT END dff_syn_reset;

std_logic; std_logic; std_logic; std_logic);

触发器 锁存器

电子与通信工程系

Latch

锁存器是电平触发的,锁存器的值在时钟的一个逻辑状态 可以更改,在另一个逻辑状态被保存下来,因此在使能阶 段输入端的一个毛刺也会导致电路的误操作,无法阻止毛 刺的传播,容易产生较多的竞争冒险现象。

EDA部分课件(常见电路)

四、程序说明 1.本设计可用顺序语句中的IF语句或并行语句中的条件 信号赋值语句来描述。因为这两类语句本身就具有优先顺 序。在本例中,输入端d7的优先级最高,只要d7=‟0‟,无 论其他输入端为何值,编码器的结果都由d7=‟0‟决定;d0 的优先级最低,只有当其他输入端信号无效时,才对 d0=‟0‟进行编码。

• • • • • • • • • • • • •

使用LOOP语句 architecture behav3 of priorityencoder is begin process( input) variable i:integer; begin for i in 0 to 7 loop if input(i) =„0‟ then y<=conv_std_logic_vector(i,3); end if; end loop; end process; end behav3;

• P1:process(a,dr,en) • begin • if ((en=„0‟) and (dr=„1‟) then • bout<=a; • else • bout<=“ZZZZZZZZ”; • end if; • b<=bout; • end process p1;

• P2: process(b,dr,en) • begin • if ((en=„0‟) and (dr=„0‟) then • bout<=b; • else • aout<=“ZZZZZZZZ”; • end if; • a<=bout; • end process p2; • end rt;

PROCESS(d) BEGIN IF d(7)=‟0‟ THEN y<=”000”; ELSIF d(6)=‟0‟ THEN y<=”001”; ELSIF d(5)=‟0‟ THEN y<=”010”; ELSIF d(4)=‟0‟ THEN y<=”011”; ELSIF d(3)=‟0‟ THEN y<=”100”; ELSIF d(2)=‟0‟ THEN y<=”101”; ELSIF d(1)=‟0‟ THEN y<=”110”; ELSIF d(0)=‟0‟ THEN y<=”111”; END IF; END PROCESS; END beh;

基于EDA技术的通用异步收发器设计

基于EDA技术的通用异步收发器设计作者:张雪来源:《中国新通信》2016年第22期【摘要】 EDA技术属于现代电子设计技术的核心内容,随着时代的发展在通信领域、电子信息领域均逐渐得到了广泛的应用。

另外,信息网络技术时电子信息技术的重要组成部门,掌握信息网络技术的情况下能够获得更加完整的数据、计算机通信概念,便于更好的从事计算机通信、数据通信工作。

本文在将EDA技术作为基础技术的情况下,重点分析了通用亦不收发器中多个层面的设计,希望能够更好的应用EDA技术。

【关键词】 EDA技术通用异步收发器数据通信前言:在数据通信系统当中,经常采用串行通信以促使信息数据交换。

异步串行通信具有比较高的可靠性,且传输线比较少,能够进行远距离的传输,当前已经能够在计算机以及外设的数据交换方面得到广泛应用。

其进行数据传输时一般均需要利用通用异步收发器。

与此同时,恰当的利用EDA技术优势对串行通信接口进行设计,能够便于人们更加直观的了解到数据链路层的工作原理,亦能够更加恰当的将其应用到实际当中。

一、EDA技术与通用异步收发器概述EDA技术即是指电子设计自动化技术,属于将计算机技术恰当应用于电子设计过程的新技术和,已经能够在电子电路设计与方针、集成电路板图设计、可编程器件的编程以及印刷电路板设计等领域得到广泛应用。

通用异步收发器简称UART,是一种通用串行数据总线,能够进行双向通信并实现全双工传输和接收。

当前,在嵌入式设计当中,通用异步收发器主要用于与计算机进行通信。

通用异步收发器在工作当中基本上分为发生和接收两个过程,并且会涉及到奇偶校验位发生器、波特率发生器、顶层模块等模块。

二、基于EDA技术的通用异步收发器的具体设计2.1奇偶校验位发生器设计基于EDA技术的通用异步收发器奇偶校验位发生器设计,必须要能够满足以下几个方面的功能:首先,所设计的奇偶校验位发生器,要能够根据奇偶校验规则,即奇校验为ODD,偶校验为EVEN,进行恰当选定后输入相应的串行二进制数据,将校验位进行准确的计算,并且与输入的串行数据校验位进行比较,由此判断数据的正确或者错误。

eda原理图

1. 系统概述

MAX+plus II是Altera公司在 Windows 环 境下开发的可编程逻辑设计软件平台。该系 统将数字电路设计集成在一个环境内,支持 Altera公司的可编程器件,允许多种输入方式 的设计文件。经过系统编辑器的编译、综合 等操作,对设计进行功能模拟、逻辑分析、 自动布局布线、延时时间分析、下载编程, 最后将电路分配到一个或多个器件中。

六、EDA软件工具介绍

(一)EDA工具的基本功能(PLD-->ASIC) PLD:Programmable Logic Device

ASIC:Application Specific Integrated

Circuit (二) PLD器件的开发设计流程 (三) EDA工具的应用环境 (四) EDA工具的来源

3. 推荐的系统配置

500MHz以上奔腾PC机; Windows98或更高版本; 有效内存和物理存储空间与使用的器件有关。

器件系列 ACEX1K FLEX10K FLEX8000 FLEX6000 MAX9000 MAX7000

有效内存 256 256 64 64 64 48

物理RAM 128 128 32 32 32 16

特点

EDA课程的教学目标

了解可编程逻辑器件的基本原理,掌握一种

描述语言,掌握一种设计软件,具备有效地 完成数字系统设计的能力。

EDA课程的考核要求

EDA课程教材及参考资料 教材:专用集成电路与电子设计自动化 图书馆的参考书籍及相关期刊资料

实验指导书 —— 自编

相关网站:学院教学网站及国际著名公司网站

EDA软件工具 ---- MAX+plus II MAX+plus : Multiple Array Matrix and

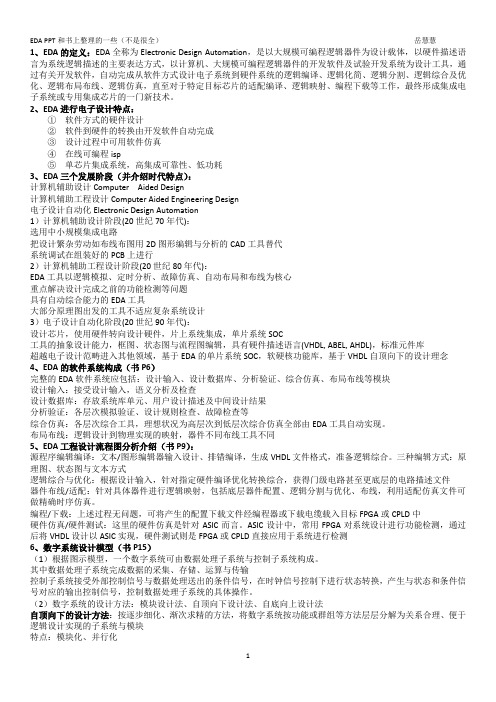

EDA-基本逻辑电路设计ppt课件

组合逻辑电路设计/译码器和编码器

译码器:将二进制码译成一组与输入代码一一对应的高、 低电平信号的过程称为译码。实现译码的电路称为译码器。 译码器是把输入的数码解出其对应的数码。 如果有N个二进制选择线,则最多可译码转换成2N个数 据。 如果一个译码器有N条输入线及M条输出线时,则称为 N×M译码器。 编码器:用特定的n位二进制代码表示某一种信息的过程 称为编码。实现编码功能的电路称为编码器。 编码器的功能与译码器恰好相反。 编码器是将2N个分离的信息代码以N个二进制码来表示。 如果一个编码器有N条输入线及M条输出线时,则称为 N×M编码器。

二、时序逻辑电路设计

1、锁存器 2、触发器 3、触发器的应用

时序逻辑电路设计/锁存器

锁存器(flip-latch)与触发器(flip-flop) 相同点:都具有记忆功能,存储二进制信号。 不同电:锁存器没有时钟信号作为启动信号;而触发 器有一个脉冲信号来启动它。 常用锁存器有RS锁存器和D锁存器。 d q ena D锁存器 d为数据输入端,ena为使能端。当ena=1时输出端状态 随输入端状态而变,当ena=0时输出端状态不变。

组合逻辑电路设计/简单门电路/ 2输入“与门”电路

查表法——利用真值表——行为描述方式 ARCHITECTURE ART OF MYAND2_1 IS BEGIN PROCESS(A,B) VARIABLE AB:STD_LOGIC_VECTOR(1 DOWNTO 0); BEGIN AB:=A&B; CASE AB IS WHEN "00"=>Y<='0'; WHEN "01"=>Y<='0'; WHEN "10"=>Y<='0'; WHEN OTHERS=>Y<='1'; END CASE; END PROCESS; END ART;

EDA教程第一章

课程所要解决的问题?

当你们经历了以上的痛苦后,不知道你们想过下 面的问题没有? 能不能让计算机帮助化简卡诺图?而且是多个 变量? 能不能用一种芯片实现多个分离小规模数字IC 能不能用一种芯片实现多个分离小规模数字IC 的功能,并且在芯片内部将这些功能连接? 设计数字系统能不能象C 设计数字系统能不能象C语言那样,只关心“如 何描述”一个数字系统,而不是“如何具体实 现”数字系统。

数字系统EDA技术发展概述 数字系统EDA技术发展概述

EDA技术所涉及的领域相当广泛,业界一般将 EDA技术所涉及的领域相当广泛,业界一般将 EDA技术分成: EDA技术分成: 狭义EDA技术 狭义EDA技术 广义EDA技术 广义EDA技术

数字系统EDA技术发展概述 数字系统EDA技术发展概述

狭义EDA技术 狭义EDA技术,就是指以大规模可编程逻辑器件为 技术,就是指以大规模可编程逻辑器件为 设计载体,以 设计载体,以硬件描述语言为系统逻辑描述的主要表达方 式,以 式,以计算机、大规模可编程逻辑器件的开发软件及实验 开发系统为设计工具,通过有关的开发软件,自动完成用 开发系统为设计工具,通过有关的开发软件,自动完成用 软件方式设计的电子系统到硬件系统的: 软件方式设计的电子系统到硬件系统的: 逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、 逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、 逻辑布局布线、逻辑仿真, 逻辑布局布线、逻辑仿真,直至对于特定目标芯片的适配 编译、逻辑映射、 编译、逻辑映射、编程下载等工作 最终形成集成电子系统或专用集成芯片的一门新技 术,或称为IES/ASIC自动设计技术。 术,或称为IES/ASIC自动设计技术。

数字系统设计技术发展历史

年代 事件

公元前3000年 公元前 年 1614-1617

第一讲-EDA简介PPT课件

31

32

(2)右击鼠标,选择“Enter Symbol”,

33

34

35

(3)调入所需各元件,并连接好, 输入各引脚名:a、b、co、so

(4)将图文件取名为:h_adder.gdf,存入E:\MY_PRJCT目录 “File”→ “ Save As”→ …… → “ OK”

9

自顶向下的设计流程

10

5. EDA与传统电子设计方法的比较

传统的电子系统或IC设计中,手工设计 占了较大比例。缺点如下:

(1)复杂电路的设计、调试十分困难; (2)如果某一过程存在错误,查找和修改十分不便; (3)设计过程中产生大量文挡,不易管理; (4)对于集成电路设计而言,设计实现过程与具体

在 MAX+plusⅡ编译设计主控界面上,它显示了 MAX+plusⅡ自动设计的各主要处理环节和设计流程, 包括设计输入编辑、编译网表提取、数据库建立、逻 辑综合、路基分割、适配、延时网表提取、编程文件 汇编(装配)以及编程下载9个步骤。

22

编译设计 主控界面

23

MAX+plusⅡ设计流程

编译网表 提取

2

1. EDA技术实现目标

利用EDA技术进行电子系统设计,最后的目标 是完成专用集成电路ASIC的设计和实现。

三条实现途径: 1)超大规模可编程逻辑器件***

主流器件:

FPGA(Field Programmable Gate Array) CPLD (Complex Programmable Logic Device)

EDA可编程逻辑器件结构与原理课件

什么是EDA可编程逻辑器件?

EDA可编程逻辑器件,简称PLD(Programmable Logic Device),是一种集成电路,用于实现数字逻 辑函数。它可以根据用户的需求进行编程,灵活地实现各种逻辑电路。

EDA可编程逻辑器件的工作原理

1

编程

使用特定的编程语言编写逻辑功能,

配置

2

并将其加载到可编程逻辑器件中。

将逻辑功能映射到器件的可编程部

分,实现用户定义的逻辑电路。

3

运行

经过配置后的可编程逻辑器件将开 始运行,执行用户定义的逻辑功能。

EDA可编程逻辑器件的应用领域

1 数字电路设计

2 嵌入式系统开发

可编程逻辑器件广泛应用于数字电路设 计,如ASIC开发、FPGA设计等。

可编程逻辑器件可用于开发嵌入式系统, 如处理器控制、通信接口等。

3 自动化控制

4 通信设备

可编程逻辑器件可用于控制系统的设计 和实现,如工业自动化、机器人控制等。

可编程逻辑器件被广泛应用于通信设备, 如路由器、交换机、光纤通信等。

局限

资源占用:逻辑功能复杂时,可能需要较 大的器件。

EDA可编程逻辑器件的发展趋势

更高集成度

未来可编程逻辑器件将不断 提高集成度,实现更多功能 在同一器件上。

人工智能与自动化

可编程逻辑器件将与人工智 能和自动化技术相结合,实 现更智能化的应用。

量子计算

可编程逻辑器件可能在量子 计算领域发挥重要作用,推 动计算机技术的发展。

EDA可编程逻辑器件的结构和组成

EDA学习大全PPT课件

图2-12 原理图管理浏览窗口

36

图2-13 添加/删除元件库对话框

37

2.3 放 置 元 件

1 利用浏览器放置元件

▪ 在如图2-12所示中的【Browse】选项的下拉式选 框中,选中【Libraries】项。

▪ 然后单击列表框中的滚动条,找出元件所在的元 件库文件名,单击鼠标左键选中所需的元件库; 再在该文件库中选中所需的元件。

3

2.印制电路板设计系统

▪ 印制电路板设计系统是一个功能强大的印制电 路板设计编辑器,具有非常专业的交互式布线 及元件布局的特点,用于印制电路板(PCB) 的设计并最终产生PCB文件,直接关系到印制 电路板的生产。

▪ Protel 99 SE的印制电路板设计系统可以进行 多达32层信号层、16层内部电源/接地层的布 线设计,交互式的元件布置工具极大地减少了 印制板设计的时间。

▪ 注意文件名后缀为.sch

24

图2-7 新建原理图文件

25

4 设计管理器

▪ 启动protel99se后设计管理器处于打开状态,以 树状结构显示出设计数据库中的文件、组织形式 和库中各文件间的逻辑关系。

▪ 双击文件夹可展开一个树,并可通过单击小加号 展开分支,单击小减号折叠分支,如图2-8所示。

31

图2-10 文档属性对话框

32

Sheet option标签有以下内容:

▪ 图纸走向(orientation):landscape为水平走向,portrait为垂直走向。 ▪ 图纸颜色:border color为图纸边框颜色,sheet color为图纸颜色。 ▪ 图纸尺寸:standard style为国际认可的标准图纸,有18种可供选择。

▪ 设计管理器主要用于管理各种文档,包括创建、 打开、关闭和删除设计数据库文件,删除访问成 员和修改密码与权限等操作。

EDA原理_第12章_通用异步接收发送器的设计与实现共41页

发送模块将发送的数据送到DBIN端口,并且将其转换 成一个字节的串行发送数据,转换完的数据TXD端口上。

UART的设计和实现-接收模块的设计

接收模块接收串行数据并将其转换为并行数据。该 设计包括下面几个部分:

UART的设计和实现-发送模块的状态机

在delay状态下,发送数据按照正确的波特率发送数 据。当tdelayctr与波特率常数一样时,结束该状态。进 入到Shift状态。一旦进入到waitwrite状态,结束发送过 程。在这个状态需要确认WR信号为高,才能开始发送 过程。

UART的设计和实现 -发送模块的状态机内部结构

该电子教案为<<EDA原理及VHDL>>一书的配套教学资源 版权所有,不得用于其它商业用途

通用异步接收发送器 的设计和实现

何宾 2019.09

UART的设计和实现-本章概要

本章给出了PLD器件在简单通信系统的应用-UART设计。 通用异步接收/发送器的设计也是PLD在通信系统的经典应 用。该章首先介绍了UART设计原理,其中包括UART原 理和设计描述、接收模块设计,随后介绍了UART的 VHDL代码描述,最后介绍了URAT的软件仿真验证和硬 件验证。

:= "101000110";

signal rdReg

: std_logic_vector(7 downto 0)

:= "00000000";

signal rdSReg

: std_logic_vector(9 downto 0)

:= "1111111111";

实例分析EDA技术下的通用异步收发器设计

实例分析EDA技术下的通用异步收发器设计数据通信系统中,通过串行通信来达到交换信息数据的目的是经常采用的方式。

异步串行通信要求的传输线少,可靠性高,传输距离远,被广泛应用于PC机和外设的数据交换。

通常都由通用异步收发器UART(Universal Asynchronous Receiver/Transmitter)来实现该功能。

同时在电子设计领域中,SOC片上系统技术日趋成熟,设计者可以在单块或极少数的几块芯片中实现整个系统的功能,将UART的功能模块集成到可编程逻辑器件FPGA (Field Programmable Gate Array)中。

利用EDA(Electronic Design Automation)技术优点来设计串行通信接口,不仅可以直观的让同学们了解到数据链路层的工作原理,还可以在分工协作中深刻领会EDA技术在网络通信中的实际应用。

1 UART工作原理和流程通过对UART工作原理的分析,我们把整个系统模块可划分波特发生器,內核,信号检测器,移位寄存器,奇偶校验器,总线选择器和计数器等。

UART的工作流程可以分为发生和接收两个过程。

1.1 接收过程当UART信号监测器模块的输入口侦测到数据时,即输入口由高电平变为低电平,UART读取串行数据并且将数据并行输给计算机。

首先UART内核会重置波特率发生器和移位寄存器,并且设置移位寄存器的时钟为波特率时钟,以准备接收串行数据。

接着,移位寄存器模块在波特率时钟的驱动下,不断读取串行总线的输入数据,并将串行数据保存在内部的寄存器中。

接收完毕,UART内核会对已接收的数据进行奇偶校验并输出校验结果。

同时,UART内核会复位信号监测器,以准备进行下一次数据接收。

1.2 发送过程由加载Load和发送Send两个部分组成,如图3所示。

加载是内核依串行发送的顺序将起始位、数据位和奇偶校验位依次加载到移位寄存器内,这个过程移位寄存器工作在系统时钟下,相对于外部总线传输速度来说非常快。

EDA原理及应用264页PPT

6、实现与布局布线 将综合生成的逻辑网表配置到具体的FPGA芯片 上,布局布线是其中最重要的过程。布局将逻辑网 表中的硬件原语和底层单元合理地配置到芯片内部 的固有硬件结构上,并且往往需要在速度最优和面 积最优之间作出选择。布线根据布局的拓扑结构, 利用芯片内部的各种连线资源,合理正确地连接各 个元件。布线结束后,软件工具会自动生成报告, 提供有关设计中各部分资源的使用情况。 由于只有FPGA芯片生产商对芯片结构最为了解, 所以布局布线必须选择芯片开发商提供的工具。

3、功能仿真 功能仿真也称为前仿真,是在编译之前对用户所设 计的电路进行逻辑功能验证,此时的仿真没有延迟 信息,仅对初步的功能进行检测。仿真前,要先利 用波形编辑器和HDL等建立波形文件和测试向量 (即将所关心的输入信号组合成序列),仿真结果 将会生成报告文件和输出信号波形,从中便可以观 察各个节点信号的变化。如果发现错误,则返回设 计修改逻辑设计。 常用的工具有Model Tech公司的ModelSim、 Sysnopsys公司的VCS和Cadence公司的NCVerilog, 以及NC-VHDL等软件。

2、设计输入 设计输入是将所设计的系统或电路以开发软件要求 的某种形式表示出来,并输入EDA工具的过程。常 用的方法有硬件描述语言(HDL)和原理图输入方 法等。 原理图输入方式是一种最直接的描述方式,在可编 程芯片发展的早期应用较广,它将所需的器件从元 件库中调出来,画出原理图。这种方法虽然直观并 易于仿真,但效率低,且不易维护。更主要的缺点 是可移植性差。 HDL语言输入法利用文本描述设计,主要使用行为 级HDL,其主流语言是Verilog HDL和VHDL。

EDA技术的共同特点: 1、通过使用相应的电路分析和设计软件,完成电子 系统各部分的设计;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

RXD=’1’

ctr!=”1000”

ctr(3)=’1’ or datactr!=”1010”

RST

idle

RXD=’0’ EightDelay ctr!=”1000” Waitfor0

dataRst=’1’

ctRst=’1’

dataRst=’1’

CheckStop CE=’1’

Datactr!=”1010”

Transfer状态准备发送移位寄存器发送数据。设置 load=’1’,移位寄存器开始加载数据,其顺序是一个起始 位、一个字节的DBIN数据、一个奇偶校验位和一个停止 位。下一个状态进入到shift状态。在该状态下,移位信号 置‘1’,表示移位寄存器移1。Tfincr信号也置1表示递增

数 据计数器。如果数据计数器不等于9,表示发送移位寄存 器没有进行移位操作,此时进入delay状态。如果移位完 成,此时进入WaitWrite状态。

:

std_logic;

: std_logic;

:

std_logic;

:

std_logic

:= '0';

:

std_logic

:= '0';

:

std_logic

:= '0';

:

std_logic;

:

std_logic

:= '0';

:

std_logic

:= '0';

:

std_logic

:= '0';

:

std_logic

UART的设计和实现-发送模块的状态机

在delay状态下,发送数据按照正确的波特率发送数 据。当tdelayctr与波特率常数一样时,结束该状态。进 入到Shift状态。一旦进入到waitwrite状态,结束发送过 程。在这个状态需要确认WR信号为高,才能开始发送 过程。

UART的设计和实现 -发送模块的状态机内部结构

两个计数器中的一个计数器用于延迟发送控制器,另 一个计数器用来计算发送的串行数据位的个数。TXD端口 和发送移位寄存器的最低位连接。

UART的设计和实现-发送模块的状态机

WR=‘0’

RST

idle tdelayRst=’1’

TBE=’1’

WR=’1’

Transfer tdelayrst=’ load=’1’ tclkrst=’1’

这两个状态保证有足够的延迟保证读取采样数据的 正中间。当计数器计数到10(8个数据位、一个奇偶位 和一个停止位),然后进入到CheckStop状态。这个状 态进行奇偶校验。当该状态结束后,进入到idle状态。

START D0 D1 D2 D3 D4 D5 D6 D7 PAR STOP

对接收数据进行采样的时序的描述

UART的设计和实现-差错控制的实现

差错控制寄存器分析接收到的数据,并对三种错误进 行判断:奇偶错、帧错误和溢出错误。

奇偶错误指接收数据的得到的校验和与接收到的Par不 一样。当进行偶校验的时候,D0到D7的和应该是偶数, 否则是奇校验。该设计中缺省设置为偶校验。当奇偶校验 错误时,PE端口为高。

UART的设计和实现-设计原理

该设计包含下面几个方面: 并行/串行和串行/并行数据转换 使用用户定义的奇偶校验位(缺省设置为奇校验) 数据波特率可修改(缺省9600) 包含测试代码和测试向量

UART的设计和实现-符号描述图

UART

RXD DBIN RDA RD WR RST

TXD DBOUT

Ctr(3)=’0’and Datactr!=”1010”

GetData

Ctr(3)=’1’ Waitfor1

dataIncr=’1’ rShift=’1’

Ctr(3)=’0’

UART的设计和实现-接收模块状态机原理

当处于idle状态时,串行数据管脚RXD处于高电平状 态,在该状态一直等待直到检测到RXD为低电平时,进入 到EightDelay状态。

begin --------------------------------------------------------------------------Title: 初始信号定义 ------------------------------------------------------------------------frameError <= not rdSReg(9); parError <= not ( rdSReg(8) xor (((rdSReg(0) xor rdSReg(1)) xor (rdSReg(2) xor

’

tfctr=”1001”

CheckStop CE=’1’

Shift

Shift=’1’ Tfctr=’1’

Tdelayctr= bandrate

Tfctr!=”1001”

Delay

UART的设计和实现-发送模块的状态机

UART在idel状态,当WR为高时状态发生变化。然 后,发送模块加载DBIN端口的数据,下一个状态发送数 据。

Hale Waihona Puke UART的设计和实现-原理和设计描述符号

接收模块

RXD DBOUT

RDA RDA

RD

PE

CLK

OE

FE

发送模块

DBIN WR

TXD TBE

CLK

UART的设计和实现-原理和设计描述

UART设计包含两个主要模块,这两个模块封装在一 个UART的设计文件中。

这两个模块一个处理接收的串行数据,另一个处理发 送的串行数据。

串行数据控制器 用于同步的两个计数器 移位寄存器,移位寄存器保存来自RXD的数据。 错误比特控制器。 来自RXD串口的数据以一定的波特率被接收,所以 需要有个控制器同步接收数据的采集相位。串行同步控 制器的设计采用了一个状态机和两个同步计数器。在设 计中,在每个接收比特数据的中间采集数据。

UART的设计和实现-接收模块状态机

:= "101000110";

signal rdReg

: std_logic_vector(7 downto 0)

:= "00000000";

signal rdSReg

: std_logic_vector(9 downto 0)

:= "1111111111";

signal tfReg

: std_logic_vector(7 downto 0);

RDA TBE

PE E FE

UART的设计和实现-原理和设计描述

UART设计主要包括两部分:并行数据转化成串行数 据,串行数据转换成并行数据。

UART设计的接收端口将接收到的串行数据转换成 并行数据,同时UART的发送端口负责并行数据转换成串 行数据。

测试代码完成对UART设计的验证,该验证已经在 Xilinx大学计划提供的开发平台进行了验证,该设计也很 容易的移植到其它的EDA平台上。

在该状态,主要是进行同步,使得在每个比特位的中间 采样数据,计数器ctr比波特率快16倍。在该状态下,ctr计 数到8。然后进入到WaitFor0状态,waitfor1状态跟在其 后,这两个状态的转移由ctr的最高两位确定。进入到 GetData状态时,开始对RXD数据进行移位。

UART的设计和实现-接收模块状态机原理

:= '0';

:

std_logic := '0';

:

std_logic_vector (12 downto 0);

:

std_logic := '0';

:

rstate := strIdle;

:

rstate;

:

tstate:= sttIdle;

:

tstate;

UART的设计和实现-UART的VHDL设计代码

UART的设计和实现-设计原理

基于通用异步接收发送器UART的RS-232接口是以 前计算机上提供的一个串行数据接口,用来将接收的串 行数据转换成并行数据,同时将并行数据转换成串行数 据后发送出去。当PLD和其它外设通过串口通信时就非 常有用。UART发送的数据,经过电平转换后,传送到 PLD的外部串行总线接口,然后这些串行数据被送到 PLD内部进行处理。被处理的数据然后转换为串行数据 经电平转换后传回串口。

帧错误是指UART在给定的时序没有正确的读到数 据。当停止位不为1时,表示帧错误,此时FE端口为1。

溢出错误是指,当前帧接收完,但还没有读时下一帧 数据就到了的情况。当单字节的串行数据可读时RDA为 高,移位后的并行数据放在DBOUT端口。一旦RDA端口 为高,且此时数据仍在DBOUT端口时,OE溢出错误标志 为高。

type tstate is (sttIdle,sttTransfer,sttShift,sttDelay,sttWaitWrite);

constant baudRate : std_logic_vector(12 downto 0) := "1010001011000";

constant baudDivide : std_logic_vector(8 downto 0)

UART的设计和实现-UART的VHDL设计代码

entity UARTcomponent is Port ( TXD RXD CLK DBIN DBOUT RDA TBE RD WR PE FE OE RST );

end UARTcomponent;

: out : in : in : in : out : inout : out : in : in : out : out : out : in