LIS8110_Datasheet _V1.1

ANT8110V1.1

ANT8110

3W Class D 全差分输入单声道音频功放

3

W

2.25

W

1பைடு நூலகம்7

W

1.3

W

0.13

%

90

dB

70

dB

1.8

2

5.5

V

-0.3

0

0.4

V

150

℃

20

℃

引脚定义及功能

引脚分配图

SD 1 VREF 2

INP 3 INN 4

ANT8110

88 VON 77 GND 66 VDD 55 VOP

MAX 1.75 0.225 1.50 0.70 0.48 0.43 0.26 0.21 5.10 6.20 4.10

0.50 0.80

8°

第 8 页 ,共 8 页

深圳市安耐科电子技术有限公司

ANT8110

3W Class D 全差分输入单声道音频功放

ANT8110 外围参数设置

增益设置: ANT8110 通过外置的输入电阻设置放大器增益,增益的设置遵循以下公式:

Av=Rf/Ri,

其中 Rf 为内置的反馈电阻,其值为 360K,Ri 为外置的输入电阻,客户可以根据自身 对增益的需要,灵活设置 Ri 的值。

ANT8110 差分输入模式电路图

1uF

pin6

VIN

56nF 30k pin4 INN

VDD

VIP

56nF 30k

Shut downn

pin3 INP pin1

SD

pin8 VON

ANT8110

pin5 VOP

1uF pin2 VREF

GND

LQ8110E无线通讯模块使用说明书

LQ8110E无线通讯模块使用说明书 V1.1山东力创科技有限公司目录一、产品简介 (3)1.1 产品概述 (3)1.2 产品特点 (3)1.3 技术参数 (3)1.4 应用领域 (4)二、产品安装 (4)2.1 安装要求 (4)2.2 开箱 (4)2.3 安装尺寸 (5)2.4 供电电源 (5)2.5 SIM卡安装 (5)2.6 数据线连接 (6)2.7 工作状态指示 (6)2.8 终端使用注意事项 (6)三、DTU参数设置 (7)3.1 参数配置方法 (7)3.2 所要配置的参数 (7)四、功能说明 (10)4.1 TCP 客户端模式 (10)4.2 UDP SERVER模式 (11)4.3 UDP LICHUANG模式 (12)4.4 UDP Client模式 (13)4.5 UDP HD Client模式 (14)4.6 SMS PDU Mode (14)4.7 开关量 (15)4.8 远程读取信号强度、SIM卡卡号及模块状态 (16)五、故障分析 (17)一、产品简介1.1 产品概述山东力创科技有限公司开发的LQ8110E GPRS-DTU(本文简称DTU)为用户提供高速、永远在线、透明数据传输通道。

DTU是基于中国移动通讯运营商的GSM/GPRS通信网络的数据传输和远程监控终端设备,采用当今前沿内核技术设计的一款工业级无线通讯终端产品,适用于GSM/GPRS网络覆盖范围内的各种室内或野外恶劣环境,主要针对电力系统自动化、工业控制、交通管理、气象、环保监测、煤矿、金融、证券、油田等行业的应用,利用GPRS 网络平台实现数据信息的透明传输,并可通过辅助手段来实现对DTU控制,组成用户专用数据网络。

1.2 产品特点●采用高性能工业级通讯模块,结合远程数据(监控)传输的特点,在产品的稳定性、可靠性、安全性、以及供电系统等方面经过精心考虑设计而成,支持双频网络。

●用先进的嵌入式内核和电路设计,工作稳定性和通讯可靠性都有更强的保障。

tle8110 编程

tle8110 编程TLE8110编程简介TLE8110是一款高性能的汽车驱动器芯片,广泛应用于汽车电动助力转向系统和电动车辆的驱动系统中。

它具有可靠性高、效率高、集成度高等特点,在汽车电子领域发挥着重要作用。

TLE8110采用了先进的半桥驱动技术,能够有效地控制电机的转速和转向。

它具有多种保护功能,如过温保护、过流保护、短路保护等,能够确保电机和电子设备的安全运行。

同时,TLE8110还具有低功耗特性,能够提高电动车辆的续航里程。

在TLE8110的编程过程中,需要针对不同的应用场景进行参数配置和控制策略的制定。

编程过程主要包括以下几个步骤:1. 引脚配置:根据实际使用情况,将TLE8110的引脚与其他电路进行连接。

在连接过程中,需要注意引脚的功能和电压等级,确保连接正确且稳定。

2. 参数配置:根据具体的电机和驱动需求,对TLE8110的参数进行配置。

主要包括电流、速度、加速度等参数的设置。

这些参数的选择要根据实际需求进行调整,以达到最佳的驱动效果。

3. 控制策略制定:根据不同的应用场景,制定相应的控制策略。

例如,在电动助力转向系统中,可以制定转向角度与转向力之间的映射关系,以实现精确的转向控制。

在电动车辆的驱动系统中,可以制定加速度与电机输出功率之间的关系,以实现平稳的加速和减速。

4. 故障处理:在编程过程中,需要考虑各种可能出现的故障情况,并制定相应的处理策略。

例如,当电机温度过高时,可以通过降低电流来保护电机;当电流过大时,可以通过减小加速度来降低负载。

TLE8110的编程可以通过软件工具进行,例如使用C语言或其他编程语言编写相应的控制程序,再通过编译和下载的方式将程序加载到TLE8110中。

在编程过程中,需要注意对TLE8110的功能和特性的理解,以确保程序的正确性和稳定性。

TLE8110是一款功能强大的汽车驱动器芯片,在汽车电子领域具有重要的应用价值。

通过合理的参数配置和控制策略制定,可以实现高效、可靠的电机驱动控制。

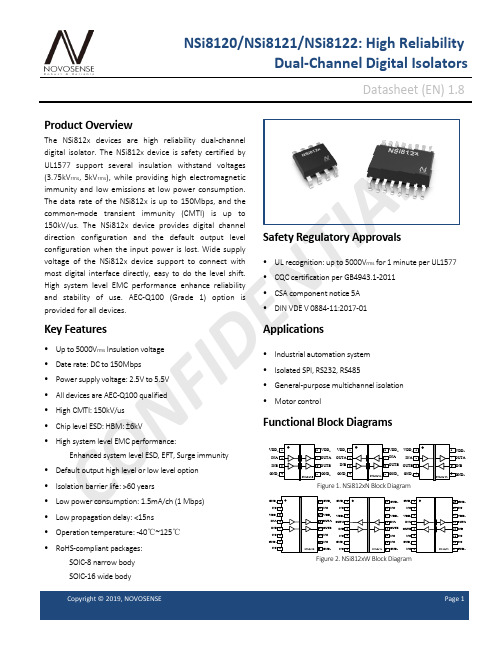

NSi812x高可靠双通道数字隔离器数据手册说明书

C O NF ID EN T IA LNSi8120/NSi8121/NSi8122: High ReliabilityDual-Channel Digital IsolatorsDatasheet (EN) 1.8Product OverviewThe NSi812x devices are high reliability dual-channel digital isolator. The NSi812x device is safety certified by UL1577 support several insulation withstand voltages (3.75kV rms , 5kV rms ), while providing high electromagnetic immunity and low emissions at low power consumption. The data rate of the NSi812x is up to 150Mbps, and the common-mode transient immunity (CMTI) is up to 150kV/us. The NSi812x device provides digital channel direction configuration and the default output level configuration when the input power is lost. Wide supply voltage of the NSi812x device support to connect with most digital interface directly, easy to do the level shift. High system level EMC performance enhance reliability and stability of use. AEC-Q100 (Grade 1) option is provided for all devices.Key Features• Up to 5000V rms Insulation voltage• Date rate: DC to 150Mbps• Power supply voltage: 2.5V to 5.5V • All devices are AEC-Q100 qualified • High CMTI: 150kV/us • Chip level ESD: HBM: ±6kV• High system level EMC performance:Enhanced system level ESD, EFT, Surge immunity• Default output high level or low level option • Isolation barrier life: >60 years• Low power consumption: 1.5mA/ch (1 Mbps) • Low propagation delay: <15ns • Operation temperature: -40℃~125℃ • RoHS-compliant packages:SOIC-8 narrow body SOIC-16 wide bodySafety Regulatory Approvals• UL recognition: up to 5000V rms for 1 minute per UL1577• CQC certification per GB4943.1-2011• CSA component notice 5A • DIN VDE V 0884-11:2017-01Applications• Industrial automation system • Isolated SPI, RS232, RS485• General-purpose multichannel isolation • Motor controlFunctional Block DiagramsC O NF ID EN T IA LIndex1.0 ABSOLUTE MAXIMUM RATINGS .............................................................................................................................. 3 2.0 SPECIFICATIONS ........................................................................................................................................................... 3 2.1. E LECTRICAL CHARACTERISTICS .................................................................................................................................................. 3 2.2. TYPICAL PERFORMANCE CHARACTERISTICS ........................................................................................................................... 7 2.3. P ARAMETER M EASUREMENT I NFORMATION . (8)3.0 HIGH VOLTAGE FEATURE DESCRIPTION (9)3.1. INSULATION AND SAFETY RELATED SPECIFICATIONS (9)3.2. DIN VDE V 0884-11(VDE V 0884-11):2017-01 INSULATION CHARATERISTICS ....................................................................... 9 3.3. R EGULATORY INFORMATION ................................................................................................................................................... 11 4.0 FUNCTION DESCRIPTION ..........................................................................................................................................11 5.0 APPLICATION NOTE ................................................................................................................................................... 12 5.1. PCB L AYOUT ...................................................................................................................................................................... 12 5.2. H IGH SPEED PERFORMANCE ................................................................................................................................................... 12 5.3. T YPICAL S UPPLY C URRENT E QUATIONS ..................................................................................................................................... 13 6.0 PACKAGE INFORMATION ......................................................................................................................................... 13 7.0 TAPE AND REEL INFORMATION ............................................................................................................................. 17 8.0 ORDER INFORMATION .............................................................................................................................................. 20 9.0 REVISION HISTORY . (21)C O NF ID EN T IA L1.0 ABSOLUTE MAXIMUM RATINGSPower Supply Voltage VDD1, VDD2 -0.5 6.5 V Maximum Input Voltage VINA, VINB -0.4 VDD+0.41 V Maximum Output Voltage V OUTA , V OUTB -0.4 VDD+0.41 VMaximum Input/Output Pulse VoltageVINA, VINB, V OUTA , V OUTB-0.8VDD+0.8VPulse width should be less than 100ns, and the duty cycle should be less than 10%Common-Mode Transients CMTI ±150 kV/us Output currentIo -15 15mAMaximum Surge Isolation VoltageV IOSM5.3kVOperating Temperature Topr -40125 ℃Storage Temperature Tstg -40150℃Electrostatic dischargeHBM±6000VCDM±2000V1 The maximum voltage must not exceed 6.5V.2.0 SPECIFICATIONS2.1. ELECTRICAL CHARACTERISTICS(VDD1=2.5V~5.5V, VDD2=2.5V~5.5V, Ta=-40℃ to 125℃. Unless otherwise noted, Typical values are at VDD1 = 5V, VDD2 = 5V, Ta =25℃)Power on ResetVDD POR2.2 V POR threshold as during power-upVDD HYS 0.1 V POR threshold Hysteresis Input ThresholdV IT1.6 V Input Threshold at rising edge V IT_HYS 0.4 V Input Threshold Hysteresis High Level Input Voltage V IH 2 V Low Level Input Voltage V IL 0.8 V High Level Output Voltage V OH VDD-0.3 V I OH ≤ 4mA Low Level Output VoltageV OL0.3VI OL ≤ 4mAC O NF ID EN T IA LOutput Impedance R out 50 ohm Input Pull high or low CurrentI pull 8 15 uA Start Up Time after POR trbs 40 usec Common Mode Transient ImmunityCMTI±100±150kV/us(VDD1=5V± 10%, VDD2=5V± 10%, Ta=-40℃ to 125℃. Unless otherwise noted, Typical values are at VDD1 = 5V, VDD2 = 5V, Ta = 25℃)Supply currentNSi8120 I DD1(Q0) 0.58 0.87 mAAll Input 0V for NSi8120x0 Or All Input at supply for NSi8120x1 I DD2(Q0) 1.18 1.77 mA I DD1(Q1) 2.92 4.38 mA All Input at supply for NSi8120x0 Or All Input 0V for NSi8120x1I DD2(Q1) 1.241.86mAI DD1(1M) 1.71 2.56 mA All Input with 1Mbps, C L =15pFI DD2(1M)1.382.07mAI DD1(10M) 1.78 2.67 mA All Input with 10Mbps, C L =15pF I DD2(10M)3.24.8mA I DD1(100M)2.103.15 mA All Input with 100Mbps, C L =15pFI DD2(100M)21.031.5mANSi8121/ NSi8122 I DD1(Q0) 1.031.55 mA All Input 0V for NSi812xx0 Or All Input at supply for NSi812xx1 I DD2(Q0) 1.00 1.5 mA I DD1(Q1)2.203.3 mA All Input at supply for NSi812xx0Or All Input 0V for NSi812xx1 I DD2(Q1)2.133.2 mA I DD1(1M) 1.72 2.58 mA All Input with 1Mbps, C L =15pFI DD2(1M) 1.68 2.52 mA I DD1(10M) 2.62 3.93 mA All Input with 10Mbps, C L =15pFI DD2(10M) 2.71 4.06 mA I DD1(100M) 11.01 16.5 mA All Input with 100Mbps, C L = 15pF I DD2(100M)12.8 19.2 mA Data RateDR 0 150 MbpsC O NF ID EN T IA LPropagation Delayt PLH 5 8.20 15 ns See Figure 2.7 , C L = 15pF t PHL 5 10.56 15 ns See Figure 2.7, C L = 15pF Pulse Width Distortion |t PHL – t PLH | PWD5.0nsSee Figure 2.7 , C L = 15pFRising Time t r 5.0 ns See Figure 2.7 , C L = 15pF Falling Timet f 5.0 ns See Figure 2.7 , C L = 15pFPeak Eye Diagram Jitter t JIT (PK) 350 ps Channel-to-Channel Delay Skewt SK (c2c) 2.5 nsPart-to-Part Delay Skewt SK (p2p)5.0ns(VDD1=3.3V± 10%, VDD2=3.3V± 10%, Ta=-40℃ to 125℃. Unless otherwise noted, Typical values are at VDD1 = 3.3V, VDD2 = 3.3V, Ta =25℃)Supply currentNSi8120 I DD1(Q0) 0.550.83mA All Input 0V for NSi8120x0 Or All Input at supply for NSi8120x1 I DD2(Q0) 1.12 1.68 mA I DD1(Q1) 2.87 4.3 mA All Input at supply for NSi8120x0 Or All Input 0V for NSi8120x1 I DD2(Q1)1.18 1.77mA I DD1(1M)1.72.55mA All Input with 1Mbps, C L = 15pFI DD2(1M)1.271.91 mA I DD1(10M) 1.732.6 mA All Input with 10Mbps, C L = 15pF I DD2(10M)2.413.6 mA I DD1(100M) 2.05 3.08 mA All Input with 100Mbps, C L = 15pF I DD2(100M)14.0521.08mANSi8121/ NSi8122 I DD1(Q0) 0.98 1.47 mA All Input 0V for NSi812xx0 Or All Input at supply for NSi812xx1 I DD2(Q0) 0.95 1.43 mA I DD1(Q1) 2.14 3.21 mA All Input at supply for NSi812xx0 Or All Input 0V for NSi812xx1 I DD2(Q1) 2.08 3.12 mA I DD1(1M) 1.63 2.45 mA All Input with 1Mbps, C L = 15pFI DD2(1M) 1.59 2.39 mA I (10M)2.223.33mAAll Input with 10Mbps,C O NF I D EN T IA LI DD2(10M) 2.25 3.38 mA C L = 15pFI DD1(100M) 7.57 11.36 mA All Input with 100Mbps, C L = 15pF I DD2(100M)8.5 12.75 mA Data RateDR 0 150 Mbps Minimum Pulse Width PW 5.0 nsPropagation Delayt PLH 5 9.20 15 ns See Figure 2.7 , C L = 15pF t PHL5 10.40 15 ns See Figure 2.7, C L = 15pF Pulse Width Distortion |t PHL – t PLH | PWD5.0nsSee Figure 2.7 , C L = 15pFRising Time t r 5.0 ns See Figure 2.7 , C L = 15pF Falling Timet f5.0 nsSee Figure 2.7 , C L = 15pFPeak Eye Diagram Jitter t JIT (PK) 350psChannel-to-Channel Delay Skewt SK (c2c)2.5nsPart-to-Part Delay Skew t SK (p2p)5.0ns(VDD1=2.5V± 10%, VDD2=2.5V± 10%, Ta=-40℃ to 125℃. Unless otherwise noted, Typical values are at VDD1 = 2.5V, VDD2 = 2.5V, Ta =25℃)Supply currentNSi8120I DD1(Q0) 0.53 0.8 mA All Input 0V for NSi8120x0 Or All Input at supply for NSi8120x1 I DD2(Q0) 1.11.65 mA I DD1(Q1)2.85 4.28 mA All Input at supply for NSi8120x0 Or All Input 0V for NSi8120x1 I DD2(Q1)1.15 1.73 mA I DD1(1M) 1.632.45 mA All Input with 1Mbps, C L = 15pFI DD2(1M) 1.21 1.82 mA I DD1(10M) 1.68 2.52 mA All Input with 10Mbps, C L = 15pFI DD2(10M) 2.05 3.08 mA I DD1(100M) 1.95 2.93 mA All Input with 100Mbps, C L = 15pFI DD2(100M)10.415.6mANSi8121/ NSi8122I DD1(Q0) 0.96 1.44 mA All Input 0V for NSi812xx0 Or All Input at supply for NSi812xx1I (Q0)0.931.395mAF ID EN T IA LI DD1(Q1) 2.11 3.165 mA All Input at supply for NSi812xx0Or All Input 0V for NSi812xx1 I DD2(Q1) 2.05 3.075 mA I DD1(1M) 1.58 2.37 mA All Input with 1Mbps, C L = 15pFI DD2(1M) 1.54 2.31 mA I DD1(10M) 2.02 3.03 mA All Input with 10Mbps, C L = 15pFI DD2(10M) 2.04 3.06 mA I DD1(100M) 6.03 9.045 mA All Input with 100Mbps, C L = 15pF I DD2(100M)6 9 mAData RateDR 0 150 Mbps Minimum Pulse Width PW 5.0 nsPropagation Delayt PLH 5 10 15 nsSee Figure 2.7 , C L = 15pF t PHL5 10 15nsSee Figure 2.7, C L = 15pFPulse Width Distortion |t PHL – t PLH | PWD5.0nsSee Figure 2.7 , C L = 15pFRising Time t r5.0ns See Figure 2.7 , C L = 15pF Falling Timet f5.0 ns See Figure 2.7 , C L = 15pFPeak Eye Diagram Jitter t JIT (PK)350ps Channel-to-Channel Delay Skewt SK (c2c)2.5ns Part-to-Part Delay Skew t SK (p2p)5.0ns2.2. TYPICAL PERFORMANCE CHARACTERISTICSFigure 2.1 NSi8120 VDD1 Supply Current vs Data Rate Figure 2.2 NSi8120 VDD2 Supply Current vs Data RateC OE2.3. PARAMETER MEASUREMENT INFORMATIONC LFigure 2.7 Switching Characteristics Test Circuit and WaveformFigure 2.8 Common-Mode Transient Immunity Test CircuitC O NF ID EN T IA L3.0 HIGH VOLTAGE FEATURE DESCRIPTION3.1. INSULATION AND SAFETY RELATED SPECIFICATIONSMinimum External Air Gap (Clearance)L(I01) 4.0 8.0 mm Shortest terminal-to-terminal distance through air Minimum External Tracking (Creepage)L(I02)4.08.0mmShortest terminal-to-terminal distance across the package surfaceMinimum internal gap DTI 20 um Distance through insulationTrackingResistance(Comparative Tracking Index) CTI>400VDIN EN 60112 (VDE 0303-11); IEC 60112Material GroupⅡ3.2. DIN VDE V 0884-11(VDE V 0884-11):2017-01 INSULATION CHARATERISTICSSOIC-8 SOIC-16 Installation Classification per DIN VDE 0110For Rated Mains Voltage ≤ 150V rms Ⅰto Ⅳ Ⅰto Ⅳ For Rated Mains Voltage ≤ 300V rms Ⅰto Ⅲ Ⅰto Ⅳ For Rated Mains Voltage ≤ 400V rms Ⅰto Ⅲ Ⅰto Ⅳ Climatic Classification10/105/2110/105/21 Pollution Degree per DIN VDE 0110, Table 122Maximum repetitive isolation voltageVIORM 565 849 Vpeak Input to Output Test Voltage, Method B1V IORM × 1.5 = V pd (m) , 100%production test, t ini = t m = 1 sec, partial discharge < 5 pCV pd (m)8471273VpeakInput to Output Test Voltage, Method AAfter Environmental Tests Subgroup 1V IORM × 1.2= V pd (m) , t ini = 60 sec, t m = 10 sec, partial V pd (m)6781018VpeakC O N T IA LAfter Input and /or Safety Test Subgroup 2 and Subgroup 3 V IORM × 1.2= V pd (m) , t ini = 60 sec, t m = 10 sec, partialdischarge < 5 pC V pd (m)6781018VpeakMaximum transient isolation voltage t = 60 sec VIOTM 5300 7000 Vpeak Maximum Surge Isolation VoltageTest method per IEC60065,1.2/50uswaveform, VTEST=VIOSM×1.3VIOSM53845384VpeakIsolation resistance VIO =500V RIO >109 >109 Ω Isolation capacitance f = 1MHzCIO 0.6 0.6pFInput capacitanceCI22pF Total Power Dissipation at 25℃Ps1499 mW Safety input, output, or supply currentθJA = 140 °C/W, V I = 5.5 V, T J = 150 °C, T A = 25 °C Is160mAθJA = 84 °C/W, V I = 5.5 V, T J = 150 °C, T A = 25 °C237 mA Case TemperatureTs150150℃Figure 3.2 NSi8120W/NSi8121W/NSi8122W Thermal Derating Curve, Dependence of Safety Limiting Values with Case Temperature per DIN VDE V 0884-11C O NF ID EN T IA L3.3. REGULATORY INFORMATIONThe NSi8120N/NSi8121N/NSi8122N are approved by the organizations listed in table.UL 1577 Component Recognition Program 1Approved under CSA ComponentAcceptance Notice 5ADIN VDE V 0884-11:2017-012Certified by CQC11-471543-2012 GB4943.1-2011Single Protection, 3750V rms Isolation voltageSingle Protection, 3750V rms IsolationvoltageBasic Insulation 565Vpeak, V IOSM =5384VpeakBasic insulation at 400V rms (565Vpeak)File (E500602)File (E500602)File (5024579-4880-0001)File (pending)1 In accordance with UL 1577, each NSi8120N/NSi8121N/NSi8122N is proof tested by applying an insulation test voltage ≥ 4500 Vrms for 1 sec.2 In accordance with DIN VDE V 0884-11, each NSi8120N/NSi8121N/NSi8122N is proof tested by applying an insulation test voltage ≥ 847 V peak for 1 sec(partial discharge detection limit = 5 pC). The * marking branded on the component designates DIN VDE V 0884-11 approval.The NSi8120W/NSi8121W/NSi8122W are approved by the organizations listed in table.UL 1577 Component Recognition Program 1Approved under CSAComponent Acceptance Notice5ADIN VDE V 0884-11(VDE V 0884-11):2017-012 Certified by CQC11-471543-2012 GB4943.1-2011Single Protection, 5000V rms Isolation voltageSingle Protection, 5000V rmsIsolation voltageBasic Insulation 849Vpeak, V IOSM =5384Vpeak Basic insulation at 800V rms (1131Vpeak) Reinforced insulation at 400V rms (565Vpeak)File (E500602)File (E500602)File (5024579-4880-0001)File (pending)1 In accordance with UL 1577, each NSi8120W/NSi8121W/NSi8122W is proof tested by applying an insulation test voltage ≥ 6000 V rms for 1 sec.2 In accordance with DIN VDE V 0884-11, each NSi8120W/NSi8121W/NSi8122W is proof tested by applying an insulation test voltage ≥ 1273 V peak for 1 sec(partial discharge detection limit = 5 pC). The * marking branded on the component designates DIN VDE V 0884-11 approval.4.0 FUNCTION DESCRIPTIONThe NSi812x is a Dual-channel digital isolator based on a capacitive isolation barrier technique. The digital signal is modulated with RF carrier generated by the internal oscillator at the Transmitter side. Then it is transferred through the capacitive isolation barrier and demodulated at the Receiver side.The NSi812x devices are high reliability dual-channel digital isolator with AEC-Q100 qualified. The NSi812x device is safety certified by UL1577 support several insulation withstand voltages (3.75kV rms , 5kV rms ), while providing high electromagnetic immunity and low emissions at low power consumption. The data rate of the NSi812x is up to 150Mbps, and the common-mode transient immunity (CMTI) is up to 150kV/us. The NSi812x device provides digital channel direction configuration and the default output level configuration when the input power is lost. Wide supply voltage of the NSi812x device support to connect with most digital interface directly, easy to do the level shift. High system level EMC performance enhance reliability and stability of use.The NSi812x has a default output status when VDDIN is unready and VDDOUT is ready as shown in Table 4.1, which helps for diagnosis when power is missing at the transmitter side. The output B follows the same status with the input A within 1us after powering up.C O NF ID EN T IA LCopyright © 2019, NOVOSENSEPage 12 Table 4.1 Output status vs. power statusH Ready Ready H Normal operation.L Ready Ready L XUnreadyReadyL HThe output follows the same status with the input within 60us after input side VDD1 is powered on.X Ready Unready XThe output follows the same status with the input within 60us after output side VDD2 is powered on.5.0 APPLICATION NOTE5.1. PCB LAYOUTThe NSi812x requires a 0.1 µF bypass capacitor between VDD1 and GND1, VDD2 and GND2. The capacitor should beplaced as close as possible to the package. Figure 5.1 to Figure 5.4 show the recommended PCB layout, make sure the space under the chip should keep free from planes, traces, pads and via. To enhance the robustness of a design, the user may also include resistors (50–300 Ω ) in series with the inputs and outputs if the system is excessively noisy. The series resistors also improve the system reliability such as latch-up immunity.The typical output impedance of an isolator driver channel is approximately 50 Ω, ±40%. When driving loads where transmission line effects will be a factor, output pins should be appropriately terminated with controlled impedance PCB traces.Figure5.1 Recommended PCB Layout — Top Layer Figure5.2 Recommended PCB Layout — Bottom LayerFigure5.3 Recommended PCB Layout — Top Layer Figure5.4 Recommended PCB Layout — Bottom Layer5.2. HIGH SPEED PERFORMANCEFigure 5.5 shows the eye diagram of NSi812x at 200Mbps data rate output. The result shows a typical measurement on the NSi812x with 350ps p-p jitter.C O NF ID EN T IA LFigure5.5 NSi812x Eye Diagram5.3. TYPICAL SUPPLY CURRENT EQUATIONSThe typical supply current of NSi812x can be calculated using below equations. I DD1 and I DD2 are typical supply currents measured in mA, f is data rate measured in Mbps, C L is the capacitive load measured in pFNSi8120:I DD1 = 0.19 *a1+1.45*b1+0.82*c1. I DD2 = 1.36+ VDD1*f* C L *c1*10-9When a1 is the channel number of low input at side 1, b1 is the channel number of high input at side 1, c1 is the channel number of switch signal input at side 1.NSi8121/ NSi8122:I DD1 = 0.87 +1.26*b1+0.63*c1+ VDD1*f* C L *c2*10-9I DD2 = 0.87 +1.26*b2+0.63*c2+ VDD1*f* C L *c1*10-9When b1 is the channel number of high input at side 1, c1 is the channel number of switch signal input at side 1, b2 is the channel number of high input at side 2, c2 is the channel number of switch signal input at side 2.6.0 PACKAGE INFORMATIONVDD GND 22VDD INA GND 2VDD 2Figure 6.1 NSi8120N Package Figure 6.2 NSi8121N PackageC O NF ID EN T IA LVDD INBGND 22Figure 6.3 NSi8122N PackageFigure 6.4 SOIC8 Package Shape and Dimension in millimeters (inches)Table6.1 NSi8120N/ NSi8121N/ NSi8122N Pin Configuration and DescriptionNSi8121N PIN NO.NSi8122N PIN NO.SYMBOL FUNCTION1 1 1 VDD1 Power Supply for Isolator Side 12 7 2 INA Logic Input A3 3 6 INB Logic Input B4 4 4 GND1 Ground 1, the ground reference for Isolator Side 15 5 5 GND2 Ground 2, the ground reference for Isolator Side 26 6 3 OUTB Logic Output B7 2 7 OUTA Logic Output A888VDD2Power Supply for Isolator Side 2C O NFVDD GND GND 2VDD 2GND 2GND NC NCNC VDD GND GND 2VDD 22GND NC NC NCFigure 6.5 NSi8120W Package Figure 6.6 NSi8121W PackageVDD INB GND GND 2VDD 2GND 2GND NC NC NCFigure 6.7 NSi8122W PackageFigure 6.8 WB SOIC16 Package Shape and Dimension in millimeters and (inches)C O NF ID EN T IA LTable 6.2 NSi8120W/ NSi8121W/ NSi8122W Pin Configuration and Description1 1 1 GND1 Ground 1, the ground reference for Isolator Side 12 2 2 NC No Connection.3 3 3 VDD1 Power Supply for Isolator Side 14 13 4 INA Logic Input A5 5 12 INB Logic Input B6 6 6 NC No Connection.7 7 7 GND1 Ground 1, the ground reference for Isolator Side 18 8 8 NC No Connection. 9 9 9 GND2 Ground 2, the ground reference for Isolator Side 210 10 10 NC No Connection. 11 11 11 NC No Connection. 12 12 5OUTB Logic Output A 13 4 13OUTALogic Output B 14 14 14 VDD2 Power Supply for Isolator Side 215 15 15 NC No Connection.161616GND2Ground 2, the ground reference for Isolator Side 27.0TAPE AND REEL INFORMATIONLAITNEDIFNOCC O NF ID EN T IA LFigure 7.1 Tape and Reel Information of SOIC8LAITNEDIFNOCFigure 7.2 Tape and Reel Information of WB SOIC16NF ID EN T IA L8.0 ORDER INFORMATIONNSi8120N0 3.75 2 0 150 Low -40 to 125℃ NO SOIC8 NSi8120N1 3.75 2 0 150 High -40 to 125℃ NO SOIC8 NSi8121N0 3.75 1 1 150 Low -40 to 125℃ NO SOIC8 NSi8121N1 3.75 1 1 150 High -40 to 125℃ NO SOIC8 NSi8122N0 3.75 1 1 150 Low -40 to 125℃ NO SOIC8 NSi8122N1 3.75 1 1 150 High -40 to 125℃ NO SOIC8 NSi8120W0 5 2 0 150 Low -40 to 125℃ NO WB SOIC16 NSi8120W1 5 2 0 150 High -40 to 125℃ NO WB SOIC16 NSi8121W0 5 1 1 150 Low -40 to 125℃ NO WB SOIC16 NSi8121W1 5 1 1 150 High -40 to 125℃ NO WB SOIC16 NSi8122W0 5 1 1 150 Low -40 to 125℃ NO WB SOIC16 NSi8122W1 5 1 1 150 High -40 to 125℃ NO WB SOIC16 NSi8120N0Q 3.75 2 0 150 Low -40 to 125℃ YES SOIC8 NSi8120N1Q 3.75 2 0 150 High -40 to 125℃ YES SOIC8 NSi8121N0Q 3.75 1 1 150 Low -40 to 125℃ YES SOIC8 NSi8121N1Q 3.75 1 1 150 High -40 to 125℃ YES SOIC8 NSi8122N0Q 3.75 1 1 150 Low -40 to 125℃ YES SOIC8 NSi8122N1Q 3.75 1 1 150 High -40 to 125℃ YES SOIC8 NSi8120W0Q 5 2 0 150 Low -40 to 125℃ YES WB SOIC16 NSi8120W1Q 5 2 0 150 High -40 to 125℃ YES WB SOIC16 NSi8121W0Q 5 1 1 150 Low -40 to 125℃ YES WB SOIC16 NSi8121W1Q 5 1 1 150 High -40 to 125℃ YES WB SOIC16 NSi8122W0Q 5 1 1 150 Low -40 to 125℃ YES WB SOIC16 NSi8122W1Q 5 1 1 150 High -40 to 125℃YES WB SOIC16 NOTE: All packages are RoHS-compliant with peak reflow temperatures of 260 °C according to the JEDEC industry standard classifications and peak solder temperatures. All devices are AEC-Q100 qualified.Part Number Rule:NSi(81)(2)(1)(N)(1)(Q)C O NF ID EN T IA LNSi8120/NSi8121/NSi81229.0 REVISION HISTORY1.0 Original2017/11/15 1.1 Change to Ordering information2018/3/26 1.2 Add maximum operation current specification. 2018/6/20 1.3 Change block diagram 2018/7/28 1.4 Correct Table 6.2 Pin No.2018/8/20 1.5 Add specification “Input Pull high or low Current” 2018/9/10 1.6 Add “Maximum Input/Output Pulse Voltage” 2018/10/91.7 Change to Ordering information 2018/12/20 1.8 Change Certification Information2019/06/17。

LIS8716_Datasheet V1.0

状态描述 初始版本

声明: 无锡莱士电子科技股份有限公司保留本 DATA SHEET 变更权。客户在下单前应获取最新版本资料,并验证 相关信息是否完整和最新。

版权© 莱士电子科技有限公司

莱士电子科技有限公司

余工:13760419224

可变电流-两绕组-初级侧控制 LED 驱动开关

极限工作范围

电源电压 (引脚 1)-----------------------------------------------------------------------------------------最大结温 (TJMAX)--------------------------------------------------------------------------------------工作环境温度(Ta)-------------------------------------------------------------------------------------存储温度范围(TSTO)--------------------------------------------------------------------------------引线温度(无铅封装,焊接,10 秒)---------------------------------------------------------------CS 引脚电压范围-----------------------------------------------------------------------------------------Drain 引脚电压范围---------------------------------------------------------------------------------------

网卡芯片rtl8110s(b-c)-8100c_111_0810

GND

1

R7

GND

*For RTL8110S(B-C) application, change L8 to 0 ohm.

GND

Q2

GND

Q3

Q4 CTRL25

2

If U4 is used, R6 and R7 can be set to 2.7K and 1.2K to have 1.8V output power at RTL8110S application, or set R6(Open) and R7(0) to have 1.25V output power at RTL8110SB application. If external regulator is preferred, replace U4 with AMS1117-1.5 component for RTL8110SC application.

3 2 2SB1188

SPX3940-2.5 OUT 3 ADJ 2

* C29 to C32 are for U7 RTL8110S(B/C)/RTL8100C AVDDL pins, such as 3, 7, 16, and 20.

3

If Q3 is used, remove R5 and keep R4 at RTL8110S & RTL8110SC application, or remove R4 and keep R5 at RTL8110SB application.

CTRL12/18/15 VDD33 3 + C38 10uF C40 .1uF U4

CTRL12/18/15

3 2 CTRL18/25 1 2SB1188

1

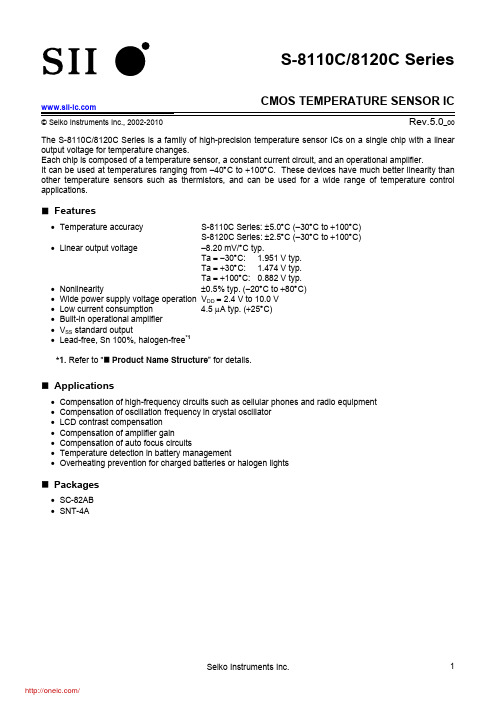

Q4

S-8110CPF-DRA-TF-G;S-8110CNB-DRA-TF-G;S-8120CPF-DRB-TF-G;中文规格书,Datasheet资料

S-8110C/8120C SeriesCMOS TEMPERATURE SENSOR IC © Seiko Instruments Inc., 2002-2010Rev.5.0_00 The S-8110C/8120C Series is a family of high-precision temperature sensor ICs on a single chip with a linear output voltage for temperature changes.Each chip is composed of a temperature sensor, a constant current circuit, and an operational amplifier.It can be used at temperatures ranging from −40°C to +100°C. These devices have much better linearity than other temperature sensors such as thermistors, and can be used for a wide range of temperature control applications.Features• Temperature accuracy S-8110C Series: ±5.0°C (–30°C to +100°C)S-8120C Series: ±2.5°C (–30°C to +100°C)• Linear output voltage –8.20 mV/°C typ.Ta =−30°C: 1.951 V typ.Ta =+30°C: 1.474 V typ.Ta =+100°C: 0.882 V typ.• Nonlinearity ±0.5% typ. (−20°C to +80°C)• Wide power supply voltage operation V DD= 2.4 V to 10.0 V• Low current consumption 4.5 μA typ. (+25°C)• Built-in operational amplifier• V SS standard output• Lead-free, Sn 100%, halogen-free*1*1. Refer to “ Product Name Structure” for details.Applications• Compensation of high-frequency circuits such as cellular phones and radio equipment• Compensation of oscillation frequency in crystal oscillator• LCD contrast compensation• Compensation of amplifier gain• Compensation of auto focus circuits• Temperature detection in battery management• Overheating prevention for charged batteries or halogen lightsPackages• SC-82AB• SNT-4ACMOS TEMPERATURE SENSOR ICS-8110C/8120C Series Rev.5.0_00 Block DiagramVDDVOUTVSSFigure 1CMOS TEMPERATURE SENSOR ICRev.5.0_00S-8110C/8120C SeriesProduct Name StructureThe product types and package types for S-8110C/8120C Series can be selected at the user’s request. Please refer to the “1. Product Name ” for the construction of the product name “2. Package ” regarding the package drawings and “3. Product Name List ” for the full product names.1. Product NameIC direction in tape specifications *1 Environmental codeU: Lead-free (Sn 100%), halogen-freeG: Lead-free (for details, please contact our sales office)Product code *2DRA: S-8110C Series DRB: S-8120C Series Package code NB: SC-82AB PF: SNT-4AProduct type 1: Temperature accuracy ±5.0°C 2: Temperature accuracy ±2.5°C*1. Refer to the tape specifications at the end of this book.*2. Refer to the Table 1 in the “3. Product Name List ”.2. PackageDrawing codePackage namePackage Tape Reel LandSC-82AB NP004-A-P-SD NP004-A-C-SDNP004-A-C-S1NP004-A-R-SD ⎯SNT-4A PF004-A-P-SD PF004-A-C-SD PF004-A-R-SD PF004-A-L-SD3. Product Name ListTable 1Series name SC-82AB SNT-4AS-8110C Series S-8110CNB-DRA-TF-x S-8110CPF-DRA-TF-x S-8120C Series S-8120CNB-DRB-TF-x S-8120CPF-DRB-TF-x Remark 1. x: G or U 2. Please select products of environmental code = U for Sn 100%, halogen-free products.CMOS TEMPERATURE SENSOR IC S-8110C/8120C SeriesRev.5.0_00Pin ConfigurationsTable 2Pin No. Pin name Pin description 1 VDD Power supply pin2 VSS GND pin3 NC *1No connection 4 VOUT Output voltage pin*1. The NC pin is electrically open. The NC pin can be connected to VDD or VSS.4 3 1 2 SC-82ABTop viewFigure 2Table 3Pin No. Pin name Pin description 1 VSS GNDpin 2 VDD Power supply pin3 VOUT Output voltage pin4 NC *1No connection*1. The NC pin is electrically open.The NC pin can be connected to VDD or VSS.SNT-4ATop view4Figure 3CMOS TEMPERATURE SENSOR ICRev.5.0_00S-8110C/8120C SeriesAbsolute Maximum RatingsTable 4(Ta = +25°C unless otherwise specified)ItemSymbol Absolute maximum ratings UnitPower supply pin voltage V DD V SS −0.3 to V SS +12.0V Output voltageV OUTV SS −0.3 to V DD +0.3V 150 (When not mounted on board) mWSC-82AB350*1mW140 (When not mounted on board) mWPower dissipationSNT-4AP D 300*1mW Operating ambient temperature T opr −40 to +100 °C Storage temperature T stg −40 to +125 °C*1. When mounted on board [Mounted board] (1) Board size : 114.3 mm × 76.2 mm × t1.6 mm (2) Board name : JEDEC STANDARD51-7Caution The absolute maximum ratings are rated values exceeding which the product could sufferphysical damage. These values must therefore not be exceeded under any conditions.CMOS TEMPERATURE SENSOR IC S-8110C/8120C SeriesRev.5.0_00Electrical Characteristics1. S-8110C SeriesTable 5(Ta = +25°C, V DD = 5.0 V, I OUT = 0 A unless otherwise specified)Item Symbol Condition Min. Typ. Max. UnitTestcircuitPower supply voltage V DD ⎯ 2.4 ⎯10.0 V 1 Ta = −30°C1.911 1.951 1.991 V 1 Ta = +30°C1.434 1.474 1.514 V 1 Output voltage V OUT Ta = +100 °C0.8420.8820.922 V 1 Temperature sensitivity V SE −30°C ≤ Ta ≤ +100°C −8.40−8.20−8.00 mV/°C ⎯Nonlinearity ΔN L−20°C ≤ Ta ≤ +80°C ⎯ ±0.5 ⎯ % ⎯ Operating temperaturerangeT opr ⎯ −40 ⎯ 100 °C ⎯Current consumption I DD ⎯ ⎯4.5 8.0 μA 1 Line regulation ΔV OUT1 V DD = 2.4 V to 10.0 V⎯ ⎯ 0.05 %/ V 2 Load regulation *1ΔV OUT2 I OUT = 0 μA to 200 μA⎯ ⎯ 1.0 mV 2 *1. Do not flow sink current into the output voltage pin.2. S-8120C SeriesTable 6(Ta = +25°C, V DD = 5.0 V, I OUT = 0 A unless otherwise specified)Item Symbol Condition Min. Typ. Max. UnitTestCircuitPower supply voltage V DD ⎯ 2.4 ⎯10.0 V 1 Ta = −30°C1.931 1.951 1.971 V 1 Ta = +30°C1.454 1.474 1.494 V 1 Output voltage V OUT Ta = +100°C0.8620.8820.902 V 1 Temperature sensitivity V SE −30°C ≤ Ta ≤ +100°C −8.40−8.20−8.00 mV/°C ⎯Nonlinearity ΔN L−20°C ≤ Ta ≤ +80°C ⎯ ±0.5 ⎯ % ⎯ Operating temperature range T opr ⎯−40 ⎯ 100 °C ⎯Current consumption I DD ⎯ ⎯4.5 8.0 μA 1 Line regulation ΔV OUT1 V DD = 2.4 V to 10.0 V⎯ ⎯ 0.05 %/ V 2 Load regulation *1ΔV OUT2 I OUT = 0 μA to 200 μA ⎯ ⎯1.0 mV 2 *1. Do not flow sink current into the output voltage pin.CMOS TEMPERATURE SENSOR IC Rev.5.0_00S-8110C/8120C SeriesTest Circuits1.Figure 42.I OUTFigure 5CMOS TEMPERATURE SENSOR ICS-8110C/8120C Series Rev.5.0_00Technical Terms1. Output Voltage (V OUT)V OUT indicates the output voltage at Ta =−30°C, Ta =+30°C and Ta =+100°C.0°C +100°C+30°C−30°CAmbient temperature [Ta]Figure 6CMOS TEMPERATURE SENSOR ICRev.5.0_00S-8110C/8120C Series2. Temperature Sensitivity (V SE )V SE indicates the temperature coefficient of the output voltage calculated using the output voltage at Ta = −30°C and Ta = +100°C.V SE is calculated using the following formula.[]3**2*1130V V V OUT OUTSE−=0°C +100°C+30°C Ambient temperature [Ta]−30°CFigure 7*1. V OUT value at Ta = +100°C. [V] *2. V OUT value at Ta = −30°C. [V]*3. The difference of the temperature from Ta = +100°C to Ta = −30°C. [°C]CMOS TEMPERATURE SENSOR IC S-8110C/8120C SeriesRev.5.0_003. Nonlinearity (ΔN L )ΔN L indicates the nonlinearity of the output voltage and is defined as the difference of the characteristic curve of the output voltage and the approximated straight line shown below. ΔN L is calculated using the following formula.100ba ΔN L ×=2**1Ambient temperature [Ta]Figure 8*1. The maximum deviation of the actual measurement of output voltage (B) and an approximated straightline (A) in temperature within −20°C to +80°C. (An approximated straight line is taken as the straight line from which the “a” becomes the minimum.)*2. The difference of the output voltage within −20°C to +80°C.4. Line Regulation (ΔV OUT1)ΔV OUT1 indicates the output voltage dependence on the input voltage. That is, the values express how the output voltage changes, when input voltage is changed under the condition that output current is fixed.5. Load regulation (ΔV OUT2)ΔV OUT2 indicates the output voltage dependence on the output current. That is, the values express how the output voltage changes, when output current is changed under the condition that input voltage is fixed.分销商库存信息:SEIKOS-8110CPF-DRA-TF-G S-8110CNB-DRA-TF-G S-8120CPF-DRB-TF-G S-8120CNB-DRB-TF-G。

IC datasheet pdf-TPIC8101,pdf(Knock Sensor Interface)

KNOCKKNOCKKNOCKInput SignalInt/Hold SignalOutput SignalFigure 3. Amplified Input Signal ProcessInput SignalInt/Hold SignalOutput SignalFigure 4. Input Signal ProcessingKNOCKPACKAGE OPTION ADDENDUM 16-Jul-2010Addendum-Page 1PACKAGING INFORMATION Orderable DeviceStatus (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)Samples (Requires Login)TPIC8101DWACTIVE SOIC DW 2025Green (RoHS & no Sb/Br)CU NIPDAU Level-3-260C-168 HR/Level-1-235C-UNLIM Contact TI Distributor or Sales Office TPIC8101DWG4ACTIVE SOIC DW 20TBD Call TI Call TI Purchase Samples TPIC8101DWRACTIVE SOIC DW 202000Green (RoHS & no Sb/Br)CU NIPDAU Level-3-260C-168 HR/Level-1-235C-UNLIM Request Free Samples TPIC8101DWRG4ACTIVE SOIC DW 20TBD Call TI Call TI Purchase Samples (1) The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDLP®Products Communications and /communicationsTelecomDSP Computers and /computersPeripheralsClocks and Timers /clocks Consumer Electronics /consumer-appsInterface Energy /energyLogic Industrial /industrialPower Mgmt Medical /medicalMicrocontrollers Security /securityRFID Space,Avionics&/space-avionics-defenseDefenseRF/IF and ZigBee®Solutions /lprf Video and Imaging /videoWireless /wireless-appsMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2010,Texas Instruments Incorporated。

Agilent 81110A 数字信号源数据手册说明书

Agilent 81110A Agilent 81100 Family ofPulse Pattern GeneratorsData Sheet – Version 1.3Flexible Pulses or Patterns for DigitalDesigns – Key Features• Pattern mode on all models from 80 MHz to 660 MHz,including pseudo-random binary sequence• The outputs of dual-channel instruments can be added(analog or EXOR, depending on model)• User-retrofittable channels for most models• Upward compatibility• Individual solutions for frequencies up to 50, 80, 165, 330, 400 and 660 MHz• 100% form/fit compatibilitySignals for testing digital designs and componentsThe Agilent 81101A, 81104A, 81110A and 81130A generate all the standard pulses and digital patterns needed to test current logic technologies (CMOS, TTL, LVDS, ECL, etc.).With the optional second channel on all of the models from 80 MHz to 660 MHz, multi-level and multi-timing signals can be obtained using the internal channel addition feature.• Variable pulse parameters in pattern mode as well as in pulse mode (not on the 81130A)• Synchronously triggerable• Simulation of reflections/distortions• (81104A, 81110A)• Three/four-level codes (81104A, 81110A)Glitch-free timing changesTiming values can now be swept without the danger of misleading pulses ordropouts that could cause measurement errors. (Applies to continuous mode, values < 100 ms, consecutive values between 0.5 and twice the previous value on the 81101A, 81104A, 81110A).Reliable measurementsAll models provide clean, accurate pulses with excellent repeatability, thus contribut-ing to measurement integrity.The Agilent 81110A features self-calibration for more accuracy. It also offers a choice of output modules. The Agilent 81111A 165 MHz 10 V module with variable transitions.Along with the Agilent 81112A 330 MHz 3.8 V module, which has differential out-puts and two selectable transition times.The Agilent 81130A offers a choice of output modules: the Agilent 81131A 400 MHz, 3.8 V module and the Agilent 81132A 660 MHz, 2.5 V module which has complementary outputs.Easy-to-useFeatures such as the clear graphicaldisplay, autoset, help, store/recall, preset TTL/ECL levels, selectable units (such as current/voltage, width/duty-cycle), and load compensation ensure a high level of convenience.Stimulate the device’s environmentToday’s devices can require very complex stimuli. To meet this, the Agilent 81130A can sequence and loop its memory for very deep patterns. RZ (return-to-zero), NRZ (non-return-to- zero) and R1 (return-to-one) formats are available. Digital channel addition allows the generation of signals with two different pulse widths and delays or of data rates up to 1.32 Gbit/s in one single channel.Frequency rangeThe Agilent 81130A is designed and recommended for an operation in the frequency range of 170 kHz to 400/660 MHz. However it can be operated in the extended range down to 1 kHz.Data Sheet 81100 Family of Pulse Pattern Generators21. Depends on selected impedance (all other values for 50 Ω source impedance into 50 Ω load).2. 0.001% +15 ps with internal PLL as clock source.3. Also avalable as VXI pulse pattern generators E8311A and E8312A.Agilent 81100 - Family of Pulse Pattern Generators81101A SpecificationsBurst Count : 2 to 65536 (single or double pulses).Delay : Delay, phase or % of period.Double pulse delay : Double pulse and delay are mutually exclusive.Duty cycle : Set between 0.1% and 95% (subject to width limits. 99.9% with overprogramming).Transition times: These can be entered as leading/trailing edge or % of width. Leading and trailing edges are indepen-dent within one of the following over-lapping segments (1:20 ratio):• 5 ns - 20 ns • 10 ns - 200 ns • 100 ns - 2 µs • 1µs - 20 µs • 10 µs - 200 µs • 100 µs - 2 ms • 1 ms - 20 ms •10 ms - 200 msData Sheet 81100 Family of Pulse Pattern Generators3Repeatability : Is typically four times better than accuracyOutput timing fidelity : Period, delay and width are continuously variable without any output glitches or dropouts.Data Sheet 81100 Family of Pulse Pattern GeneratorsTrigger modesContinuous : Continuous pulses, double pulses or bursts (single or double pulses).External triggered : Each active inputtransition (rising, falling or both) generates a single or double pulse or burst.External gated : The active input level (high or low) enables pulses, double pulses or bursts. The last single/double pulse or burst is always completed.External width : The pulse shape can be recovered whilst the period and width of an external input signal are maintained. Levels and transitions can be set.Manual : Simulates an external input signal.Internal triggered : Internal PLL replaces an external trigger source.Inputs and outputsClock input/PLL reference and external input: One input (BNC connector at rear panel) is used for clock input or alterna-tively for the PLL.PLL reference : The internal PLL is locked to an external 5 MHz or 10 MHz reference frequency.Clock input : The output period isdetermined by the signal at CLK input. Ext. input : Used for trigger, gate or external width.Level parameters: Can be entered as volt-age or current, as high and low level, or as offset and amplitude.Load compensation:The actual load value can be entered (for loads ≠ 50 Ω) to display actual output values. On/off: Relays connect/disconnect output (HiZ).Normal/complement: Selectable.Limit : Programmable high and low levels can be limited to protect the device-under-test.Input impedance : 50 Ω/10 kΩ selectable.Threshold : -10 V to +10 V.Max. input voltage : ±15 Vpp.Sensitivity : 300 mVpp typical.Input transitions : < 100 ns.Frequency : Dc to 50 MHz.Minimum pulse width : 10 nsStrobe output and trigger output trigger format : One pulse per period with 50% duty cycle typical.External mode : 9 ns typ.Level : TTL or ECL selectable.Output impedance : 50 Ω typical.Max. external voltage : -2 V/+7 V.Transition times : 1.0 ns typical for TTL, 600 ps typical for ECL.41. In ±19 V level window81104A and 81110A SpecificationsBurst count: 2 to 65536 (single or double pulses).Delay : Delay, phase or % of period.Double pulse and delay : Mutually exclusive.Duty cycle : Set between 0.1% and 95% (subject to width limits. 99.9% with over-programming).Repeatability : Is typ. four times better than accuracy.Transition times : leading/ trailing edge or % of width. Leading and trailing edges are independent Agilent 81111A/Agilent 81105A) within one of the following overlapping segments (1:20 ratio): • 2 ns (3 ns) - 20 ns • 10 ns - 200 ns • 100 ns - 2 ms • 1µs - 20 µs • 10 µs - 200 µs • 100 µs - 2 ms • 1 ms - 20 ms •10 ms - 200 msOutput timing fidelity : Period, delay and width are continuously variable without any output glitches or dropouts.Overprogramming : All parameters of the Agilent 81110A, except transitions, can be set to whatever the 330 MHz timing system will allow. This applies also when the Agilent 81111A (165 MHz) output module is used.Data Sheet 81100 Family of Pulse Pattern Generators51. Source impedance is selectable from 50 Ω to 1 KΩ for the Agilent 81111A.2. Changing of amplitude may add 0.5 ns.Level/Pulse Performance CharacteristicsLevel parameters: voltage or current, high or low level, offset or amplitude.On/off: relays connect/ disconnect output (HiZ).Load compensation: the actual load value can be entered (forloads ≠ 50 Ω) to display actual output values. (Applies to theAgilent 81105A and Agilent 81111A only).Normal/complement: selectable.Limit: programmable high and low levels can be limited to protect the device-under-test.Channel Addition (with Agilent 81105A or Agilent 81111A output channels)If the instrument is equipped with 2 output modules, channel 2 can be added to channel 1 internally. In this case the second output is disabled. The additional fixed delay on the second channel is typ. 2.5 ns. The following parameters differ from the above specifications if two output modules (Agilent 81105A/Agilent 81111A) are added.Data Sheet 81100 Family of Pulse Pattern Generators61. In ± 19 V level window.Pattern modePattern length: 16 kbit/channel and strobe output.Output format: RZ (return to zero), NRZ (non-return to zero), DNRZ (delayednon-return to zero).Random pattern:PRBS 2 ^ (n - 1) n = 7,8, (14)Trigger modesContinuous: Continuous pulses, double pulses, bursts (single or double pulses)or patterns.External triggered: Each active input transition (rising, falling or both) generates a single or double pulse,burst or pattern.External gated: The active input level (high or low) enables pulses, double pulses, bursts or patterns. The last single/double pulse, burst or patternis always completed.External width: The pulse shape can be recovered. Period and width of an external input signal is maintained. Delay, levels and transitions can be set.Manual: Simulates an external input signal.Internal triggered: Internal PLL replaces an external trigger source. Pulses, double pulses, bursts or patterns can be set.Strobe output and trigger outputStrobe output: User-defined, 16 kbitpattern (NRZ) when in pattern mode.Trigger format: One pulse per period with50% duty cycle typical. External mode:1.5 ns typ. for Agilent 81110A. 5.9 ns typ.for Agilent 81104A.Level: TTL or ECL selectable.Output impedance: 50 Ω typical.Max. external voltage: - 2 V/+7 V.Transition times: 1.0 ns typical for TTL,600 ps typical for ECL.Inputs and OutputsClock input/PLL reference andexternal inputPLL reference: (BNC connector at rearpanel). The internal PLL is locked to anexternal 5 MHz or 10 MHz referencefrequency.Clock input: (BNC connector at rearpanel). The output period is determinedby the signal at CLK input.Ext. input: Used for trigger, gate orexternal width.Input impedance: 50 Ω/10 kΩ selectable.Threshold: - 10 V to + 10 V.Max. input voltage: ± 15 Vpp.Sensitivity: ≤ 300 mVpp typical.Transitions: < 100 ns.Frequency: dc to max. frequencyof output module.Min. pulse width: 1.5 ns (as width ofoutput module in external width mode).711. Subtract 4 ns from the typ. delay value when referring to OUTPUT 1 / 2 for the Agilent 81112A output module and add 1 ns when referring toOUTPUT 1 / 2 for the Agilent 81104A with the Agilent 81105A output module.Data Sheet 81100 Family of Pulse Pattern GeneratorsData Sheet 81100 Family of Pulse Pattern Generators8Burst count : 2 to 65504.Delay : Delay, phase or % of period.Duty cycle : Set between 0.1% and 99,9% (subject to width limits).Repeatability : Is typ. four times better than accuracy.1. The uncertainty of 1 period can be eliminated if an external clock and the following setup and hold times are upheld. setup time: 0.3 ns to 4.3 ns; hold time: -2.8 ns to 4.0 ns.Data Sheet 81100 Family of Pulse Pattern GeneratorsSequencing : A sequence is a succession of segments. One outer loop running once or continuous, and one nested loop can be applied. The nested loop can be set from 1 to 2 ^ 20 repetitions.Segment : The memory can be divided into maximal 4 segments.Segment length resolution : This is the resolution for which the segment can be set dependent on the maximum data rate. See Table 1.Limit : Programmable high and low levels can be limited to protect the device-under-test.Segment types: Pattern, PRBS, high and low segments ( “0” or “1” levels segments selectable).Note : If one channel is set to PRBS the other channel can only be high or low segments, or PRBS type.Random pattern : PRBS 2 ^ n - 1,n = 7,8,...,15 (CCITT 0.151).Level parameters : Voltage or current, high and low level, or offset and amplitude.Pattern and sequencingPattern length: 65504 bit/channel. If PRBS is used: (65503-RBLength).Pattern formats : NRZ (non-return-to-zero), DNRZ (delayed non-return-to-zero), RZ (return-to-zero) and R1 (return-to-one) can be selected (see Figure 1).On/off : Relays connect/disconnect output (HiZ).9Segment length resolution trade-offs1. The minimum length in the first segment of a nestedloop is two times that of the segment length resolution.Width is a multiple of clock periods.Width and delay can be set as required.Width and delay can be set as required.The signal can be delayed as required.Output pattern formats Non-return-to-zeroR1RZ DNRZNRZReturn-to-oneReturn-to-zero Delayed non-return-to-zeroData Sheet 81100 Family of Pulse Pattern GeneratorsTrigger modesContinuous : Continuous pulses, bursts or patterns.External started : Each active input transi-tion (rising, falling edge) generates pulses, bursts or patterns.External gated : The active input level (high or low) enables pulses, bursts or patterns. On an external gate signal the output is immediately stopped, that means the last cycle will not be completed.Manual : Simulates an external input signal with push of a front panel button.Inputs and outputsClock input/PLL reference and external inputConnectors : SMA (f) 3.5 mm Input impedance : 50 ΩTermination voltage : -2.10 V to 3.30 V Input sensitivity : < 400 mV typ.Max. input voltage : -3 V to + 6 V Input transitions : < 20 nsOnly valid for clock input/PLL reference One input is used for clock input or for the PLL reference alternatively.Reference : The internal PLL is locked to the 1,2,5 or 10 MHz. The output frequency of the instrument must be larger than the clock input/PLL reference frequency.External clock : The output period is determined by the signal at clock input. Clock input frequency : 170 kHz to 660 MHz (at 50% ±10% duty cycle).Delay from input trigger output : 21 ns.Delay from input to output : 53 ns.Threshold : ac coupled. Only valid for external input.External input : Used for external started or gated.Input frequency : DC to 330MHz.Delay from external input to trigger output : 22ns + 0 to 1 period.Delay from external input to output : 54 ns + 0 to 1 period.Threshold : -1.4 V to +3.7 V.Trigger outputTrigger format : One pulse per period with 50% duty cycle typical. In pattern mode the trigger pulse can be set to mark the start of any segment.Output impedance : 50 Ω typical.Level : TTL/ETTL (for frequency < 180 MHz), 1 V to GND, ECL 50 Ω to GND/-2 V, PECL 50 Ω to + 3 V.Max. external voltage : -2 V/+3 V.Transition times : 1.0 ns typical for TTL, 600 ps typical for ECL.Delay from external input to trigger output : 32 ns typical.Channel 1 +Figure 2: Channel addition10Programming times: (measured at display off)1. Range depends on segment length resolution, see previous table.Data Sheet 81100 Family of Pulse Pattern Generators11Ordering Information - 81100 FamilyThe minimum configuration for a working instrument consists of a mainframe and one output module. The second output module can be added later. Output modules can be exchanged and retrofitted by the user. The Reference Guide (811xx-91021) is supplied with each mainframe for all configurations. A memory card is not included.Each Agilent 81101A mainframe includes one output channel (in comparison to the other models of the Agilent 81100 family). The output module of the 81101A does not need to be ordered separately.Agilent 81101A50 MHz one channel pulse generator, 10 V Quick start guide language options Opt OBI Engish Guide(811xx-91021)Opt ABF French Guide(81101-91210)Opt ABJ Japanese Guide(81101-91510)Opt AB0Taiwan Chinese Guide(81101-91610)Opt AB1Korean Guide(81101-91710)Opt AB2Chinese Guide(81101-91810)Additional documentation optionsOpt 0BW Service Manual(81101-91021)Agilent 81104A80 MHz pulse/pattern generatormainframeOutput module:Agilent 81105A 80 MHz, 10 VAgilent 81110A330/165 MHz pulse/pattern generatormainframeOutput modules:Agilent 81111A 165 MHz, 10 VAgilent 81112A 330 MHz, 3.8 VNote: Only use output modules of thesame module number. A combination ofthe Agilent 81111A and Agilent 81112A inone Agilent 81110A is not possible.Quick start guide language optionsOpt OBI Engish Guide(811xx-91021)Opt ABF French Guide(81110-91210)Opt ABJ Japanese Guide(81110-91510)Opt AB0 Taiwan Chinese Guide(81110-91610)Opt AB1Korean Guide(81110-91710)Opt AB2 Chinese Guide(81110-91810)Additional documentation optionsOpt 0BW Service Manual(81110-91021)Agilent 81130A400/660 MHz pulse/data generatormainframeOutput modules:Agilent 81131A 400 MHz, 3.8 VAgilent 81132A 660 MHz, 2.4 VNote: Only use output modules of thesame module number. A combination ofthe Agilent 81131A and Agilent 81132A inone Agilent 81130A is not possible.Quick start guide language optionsOpt OBI Engish Guide(811xx-91021)Opt ABF French Guide(81130-91220)Opt ABJ Japanese Guide(81130-91520)Opt AB0Taiwan Chinese Guide(81130-91620)Opt AB1Korean Guide(81130-91720)Opt AB2Chinese Guide(81130-91820)Additional documentation optionsOpt 0BW Service Manual(81130-91021)Opt 0B1English Quick StartGuide (includes EnglishRef eremceGuide)Opt ABJ Japanese Quick StartGuide (includes EnglishRef erecnceGuide)Opt 0B0 Does not include anyQuick Start Guide(includes EnglishReferenceGuide)All options are orderable with themainframes.AccessoriesOpt UN2Rear panel connectors (insteadof front panel)Opt 1CP Rack mount and handle kit(5063-9219)Opt 1CN Handle kit (5063-9226)Opt 1CM Rack mount kit (5063-9212)Opt 1CR Rack slide kit (1494-0059)Opt UFJ 1 MB SRAM memory card(0950-3380)Opt UK6Commercial cal. certificate withtestdataData Sheet 81100 Family of Pulse Pattern Generators 12Product specifications and descriptions in this document subject to change without notice.© Agilent Technologies, Inc. 2009Printed in USA, November 24, 20095980-1215E。

HLW8110 HLW8112智能计量IC用户手册说明书

REV 1.191 / 68HLW8110/HLW8112用户手册REV 1.19REV 1.192 / 68智能计量IC1应用领域 ⏹ 智能家电设备 ⏹ 漏电检测设备 ⏹ 计量电表⏹ 计量插座 ⏹ WIFI 插座 ⏹ 充电桩 ⏹ PDU 设备 ⏹ LED 照明 ⏹ 交通路灯REV 1.193 / 682修订历史时间 修改记录版本 2018-03-16 初始版本 REV 1.00 2018-04-10 增加图表附录 REV 1.01 2018-05-25 增加协议资料 REV 1.02 2018-09-26 修改PIN 脚说明 REV 1.05 2018-09-28 重新排版 REV 1.06 2018-12-25 增加相角计算公式 REV 1.07 2019-02-13 修改字体REV 1.08 2019-02-18 更正输入通道信号输入范围值 REV 1.09 2019-02-20 增加B 通道比较器描述 REV 1.10 2019-05-21 电气特性参数修改REV 1.12 2019-10-03 增加UART 复位条件,删除uart 4800bps 设置选项 REV 1.16 2020-03-02 修改漏电检测电路 REV 1.17 2020-08-28 修订版本REV 1.18 2020-11-20 修改原理图,1K 和33NF 变更为100R 和330NF REV 1.19REV 1.194 / 68目录1 应用领域 .........................................................................................................................................2 2 修订历史 .........................................................................................................................................3 3 特性 ................................................................................................................................................. 74 概述 ................................................................................................................................................. 85 功能框图 ......................................................................................................................................... 8 6引脚配置和功能描述 (9)6.1 HLW8110芯片管脚描述 ............................................................................................................ 9 6.2 HLW8110典型应用 .................................................................................................................. 10 6.3 HLW8112芯片管脚描述 .......................................................................................................... 10 6.4HLW8112典型应用 (12)7电气特性 (12)7.1 推荐工作条件 ......................................................................................................................... 12 7.2 模拟特性 ................................................................................................................................. 13 7.3 数字特性 ................................................................................................................................. 14 7.4 极限额定值 ............................................................................................................................. 15 7.5可靠性 (15)8功能概述 (16)8.1 复位系统 ................................................................................................................................. 16 8.2 时钟系统 ................................................................................................................................. 17 8.3 模数转换 ................................................................................................................................. 17 8.4 通道切换 ................................................................................................................................. 18 8.5 有功功率 ................................................................................................................................. 18 8.6 有效值 ..................................................................................................................................... 19 8.7 视在功率和功率因素 ............................................................................................................. 20 8.8 能量计算 ................................................................................................................................. 20 8.9 过零检测、相角、电压频率测量 ......................................................................................... 21 8.10 峰值检测 ................................................................................................................................. 23 8.11 过流、过压、有功功率过载检测 ......................................................................................... 25 8.12 电压聚降检测 ......................................................................................................................... 27 8.13 均值信号 ................................................................................................................................. 29 8.14 瞬时信号和采样波形 ............................................................................................................. 30 8.15 温度传感器 ............................................................................................................................. 30 8.16比较器 (31)9寄存器说明 (32)REV 1.195 / 689.1.1 系统控制寄存器 ............................................................................................................. 34 9.1.2 计量控制寄存器 ............................................................................................................. 35 9.1.3 计量控制寄存器2 .......................................................................................................... 36 9.1.4 脉冲频率寄存器 ............................................................................................................. 37 9.1.5 无负载有功功率(潜动与启动)阈值寄存器PstartPA 、PstartPB ......................... 38 9.1.6 有功功率和视在功率增益校正寄存器 ......................................................................... 38 9.1.7 相位校正寄存器 .............................................................................. 错误!未定义书签。

塑封GED1121IS8系列规格书(原位替换LT1121系列)

GED1121IS8系列——低压差线性稳压器1.产品特性◆输出电流:150mA◆压差电压:0.4V◆静态电流:30μA◆无需保护二极管◆固定输出电压:3.3V,5V◆可调输出电压:3.95V~20V◆电池反接保护◆关断电流:16μA◆关断功能◆过热保护◆0.33uF的输出稳定电容◆封装:SOP8◆工作温度范围:-40℃~125℃◆质量等级:工业级(I)2.产品应用◆低电流稳压器◆电池供电系统的稳压器3.产品概述GED1121IS8系列产品是一款带关断、微功耗低压差稳压器。

此器件在0.4V的压差下能够提供150mA的电流。

最小静态电流为30μA,关断时降至16μA,这种特性使GED1121IS8系列产品产品在电池供电系统中成为理想选择。

产品静态电流能够被很好的控制,静态电流不会像其他PNP低压差稳压器那样在Dropout情况升高。

GED1121IS8系列产品可使用最小0.33uF的输出电容,芯片具有电池反接保护、过流保护、过热保护等特性。

GED1121IS8系列采用SOP的塑封封装。

4. 典型应用4.1 典型应用原理图图4-1 GED1121IS8系列产品的典型应用电路图4-2 GED1121IS8系列产品输出电流与压差电压关系特性曲线调整管图4-3 GED1121IS8系列产品功能框图4.3 推荐工作条件输入电压(V I ).......................................................................................................... 4.3V~20V 工作温度(T A ) ..................................................................................................... -40℃~+125℃4.4 热阻信息4.5 ESD 等级5. 绝对最大额定值输入电压(V I ) …………………………………………………… ±30V 反向输出电流 …………………………………………………… 10mA SHDN 脚电压 …………………………………………………… 8V ,-0.6V SHDN 脚电流 …………………………………………………… 20mA贮存温度范围 …………………………………………………… -65℃~+150℃ 最大结温(T JMAX ) …………………………………………………… 150℃ 引脚温度(焊接时间10秒)…………………………………………………… 300℃注:超出任一绝对最大额定值可能会引起器件的永久性损坏。

PA8110D说明书

开孔尺寸

152+1mm×76+1mm

4.2 台式: 外形尺寸

209mm×125mm×224mm(宽×高×深)

5.使用环境条件

5.1 电源:

电压 频率

AC220V

+22V -33V

50Hz±1Hz

5.2 温度: -10℃~40℃

5.3 湿度: 40℃(20~90)%RH

5.4 无腐蚀性气体和强电磁场干扰场合

级为 3 级的规定。

1. 称量性能的基本技术指标

1.1 非线性度

0.01%FS

1.2 显示分度数

≤60000码

1.3 零点温度影响量

≤0.2μV/℃

1.4 满度温度影响量

≤10PPm/℃

1.5 传感器激励电源

电压 DC10V±0.5V

1

电流 250mA

1.6 单个传感器满量程输出码数 30000码或60000码

[启动/↑] [停机/↓]

1.称量工作状态时使显示器进入配料工作状态,“运行”指示灯亮; 2.置数时使显示闪烁位加1; 3.参数选择时确认选择数据并进入上级菜单项。

1.配料工作状态时使显示器退出配料工作状态,进入称量工作状态, “运行”指示灯熄灭; 2.置数时使显பைடு நூலகம்闪烁位减1; 3.参数选择时进入下级菜单项。

16

运行

1 1 1 1 1 1 1 0

上限

0 0 0 1 1 1 1 0

零区

0 1 1 0 0 1 1 0

锁零

1 0 1 0 1 0 1 0

注:1- 亮;0- 灭。

6

2、键功能

按键 [回零]

按键功能

1.称量工作状态时使显示回零;在称量为动态、锁零时按此键无效; 2.参数设置时取消当前修改,返回到上级菜单项。

LIS8410C_Datasheet _V1.0

版权© 莱士电子科技有限公司

莱士电子科技有限公司

4/7

LIS-DS-8410C-V1.0

LIS8410C

非隔离降压式 LED 驱动控制器

功能描述

启动和供电 LIS8410C 是通过供电电阻从线电压直接启动。通 过典型应用电路可以了解到,当采用这种供电方式 启动时,芯片 VDD 的供电电容首先通过供电电阻由 线电压充电,当其上的电压达到阈值 UVLO(off)后, 芯片启动,并开始输出脉冲驱动内部功率开关,由 于芯片自身的耗电非常少,通过启动电阻供电,便 可使 VDD 电压维持在某一值上,保证 IC 正常工作。

变压器匝数计算 当以上计算,得出L和IPK后,需用到NBS=LIPK来计算 出变压器或电感的最少匝数,N>LIPK/BS;N为变压 器线圈匝数, S为变压器磁芯中柱的截面积(AE值), B的取值需参考磁芯材质而定,以PC40材质为例,建 议B取值0.28T以下。

最短消磁时间与最长消磁时间 LIS8410C 设置了最短消磁时间和最长消磁时间,当 电感过小或输出电压过高时(输出开路),电感的消 磁时间就有可能小于芯片的最短消磁时间,此时芯片 进入保护状态,系统不断重启;当电感过大或输出电 压过低时(输出短路),电感的消磁时间就有可能大 于芯片的最长消磁时间,此时芯片也会进入保护状态。 因此选取一个合理的电感值非常重要,需要设计者重 点考量。需特别指出,当电源正常工作时,其设计的 最小消磁时间一定不能小于芯片的最小消磁时间,并 且留有足够的余量,否则电源将不能正常工作,由于 该系统架构是降压式,所以输入端整流后的最小直流 电压也一定不能低于输出电压。

过温保护 LIS8410C 集成了过温保护功能,当芯片温度超过 保护阈值后,开关管会关断,进入自动重起保护模 式。当错误条件消失,系统自动恢复正常工作状态。

阿吉伦技术8110A 150MHz脉冲生成器技术规范说明书