L1119L-33-TN3-O-T中文资料

艾特顿199333产品说明书

Eaton 199333Eaton Moeller® series U-PKZ0 Undervoltage release PKZ0(4), PKE, AC, 120 V 60 Hz, Push in terminalsGeneral specificationsEaton Moeller® series U-PKZ0 Accessory Undervoltage Release199333U-PKZ0(120V60HZ)-PI401508197417768 mm 91 mm 24 mm 0.134 kgCE Marked RoHS conformCannot be combined with A-PKZ0 shunt releaseProduct NameCatalog Number Model CodeEANProduct Length/Depth Product Height Product Width Product Weight Compliances Catalog Notes0,7- 0,35 x Uc3 VA, Coil in a cold state and 1.0 x Us5 VA, Pull-in power, Coil in a cold state and 1.0 x Us0 VMotor safety switch0.85 - 1.1 V x Uc0 V42 V0 V20 - 1424 V250 V3 VA, Coil in a cold state and 1.0 x UsEMERGENCY STOP or EMERGENCY switching-off device in accordance with IEC/EN 60204 when combined with circuit breaker55 °C480 V120 V Save time and space thanks to the new link module PKZM0-XDM32ME Motor Starters in System xStart - brochureProduct Range Catalog Switching and protecting motorsSwitching and protecting motors - catalogDA-DC-00004316.pdfDA-DC-00004917.pdfDA-DC-00004916.pdfDA-DC-00004913.pdfDA-DC-00004887.pdfDA-DC-00004889.pdfDA-DC-00004888.pdfDA-DC-00004881.pdfDA-DC-00004919.pdfDA-DC-00004918.pdfDA-DC-00004880.pdfDA-DC-00004912.pdfDA-DC-00004885.pdfeaton-manual-motor-starters-undervoltage-u-pkz0-accessory-dimensions.epsETN.U-PKZ0(120V60HZ)-PI.edzIL03407011ZIL122024ZUWIN-WIN with push-in technologya_pkz_pi.stpa_pkz_pi.dwgDrop-out voltagePower consumption, sealing, 60 HzPower consumption, pick-up, 50 HzRated control supply voltage (Us) at AC, 50 Hz - min Suitable forPick-up voltageRated control supply voltage (Us) at DC - minRated operational voltage (Ue) at AC - minRated control supply voltage (Us) at AC, 50 Hz - max Terminal capacity (solid/stranded AWG)Rated operational voltage (Ue) at DC - minRated operational voltage (Ue) at DC - maxPower consumption, sealing, 50 HzSuitable asAmbient operating temperature - maxRated operational voltage (Ue) at AC - maxRated control supply voltage (Us) at AC, 60 Hz - min BrochuresCatalogsCertification reports Declarations of conformityDrawingseCAD modelInstallation instructions Installation videosmCAD modelEaton Corporation plc Eaton House30 Pembroke Road Dublin 4, Ireland © 2023 Eaton. All Rights Reserved. Eaton is a registered trademark.All other trademarks areproperty of their respectiveowners./socialmedia5 VA, Pull-in power, Coil in a cold state and 1.0 x Us 0 V-25 °C120 V Motor protective circuit-breakerSpring clamp connectionACPower consumption, pick-up, 60 HzRated control supply voltage (Us) at DC - max Ambient operating temperature - min Rated control supply voltage (Us) at AC, 60 Hz - max Used withNumber of contacts (normally open contacts)Electric connection type Number of contacts (normally closed contacts)Number of contacts (change-over contacts)Voltage type。

(整理)国内外不锈钢焊条对照表

SAFINOX

E1-26-21Mo2-16 A412

RCND

25.20

E2-16-35Mo3Mn4W3Nb-15 A607

Nicrex 330

中国 GB E1-13-16 E1-13-15

E00-19-10-16

.................

韩 国 比利时

瑞典

国际标准化 组织

牌

号 HYUNDAI ARCOS ESAB AVESTA

R347

E19.9NbLAR Nicrex

SAFINOX

A132 E19.9NbR

NDR

EZ19.9NbLR23 RCN 18.8Nb

Chromoid

1

Nicrex

NDL A137 E19.9Nb B Chromoid

SAFINOX BCN 347

2

A202

E19.12.3RMP E19. 12.3R

A302 E23.12R

RCN

24.12

E1-23-13Mo2-16 A312 E23.12.2LR

EZ23.12.3LR23

SAFINOX

E2-26-21-16

A402 E25.20R

RCN

25.20

E2-26-21-15

SAFINOX A407 E25.20R Nicrex 1 EZ25.20 B20 BCN 310

R26

E0-18-12Mo2-15

A20 E19 123 Phoeni 4402Kb 7 B20+ x 4403K

FOX AS4 TS-309

E0-19-13Mo3-16

A24 E19 2 134LR26

TS-309M o

33099资料

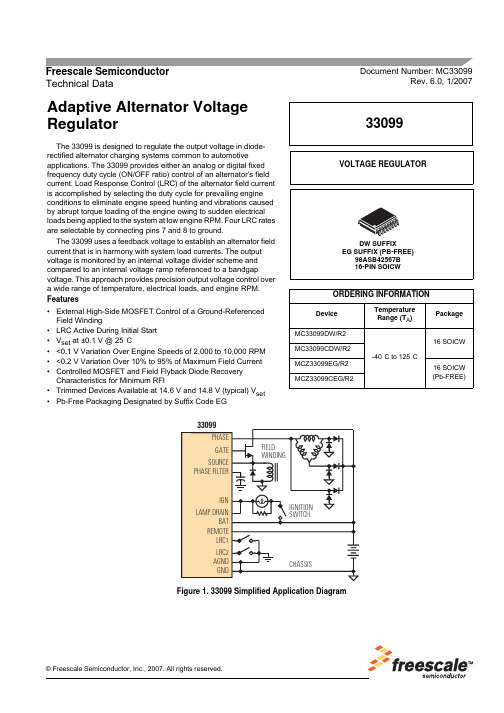

Document Number: MC33099Rev. 6.0, 1/2007Freescale Semiconductor Technical Data© Freescale Semiconductor, Inc., 2007. All rights reserved.Adaptive Alternator Voltage RegulatorThe 33099 is designed to regulate the output voltage in diode-rectified alternator charging systems common to automotiveapplications. The 33099 provides either an analog or digital fixed frequency duty cycle (ON/OFF ratio) control of an alternator’s field current. Load Response Control (LRC) of the alternator field current is accomplished by selecting the duty cycle for prevailing engine conditions to eliminate engine speed hunting and vibrations caused by abrupt torque loading of the engine owing to sudden electrical loads being applied to the system at low engine RPM. Four LRC rates are selectable by connecting pins 7 and 8 to ground.The 33099 uses a feedback voltage to establish an alternator field current that is in harmony with system load currents. The output voltage is monitored by an internal voltage divider scheme and compared to an internal voltage ramp referenced to a bandgapvoltage. This approach provides precision output voltage control over a wide range of temperature, electrical loads, and engine RPM.Features•External High-Side MOSFET Control of a Ground-Referenced Field Winding•LRC Active During Initial Start •V set at ±0.1 V @ 25°C•<0.1 V Variation Over Engine Speeds of 2,000 to 10,000 RPM •<0.2 V Variation Over 10% to 95% of Maximum Field Current •Controlled MOSFET and Field Flyback Diode Recovery Characteristics for Minimum RFI•Trimmed Devices Available at 14.6 V and 14.8 V (typical) V set •Pb-Free Packaging Designated by Suffix Code EGFigure 1. 33099 Simplified Application DiagramVOLTAGE REGULATOR33099ORDERING INFORMATIONDeviceTemperature Range (T A )PackageMC33099DW/R2-40°C to 125°C16 SOICWMC33099CDW/R2MCZ33099EG/R216 SOICW (Pb-FREE)MCZ33099CEG/R233099 Figure 2. 33099 Simplified Internal Block DiagramAnalog Integrated Circuit Device DataAnalog Integrated Circuit Device Data 33099PIN CONNECTIONSPIN CONNECTIONSFigure 3. 33099 Pin ConnectionsTable 1. PIN Function DescriptionPin NumberPin Name Formal Name Definition1GATE GATE DRIVE Controls the GATE of the MOSFET to control the alternator field current.2BAT BATTERY Primary power connection to the system battery.3GND GROUND Source lamp current and digital ground.4LAMP DRAIN LAMP DRAIN Controls the Fault Lamp current.5LAMP GATE LAMP GATE Controls the Fault Lamp internal driver as an override function.6IGN IGNITION Controls the ON or OFF function of the regulator.78LRC2LRC1LOAD RESPONSE CONTROL 2LOAD RESPONSE CONTROL 1Inputs for selecting the LRC rate.9AGND ANALOG GROUNDGround connection for analog circuitry.10REMOTEREMOTE Provides for external Kelvin connection to system battery.11, 14NC NO CONNECT No internal connection to this pin.12LRC TEST LOAD RESPONSE CONTROL TEST Provides acceleration of LRC rate for testing.13PHASE FILTER PHASE FILTER Provides access to Phase Resistive Divider for External Phase Filter capacitance.15PHASE PHASE SENSE INPUTInput for phase voltage.16SOURCESOURCECoupled to source of MOSFET to provide a GATE voltage reference and to monitor for source shorts to ground.Analog Integrated Circuit Device Data33099ELECTRICAL CHARACTERISTICS MAXIMUM RATINGSELECTRICAL CHARACTERISTICSMAXIMUM RATINGSTable 2. Maximum RatingsAll voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.RatingSymbolValueUnitELECTRICAL RATINGS Power Supply VoltageLoad Dump Transient Voltage (1)Negative Voltage (2)V BAT +V MAX -V MIN2440-2.5VESD VoltageHuman Body Model (3)Machine Model (3) (4)V ESD1V ESD2±2000±200V THERMAL RATINGSOperating Junction Temperature T J 150°C Operating Ambient Temperature Range T A - 40 to 125°C Storage Temperature RangeT STG- 45 to 150°CPower Dissipation and Thermal Characteristics Maximum Power Dissipation @ T A = 125°C Thermal Resistance, Junction-to-AmbientP D R ΘJA 64085mW °C/W Peak Package Reflow Temperature During Reflow (5), (6)T PPRTNote 6°CNotes1.125 ns wide square wave pulse.2.Maximum time = 2 minutes.3.ESD1 testing is performed in accordance with the Human Body Model (C ZAP = 100 pF, R ZAP = 1500 Ω). ESD2 testing is performed inaccordance with the Machine Model (C ZAP = 200 pF, R ZAP = 0 Ω).4.ESD2 voltage capability of PHASE FILTER pin is greater than 150 V. All other device pins are as indicated.5.Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.6.Freescale’s Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL),Go to , search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.Analog Integrated Circuit Device Data 33099ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSTable 3. Static Electrical CharacteristicsCharacteristics noted under conditions 7.0 V ≤ V SUP ≤ 18 V, - 40°C ≤ T A ≤ 125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbol MinTypMaxUnit Regulation Voltage @ 50% Duty Cycle V rem = V set or V rem < V Trem MC33099V rem = V set or V rem < V Trem MC33099CV SET14.5514.314.814.615.0514.85VRegulation Voltage Range 10% < DC < 95%DVSET–210300mVRegulation Voltage Temperature Coefficient (TC) V rem = V bat or V rem < V TremTC (V SET )-13-11-9mV/°CPower Up/Down IGN Threshold Voltage V TIGN 0.91.251.6V Operating Drain Current (Ignition ON) V ign > V Tign , V rem = V ph = V set , T A = 25°CV ign > V Tign , V rem = V ph = V set , -40°C ≤ T A ≤ 125°C I Q1(ON)I Q2(ON)––6.56.58.08.4mAStandby Drain Current (Ignition OFF)V ign < V Tign , V ph = 0 V, V rem = V bat = 12.6 V, T A = 25°CV ign < V Tign , V ph = 0 V, V rem = V bat = 12.6 V, -40°C ≤ T A ≤ 125°C I Q1(OFF)I Q2(OFF)––0.61.0 1.53.4mARemote Loss Voltage Threshold V TREM 4.2 4.5 4.8V Phase Detection Threshold Voltage V TPH 3.754.04.25V Undervoltage Threshold Voltage V set = 14.8 typical MC33099V set = 14.6 typicalMC33099CV TUV10.910.3511.3510.9511.611.55VOvervoltage Threshold Voltage V set = 14.8 typical MC33099V set = 14.6 typicalMC33099CV TOV16.1515.816.6516.417.1517.0VOvervoltage Threshold Voltage TC TC(V TOV )–-12.4–mV/°C Load Dump Threshold Voltage V set = 14.8 typical MC33099V set = 14.6 typicalMC33099CV TLD18.918.4519.2519.1519.819.85VLoad Dump Threshold Voltage TC TC(V TLD )–-14.3–mV/°C Secondary Regulation V set = 14.8 typical MC33099V set = 14.6 typical MC33099CV SET218.017.6518.518.1518.818.75VSecondary Regulation TCTC(V SET2)–-13.4–mV/°C Secondary Load Dump Threshold Voltage V set = 14.8 typical MC33099V set = 14.6 typicalMC33099CV T L D223.523.52423.852524.65VSecondary Load Dump Threshold Voltage TCTC(V T L D2)–-17.9–mV/°CAnalog Integrated Circuit Device Data33099ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSLamp Drain Short Circuit Threshold Voltage (7)V T D SC 1.8 2.25 2.85V Lamp Drain Short Circuit Current I DSC 2.02.53.0Amps Lamp Drain ON Voltage I lamp = 0.4 AV D(SAT)–0.3 2.5VLamp Drain-to-GATE Clamping Voltage V DG –48.4855V Lamp GATE Override ResistanceR LG – 4.6–k ΩLamp Driver Thermal Shutdown Temperature Limit (7)T LIM –185–°C GATE Drive Source Current I PU 240300340µA GATE Drive Sink CurrentI PD 400480560µA GATE Drive GATE-to-Source Clamping Voltage V GS 101215V Minimum Charge Pump GATE Drive Voltage V bat = V source = V setV G(MIN)21.523.4–VSource Short Circuit Threshold Voltage V TSSC 1.852.32.75V Remote Input Resistance V rem = V setR REM–68–k ΩPhase Input Resistance V ph = V setR PH–60–k ΩIGN Input Pull-Down Current V ign = 1.25 V I IGN407390µALRC Input Current V lrc = 0 VI LRC354555µANotes7.Not 100% tested.Table 3. Static Electrical Characteristics (continued)Characteristics noted under conditions 7.0 V ≤ V SUP ≤ 18 V, - 40°C ≤ T A ≤ 125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbol Min Typ Max UnitAnalog Integrated Circuit Device Data33099ELECTRICAL CHARACTERISTICSDYNAMIC ELECTRICAL CHARACTERISTICSDYNAMIC ELECTRICAL CHARACTERISTICSTable 4. Dynamic Electrical CharacteristicsCharacteristics noted under conditions 7.0 V ≤ V SUP ≤ 18 V, - 40°C ≤ T A ≤ 125°C, GND = 0 V unless otherwise noted.Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbol MinTypMaxUnit Duty Cycle Regulation Output Frequency f OSC / 256F DC300375440HzPhase Rotation Detection Frequency F 144.284953.8Hz Low / H igh RPM Transition Phase Frequency F 2267.5296325Hz GATE Duty Cycle at Startup and WOT f ph > f 2DC START3031.2534.5%Minimum GATE LRC Duty Cycle f ph < f 2DC (LRC)MIN2931.2533.5%Minimum GATE Duty Cycle V bat > V reg(max)DC MIN2.13.13.3%LRC Increasing GATE Duty Cycle Rate Low RPM Mode (f ph < f 2)LRC1 at GND, LRC2 at GND LRC1 Open, LRC2 at GND LRC1 at GND, LRC2 Open LRC1 Open, LRC2 Open High RPM Mode (f ph > f 2)R LRC1R LRC2R LRC3R LRC4R LRC (MAX)–––––9.3112.4518.7137.42616–––––%/sIgnition Turn OFF Delay (Lamp ON)T I D (OFF)–10.2–ms Lamp Short Circuit ON Polling Frequency F LSC –98.6–Hz Lamp Short Circuit ON Duty Cycle DC L – 1.56–%Lamp OFF Polling Frequency F L (OFF)–98.6–Hz Lamp Polling OFF Duty CycleDC L (OFF)– 1.56–%Field Short Circuit ON Polling Frequency F F SC –98.6–Hz Field Short Circuit Polling ON Duty CycleDC F–1.56–%Analog Integrated Circuit Device Data33099FUNCTIONAL DESCRIPTION INTRODUCTIONFUNCTIONAL DESCRIPTIONINTRODUCTIONThe 33099 is specifically designed for regulation of an automotive system voltage using diode-rectified alternator charging systems commonly found in automotiveapplications. The 33099 provides either an analog or digital duty cycle control of an ON/OFF ratio of an alternator field current at a fixed frequency. This provides for a LoadResponse Control (LRC) of the alternator field current at low engine RPM to eliminate engine speed hunting and vibration owing to abrupt torque loading of the engine when a sudden electrical load is applied to the system. Four LRC rates are selectable using a combination of pins 7 and 8 being connected to ground.The 33099 provides a regulated voltage feedback system to activate the alternator field current in response to system load current. The output voltage is monitored by an internal voltage divider scheme and compared to an internal voltage ramp referenced to a bandgap voltage. The 33099 regulates the system voltage to 14.8 V for the DW suffix and to 14.6 V for the CDW suffix by generating a pulse width modulation (PWM) voltage waveform at the GATE of an externalMOSFET to provide an average alternator field coil current as a function of the internal voltage comparison.Analog Integrated Circuit Device Data 33099TYPICAL APPLICATIONSINTRODUCTIONTYPICAL APPLICATIONSINTRODUCTIONThe 33099 is an alternator voltage regulator designed with internal level shifting resistors to control the voltage in a 12 V automotive system that uses a three-phase alternator with a rotating field winding. The system shown in Figure 4 includesan alternator with its associated field coil, stator coils and rectifiers, an automotive battery, a fault indicator lamp, an ignition switch, a field flyback diode, and the 33099.Figure 4. 33099 Simplified ApplicationThe 12 V system voltage (V BAT ) is connected to a REMOTE input by a remote wire, which provides the IC regulator with an external Kelvin connection directly to the battery to provide REMOTE voltage, V rem . The systemvoltage at the BAT pin is also sensed by an internal Local IC connection as Local voltage V l . The Local connection is provided in the event the remote wire or remote connection becomes faulty such as being resistive, an open, or shorted to ground.The PHASE input is normally connected to a tap on one corner of the alternator's stator winding, which provides an AC phase voltage (V ph ) for the IC to determine the rotational frequency (f ph ) of the alternator rotor. Two frequencycomparators (F1 and F2) monitor voltage V ph to determine a phase rotation detection frequency (f 1) and a Low/ H igh RPM transition phase frequency (f 2), respectively. A PHASE FILTER pin is provided for externally providing a filter capacitance for filtering phase input noise.The regulated DC system set voltage (V set ) is achieved by employing feedback to compare a ratioed value of V set to an internal IC bandgap voltage reference having a negative temperature coefficient (TC). The GATE drive of an external N-channel MOSFET is regulated by the IC to control the field current in the alternator field coil as an alternating ON or OFF state dependent on load current conditions affecting voltage V set . The external MOSFET receives GATE-to-sourcevoltage drive from between the GATE and SOURCE output pins of the IC. The GATE-to-source voltage is a Pulse WidthAnalog Integrated Circuit Device Data33099TYPICAL APPLICATIONSModulated (PWM) waveform having a variable ON / O FF duty cycle ratio that is determined by an analog or a digital duty cycle control circuitry that responds to variations in thesystem voltage due to variations in system load current. The PWM waveform has a duty cycle regulation output frequency of about 395 Hz (f dc ) defined by an 8-bit division of an internal 101 kHz oscillator clock frequency (f osc ). The GATE voltage at the GATE pin is due to a charge pump GATE voltage (V g ) generated by voltage multiplication using an internal charge pump voltage regulator. The high GATE-to-source voltage applied to the external MOSFET during the ON cycle of the PWM waveform minimizes a low drain-to-source ONresistance (R DS(ON) ) and associated drain-to-source voltage V d(SAT) to maximize the field current while minimizing the associated power dissipation in the MOSFET.A unique feature of the 33099 is the combinational use of analog and digital duty cycle controllers to provide a Load Response Control (LRC) duty cycle function when rotor frequency f ph is less than frequency f 2. A classic analog duty cycle function is provided at the GATE output whenfrequency f ph is greater than frequency f 2. During the LRC mode when f 1 < f ph < f 2, a sudden decrease in the system voltage due to a sudden increase in system load current will cause the analog duty cycle to rapidly increase to as great as 100%. However, the LRC circuitry causes the digital duty cycle to increase to 100% at a controlled predetermined LRC rate and overrides the analog duty cycle. Thus the alternator response time is decreased in the LRC mode and prevents the alternator from placing a sudden high torque load on the automobile engine during this slow RPM mode. This can occur when a high current accessory is switched on to the 12 V system, producing a sudden drop in system voltage. When frequency f ph is greater than frequency f 2, the slow LRC response is not in effect and the analog duty cycle controller controls the PWM voltage waveform applied to the external MOSFET to regulate the system voltage. By selectively coupling the LRC1 and LRC2 pins to ground or leaving them open, the user can program four different LRC rates (R lrc1-R lrc4) from 9.37%/sec to 37.4%/sec. During an initial ignition ON and engine start-up, the LRC rate is also in effect to minimize alternator torque loading on the engine during start, even when a Wide Open Throttle (WOT) condition (f ph > f 2) occurs.An internal N-Channel MOSFET is provided on the IC to directly drive lamp current as a fault indicator. The fault lamp is connected between the low side of the ignition switch and the LAMP DRAIN pin of the IC. A fault is indicated during an undervoltage battery condition when frequency f ph is greater than frequency f 2, during an overvoltage battery condition, and when frequency f ph is less than frequency f 1. Frequency f ph < f 1 when an insufficient alternator output voltage results or a slow or non-rotating rotor occurs due to a slipping or broken belt. An external LAMP GATE pin is also provided for the internal lamp driver to allow the user to override the internal IC fault logic and externally drive the internal lamp drive MOSFET.When a loose wire or battery pin corrosion causes the Remote voltage to decrease but is not a Remote Open condition, the system voltage will increase, causing anovervoltage Lamp fault indication, and is regulated at a secondary value of about 18.5 V.During a system load dump condition, load dumpprotection circuitry prevents GATE-to-source drive to the external MOSFET and to the internal lamp drive MOSFET. This ensures that neither the field current nor the lampcurrent is activated during load dump conditions. A drain-to-GATE voltage clamp is also provided for the internal lamp driver for further protection of this driver during load dump.An ignition pin (IGN) is provided to activate the regulator from the standby mode into a normal operating mode when the ignition switch is ON and an ignition voltage (V ign ) is greater than a power up/down ignition threshold voltage (V Tign ). When the ignition switch is OFF, voltage V ign is less than voltage V Tign , and the regulator is switched into a low current standby mode, when frequency f ph < f 1. The IGN pin can either be coupled to the low side of the ignition switch or to the low side of the lamp. When the IGN pin is connected to the low side of the lamp, the lamp must be shunted by a resistor to ensure that ignition ON is sensed, even with an OPEN lamp fault condition. When the lamp in ON, lamp current is polled OFF periodically at an ignition pollingfrequency in order for the IGN pin to periodically sense that the ignition voltage is high even though the lamp is ON. An ignition input pull-down current (I ign ) is provided to pull voltage V ign to ground when the IGN pin is OPEN or terminated on a high resistance.Two ground pins are provided by the 33099 to separate sensitive analog circuit ground (AGND) from noisy digital and high-current ground (GND).ALTERNATOR REGULATOR BIASING AND POWER UP/DOWNThe biasing of the regulator is derived from the BAT pin voltage V bat . In the normal operating mode when the ignition switch is ON and voltage V ign is greater than V Tign (about 1.25 V), a 5.0 V V DD voltage regulator biases the IC logic and provides bias to a bandgap shunt voltage regulator. The bandgap regulator maintains a reference voltage (V ref ) of approximately 2.0 V with an internal negative temperature coefficient (-TC) as well as a 1.25 V Zero TemperatureCoefficient (OTC) reference voltage. Additional bias currents and reference voltages, including a charge pump GATE voltage V g , are also generated from voltage V bat . Thetypically ignition ON drain current (I Q1(on) ) is about 6.5 mA at 25°C. When the ignition switch is OFF and voltage V ign is less than V Tign , the regulator is in a low current standby mode, having a standby drain current of about 0.7 mA (I Q1(off) ) at 25°C. During the sleep mode, some internal voltage regulators and bias currents are either terminated or minimized. However, the V DD regulator and the bandgap voltage regulator continue to maintain voltages V DD for the logic, the 2.0 V V ref , and the 1.25 V reference voltage. In addition, all logic is reset in the standby mode.After switching the ignition switch to the ON position, voltage V ign will exceed voltage V Tign , causing comparator C ign to switch states, providing an ignition-ON signal to the Ignition Delay circuit. After an Ignition start Delay Time of 500 ms, the Ignition Delay circuit activates additional currentAnalog Integrated Circuit Device Data 33099TYPICAL APPLICATIONSfor the V DD regulator and activates all other voltageregulators and bias currents. After engine start, the LRC mode is activated, independent of the phase frequency or independent of a Wide Open Throttle condition. When the battery system voltage increases to V set , the regulator resumes the normal operational mode. After switching the ignition switch to the OFF position, voltage V ign decreases below voltage V Tign , causing the comparator C ign to provide an ignition-OFF signal to the Ignition Delay Circuit. After phase frequency f ph < f 1 due to ignition turn OFF, supply currents and voltages are reduced in the regulator to provide the standby drain current drain. However, voltage V DD for logic and voltage V ref for reference voltages remain active to be able to sense an ignition input voltage.In some applications, the ignition input is connected to the low side of the fault lamp as shown in Figure 4, page 9. When the lamp driver circuitry is generating a lamp ON signal, a lamp polling signal causes the Lamp Drain output to be periodically GATED OFF. As a result, voltage V ign > V Tign during the lamp OFF polling period, causing comparator C ign to periodically provides an ignition-ON signal to the Ignition Delay Circuit. During the Lamp On condition, the Ignition Delay Circuit provides a minimum ignition turn-off delay (t id(off)) such that all currents and regulator voltages remain ON between the Lamp Off polling pulses.BATTERY AND ALTERNATOR OUTPUT VOLTAGE SENSINGThe system battery voltage is directly sensed by theREMOTE input using a remote wire as a Kelvin connection. The Remote input resistance (R rem ) at the REMOTE input is typically 68 k Ω. The voltage at the Remote Sense input (V rs ) is a ratioed value of the Remote voltage (V rem ). The intended ratio of V rem / V rs is about 7.45. The BAT pin voltage (V bat ) is also sensed as an internal Local voltage (V l ). A Local Sense voltage (V ls ) is a ratioed value of voltage V l , where the intended ratio of V l / V ls is also 7.45. The Local internalconnection is provided for fault protection against the remote wire being grounded or exhibiting a high remote wireresistance due to being disconnected or due to a corrosive or loose connection. Thus the Local connection ensures that alternator regulation of the system voltage continues in well-defined states for all possible Remote input fault conditions.LOCAL AND REMOTE VOLTAGE PROCESSING AND SWITCHINGDuring Remote operation both the external Remote input connection and internal Local connection sensesapproximately the same regulated system voltage of V set = 14.8 V. For this case, voltages V rs and V ls are approximately 2.0 V. Because the remote switching comparator C rs isreferenced to 0.6 V, both switches S1 and S2 are OPEN and remain open when voltage V rs > 0.6 V or when voltage V rem is greater than the remote loss threshold voltage (V Trem ). Voltage V rs is coupled to the input of a unity-gain combiner / b uffer CB1. Voltage V ls is buffered and coupled to the output of a unity-gain Local Buffer (LB) and ratioed by the R5 /(R4+R5) resistor divider to provide an input voltage to a unity-gain combiner / b uffer CB2. Thus the voltage at the input of the combiner CB2 is normally 0.8 V ls (or 1.6 V typically), while voltage V rs on the input of CB1 is typically 2.0 V.Because voltage V o reflects the highest voltage at the input of either combiner, voltage V o will be voltage V rs in Remote operation with Remote connected to V bat . For this case, voltage V rs is filtered by a 300 Hz low-pass filter andtranslated to the FB buffer output. Voltage V rs at the FB buffer output is then compared to a digital-to-analog converter output voltage ramp (V dac ) for duty cycle regulation.During a Remote fault condition when the remote sense line is OPEN or grounded, voltage V rs at the Remote Sense input will be zero, causing comparator C rs to activate switches S1 and S2 to a CLOSED position. As a result, voltage V ls is coupled through buffer LB directly to the input of combiner CB2. Because the voltage V ls on the input of combiner CB2 is greater than voltage V rs (= 0 V) on the input of combiner CB1, voltage V ls is coupled to the output of the combiners as voltage V o . Thus in this fault case, voltage V ls is filtered and translated to the FB buffer output for being compared to voltage ramp V dac for regulation.During a remote fault condition in which the resistance of the Remote sense wire increases due to the corrosion or a loose connection, a finite external remote fault resistance occurs causing voltage V rem to decrease, but voltage V rem remains greater than voltage V Trem . As a result, switches S1 and S2 remain in an OPEN condition, while the system voltage will increase due to the effective increase in the Remote resistor divider ratio. As a result, voltage V l increases until the voltage at the input of combiner CB2 isapproximately 2.0 V, or V ls is about 1.2 (2.0 V), or 2.25 V due to the R4 / R 5 divider ratio. Because the local divider ratio translates voltage V ls to V bat by about factor 7.4, the final regulated output voltage for this condition is 7.4 (2.25), or 18.5 V. This is the secondary regulation voltage (V set2). When the system voltage increases to the OvervoltageThreshold (V Tov ), a fault indication occurs by the lamp. Thus this particular Remote fault condition produces a fault indication, but regulates to prevent an extreme system overvoltage condition. When the Remote fault resistance becomes great enough to cause voltage V rem < V Trem , the regulated system voltage returns to the local regulation as described for an OPEN or grounded Remote input.INTERNAL CLOCK OSCILLATOR AND 8-BIT COUNTERAn internal clock oscillator is provided having a typical oscillation frequency (f osc ) of 101 kHz. The output of the oscillator is coupled to an 8-bit counter that provides 8 counting bits to the logic and the four most significant counting bits (MSB) to the LRC circuitry and to a digital-to-analog converter (DAC) waveform generator. The output MSB frequency (f msb ) of the 8-bit divider is about 395 Hz (f msb = f osc / 256), which determines the PWM frequency at the GATE output. An external LRC TEST pin is provided for accelerating internal testing of the LRC function and logic. Under normal operation, the LRC TEST pin is grounded by an internal 10 k Ω resistance to ground. Under accelerated test conditions, the LRC TEST voltage is 5.0 V, and a fourth bit (f osc /16) from the 8-bit divider is used to determine the。

REF3333中文资料

BurrĆBrown Products from Texas Instruments

REF3312, REF3318 REF3320, REF3325 REF3330, REF3333

SBOS392A – AUGUST 2007 – REVISED SEPTEMBER 2007

NOISE Output Voltage Noise

OUTPUT VOLTAGE Initial Accuracy

NOISE OutputБайду номын сангаасVoltage Noise

OUTPUT VOLTAGE Initial Accuracy

NOISE Output Voltage Noise

OUTPUT VOLTAGE Initial Accuracy

Boldface limits apply over the specified temperature range, –40°C to +125°C. At TA = +25°C and ILOAD = 0mA, unless otherwise noted.

PARAMETER

OUTPUT VOLTAGE Initial Accuracy

MAX +0.15 +0.15 +0.15 +0.15 +0.15 +0.15

UNITS

V % μVPP

V % μVPP

V % μVPP

V % μVPP

V % μVPP

V % μVPP

Copyright © 2007, Texas Instruments Incorporated

f = 0.1Hz to 10Hz REF3330 (3.0V) VIN = 5V

L1119L-33-AA3-O-T中文资料

UNISONIC TECHNOLOGIES CO., LTDL1119 CMOS IC1.5A LOW DROPOUT REGULATORSDESCRIPTIONThe UTC L1119 is a fast ultra low-dropout linear regulator that developed in CMOS process which allows low quiescent current operation independent of output load current. This CMOS process also allows the device to operate under extremely low dropout conditions.The UTC L1119 allows to operate from a 2.5V~7.0V input supply. Wide range of preset output voltage options are available and respond very fast to step changes in load which makes them suitable for low voltage microprocessor applications.FEATURES* Low ground current* Load regulation of 0.04%* Output current of 1.5A DC is guaranteed * Accurate output voltage.(± 1.5%)* Extremely low output capacitor requirements * Over temperature/ Over current protection*Pb-free plating product number: L1119L-xxORDERING INFORMATIONOrder Number Pin AssignmentNormal Lead Free Plating Package 1 2 3PackingL1119-xx-AA3-A-R L1119L-xx-AA3-A-R SOT-223 G O I Tape Reel L1119-xx-AA3-C-R L1119L-xx-AA3-C-R SOT-223 G I O Tape Reel L1119-xx-AB3-A-R L1119L-xx-AB3-A-R SOT-89 G O I Tape Reel L1119-xx-AB3-B-R L1119L-xx-AB3-B-R SOT-89 O G I Tape Reel L1119-xx-AB3-C-R L1119L-xx-AB3-C-R SOT-89 G I O Tape Reel L1119-xx-AB3-D-R L1119L-xx-AB3-D-R SOT-89 I G O Tape Reel L1119-xx-TN3-D-R L1119L-xx-TN3-D-R TO-252 I G O Tape Reel L1119-xx-TN3-D-T L1119L-xx-TN3-D-T TO-252 I G O TubeMARKING INFORMATIONBLOCK DIAGRAMGNDABSOLUTE MAXIMUM RATINGSPARAMETER SYMBOL RATINGSUNIT Input Supply Voltage V IN-0.3 ~ +7.5 VOutput Voltage V OUT-0.3 ~ +7.5 VOutput Current I OUT Short Circuit ProtectedPower Dissipation P D InternallyLimitedOperating Junction Temperature T OPR-40 ~ +125Storage Temperature T STG-65 ~ +150Note Absolute maximum ratings are those values beyond which the device could be permanently damaged.Absolute maximum ratings are stress ratings only and functional device operation is not implied.RECOMMENDED OPERATING RATINGSPARAMETER SYMBOL RATINGSUNIT Input Supply Voltage V IN 2.5 ~ 7.0 VMaximum Operating Current (DC) I OPR(MAX) 1.5 A Operating Junction Temperature T J-40 ~ +125Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged.Absolute maximum ratings are stress ratings only and functional device operation is not implied.ELECTRICAL CHARACTERISTICS(T J=25°C, V IN =V OUT+1V, I L=10mA, C OUT=33µF,unless otherwise specified.)PARAMETER SYMBOL TESTCONDITIONSMINTYPMAX UNITI L = 150 mA 38 45Dropout Voltage (Note) V DI L = 1.5 A 870mVPeak Output Current I PEAK 2.0 2.5 AI L = 150 mA 4 9Ground Pin Current I GNDI L = 1.5 A 5 14mAOutput Voltage Tolerance V OUT 10 mA ≤ I L≤ 1.5AV OUT +1 ≤ V IN≤ 7.0V-1.5 0 +1.5 %Line Regulation ∆V OUT V OUT+1V<V IN<7.0V 0.1 % Load Regulation ∆V OUT10 mA < I L < 1.5 A 1.5 % SHORT CIRCUIT PROTECTIONShort Circuit Current I SC 4.5 A AC PARAMETERSOutput Noise Density ρN(l/f) f = 120Hz 0.8 µVBW = 10Hz – 100kHz 150Output Noise Voltage eNBW = 300Hz – 300kHz 100µV(rms)V IN = V OUT + 1.5VC OUT =100uF, V OUT = 3.3V 60Ripple Rejection RRV IN = V OUT + 0.3VC OUT =100uF, V OUT = 3.3V 40dBOVER TEMPERATURE PROTECTIONShutdown Threshold T SHDN165 °C Thermal Shutdown Hysteresis T HYS 10 °C Note: Dropout voltage is defined as the minimum input to output differential voltage at which the output drops 2% below the nominal value. Dropout voltage specification applies only to output voltages of 2.5V and above. For output voltages below 2.5V, the drop-out voltage is nothing but the input to output differential, since the minimum input voltage is 2.5V.TYPICAL CHARACTERISTICS(V IN =V OUT +1V, V OUT =2.5V, C OUT =33µF, I OUT =10mA, C IN =68µF, Ta =25°C.)-40-200204060801001201400.050.10.150.20.25Temperature (℃)D r o p -O u t (V )Drop-Out Voltage vs Temperature (I L )-40-200204060801001201400.150.1750.20.225Temperature (℃)D r o p -O u t (V )Drop-Out Voltage vs Temperature (V OUT )0.125V OUT vs Temperature0.00D e l t a V O U T (%)-0.10-0.20-0.30-0.40-0.50-0.60-0.70-0.80-0.90-75-50-25255075100125Temperature (℃)100.01010Frequency (Hz)N o i s e ( V / H z )Noise Density1.0000.10010010001000001000003V IN (V)V O U T (V )Input Voltage vs Output Voltage2.50.51.5211234TYPICAL CHARACTERISTICS(Cont.)100Frequency (Hz)Output Noise Density100010000100000100Output Noise Density100010000100000Frequency (Hz)10-1090Frequency (Hz)Ripple Rejection vs Frequency1M100K10K1K1001020304050607080R i p p l e R e j e c t i o n (d B )Load Transient Response20 I O U T (A)VO U T (V )Line Transient Response10 s/DIV V I N (V )V O U T (V )Line Transient Response10 s/DIVV I N (V )V O U T (V )TYPICAL CHARACTERISTICS(Cont.)Line Transient Response10s/DIVV I N (V )V O U T (V )Line Transient Response10 3.253.33.35V I N (V )V O U T (V ) 5.34.33.453.4。

AUO_G173HW01_v0_20110530

() Preliminary Specification(V) Final SpecificationModule 17.3” FHD Color TFT-LCD Model Name G173HW01 V0Customer Date Approved byNote: This Specification is subject to change without notice.Checked &Approved by DateVito Huang2011/5/30 Prepared byVivian Huang2011/5/30Audio Video Business Group /AU Optronics corporationContents1. Handling Precautions (4)2. General Description (5)2.1 Display Characteristics (5)3. Functional Block Diagram (10)4. Absolute Maximum Ratings (11)4.1 Absolute Ratings of TFT LCD Module (11)4.2 Absolute Ratings of Environment (11)5. Electrical characteristics (12)5.1 TFT LCD Module (12)5.2 Backlight Unit (14)6. Signal Characteristic (15)6.1 Pixel Format Image (15)6.2 The Input Data Format (16)6.4 Interface Timing (19)6.5 Power ON/OFF Sequence (20)7. Connector & Pin Assignment (21)7.1 TFT LCD Module (21)7.2 Backlight Unit (22)8. Reliability Test (23)9. Shipping Label (24)10. Packing Form (25)10.1 Packaging material (25)10.2 External packaging material required (25)10.3 Palletizing sequence (26)10.4 Packing instruction (27)11. Outline Drawing (28)Record of RevisionVersion & Date PageOld DescriptionNew Description0.0 2011/1/20 All First Edition for Customer0.1 2011/1/31 12 IDD unit: A IDD unit: mA 14 VCC Max: 12.6V VCC Max: 13.4V14 Operation LifeLED life time1.0 2011/5/30 5 White Luminance(cd/m 2): 500(Typ.) White Luminance(cd/m 2): 400(Typ.) 5 Optical Response Time(ms): 8(Typ.)Optical Response Time(ms): 40(Typ.)5 Power Consumption(Watt): TBD(Typ.) Power Consumption(Watt): 17(Typ.) 5 Weight(g): TBD(Typ.) Weight(g): 1080(Typ.)6 Update Viewing Angle 6 Update Optical Response Time6 Update Color / Chromaticity Coordinates6Update White Luminance 12 IDD (mA): 350(Typ), 600(Max) IDD (mA): 1200(Typ), 1400(Max) 12 PDD (Watt): TBD(Typ), 2(Max) PDD (Watt): 5(Typ), 6(Max)12Update the diagram of Vin rising time 14 P VCC (Watt): 11.88(Typ), 13.39(Max) P VCC (Watt): 12(Typ), 15(Max) 14 Update LED Forward Voltage 14 Update Note6 description 25 Update Shipping Label25 Update Packing Form28Update Outline Drawing1. Handling Precautions1) Since front polarizer is easily damaged, please be cautious and not to scratch it.2) Be sure to turn off power supply when inserting or disconnecting from input connector.3) Wipe off water drop immediately. Long contact with water may cause discoloration or spots.4) When the panel surface is soiled, wipe it with absorbent cotton or soft cloth.5) Since the panel is made of glass, it may be broken or cracked if dropped or bumped on hard surface.6) To avoid ESD (Electro Static Discharde) damage, be sure to ground yourself before handling TFT-LCD Module.7) Do not open nor modify the module assembly.8) Do not press the reflector sheet at the back of the module to any direction.9) In case if a module has to be put back into the packing container slot after it was taken out from the container, do not press the center of the LED light bar edge. Instead, pressat the far ends of the LED light bar edge softly. Otherwise the TFT Module may be damaged.10) At the insertion or removal of the Signal Interface Connector, be sure not to rotate nor tilt the Interface Connector of the TFT Module.11) TFT-LCD Module is not allowed to be twisted & bent even force is added on module in a very short time. Please design your display product well to avoid external force applying to module by end-user directly.12) Small amount of materials without flammability grade are used in the TFT-LCD module. The TFT-LCD module should be supplied by power complied with requirements of Limited Power Source (IEC60950 or UL1950), or be applied exemption.13) Severe temperature condition may result in different luminance, response time and lamp ignition voltage.14) Continuous operating TFT-LCD display under low temperature environment may accelerate lamp exhaustion and reduce luminance dramatically.15) The data on this specification sheet is applicable when LCD module is placed in landscape position.16) Continuous displaying fixed pattern may induce image sticking. It’s recommended to use screen saver or shuffle content periodically if fixed pattern is displayed on the screen.2. General DescriptionG173HW01 V0 is a Color Active Matrix Liquid Crystal Display composed of a TFT-LCD panel, a LED driver circuit, and a LED backlight system. The screen format is intended to support the FHD (1920(H) x 1080(V)) screen and 16.7M colors (RGB 6-bits + HiFRC data). All input signals are LVDS interface compatible. Inverter card of backlight is not included.2.1 Display CharacteristicsThe following items are characteristics summary on the table under 25 ℃condition:Items Unit Specifications Screen Diagonal [mm] 17.3W (17.25)Active Area [mm] 381.888 (H) x 214.812 (V)Pixels H x V 1920(x3) x 1080Pixel Pitch [mm] 0.1989 (per one triad) x 0.1989Pixel Arrangement R.G.B. Vertical StripeDisplay Mode Normally WhiteWhite Luminance [cd/m2] 400 (Typ.)Contrast Ratio 600 : 1 (Typ)Optical ResponseTime [msec] 40 (Typ, on/off)Nominal Input Voltage VDD [Volt] 3.3 VPower Consumption [Watt] 17 (Typ)Weight [Grams] 1080 (Typ)Physical Size (H x V x D) [mm] 403 (H) x 240 (V) x 12.5 (D) (Typ) Electrical Interface Dual channel LVDSSurface Treatment Hard-coating (3H), Glare treatment Support Color 16.7M colors (RGB 6-bit data + HiFRC data)Temperature Range (Ta) Operating Storage (Non-Operating) [o C][o C]0 to +70-20 to +70RoHS Compliance RoHS Compliance2.2 Optical CharacteristicsThe optical characteristics are measured under stable conditions at 25℃ (Room Temperature):ItemUnit Conditions Min.Typ.Max.NoteHorizontal (Right) CR = 10 (Left) 70 70 80 80 -Viewing Angle [degree]Vertical (Up) CR = 10 (Down) 50 70 60 80 - 1Luminance Uniformity [%] 13 Points 75 80 - 2, 3Rising - 37 50 Falling - 3 10 Optical Response Time[msec] Rising + Falling -4060 4, 5 Red x 0.590 0.640 0.690 Red y 0.296 0.346 0.396 Green x 0.264 0.314 0.364 Green y 0.574 0.624 0.674 Blue x 0.100 0.150 0.200 Blue y 0.004 0.054 0.104 White x 0.255 0.305 0.355 Color / Chromaticity Coordinates (CIE 1931)White y0.268 0.318 0.368 4 White Luminance (At LED=100mA) [cd/m2 ]320 400 - 4 Contrast Ratio 500 600 - 4 NTSC%72Optical Equipment: BM-5A, BM-7, PR880, or equivalentNote 1: Definition of viewing angleViewing angle is the measurement of contrast ratio≧10, or ≧5, at the screen center, over a 180° horizontal and 180° vertical range (off-normal viewing angles). The 180° viewing angle range is broken down as follows; 90° (θ) horizontal left and right and 90° (Φ) vertical, high (up) and low (down). The measurement direction is typically perpendicular to the display surface with the screen rotated about its center to develop the desired measurement viewing angle.Note 2: 13 points positionNote 3:Note 4: Measurement methodThe LCD module should be stabilized at given temperature for 30 minutes to avoid abrupt temperature change during measuring. In order to stabilize the luminance, the measurement should be executed after lighting Backlight for 30 minutes in a stable, windless and dark room.Note 5: Definition of response time:The output signals of photo detector are measured when the input signals are changed from “Full Black” to “Full White” (rising time), and from “Full White” to “Full Black” (falling time), respectively. The response time is interval between the 10% and 90% of amplitudes. Please refer to the figure as below.3. Functional Block DiagramThe following diagram shows the functional block of the 17.3 inches Color TFT-LCD Module:4. Absolute Maximum RatingsAbsolute maximum ratings of the module are as following:4.1 Absolute Ratings of TFT LCD ModuleItem Symbol Min Max Unit Logic/LCD Drive Voltage Vin -0.3 +3.6 [Volt]4.2 Absolute Ratings of EnvironmentItem Symbol Min Max Unit Operating Temperature TOP 0 +70 [o C] Operation Humidity HOP 5 95 [%RH] Storage Temperature TST -20 +70 [o C] Storage Humidity HST 5 95 [%RH] Note: Maximum Wet- and no condensation.5. Electrical characteristics 5.1 TFT LCD Module5.1.1 Power Specification Input power specifications are as follows:SymbleParameter Min.Typ.Max.UnitConditionVDD Logic/LCD DriveVoltage 3.0 3.3 3.6 [Volt] ±10%IDD Input Current - 1200 1400 [mA] VDD= 5.0V, All Black Pattern At 75Hz, +30%PDD VDD Power - 5 6 [Watt] VDD= 5.0V, All Black Pattern At 75Hz , Note 1IRush Inrush Current- - 2000 [A] Note 2VDDrpAllowable Logic/LCD Drive Ripple Voltage --100[mV] p-pVDD= 3.3V, All Black Pattern At 75HzNote 1: The variance of VDD power consumption is ±30%. Note 2: Measurement conditions:Vin rising time0V5.1.2 Signal Electrical Characteristics Input signals shall be low or Hi-Z state when VDD is off. Note: LVDS Signal Waveform.5.2 Backlight UnitFollowing characteristics are measured under a stable condition using a inverter at 25℃. (Room Temperature): Symbol Parameter Min.Typ.Max.Unit RemarkVCC Input Voltage 10.8 12 13.4 [Volt]I VCC Input Current - 0.99 - [A] 100% PWM DutyP VCC Power Consumption - 12 15 [Watt]100% PWM DutyF PWM Dimming Frequency 200 - 20K [Hz]Swing Voltage 3 3.3 5.5 [Volt]Dimming duty cycle 5 - 100 %I F LED Forward Current-100 -[mA] Ta = 25o C- (3.3) (3.7) [Volt]I F = 100mA, Ta = 0o C- 3.2 3.6 [Volt]I F = 100mA, Ta = 25o C V F LED Forward Voltage- (3.1) (3.5) [Volt]I F = 100mA, Ta = 70o C P LED LED Power Consumption- (10.24)11.52 [Watt]LED Life Time50,000 - - Hrs I F=100mA, Ta= 25o CNote 1: Ta means ambient temperature of TFT-LCD module.Note 2: VCC, I VCC, P VCC are defined for LED backlight.(100% duty of PWM dimming)Note 3: I F, V F are defined for one channel LED. There are four LED channel in back light unit.Note 4: If G173HW01 V0 module is driven by high current or at high ambient temperature & humidity condition. The operating life will be reduced.Note 5: Operating life means brightness goes down to 50% initial brightness. Minimum operating life time is estimated data.Note 6: LED lifetime is definition: brightness is decreased to 50% of the initial value. LED lifetime is restricted under6. Signal Characteristic6.1 Pixel Format ImageFollowing figure shows the relationship of the input signals and LCD pixel format.1st2nd1919th1920th1stLine1080thLin6.2 The Input Data FormatNote1: Normally, DE, VS, HS on EVEN channel are not used. Note2: 8-bit in6.3 Signal DescriptionThe module using a pair of LVDS receiver SN75LVDS82(Texas Instruments) or compatible. LVDS is a differential signal technology for LCD interface and high speed data transfer device. Transmitter shall be SN75LVDS83(negative edge sampling) or compatible. The first LVDS port(RxOxxx) transmits odd pixels while the second LVDS port(RxExxx) transmits even pixels.PIN #SIGNAL NAME DESCRIPTION1 RxOIN0- Negative LVDS differential data input (Odd data)2 RxOIN0+ Positive LVDS differential data input (Odd data)3 RxOIN1- Negative LVDS differential data input (Odd data)4 RxOIN1+ Positive LVDS differential data input (Odd data)5 RxOIN2- Negative LVDS differential data input (Odd data, H-Sync,V-Sync,DSPTMG)6 RxOIN2+ Positive LVDS differential data input (Odd data, H-Sync,V-Sync,DSPTMG)7 VSS Power Ground8 RxOCLKIN- Negative LVDS differential clock input (Odd clock)9 RxOCLKIN+Positive LVDS differential clock input (Odd clock)10 RxOIN3- Negative LVDS differential data input (Odd data)11 RxOIN3+ Positive LVDS differential data input (Odd data)12 RxEIN0- Negative LVDS differential data input (Even data)13 RxEIN0+ Positive LVDS differential data input (Even data)14 VSS Power Ground15 RxEIN1- Negative LVDS differential data input (Even data)16 RxEIN1+ Positive LVDS differential data input (Even data)17 VSS Power Ground18 RxEIN2- Negative LVDS differential data input (Even data)19 RxEIN2+ Positive LVDS differential data input (Even data)20 RxECLKIN- Negative LVDS differential clock input (Even clock)21 RxECLKIN+ Positive LVDS differential clock input (Even clock)22 RxEIN3- Negative LVDS differential data input (Even data)23 RxEIN3+ Positive LVDS differential data input (Even data)24 VSS Power Ground25 VSS Power Ground26 VSS Power Ground27 VSS Power Ground28 VDD +3.3V Power Supply29 VDD +3.3V Power Supply30 VDD +3.3V Power SupplyNote1: Start from left sideRxOIN0-VDDNote2: Input signals of odd and even clock shall be the same timing. Note3: Please follow PSWG.6.4 Interface Timing6.4.1 Timing CharacteristicsBasically, interface timings should match the 1920X1080 / 60Hz manufacturing guide line timing.Note : DE mode only6.4.2 Timing Diagram6.5 Power ON/OFF SequenceVDD power and lamp on/off sequence is as follows. Interface signals are also shown in the chart. Signals from any system shall be Hi-Z state or low level when VDD is off.Power Sequence TimingPower Sequence TimingValueUnitsParameterMin. Typ. Max.T1 0.5 - 10T2 0 - 50T3 200 - --T4 0.5 - 10T5 10 - -T6 10 - -msT7 0 - -T8 10 - -T9 - - 10T10 110 - -T11 0 50T12 0 10T13 500 - -7. Connector & Pin AssignmentPhysical interface is described as for the connector on module.These connectors are capable of accommodating the following signals and will be following components.7.1 TFT LCD Module7.1.1 ConnectorConnector Name / Designation Interface Connector / Interface card Manufacturer HRSType Part Number MDF76TW-30S-1HMating Type Part Number MDF76-30P-1C7.1.2 Pin AssignmentPin#Signal Name Pin#Signal Name1 RxOIN0-2 RxOIN0+3 RxOIN1-4 RxOIN1+5 RxOIN2-6 RxOIN2+7 VSS 8 RxOCLKIN-9 RxOCLKIN+ 10 RxOIN3-11 RxOIN3+ 12 RxEIN0-13 RxEIN0+ 14 VSS15 RxEIN1- 16 RxEIN1+17 VSS 18 RxEIN2-19 RxEIN2+ 20 RxECLKIN-21 RxECLKIN+ 22 RxEIN3-23 RxEIN3+ 24 VSS25 VSS 26 VSS27 VSS 28 VDD29 VDD 30 VDD7.2 Backlight UnitPhysical interface is described as for the connector on module. These connectors are capable of accommodating the following signals and will be following components.7.2.1 ConnectorConnector Name / Designation Lamp Connector / Backlight lamp Manufacturer HRSType Part Number DF14A-6P-1.25HMating Type Part Number DF14-6S-1.25C7.2.2 Pin AssignmentPin No. Symbol DescriptionPin1 VLED 12V inputPin2 VLED 12V inputPin3 GND GNDPin4 GND GNDPin5 On/OFF 3.3-5V:ON, 0V:OFFPin6 Dimming PWM8. Reliability TestEnvironment test conditions are listed as following table.Items Required Condition Note Temperature Humidity Bias (THB) Ta= 50℃, 80%RH, 240hoursHigh Temperature Operation (HTO)Ta= 70℃, 240hoursLow Temperature Operation (LTO) Ta= 0℃, 240hoursHigh Temperature Storage (HTS) Ta= 70℃, 240hoursLow Temperature Storage (LTS) Ta= -20℃, 240hoursVibration Test (Non-operation) Acceleration: 1.5 GWave: Random Frequency: 10 - 200 - 10 Hz Sweep: 30 Minutes each Axis (X, Y, Z)Shock Test (Non-operation) Acceleration: 50 GWave: Half-sineActive Time: 20 msDirection: ±X,±Y,±Z (one time for each Axis)Drop Test Height: 60 cm, package testThermal Shock Test (TST) -20℃/30min, 60℃/30min, 50 cycles 1Contact Discharge: ± 8KV, 150pF(330Ω ) 1sec,8 points, 25 times/ point.ESD (Electro-Static Discharge)Air Discharge: ± 15KV, 150pF(330Ω ) 1sec8 points, 25 times/ point.2Note 1: The TFT-LCD module will not sustain damage after being subjected to 100 cycles of rapid temperature change. A cycle of rapid temperature change consists of varying the temperature from -20℃to 60℃, and back again. Power is not applied during the test. After temperature cycling, the unit is placed in normal room ambient for at least 4 hours before power on.Note 2: According to EN61000-4-2, ESD class B: Some performance degradation allowed. No data lost.Self-recoverable. No hardware failures.9. Shipping LabelUnit: mm10. Packing Form10.1 Packaging materialFILM PROTECTBAG ANTI-STATICTAPETAPE CREPED PAPERPACKING CARTONLABEL SPECLABEL CARTON.CUSHION PACKING10.2 External packaging material required‧Carton : 524mm*321mm*360mm, weight (carton + cushion): 1250g‧Pallet : 1140mm*980mm*140mm‧Stretch film : 500mm (W)*300M (L)‧Corner angle : L type fiber board‧PET band : 19mm (W)‧ Label : 220mm*200mm10.3 Palletizing sequencepcs / box box / layer layer / pallet pcs / pallet Shipping by air 10 2*3 3 180 Shipping by sea 10 2*3 3 180A U O P T R O N I C S C O R P O R A T I O NP r o d u c t S p e c i f i c a t i o nm e n t v e r s i o n 1.0 27/29G 173H W 01 V 0P a c k i n g i n s t r u c t i o nA U O P T R O N I C S C O R P O R A T I O NP r o d u c t S p e c i f i c a t i o nm e n t v e r s i o n 1.0 28/29G 173H W 01 V 0A U O P T R O N I C S C O R P O R A T I O NP r o d u c t S p e c i f i c a t i o nm e n t v e r s i o n 1.0 29/29G 173H W 01 V 0。

1103a-33tg1技术参数

主题:1103a-33tg1技术参数1. 产品概述1103a-33tg1是一款高性能的柴油发动机,适用于各类商用车辆、工程机械以及动力设备。

该发动机采用先进的柴油喷射技术,具有高效、节能、环保的特点。

下面将详细介绍1103a-33tg1的技术参数。

2. 发动机类型1103a-33tg1属于柴油发动机,采用直列四缸、涡轮增压、中冷技术。

该设计使得发动机在动力输出和燃油经济性方面表现出色。

3. 排量和缸径1103a-33tg1的排量为3.3升,缸径为106毫米。

这样的排量和缸径设计,使得发动机在不同负载下都能够提供充足的动力输出。

4. 最大功率1103a-33tg1的最大净功率为75kW,最大毛功率为87kW。

这一参数表明该发动机可在各种工况下提供稳定、高效的动力输出。

5. 最大扭矩1103a-33tg1的最大扭矩为320N.m,在低速工况下提供充足的动力输出,保证了车辆和设备的良好启动和加速性能。

1103a-33tg1采用了先进的共轨柴油喷射系统,能够精确控制燃油喷射的压力和时间,从而实现更加高效的燃烧,降低燃油消耗和排放。

7. 排放标准1103a-33tg1符合国家V阶段排放标准,通过优化燃烧控制和废气处理系统,将废气排放降至最低,保护环境、符合绿色环保的发展理念。

8. 应用领域1103a-33tg1适用于各种商用车辆、工程机械和动力设备,广泛应用于公交车、货车、挖掘机、装载机、发电机组等领域。

9. 总结1103a-33tg1发动机具有较高的性能、可靠的质量和先进的技术,适用于各种商用车辆和动力设备。

其符合国家V阶段排放标准,环保节能。

1103a-33tg1发动机的推出,将为各行各业的用户提供更加安全、可靠和环保的动力选择。

1103a-33tg1技术参数:10. 散热系统1103a-33tg1配备了高效的散热系统,确保发动机长时间运行时的稳定性和安全性。

通过优化的散热器设计和风道结构,有效地降低了发动机的工作温度,保证了发动机在高负荷工况下的可靠性。

Silicon Digital Attenuator HMC1119数据手册说明书

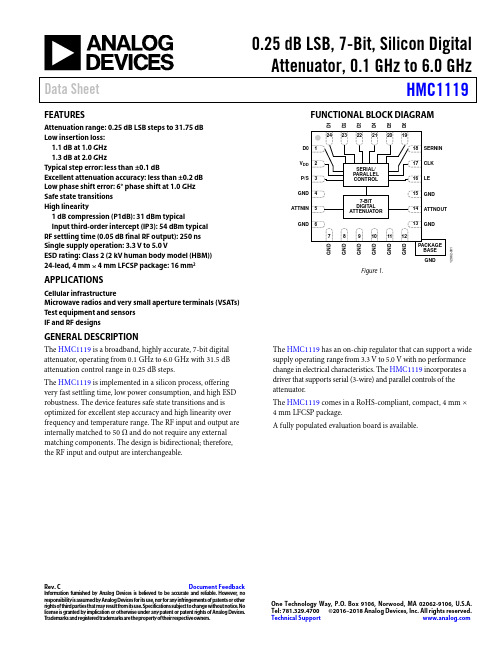

0.25 dB LSB, 7-Bit, Silicon DigitalAttenuator, 0.1 GHz to 6.0 GHz Data Sheet HMC1119Rev. C Document FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. O ne Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2016–2018 Analog Devices, Inc. All rights reserved. Technical Support FEATURESAttenuation range: 0.25 dB LSB steps to 31.75 dBLow insertion loss:1.1 dB at 1.0 GHz1.3 dB at2.0 GHzTypical step error: less than ±0.1 dBExcellent attenuation accuracy: less than ±0.2 dBLow phase shift error: 6° phase shift at 1.0 GHzSafe state transitionsHigh linearity1 dB compression (P1dB): 31 dBm typicalInput third-order intercept (IP3): 54 dBm typicalRF settling time (0.05 dB final RF output): 250 nsSingle supply operation: 3.3 V to 5.0 VESD rating: Class 2 (2 kV human body model (HBM))24-lead, 4 mm × 4 mm LFCSP package: 16 mm2 APPLICATIONSCellular infrastructureMicrowave radios and very small aperture terminals (VSATs) Test equipment and sensorsIF and RF designsFUNCTIONAL BLOCK DIAGRAMVGND65432112962-1Figure 1.GENERAL DESCRIPTIONThe HMC1119 is a broadband, highly accurate, 7-bit digital attenuator, operating from 0.1 GHz to 6.0 GHz with 31.5 dB attenuation control range in 0.25 dB steps.The HMC1119 is implemented in a silicon process, offering very fast settling time, low power consumption, and high ESD robustness. The device features safe state transitions and is optimized for excellent step accuracy and high linearity over frequency and temperature range. The RF input and output are internally matched to 50 Ω and do not require any external matching components. The design is bidirectional; therefore, the RF input and output are interchangeable. The HMC1119 has an on-chip regulator that can support a wide supply operating range from 3.3 V to 5.0 V with no performance change in electrical characteristics. The HMC1119 incorporates a driver that supports serial (3-wire) and parallel controls of the attenuator.The HMC1119 comes in a RoHS-compliant, compact, 4 mm ×4 mm LFCSP package.A fully populated evaluation board is available.HMC1119Data SheetRev. C | Page 2 of 15TABLE OF CONTENTSFeatures .............................................................................................. 1 Applications ....................................................................................... 1 Functional Block Diagram .............................................................. 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Specifications ..................................................................................... 3 Electrical Specifications ............................................................... 3 Timing Specifications .................................................................. 4 Absolute Maximum Ratings ....................................................... 5 ESD Caution .................................................................................. 5 Pin Configuration and Function Descriptions ............................. 6 Interface Schematics..................................................................... 7 Typical Performance Characteristics ............................................. 8 Insertion Loss, Return Loss, State Error, Step Error, andRelative Phase ................................................................................8 Input Power Compression and Third-Order Intercept ......... 10 Theory of Operation ...................................................................... 11 Serial Control Interface ............................................................. 11 RF Input Output ......................................................................... 11 Parallel Control Interface .......................................................... 12 Power-Up Sequence ................................................................... 12 Applications Information .............................................................. 13 Evaluation Printed Circuit Board ............................................ 13 Packaging and Ordering Information ......................................... 15 Outline Dimensions ................................................................... 15 Ordering Guide .. (15)REVISION HISTORY4/2018—Rev. B to Rev CChanges to Figure 23 ...................................................................... 12 Change to PCB Description, Table 7 ............................................ 13 Updated Outline Dimensions . (15)9/2017—Rev. A to Rev. BChanged CP-24-16 to HCP-24-3 ................................. Throughout Updated Outline Dimensions ....................................................... 15 Changes to Ordering Guide .......................................................... 15 8/2017—Rev. 0 to Rev. AAdded Timing Specifications Section ............................................. 4 Moved Table 2 .................................................................................... 4 Changes to Figure 5 and Figure 6 .................................................... 7 Changes to Serial Control Interface Section ............................... 11 Moved Figure 22 and Table 6 ........................................................ 11 Changes to Figure 23 ...................................................................... 12 Moved Parallel Control Interface Section, Direct Parallel Mode Section, Latched Parallel Mode Section, Power-Up Sequence Section, and Power-Up States Section ......................................... 12 Updated Outline Dimensions . (15)9/2016—Revision 0: Initial VersionData SheetHMC1119Rev. C | Page 3 of 15SPECIFICATIONSELECTRICAL SPECIFICATIONSV DD = 3.3 V to 5.0 V , T A = 25°C, 50 Ω system, unless otherwise noted. Table 1.ParameterTest Conditions/Comments Min Typ Max Unit FREQUENCY RANGE0.1 6.0 GHz INSERTION LOSS 0.1 GHz to 1.0 GHz 1.1 1.8 dB 0.1 GHz to 2.0 GHz 1.3 2.0 dB 0.1 GHz to 4.0 GHz 1.6 2.3 dB0.1 GHz to 6.0 GHz 2.0 2.8 dB ATTENUATION 0.2 GHz to 6.0 GHzRange Delta between minimum and maximum attenuation states31.75dB AccuracyReferenced to insertion loss; all attenuation states−(0.05 + 4% of attenuation setting) +(0.05 + 4% of attenuation setting) dB Step Error All attenuation states±0.1 dB Overshoot Between all attenuation states ≤0.1 dB RETURN LOSSAll attenuation states ATTNIN, ATTNOUT 1.0 GHz 23 dBm 2.0 GHz 22 dBm 4.0 GHz 19 dBm6.0 GHz 17 dBm RELATIVE PHASE 1.0 GHz 6 Degrees 2.0 GHz 18 Degrees 4.0 GHz 38 Degrees6.0 GHz 58 Degrees SWITCHING CHARACTERISTICSt RISE , t FALL 10%/90% RF output60 ns t ON , t OFF50% CTL to 10%/90% RF output 150 ns Settling Time 50% CTL to 0.05 dB final RF output 250 ns50% CTL to 0.10 dB final RF output 200 ns INPUT LINEARITYAll attenuation states, 0.2 GHz to 6 GHz 0.1 dB Compression (P0.1dB) 30 dBm 1 dB Compression (P1dB)31 dBm Input Third-Order Intercept (IP3) Two-tone input power = 16 dBm/tone, ∆f = 1 MHz 54 dBm SUPPLY CURRENT (I DD ) V DD = 3.3 V 0.3 mAV DD = 5.0 V 0.6 mA CONTROL VOLTAGE THRESHOLD <1 µA typical Low V DD = 3.3 V 0 0.5 VV DD = 5.0 V 0 0.8 V High V DD = 3.3 V 2.0 3.3 VV DD = 5.0 V 3.5 5.0 V RECOMMENDED OPERATING CONDITIONS Supply Voltage Range (V DD )3.0 5.4 V Digital Control Voltage Range For P/S, CLK, SERNIN, LE, D0 to D6 pins 0 V DD V RF Input PowerAll attenuation states, T CASE = 85°C 24 dBm Case Temperature (T CASE )−40+85°CHMC1119 Data SheetTIMING SPECIFICATIONSSee Figure 23 and Figure 24 for the timing diagrams.Table 2.Parameter Description Min Typ Max Unitt SCK Minimum serial period, see Figure 23 70 nst CS Control setup time, see Figure 23 15 nst CH Control hold time, see Figure 23 20 nst LN LE setup time, see Figure 23 15 nst LEW Minimum LE pulse width, see Figure 24 10 nst LES Minimum LE pulse spacing, see Figure 23 630 nst CKN Serial clock hold time from LE, see Figure 23 0 nst PH Hold time, see Figure 24 10 nst PS Setup time, see Figure 24 2 nsRev. C | Page 4 of 15Data SheetHMC1119Rev. C | Page 5 of 15ABSOLUTE MAXIMUM RATINGSTable 3.ParameterRating RF Input Power (T CASE = 85°C) 25 dBmDigital Control Inputs (P/S, CLK, SERNIN, LE, D0 to D6) −0.3 V to V DD + 0.5 V Supply Voltage (V DD )−0.3 V to +5.5 V Continuous Power Dissipation (P DISS ) 0.31 W Thermal Resistance (at Maximum Power Dissipation) 156°C/WTemperatureChannel Temperature 135°CStorage−65°C to +150°C Maximum Reflow Temperature 260°C (MSL3 Rating) ESD Sensitivity (HBM)2 kV (Class 2)Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.ESD CAUTIONHMC1119Data SheetRev. C | Page 6 of 15PIN CONFIGURATION AND FUNCTION DESCRIPTIONSV SERNIN NOTES1. THE EXPOSED PAD AND GND PINS MUST BE CONNECTED TO RF DC GROUND.CLK LE GND ATTNOUT GNDG N G N G N G N G N G N D 6D 5D 4D 3D 2D 112962-002Figure 2. Pin ConfigurationTable 4. Pin Function DescriptionsPin No. Mnemonic Description1, 19 to 24 D0, D6 to D1 Parallel Control Voltage Inputs. These pins attain the required attenuation (see Table 6). There is no internal pull-up or pull-down on these pins; therefore, these pins must always be kept at a valid logic level (V IH or V IL ) and must not be left floating. 2 V DD Supply Voltage Pin.3P/S Parallel/Serial Control Input. There is no internal pull-up or pull-down on this pin; therefore, this pin must always be kept at a valid logic level (V IH or V IL ) and must not be left floating. For parallel mode, set Pin 3 to low; for serial mode, set Pin 3 to high.4, 6 to 13, 15 GND Ground. The package bottom has an exposed metal pad that must connect to the printed circuit board (PCB) RF/dc ground. See Figure 4 for the GND interface schematic.5 ATTNIN Attenuator Input. This pin is dc-coupled and matched to 50 Ω. A blocking capacitor is required. Select the value of the capacitor based on the lowest frequency of operation. See Figure 5.14 ATTNOUT Attenuator Output. This pin is dc-coupled and matched to 50 Ω.A blocking capacitor is required. Select the value of the capacitor based on the lowest frequency of operation. See Figure 5.16 LE Serial/Parallel Interface Latch Enable Input. There is no internal pull-up or pull-down on this pin; therefore, this pin must always be kept at a valid logic level (V IH or V IL ) and must not be left floating. See the Theory of Operation section for more information.17 CLK Serial Interface Clock Input. There is no internal pull-up or pull-down on this pin; therefore, this pin must always be kept at a valid logic level (V IH or V IL ) and must not be left floating. See the Theory of Operation section for more information.18 SERNIN Serial interface Data Input. There is no internal pull-up or pull-down on this pin; therefore, this pin must always be kept at a valid logic level (V IH or V IL ) and must not be left floating. See the Theory of Operation section for more information.EPADExposed Pad. The exposed pad must be connected to RF/dc ground.Data SheetHMC1119Rev. C | Page 7 of 15INTERFACE SCHEMATICSD0TO D512962-021Figure 3. D0 to D6 Interface12962-022Figure 4. GND Interface12962-023Figure 5. ATTIN and ATTOUT InterfaceV 12962-024Figure 6. P/S, LE, CLK, and SERNIN InterfaceHMC1119Data SheetRev. C | Page 8 of 15TYPICAL PERFORMANCE CHARACTERISTICSINSERTION LOSS, RETURN LOSS, STATE ERROR, STEP ERROR, AND RELATIVE PHASE–4–3–2–1I N S E R T I O N L O S S (d B )FREQUENCY (GHz)12962-003Figure 7. Insertion Loss vs. Frequency at Various TemperaturesFREQUENCY (GHz)–50–40–30–20–100I N P U T R E T U R N L O S S (d B)12962-004Figure 8. Input Return Loss (Major States Only)–2.0–1.6–1.2–0.8–0.400.40.81.21.62.0043281216202428S T A T E E R R O R (d B )ATTENUATION STATE (dB)12962-007Figure 9. State Error vs. Attentuation State, 0.1 GHz to 0.5 GHzFREQUENCY (GHz)–35–30–25–20–15–10–50N O R M A L I Z E D A T T E N U A T I O N (d B )12962-005Figure 10. Normalized Attenuation (Major States Only)FREQUENCY (GHz)–60–50–40–30–20–10O U T P U T R E T U R N L O S S (d B )12962-006Figure 11. Output Return Loss (Major States Only)–1–0.8–0.6–0.4–0.200.20.40.60.81S T A T E E R R O R (d B )043281216202428ATTENUATION STATE (dB)12962-009Figure 12. State Error vs. Attentuation State, 1 GHz to 6 GHzData SheetHMC1119Rev. C | Page 9 of 15–2.0–1.5–1.0–0.500.51.01.52.0S T A T E E R R O R (d B )FREQUENCY (GHz)12962-008Figure 13. State Error vs. Frequency, Major States Only–60–40–20020406080R E L A T I V E P H A S E (d e g )FREQUENCY (GHz)12962-011Figure 14. Relative Phase vs. Frequency, Major States Only–1.0–0.8–0.6–0.4–0.200.20.40.60.81.0S T E P E R R O R (d B )FREQUENCY (GHz)12962-010Figure 15. Step Error vs. Frequency, Major States OnlyHMC1119Data SheetRev. C | Page 10 of 15INPUT POWER COMPRESSION AND THIRD-ORDER INTERCEPT152025303540P 1d B(d B m )FREQUENCY (GHz)12962-012Figure 16. P1dB vs. Frequency at Various Temperatures, MinimumAttentuation State, 0.05 GHz to 1 GHz152025303540P 0.1d B(d B m )FREQUENCY (GHz)12962-013Figure 17. P0.1dB vs. Frequency at Various Temperatures, MinimumAttentuation State, 0.05 GHz to 1 GHzFREQUENCY (GHz)3040506070I P 3(d B m )0.200.40.60.8 1.012962-014Figure 18. IP3 vs. Frequency at Various Temperatures, MinimumAttentuation State, 0.1 GHz to 1 GHz 152025303540P 1d B (dB m )FREQUENCY (GHz)12962-015Figure 19. P1dB vs. Frequency at Various Temperatures, MinimumAttentuation State, 0.05 GHz to 6 GHz152025303540P 0.1d B (dB m )FREQUENCY (GHz)12962-016Figure 20. P0.1dB vs. Frequency at Various Temperatures, MinimumAttentuation State, 0.05 GHz to 6 GHzFREQUENCY (GHz)3040506070I P 3(d B m )12962-017Figure 21. IP3 vs. Frequency at Various Temperatures, MinimumAttentuation State, 0.1 GHz to 6 GHzTHEORY OF OPERATIONThe HMC1119 incorporates a 7-bit fixed attenuator array that offers an attenuation range of 0.25 dB to 31.75 dB, with 0.25 dB steps. An integrated driver provides both serial and parallel mode control of the attenuator array (see Figure 22).The HMC1119 can be in either serial or parallel mode control by setting the P/S pin to high or low, respectively (see Table 5). The 7-bit data, loaded in either serial or parallel mode, then latches with the control signal, LE, to determine the attenuator value. Table 5. Mode Selection Table 1P/S Pin State Control Mode Low Parallel HighSerial1The P/S pin must always be kept at a valid logic level (V IH or V IL ) and must not be left floating.SERIAL CONTROL INTERFACEThe HMC1119 utilizes a 3-wire serial to parallel (SPI)configuration, as shown in the serial mode timing diagram (see Figure 23): serial data input (SERNIN), clock (CLK), and latch enable (LE). The serial control interface activates when the P/S pin is set to high.In serial mode, the 7-bit SERNIN data is clocked MSB first on rising CLK edges into the shift register; then, LE must betoggled high to latch the new attenuation state into the device. The LE must be set low to clock a set of 7-bit data into the shift register because CLK is masked to prevent the attenuator value from changing if LE is kept high.In serial mode operation, both the serial control inputs (LE, CLK, SERNIN) and the parallel control inputs (D0 to D6) must always be kept at a valid logic level (V IH or V IL ) and must not be left floating. It is recommended to connect the parallel control inputs to ground and to use pull-down resistors on all serial control input lines if the device driving these input lines goes high impedance during hibernation.RF INPUT OUTPUTThe attenuator in the HMC1119 is bidirectional; the ATTNIN and ATTNOUT pins are interchangeable as the RF input and output ports. The attenuator is internally matched to 50 Ω at both input and output; therefore, no external matching components are required. The RF pins are dc-coupled; therefore, dc blocking capacitors are required on RF lines.SERNIND0D1D2D3D4D5D6CLK P/S LERFOUTPUT12962-018Figure 22. Attenuator Array Functional Block DiagramTable 6. Truth TableDigital Control Input 1Attenuation State (dB) D6 D5 D4 D3 D2 D1D0 Low Low Low Low Low Low Low 0 (reference) Low Low Low Low Low Low High 0.25 Low Low Low Low Low High Low 0.5 Low Low Low Low High Low Low 1.0 Low Low Low High Low Low Low 2.0 Low Low High Low Low Low Low 4.0 Low High Low Low Low Low Low 8.0 High Low Low Low Low Low Low 16.0 HighHighHigh High HighHigh High 31.751Any combination of the control voltage input states shown in Table 6 provides an attenuation equal to the sum of the bits selected.12962-19 P/SSERNINCLKLEFigure 23. Serial Control Timing DiagramPARALLEL CONTROL INTERFACEThe parallel control interface has seven digital control input lines(D6 to D0) to set the attenuation value. D6 is the most significantbit (MSB) that selects the 16 dB attenuator stage, and D0 is theleast significant bit (LSB) that selects the 0.25 dB attenuator stage(see Figure 22).In parallel mode operation, both the serial control inputs (LE, CLK,SERNIN) and the parallel control inputs (D0 to D6) must always bekept at a valid logic level (V IH or V IL) and must not be left floating. Itis recommended to connect the serial control inputs to ground andto use pull-down resistors on all parallel control input lines ifthe device driving these input lines goes high impedance duringhibernation.Setting P/S to low enables parallel mode. There are two modes ofparallel operation: direct parallel mode and latched parallel mode.Direct Parallel ModeFor direct parallel mode, the latch enable (LE) pin must be kepthigh. Change the attenuation state using the control voltage inputs(D0 to D6) directly. This mode is ideal for manual control of theattenuator and using hardware, switches, or a jumper.Latched Parallel ModeThe latch enable (LE) pin must be low when changing thecontrol voltage inputs (D0 to D6) to set the attenuation state.When the desired state is set, LE must be toggled high to transferthe 7-bit data to the bypass switches of the attenuator array, thentoggled low to latch the change into the device (see Figure 24).LED6TO D0P/S12962-2Figure 24. Latched Parallel Mode Timing DiagramPOWER-UP SEQUENCEThe ideal power-up sequence is as follows:1.Power up GND.2.Power up V DD.3.Power up the digital control inputs (the relative order ofthe digital control inputs is not important).4.Power up the RF input.For latched parallel mode operation, LE must be toggled. Therelative order of the digital inputs is not important as long as theinputs are powered up after GND and V DD.Power-Up StatesThe logic state of the device is at maximum attenuation when, atpower up, LE is set to low. The attenuator latches in the desiredpower-up state approximately 200 ms after power up.APPLICATIONS INFORMATIONEVALUATION PRINTED CIRCUIT BOARDThe schematic of the evaluation board, EV2HMC1119LP4M , is shown in Figure 25. The PCB is four-layer material with a copper thickness of 0.7 mils on each layer. Each copper layer is separated with a dielectric material. The top dielectric material is 10-mil RO4350 with a typical dielectric constant of 3.48. The middle and bottom dielectric materials are FR-4 material, used for mechanical strength and to meet the overall board thickness of approximately 62 mils, which allows SMA connectors to beAll RF and dc traces are routed on the top copper layer. The RF transmission lines are designed using coplanar waveguide model (CPWG) with a width of 18 mils, spacing of 17 mils, and dielectric thickness of 10 mils to maintain 50 Ω characteristic impedance. The inner and bottom layers are solid ground planes. For optimal electrical and thermal performance, an ample number of vias are populated around the transmission lines and under the package exposed pad. The evaluation board layout serves as a recommenda-tion for the optimal performance on both electrical and thermal aspects.12962-026Figure 25. EV2HMC1119LP4M Evaluation PCBTable 7. Bill of MaterialsItem Value 1 DescriptionManufacturer 2 J1, J2 PCB mount SMA connector J318-pin dc connectorTP1, TP2Through hole mount test point C1, C3 100 pF Capacitor, 0402 package C6 10 μF Capacitor, 0603 package C71000 pF Capacitor, 0402 package R1 to R11 0 Ω Resistor, 0402 package R12 to R25 100 kΩ Resistor, 0402 packageSW1, SW2 SPDT four-position DIP switchU1 HMC1119 digital attenuator Analog Devices, Inc.PCB 3600-01280-00-1 evaluation PCB EV2HMC1119LP4M 4 from Analog Devices1 Blank cells in the Value column indicate that there is no specific value recommendation for the listed component.2Blank cells in the Manufacturer column indicate that there is no specific manufacturer recommendation for the listed component. 3Circuit board material is Arlon 25FR. 4Reference this number when ordering the full evaluation PCB. See the Ordering Guide section.12962-027Figure 26. Applications CircuitPACKAGING AND ORDERING INFORMATIONOUTLINE DIMENSIONS0.50BSC0.500.400.30BOTTOM VIEWTOP VIEWSIDE VIEW4.104.00 SQ 3.900.950.850.750.05 MAX 0.02 NOM0.20 REFCOPLANARITY0.08PIN 1INDICATORFOR PROPER CONNECTION OF THE EXPOSED PAD, REFER TO THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONSSECTION OF THIS DATA SHEET.12-08-2017-C0.300.250.180.20 MIN2.852.70 SQ 2.55EXPOSED PAD00SEATING PLANEDETAIL A (JEDEC 95)Figure 27. 24-Lead Lead Frame Chip Scale Package [LFCSP]4 mm × 4 mm Body and 0.85 mm Package Height(HCP-24-3)Dimensions shown in millimetersORDERING GUIDEModel 1Temperature Range MSL Rating 2 Package DescriptionPackage Option HMC1119LP4ME −40°C to +85°C MSL3 24-Lead Lead Frame Chip Scale Package [LFCSP] HCP-24-3 HMC1119LP4METR −40°C to +85°C MSL3 24-Lead Lead Frame Chip Scale Package [LFCSP] HCP-24-3 EV2HMC1119LP4MEvaluation Board1 All models are RoHS compliant.2See the Absolute Maximum Ratings section.©2016–2018 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D12962-0-4/18(C)。

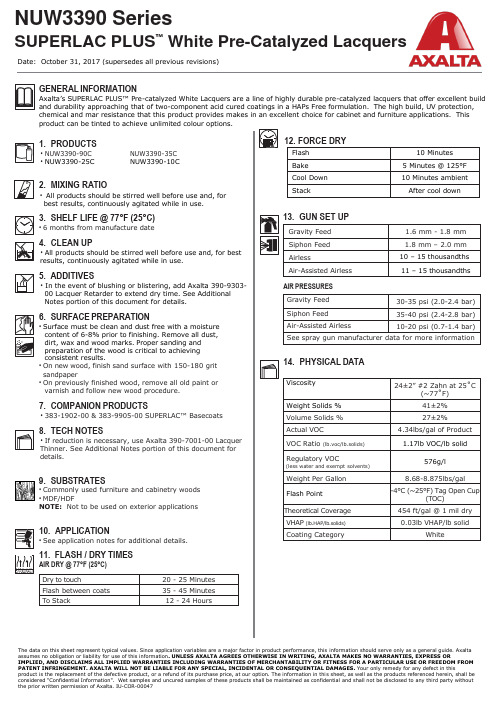

NUW3390系列超级白色预催化漆 Zenith透明防水剂说明书