第五章 集成门电路和触发器

电子教案《数字电子技术(第5版_杨志忠)》教学资源第5章练习题参考答案

电压波形。

图 P5 2

图[题 ] 图[题 ]

5 2 A

5 2 B

[题 5 3] 在同步 RS 触发器中,已知 CP、R、S 输入的电压波形如图 P5 3 所示,试画出

输出 Q 端的电压波形。设触发器的初始状态为 Q =0。

[解] 根据由与非门组成同步 RS 触发器的逻辑功能画输出 Q 的电压波形。Q 电压波形中

[解] 先画出 、 Q0 Q0 和 、 Q1 Q1 的电压波形,再根据 Y1 = Q0 Q1 和 Y2 = Q0 Q1 的与非关系,

画出输出 Y1 和 Y2 的电压波形,如图[题 5 14]所示。

图 P5 14

图[题 5 14]

第 5 章 集成触发器 127

[题 5 15] 图 P5 15 是一个用 TTL 边沿双 JK 触发器组成的单脉冲发生器,CP 为连续脉 冲,试分析其工作原理,并画出 uO 的电压波形图。 [解] 由图 P5 15 可知,平时 S 开关接地,FF0 的 J0 接地,同时 K0 = ,1 FF1 的直接置 0 端通过 S 开关接地。因此,触发器 FF0 和 FF1 都处于 0 状态,Q0 = Q1 = 0,输出 uO 为低电平 0。 当 S 开关按下时,接高电平 1,这时 FF0 和 FF1 都为 T′触发器,处于计数状态。在 CP 下 降沿作用下,FF0 由 0 状态翻到 1 状态,Q0 = 1,输出 uO 由低电平 0 跃到高电平 1。 当输入下一个 CP 的下降沿时,FF0 由 1 状态翻到 0 状态,Q0 输出一个负跃变,输出 uO 由高电平 1 跃到低电平 0,与此同时,Q0 输出的负跃变使 FF1 由 0 状态翻到 1 状态,Q1 输出 的低电平使 FF0 置 0,从而保证了 S 开关每按一次,uO 输出一个正脉冲,输入和输出电压波形 如图[题 5 15]所示。 当 S 开关放开时,S 又接地,FF0 和 FF1 又回到初始的 0 状态,为下一次输出正脉冲做好准备。

数电第5章

第五章 触 发 器

图 5 – 7 由与非门构成的基本RS触发器

第五章 触 发 器

1. 功能描述 (1) 当Rd=1, Sd=0时,不管触发器原来处于什么状态, 其次态一定为“1”,即Qn+1=1,故触发器处于置位状态。 (2) 当Rd=0, Sd=1时,Qn+1=0,触发器处于复位状态。 (3) 当Rd=Sd=1 时,触发器状态不变,处于维持状态, 即Qn+1=Qn。 (4) 当Rd=Sd=0 时,Qn+1=Q n+1=1,破坏了触发器的正常 工作,使触发器失效。而且当输入条件同时消失时,触发 器是“0”态还是“1”态是不定的,这种情况在触发器工作 时是不允许出现的。因此使用这种触发器时, 禁止 Rd=Sd=0出现。

发生的。这种电路中没有统一的时钟脉冲。任何输入信

号的变化都可能立刻引起异步时序电路状态的变依从关系来分,又可分为米里 (Mealy)型和莫尔(Moore)型两类。米里型电路的输出是输 入变量及现态的函数,即

F (t ) f [ x(t ),Qn (t )]

器和JK触发器。在基本RS触发器的基础上, 加两个与非

门即可构成钟控RS触发器, 如图 5-10 所示。

第五章 触 发 器

图 5 – 10 钟控RS触发器

第五章 触 发 器

1. 功能描述 当CP=0时,触发器不工作,此时C、D门输出均为 1, 基本RS触发器处于保持态。此时无论R、S如何变化,均 不会改变C、D门的输出,故对状态无影响。 当CP=1 时,触发器工作,其逻辑功能如下: R=0, S=1, Qn+1=1,触发器置“1”; R=1, S=0, Q n+1=0,触发器置“0”; R=S=0, Qn+1=Qn,触发器状态不变; R=S=1, 触发器失效,工作时不允许。

数字逻辑期末复习资料

第一章 数制与编码1、二、八、十、十六进制数的构成特点及相互转换;二转BCD :二B 到十D 到BCD ,二B 到十六H ,二B 到八O2、有符号数的编码;代码的最高位为符号位,1为负,0为正3、各种进制如何用BCD 码表示;4、有权码和无权码有哪些?BCD 码的分类:有权码:8421,5421,2421 无权码:余3码,BCD Gray 码 例:1、〔1100110〕B =〔0001 0000 0010〕8421BCD =〔102〕D =〔 66 〕H =〔146〕O〔178〕10=〔10110010〕2=〔0001 0111 1000 〕8421BCD =〔B2 〕16=〔 262〕8 2、将数1101.11B 转换为十六进制数为〔 A 〕A. D.C HB. 15.3HC. 12.E HD. 21.3H 3、在以下一组数中,最大数是〔 A 〕。

A.(258)D1 0000 0010B.(100000001 )B 257C.(103)H 0001 0000 0011259D.(001001010111 )8421BCD 2574、假设用8位字长来表示,〔-62〕D =( 1011 1110)原5、属于无权码的是〔B 〕A.8421 码B.余3 码 和 BCD Gray 的码C.2421 码D.自然二进制码 6、BCD 码是一种人为选定的0~9十个数字的代码,可以有许多种。

〔√〕 第二章 逻辑代数根底1、根本逻辑运算和复合逻辑运算的运算规律、逻辑符号;F=AB 与 逻辑乘 F=A+B 或 逻辑加F=A 非 逻辑反2、逻辑代数的根本定律及三个规则;3、逻辑函数表达式、逻辑图、真值表及相互转换;4、最小项、最大项的性质;5、公式法化简;卡诺图法化简〔有约束的和无约束的〕。

例:1、一个班级中有四个班委委员,如果要开班委会,必须这四个班委委员全部同意才能召开,其逻辑关系属于〔 A 〕逻辑关系。

A 、与B 、或C 、非 2、数字电路中使用的数制是〔 A 〕。

第五章触发器ppt课件

10

次态Qn+1的卡诺图

S Qn

R

00 01 11 10

0× × 0

0

11 1 1 0

特性方程

Qn1 (S ) S RQn

R S 1

约束条件

触发器的特性方程就是触发器次态Qn+1 与输入及现态Qn之间的逻辑关系式

11

波形图

反映触发器输入信号取值和状态之间对应关系的图形称为波形图

跳变

27

存在问题:时钟脉冲不能过宽,否则出现空翻现 象,即在一个时钟脉冲期间触发器翻 转一次以上。

C Q=S Q=R

S R Qn+1 0 0 Qn 01 0 10 1 1 1 不定

克服办法:采用 JK 触发器或 D 触发器

28

1、电路结构

Q

& RD

&

D触发器

Q

& SD

&

2、功能表

CP D Q n+1 1 00

5.1 概述

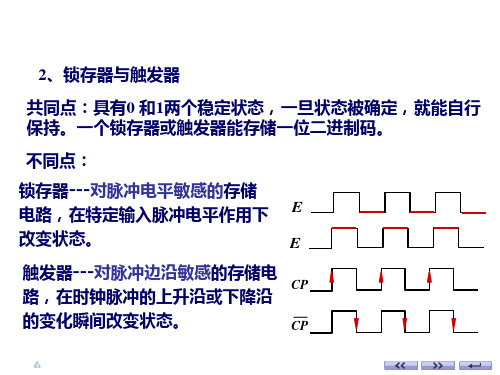

双稳态触发器: 是一种具有记忆功能的逻辑单元电路,它能储存

一位二进制码。 特点: 1、有两个稳定状态“0”态和“1”态; 2、能根据输入信号将触发器置成“0”或“1”态; 3、输入信号消失后,被置成的“0”或“1”态能

保存下来,即具有记忆功能。

1

触发器的基本概念

1.触发器有两个互补输出端:Q 、 Q 2.有两个稳定的状态:0状态和1状态; 3.在不同的输入情况下,它可以被置成0状态或1状态; 4.具有记忆(存储)功能,当输入信号消失后,所置成的

CLK S R Q Q *

X X X X Qn

0 00 0

0 01 1

1 00 1

数字电路第五章锁存器和触发器

Q3

Q

S 1S

Q

G1 G3

使能信号控制门电路

2、工作原 理

E=0: 状态不变

E=1: Q3 = S Q4 = R R

G4

G2

& Q4 ≥1

Q

状态发生变化。

S=0,R=0:Qn+1=Qn

E

S=1,R=0:Qn+1=1

≥1

&

Q

S=0,R=1:Qn+1=0

S

Q3 G1

G3

S=1,R=1:Qn+1= Ф

逻辑门控SR锁存器的E、S、R的波形如下图虚线上边所示, 锁存器的原始状态为Q = 0,试画出Q3、Q4、Q和Q 的波形。

或非门

G1

G2

Q T1 T4 Q

T3 R

T6 S

T2 T5

初态:R、S信号作用前Q端的 次态:R、S信号作用后Q端的

状态,初态用Q n表示。

状态次态用Q n+1表示。

1) 工作原理 R=0、S=0

状态不变

0 G1

R

≥1

11

Q

R

0 G1

≥1

00

Q

G2 ≥1 S

0

0

Q

若初态 Q n = 1

G2 ≥1 S

建立时间tSU :保证与D 相关的电路建立起稳定的状态,使触 发器状态得到正确的转换。 保持时间tH :保证D状态可靠地传送到Q 触发脉冲宽度tW :保证内部各门正确翻转。 传输延迟时间tPLH和tPHL :时钟脉冲CP上升沿至输出端新状态 稳定建立起来的时间 最高触发频率fcmax :触发器内部都要完成一系列动作,需要 一定的时间延迟,所以对于CP最高工作频率有一个限制。

数字电子技术基础第五章触发器

S

(a)

(a)防抖动开关电路图

uA Q uB Q

Q

反跳

反跳

Q (b)

(b)开关反跳现象及改善后的波形图

20

5.3 同步触发器

实际工作中,触发器的工作状态不仅要由触发输入 信号决定,而且要求按照一定的节拍工作。为此,需要 增加一个时钟控制端 CP。

CP 即 Clock Pulse,它是一串 周期和脉宽一定的矩形脉冲。

具有时钟脉冲控制的触发器称为时钟触发器,

又称钟控触发器。

同步触发器是其中最简单的一种,而 基本 RS 触发器称异步触发器。

21

(一)同步 RS 触发器

1. 电路结构与工作原理 Q 基本 RS 触发器 Q

G1

S1 Q3 G3

G2

Q4 R1 G4

S

10 CP

R

增加了由时钟 CP 控制的门 G3、G4

工作原理 ★ CP = 0 ,G3、G4 被封锁。基本 RS 触发 器的输入均为 1,触发器 状态保持不变。

的作用下,状态转换的 方向。

尾端:表示现态,箭头

指向表示次态。

16

(3) 特征方程(也称为状态方程或次态方程)

RD SD Qn Qn+1

说明

0 0 0 × 触发器状态不定

0 0 1×

0 1 0 0 触发器置 0 0110

1 0 0 1 触发器置 1 1011

1 1 0 0 触发器保持原状态不变 1111

9

2. 工作原理及逻辑功能 Q 1 触发器被置 1 0 Q

G1

G2

11

0 SD

输入 RD SD 00 01 10 11

输出 QQ

01 10

第五章 锁存器和触发器

Q0

Q 1

状态保持 ④ R=1,S=1

Q 0,Q 0

在这种状态下,当R、S信号同时由 “1”→“0”后,由于G1、G2传输时间不等, 输出状态将不能确定。(应避免这种情况) 。

SR锁存器约束条件:

SR = 0

《数字电子技术基础》 3)逻辑功能表

R 1 1 1 1 0 0 0 0

第五章 锁存器和触发器

G12

& &

G11

>=1 1

G4 K

0

Q

& &

J C K

Q Q

& &

G13 CP G23 J

0

&

G3

&

& &

&

G22

&

>=1 1

CP

Q

J

× 0

K

× 0 1

G21

1

Q

n 1

JQ KQ

n

n

0

1

1

0

1

Qn Qn+1 0 0 1 1 0 0 1 1 0 0 1 0 0 1 1 1 0 1 1 0

5.1 双稳态存储单元 5.2 锁存器 5.3 触发器的电路结构和工作原理

5.4 触发器的逻辑功能

5.5 用Verilog HDL描述锁存器和触发器

《数字电子技术基础》

第五章 锁存器和触发器

主讲:何玉钧

教学基本要求 1. 掌握锁存器、触发器的电路结构和工作原理;

2. 熟练掌握SR触发器、JK触发器、D触发器及T

(1)特征表:以触发器的现态和输入信号为变量,以次态为 函数,描述它们之间逻辑关系的真值表。

门电路和触发器简介

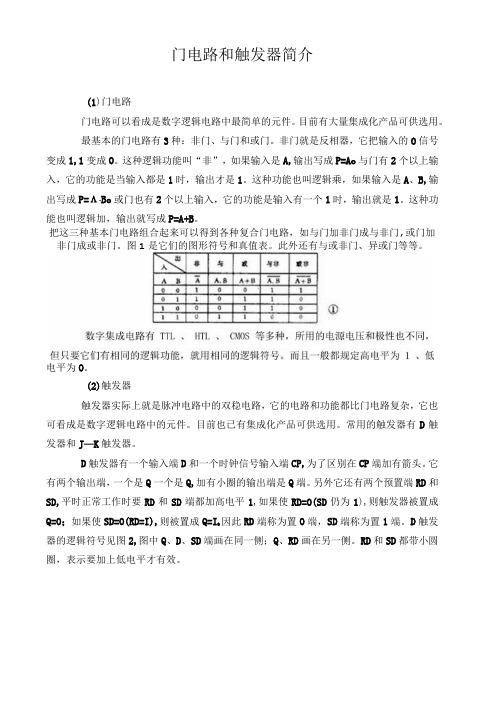

门电路和触发器简介(1)门电路门电路可以看成是数字逻辑电路中最简单的元件。

目前有大量集成化产品可供选用。

最基本的门电路有3种:非门、与门和或门。

非门就是反相器,它把输入的O信号变成1,1变成O。

这种逻辑功能叫“非”,如果输入是A,输出写成P=Ao与门有2个以上输入,它的功能是当输入都是1时,输出才是1。

这种功能也叫逻辑乘,如果输入是A、B,输出写成P=Λ∙Bo或门也有2个以上输入,它的功能是输入有一个1时,输出就是1。

这种功能也叫逻辑加,输出就写成P=A+B。

把这三种基本门电路组合起来可以得到各种复合门电路,如与门加非门成与非门,或门加非门成或非门。

图1是它们的图形符号和真值表。

此外还有与或非门、异或门等等。

电平为O。

(2)触发器触发器实际上就是脉冲电路中的双稳电路,它的电路和功能都比门电路复杂,它也可看成是数字逻辑电路中的元件。

目前也已有集成化产品可供选用。

常用的触发器有D触发器和J—K触发器。

D触发器有一个输入端D和一个时钟信号输入端CP,为了区别在CP端加有箭头。

它有两个输出端,一个是Q一个是Q,加有小圈的输出端是Q端。

另外它还有两个预置端RD和SD,平时正常工作时要RD和SD端都加高电平1,如果使RD=O(SD仍为1),则触发器被置成Q=O;如果使SD=O(RD=I),则被置成Q=I因此RD端称为置O端,SD端称为置1端。

D触发器的逻辑符号见图2,图中Q、D、SD端画在同一侧;Q、RD画在另一侧。

RD和SD都带小圆圈,表示要加上低电平才有效。

D触发器是受CP和D端双重控制的,CP加高电平1时,它的输出和D的状态相同。

如D=O,CP来到后,Q=O;如D=I,CP来到后,Q=I。

CP脉冲起控制开门作用,如果CP=O,则不管D是什么状态,触发器都维持原来状态不变。

这样的逻辑功能画成表格就称为功能表或特性表,见图2。

表中Qn÷1表示加上触发信号后变成的状态,Qn是原来的状态。

"X"表示是。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

36

A

B

TG1

Y TG2

A=0、B=1时,TG2截止,TG1导通,Y=B =1;

37

A

B

TG1

Y TG2

A=0、B=0时,TG2截止,TG1导通,Y=B =0;

38

A

B

TG1

Y TG2

A=1、B=1时,TG1截止,TG2导通,Y=B =0;

39

四、漏极开路门和三态门 (一) 漏极开路输出缓冲器 为什么需要漏极开路输出门电路 (OD门)? 普通与非门输出不能直接连在一 起实现“线与”!

动态功耗包括:负载电容充放电所消耗的功率PC和 PMOS、NMOS同时导通所消耗的瞬时导通功耗PT。

在工作频率较高的情况下,CMOS反相器的动态功耗 要比静态功耗大得多,静态功耗可忽略不计。

26

(8)转换时间和传输延迟时间

平均传输时间

vi

t pd

1 (t pLH t pHL ) 2

50%

o

(二)三态输出缓冲器

VDD

1

G4 G2

A EN

1

vO

G1 G3

0

A EN

-

1

EN

逻辑符号

Y

EN 1 , G3、G4 同时截止,输出呈高阻态;

44

(二)三态输出缓冲器

VDD

0

G4 G2 G1 G3

A EN

0

0 1

vO

0

1

A EN

-

1

EN

逻辑符号

Y

1

YA

EN 0 , G3、G4 同时导通;

49

第二节 TTL门电路

双极型三极管的开关特性

一、双极型三极管的结构

C B

集电极

集电极

C

基极

N P N E

发射极 NPN型三极管

C B E B

基极

P N P

E

发射极 PNP型三极管

C

B E

50

二、双极型三极管的输入特性和输出特性

IB(A)

80

60

饱 和 区

IC(mA )

4 3

放大区

100A 80A 60A

48

(1)所有与CMOS电路直接接触的工具、仪表等必须可 靠接地。

(2)存储和运输CMOS电路,最好采用金属屏蔽层做包 装材料。 2.多余的输入端不能悬空。

输入端悬空极易产生感应较高的静电电压,造成器件

的永久损坏。对多余的输入端,可以按功能要求接电源或 接地,或者与其它输入端并联使用。

3.输入电路需过流保护

A B C D

& Y &

Y AB CD

40

四、漏极开路门和三态门 (一) 漏极开路输出缓冲器 为什么需要漏极开路输出门电路 (OD门)?

1

0

Y AB

产 生 一 个 很 大 的 电 流

需将一个MOS管的漏极开路构成OD门。

41

四、漏极开路门和三态门 (一) 漏极开路输出缓冲器

VDD RL

18

(3)电压传输特性 电 压 传 输 特 T1T2同时导通 T1导通T2截止

性

vTN

vTP

T2导通T1截止

阈值电压VTH

19

阈值电压UTR:电压传输特性转折区中间那一点 所对应的输入电压值 当uI<UTR时,认为 反相器是截止的, 输出高电平。 当uI>UTR时,认为 反相器是导通的, 输出低电平。 T1导通T2截止 T1T2同时导通

40

20 0.4 0.8

2

40A

20A IB=0 12 UCE(V)

UBE(V) 1

3 6 9

截止区

开启电压

输入特性曲线

输出特性曲线

51

三、双极型三极管的基本开关电路 在数字电路中,三极管作为开关元件,主要工作在饱和 和截止两种开关状态,放大区只是极短暂的过渡状态。

52

截止状态 + - ②ui=0.3V时,因为uBE<0.5V,iB=0,三极管工作在 截止状态,ic=0。因为ic=0,所以输出电压: Rb b c

21

测试表明:CMOS电路噪声容限VNH=VNL=30%VDD, 且随VDD的增加而加大。 噪声容限--衡量门电路的抗干扰能力。 噪声容限越大,表明电路抗干扰能力越强。

22

(4)输入特性 因为MOS管的栅极和衬底之间存在着以SiO2为介质的 输入电容,而绝缘介质非常薄,极易被击穿,所以应采取

保护措施。

数字电路用得最多的是增强型场效应管

2

N沟道增强型绝缘栅场效应管 (1) N沟道增强型管的结构 源极S 栅极G 漏极D SiO2绝缘层

栅极和其它 电极及硅片之 间是绝缘的, 称绝缘栅型场 效应管。

金属电极

P型硅衬底

高掺杂N区

由于金属栅极和半导体之间的绝缘层目前常用二氧化硅, 故又称金属-氧化物-半导体场效应管,简称MOS场效应管。

34

C

②C =1、 0 ,即 C 端为 C uI A VT1 Vss VT2 u0 高电平(+VDD)、C 端为低 Y

电平(0V)时,T1 和T2 至少

有一个导通,输入和输出之 间相当于开关接通一样,呈 低阻态,Vo=Vi 。

35

A

B

TG1

Y TG2

A=1、B=0时,TG1截止,TG2导通,Y=B =1;

3

vGS=0时

vGS S G vDS D

iD=0

D、S间相 当于两个 背靠背的 PN结

B

N P

N

S

D 不论D、S间有无 电压,均无法导 通,不能导电。

B

4

源极与 衬底接 在一起

vGS>0时

VGS VDS G vGS足够大时 (vGS>VGS(th)),

S

D

N B

道

N P

形成电场G—B,把 衬底中的电子吸引 到上表面,除复合 外,剩余的电子在 上表面形成了N型 层(反型层)为D、 S间的导通提供了 通道。

VT3 VT1 断开

33

三、CMOS传输门和异或门 1、CMOS传输门

C

C

uI A

VT2 VT1 Vss

u0 Y

uI A

u0 Y

①C=0、C 1 ,即C 端为低电平(0V)、 C 端为高电 平(+VDD)时, VT1和VT2都不具备开启条件而截止,输 入和输出之间相当于开关断开一样,呈高阻态。

的区域, iI从零开始增大,

24

(6)输出特性

低电平输出特性 VOL≈0 输出电压VOL随灌入电流 IOL的增加而升高

高电平输出特性 VOH≈VDD 输出电压VOH随拉入电流 25 IOH的增加而降低

(7)功耗特性 反相器从一种稳定状态突然变到另一种稳定状态的过 程中,将产生附加的功耗,即为动态功耗。

VGS(th)称为阈值电压(开启电压)

可以通过改变vGS的大小来控制iD的大小。

5

漏极

D

栅极

G S

源极

N沟道增强型

6

二、MOS管的输入、输出特性 (1) 转移特性曲线 UDS

开启 电压 UT UGS/ 无导电 有导电沟道 沟道 转移特性曲线

7

二、MOS管的输入、输出特性 (2) 输出特性曲线 对于共源极接法的电路,栅极和衬底之间被二氧 化硅绝缘层隔离,所以栅极电流为零。

若A=0,则G1导通、G2截止,Y=1; 若A=1,则G1截止、G2导通,Y=0;

45

低电平有效

A EN

-

1

EN

逻辑符号

Y

A ( EN 0) Y Z ( EN 1)

高电平有效

A EN

1

EN

逻辑符号

Y

A ( EN 1) Y Z ( EN 0)

三态门有三种状态:高电平、低电平、高阻态。

输出特性曲线

(漏极特性曲线)

8

夹断区(截止区) 条件:整个沟道都夹断

vGS UTN

特点:

iD 0

用途:做无触点的、断开状态的电子开关。

9

可变电阻区 (又称非饱和区) 条件:源端与漏端沟道 都不夹断 特点:(1)当vGS 为定值 时,iD 是 vDS 的线性函数, 管子的漏源间呈现为线性 电阻,且其阻值受 vGS 控 制。 (2)管压降vDS 很小。 用途:做压控线性电阻和无触点的、闭合状态的电子开 关。

46

(三)主要特点

CMOS电路的优点 1. 静态功耗小。 2. 允许电源电压范围宽(318V)。 3. 扇出系数大,噪声容限大。

47

CMOS电路的正确使用

1.输入电路的静电保护 CMOS电路的输入端设置了保护电路,给使用者带来很大方 便。但是,这种保护还是有限的。由于CMOS电路的输入阻抗高, 极易产生感应较高的静电电压,从而击穿MOS管栅极极薄的绝 缘层,造成器件的永久损坏。为避免静电损坏,应注意以下几 点:

G

S N 沟道耗尽型

14

D

G S

P 沟道增强型

D G S

P 沟道耗尽型

在数字电路中,多采用增强型。

15

一、CMOS反相器

当NMOS管和PMOS管成对出现在电路中,且二者在工作 中互补,称为CMOS管(意为互补)。 (1)电路结构

VDD G2

vI

G1

S2 B2 D2

D1 B1 S1

PMOS管

VT2 VT1

23

在正常的输入信号范围内 ,即–0.7V< vI <(VDD+0.7)V时 输入电流iI ≈0。(因为CMOS门 电路的GS间有一层绝缘的SiO2 薄层。) 在–0.7V ~ (VDD+0.7)V以外 -0.7