《数字电路与系统设计》第6章习题答案概要

数字电路答案第六章

第六章可编程逻辑器件PLD可编程逻辑器件PLD是由用户借助计算机和编程设备对集成电路进行编程,使之具有预定的逻辑功能,成为用户设计的ASIC芯片。

近年来,可编程逻辑器件从芯片密度上、速度上发展相当迅速,已成为集成电路的一个重要分支。

本章要求读者了解PLD器件的工作原理,掌握用可编程逻辑器件设计数字电路的方法。

为掌握使用电子设计自动化和可编程逻辑器件设计电路系统的后续课程打下良好的基础。

第一节基本知识、重点与难点一、基本知识(一)可编程逻辑器件PLD基本结构可编程逻辑器件PLD包括只读存储器ROM、可编程只读存储器PROM、可编程逻辑阵列PLA、可编程阵列逻辑PAL、通用阵列逻辑GAL和可擦写编程逻辑器件EPLD等。

它们的组成和工作原理基本相似,其基本结构由与阵列和或阵列构成。

与阵列用来产生有关与项,或阵列把所有与项构成“与或”形式的逻辑函数。

在数字电路中,任何组合逻辑函数均可表示为与或表达式,因而用“与门-或门”两级电路可实现任何组合电路,又因为任何时序电路是由组合电路加上存储元件(触发器)构成的,因而PLD的“与或”结构对实现数字电路具有普遍意义。

(二)可编程逻辑器件分类1.按编程部位分类PLD有着大致相同的基本结构,根据与阵列和或阵列是否可编程,分为三种基本类型:(1)与阵列固定,或阵列可编程;(2)与或阵列均可编程;(3)与阵列可编程,或阵列固定。

2.按编程方式分类(1)掩膜编程;(2)熔丝与反熔丝编程;(3)紫外线擦除、电可编程;(4)电擦除、电可编程;(5)在系统编程(Isp)。

(三)高密度可编程逻辑器件HDPLD单片高密度可编程逻辑器件HDPLD(High Density Programmable Logic Device)芯片内,可以集成成千上万个等效逻辑门,因此在单片高密度可编程逻辑器件内集成数字电路系统成为可能。

HDPLD器件在结构上仍延续GAL的结构原理,因而还是电擦写、电编程的EPLD 器件。

数字电路与系统设计课后习题答案

将下列各式写成按权展开式:()10=3×102+5×101+2×100+6×10-1()2=1×22+1×20+1×2-1+1×2-3()8=5×81+54×80+6×8-1()16=1×162+3×161+10×160+4×16-1+15×16-2按十进制0~17的次序,列表填写出相应的二进制、八进制、十六进制数。

解:略二进制数00000000~和0000000000~11分别可以代表多少个数?解:分别代表28=256和210=1024个数。

将下列个数分别转换成十进制数:(00)2,(1750)8,(3E8)16解:(00)2=(1000)10(1750)8=(1000)10(3E8)16=(1000)10将下列各数分别转换为二进制数:(210)8,(136)10,(88)16解:结果都为:()2将下列个数分别转换成八进制数:(111111)2,(63)10,(3F)16解:结果都为(77)8将下列个数分别转换成十六进制数:()2,(377)8,(255)10解:结果都为(FF)16转换下列各数,要求转换后保持原精度:解:()10=()10——小数点后至少取10位(0010 1011 0010)2421BCD=()2()余3循环BCD码=()2用下列代码表示(123)10,()2:解:(1)8421BCD码:(123)10=(0001 0010 0011)8421BCD()2=()10=(0001 0101)8421BCD(2)余3 BCD码(123)10=(0100 0101 0110)余3BCD()2=()10=(0100 1000)余3BCD已知A=(1011010)2,B=(101111)2,C=(1010100)2,D=(110)2(1)按二进制运算规律求A+B,A-B,C×D,C÷D,(2)将A、B、C、D转换成十进制数后,求A+B,A-B,C×D,C÷D,并将结果与(1)进行比较。

数字集成电路--电路、系统与设计(第二版)课后练习题 第六章 CMOS组合逻辑门的设计

Chapter 6 Problem Set

Chapter 6 PROBLEMS

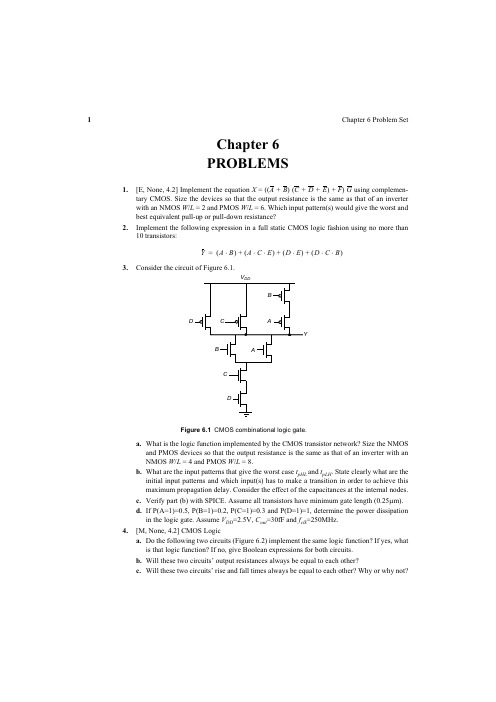

1. [E, None, 4.2] Implement the equation X = ((A + B) (C + D + E) + F) G using complementary CMOS. Size the devices so that the output resistance is the same as that of an inverter with an NMOS W/L = 2 and PMOS W/L = 6. Which input pattern(s) would give the worst and best equivalent pull-up or pull-down resistance? Implement the following expression in a full static CMOS logic fashion using no more than 10 transistors: Y = (A ⋅ B) + (A ⋅ C ⋅ E) + (D ⋅ E) + (D ⋅ C ⋅ B) 3. Consider the circuit of Figure 6.1.

2

VDD E 6 A A 6 B 6 C 6 D 6 E F A B C D 4 4 4 4 E 1 A B C D 4 4 4 4 E 1 6 F 6 B 6 C 6 D

Chapter 6 Problem Set

VDD 6

Circuit A

Circuit B

Figure 6.2 Two static CMOS gates.

数字电子技术第五版阎石 第五版第6章的 习题答案

第六章习题课后一、选择题1.PROM和PAL的结构是。

A.PROM的与阵列固定,不可编程B. PROM与阵列、或阵列均不可编程C.PAL与阵列、或阵列均可编程D. PAL的与阵列可编程2.PAL是指。

A.可编程逻辑阵列B.可编程阵列逻辑C.通用阵列逻辑D.只读存储器3.当用异步I/O输出结构的PAL设计逻辑电路时,它们相当于。

A.组合逻辑电路B.时序逻辑电路C.存储器D.数模转换器4.PLD器件的基本结构组成有。

A.输出电路B.或阵列C. 与阵列D. 输入缓冲电路5.PLD器件的主要优点有。

A.集成密度高B. 可改写C.可硬件加密D. 便于仿真测试6.GAL的输出电路是。

A.OLMCB.固定的C.只可一次编程D.可重复编程7.PLD开发系统需要有。

A.计算机B. 操作系统C. 编程器D. 开发软件8.只可进行一次编程的可编程器件有。

A.PALB.GALC.PROMD.PLD9.可重复进行编程的可编程器件有。

A.PALB.GALC.PROMD.ISP-PLD10.ISP-PLD器件开发系统的组成有。

A.计算机B.编程器C.开发软件D.编程电缆11.全场可编程(与、或阵列皆可编程)的可编程逻辑器件有。

A.PALB.GALC.PROMD.PLA12.GAL16V8的最多输入输出端个数为。

A.8输入8输出B.10输入10输出C.16输入8输出D.16输入1输出13一个容量为1K×8的存储器有个存储单元。

A.8B. 8192C.8000D. 8K14.要构成容量为4K×8的RAM,需要片容量为256×4的RAM。

A. 8B.4C. 2D.3215.寻址容量为16K×8的RAM需要根地址线。

A. 8B. 4C.14D.16KE. 1616.RAM的地址码有8位,行、列地址译码器输入端都为4个,则它们的字线加位线共有条。

A.8B.16C.32D.25617.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。

数电课后习题及答案

第1章 数字电路基础知识1 电子电路主要分为两类:一类是电子电路主要分为两类:一类是 模拟电路 ,另一类是,另一类是 数字电路 。

2 模拟电路处理的是模拟电路处理的是 模拟信号 ,而数字电路处理的是,而数字电路处理的是 数字信号 。

3 晶体管(即半导体三极管)的工作状态有三种:晶体管(即半导体三极管)的工作状态有三种:截止截止、 放大和 饱和。

在模拟电路中,晶体管主要工作在体管主要工作在 放大状态 。

4 在数字电路中,晶体管工作在在数字电路中,晶体管工作在 截止与 饱和状态,也称为状态,也称为 “开关”状态。

状态。

5 模拟信号是一种模拟信号是一种大小随时间连续变化大小随时间连续变化的电压或电流,数字信号是一种的电压或电流,数字信号是一种突变突变的电压和电流。

6 模拟信号的电压或电流的大小是模拟信号的电压或电流的大小是随时间连续缓慢变化的随时间连续缓慢变化的,而数字信号的特点是“保持”(一段时间内维持低电压或高电压)和“段时间内维持低电压或高电压)和“突变突变”(低电压与高电压的转换瞬间完成)。

7 在数字电路中常将0~1v 范围的电压称为范围的电压称为低电平低电平,用,用““0”来表示;将3~5v 范围的电压称为高电平,用,用““1”来表示。

来表示。

介绍了数字电路的发展状况和数字电路的一些应用领域,并将数字电路和模拟电路进行了比较,让读者了解两者的区别,以利于后面数字电路的学习。

以利于后面数字电路的学习。

第2章 门电路1 基本门电路有基本门电路有与门与门、或门、非门三种。

三种。

2 与门电路的特点是:只有输入端都为只有输入端都为 高电平 时,输出端才会输出高电平;只要有一个输入端为“0”,输出端就会输出输出端就会输出 低电平 。

与门的逻辑表达式是与门的逻辑表达式是 Y A B =· 。

3 或门电路的特点是:只要有一个输入端为只要有一个输入端为 高电平 ,输出端就会输出高电平。

只有输入端都为 低电平 时,输出端才会输出低电平。

数字电路与逻辑设计 徐秀平 第六章答案

读/写信号: W R 片选信号: CS

地址线: A0 ~ A7 , A8 , A9 读/写信号: W R

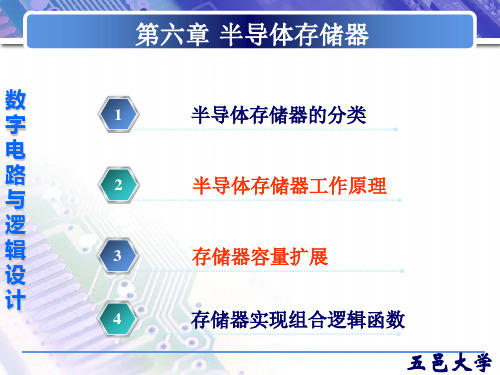

五邑大学

6.3 半导体存储器容量扩展

每一片256×8的A0~ A7可提供28=256个地址,为0~0到1~1,用扩展 的字A8、 A9构成的两位代码区别四片256×8的RAM,即将A8、 A9译成四 个低电平信号,分别接到四片256×8RAM的CS ,如下表 数

内容丢失),不能随便撕下。 586以后的ROM BIOS多采用E2PROM(电可擦写只

读ROM),通过跳线开关和系统配带的驱动程序盘,可

以对E2PROM进行重写,方便地实现BIOS升级。

五邑大学

6.1 半导体存储器的分类

ROM存储器的应用实例

数 字 电 路 与 逻 辑 设 计

• U盘是采用flash memory(也称闪存)存储技术的USB设备. USB (Universal Serial Bus)指“通用串行接口”,用 第一个字母U命名,所以简称“U盘”。 • 最新的数码存储卡是一种不需要电来维持其内容的固态

1

2

1

0

D1 W1 W2 W3

1

0

D2 W0 W2 W3

D3 W1 W3

存 储 内 容 D3 D2 D1 D0

3

1

0

1

0

0

1 0 1

1

0 1 1

0

1 1 1

1

0 1 0

存储器的容量:存储器的容量=字数(m)×字长(n)

五邑大学

6.3 半导体存储器容量扩展

1.位扩展

数 用8片1024(1K)×1位RAM构成的1024×8位RAM系统。 字 I/O I/O I/O 电 I/O I/O I/O 路 ... 102 4×1R AM 102 4×1R AM 102 4×1R AM 与 A A ... A R/W CS A A ... A R/W CS A A ... A R/W CS 逻 辑 A A 设A 计 R/W

数字电路答案第六章

第六章可编程逻辑器件PLD可编程逻辑器件PLD是由用户借助计算机和编程设备对集成电路进行编程,使之具有预定的逻辑功能,成为用户设计的ASIC芯片。

近年来,可编程逻辑器件从芯片密度上、速度上发展相当迅速,已成为集成电路的一个重要分支。

本章要求读者了解PLD器件的工作原理,掌握用可编程逻辑器件设计数字电路的方法。

为掌握使用电子设计自动化和可编程逻辑器件设计电路系统的后续课程打下良好的基础。

第一节基本知识、重点与难点一、基本知识(一)可编程逻辑器件PLD基本结构可编程逻辑器件PLD包括只读存储器ROM、可编程只读存储器PROM、可编程逻辑阵列PLA、可编程阵列逻辑PAL、通用阵列逻辑GAL和可擦写编程逻辑器件EPLD等。

它们的组成和工作原理基本相似,其基本结构由与阵列和或阵列构成。

与阵列用来产生有关与项,或阵列把所有与项构成“与或”形式的逻辑函数。

在数字电路中,任何组合逻辑函数均可表示为与或表达式,因而用“与门-或门”两级电路可实现任何组合电路,又因为任何时序电路是由组合电路加上存储元件(触发器)构成的,因而PLD的“与或”结构对实现数字电路具有普遍意义。

(二)可编程逻辑器件分类1.按编程部位分类PLD有着大致相同的基本结构,根据与阵列和或阵列是否可编程,分为三种基本类型:(1)与阵列固定,或阵列可编程;(2)与或阵列均可编程;(3)与阵列可编程,或阵列固定。

2.按编程方式分类(1)掩膜编程;(2)熔丝与反熔丝编程;(3)紫外线擦除、电可编程;(4)电擦除、电可编程;(5)在系统编程(Isp)。

(三)高密度可编程逻辑器件HDPLD单片高密度可编程逻辑器件HDPLD(High Density Programmable Logic Device)芯片内,可以集成成千上万个等效逻辑门,因此在单片高密度可编程逻辑器件内集成数字电路系统成为可能。

HDPLD器件在结构上仍延续GAL的结构原理,因而还是电擦写、电编程的EPLD 器件。

《数字电路与系统设计》课后答案

= A·BD·BC

(3) 画逻辑电路,如下图所示:

D

B

F

C

A

题4.4图

4.10电话室对3种电话编码控制,按紧急次序排列优先权高低是:火警电话、急救电话、普通电话,分别编码为11,10,01。试设计该编码电路。

解:设火警为A,急救为B,普通为C,列真值表为:

A

B

C

F

1

F2

1

1பைடு நூலகம்

1

0

1

1

0

0

0

1

0

1

0

0

0

= Y0Y4Y8Y12

F2(A,B,C,D)

m(0,1,2)

= m0m1m2

= Y0Y1Y2

F3(A,B,C,D)

m(8,9,10,11)

= m8m9m10m11

= Y8Y9Y10Y11

F4(A,B,C,D)m0

=Y0

数字电路与系统设计课后答案

4.1分析图P4.1电路的逻辑功能

数字电路课后题参考答案

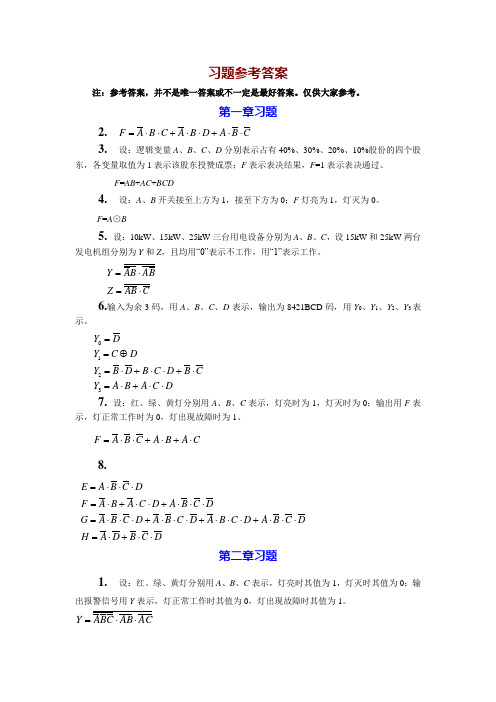

习题参考答案注:参考答案,并不是唯一答案或不一定是最好答案。

仅供大家参考。

第一章习题2. C B A D B A C B A F ⋅⋅+⋅⋅+⋅⋅=3. 设:逻辑变量A 、B 、C 、D 分别表示占有40%、30%、20%、10%股份的四个股东,各变量取值为1表示该股东投赞成票;F 表示表决结果,F =1表示表决通过。

F =AB +AC +BCD4. 设:A 、B 开关接至上方为1,接至下方为0;F 灯亮为1,灯灭为0。

F =A ⊙B5. 设:10kW 、15kW 、25kW 三台用电设备分别为A 、B 、C ,设15kW 和25kW 两台发电机组分别为Y 和Z ,且均用“0”表示不工作,用“1”表示工作。

C AB Z BA B A Y ⋅=⋅=6.输入为余3码,用A 、B 、C 、D 表示,输出为8421BCD 码,用Y 0、Y 1、Y 2、Y 3表示。

D C A B A Y CB DC BD B Y DC Y DY ⋅⋅+⋅=⋅+⋅⋅+⋅=⊕==32107. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时为1,灯灭时为0;输出用F 表示,灯正常工作时为0,灯出现故障时为1。

C A B A C B A F ⋅+⋅+⋅⋅=8. D C B D A H DC B AD C B A D C B A D C B A G DC B AD C A B A F DC B A E ⋅⋅+⋅=⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=⋅⋅⋅+⋅⋅+⋅=⋅⋅⋅=第二章习题1. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时其值为1,灯灭时其值为0;输出报警信号用Y 表示,灯正常工作时其值为0,灯出现故障时其值为1。

AC AB C B A Y ⋅⋅=2. 设:烟、温度和有害气体三种不同类型的探测器的输出信号用A 、B 、C 表示,作为报警信号电路的输入,有火灾探测信号时用1表示,没有时用0表示。

报警信号电路的书躇用Y 表示,有报警信号时用1表示,没有时用0表示。

数字逻辑电路与系统设计第6章习题及解答

第6章题解:6.1 试用4个带异步清零和置数输入端的负边沿触发型JK 触发器和门电路设计一个异步余3BCD 码计数器。

题6.1 解:余3BCD 码计数器计数规则为:0011→0100→…→1100→0011→…,由于采用异步清零和置数,故计数器应在1101时产生清零和置数信号,所设计的电路如图题解6.1所示。

CLK13图 题解6.1题6.2 试用中规模集成异步十进制计数器74290实现模48计数器。

题6.2 解:6.3 试用D 触发器和门电路设计一个同步4位格雷码计数器。

题6.3 解:根据格雷码计数规则,Q 3 Q 2Q 1 Q 0计数器的状态方程和驱动方程为:1333031210122202131011110320320100321321321321n n n n n n n nn n n n n n n n n n n n n n n n n n n n n n n n n n n n n n Q D Q Q Q Q Q Q Q Q D Q Q Q Q Q Q Q QD Q Q Q Q Q Q Q QQ D Q Q Q Q Q Q Q Q Q Q Q Q ++++==++==++==++==+++按方程画出电路图即可,图略。

题 6.4 解:反馈值为1010。

十一进制计数器6.5 试用4位同步二进制计数器74163实现十二进制计数器。

74163功能表如表6.4所示。

题 6.5 解:可采取同步清零法实现。

电路如图题解6.5所示。

题 6.6 解: 当M=1时:六进制计数器 当M=0时:八进制计数器图题解6.5图题解6.56.7 试用4位同步二进制计数器74163和门电路设计一个编码可控计数器,当输入控制变量M=0时,电路为8421BCD 码十进制计数器,M=1时电路为5421BCD 码十进制计数器,5421BCD 码计数器状态图如下图P6.7所示。

74163功能表如表6.4所示。

图 P 6.7Q 3Q 2Q 1Q 01010题6.7 解:实现8421BCD 码计数器,可采取同步清零法;5421BCD 码计数器可采取置数法实现,分析5421BCD 码计数规则可知,当21Q =时需置数,应置入的数为:32103000D D D D Q =。

数字电子技术 第六章习题答案

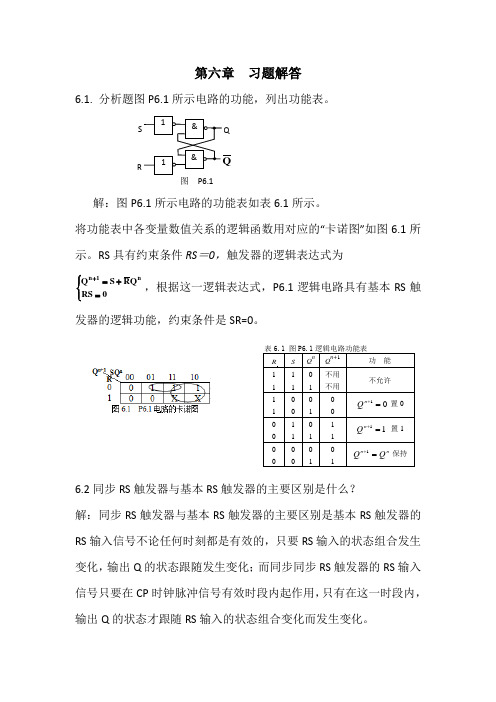

第六章 习题解答6.1. 分析题图P6.1所示电路的功能,列出功能表。

解:图P6.1所示电路的功能表如表6.1所示。

将功能表中各变量数值关系的逻辑函数用对应的“卡诺图”如图6.1所示。

RS 具有约束条件RS =0,触发器的逻辑表达式为⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,根据这一逻辑表达式,P6.1逻辑电路具有基本RS 触发器的逻辑功能,约束条件是SR=0。

6.2同步RS 触发器与基本RS 触发器的主要区别是什么?解:同步RS 触发器与基本RS 触发器的主要区别是基本RS 触发器的RS 输入信号不论任何时刻都是有效的,只要RS 输入的状态组合发生变化,输出Q 的状态跟随发生变化;而同步同步RS 触发器的RS 输入信号只要在CP 时钟脉冲信号有效时段内起作用,只有在这一时段内,输出Q 的状态才跟随RS 输入的状态组合变化而发生变化。

1& & 1QR图 P6.1QR S Q nQ n+1功 能 1 1 1 1 0 1 不用 不用 不允许11 0 0 0 1 0 0 01=+n Q 置0 0 0 1 1 0 1 1 1 11=+n Q 置10 00 00 10 1n n Q Q =+1 保持6.3如图P6.3 (a)所示电路的初始状态为Q =1,R 、S 端和CP 端的信号如图P6.3(b )所示,画出该同步RS 触发器相应的Q 和Q 端的波形。

解:根据图P6.3 (a)所示电路结构,其功能为同步RS 触发器,电路的特性方程为:⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,若R=S=1,在CP 时钟脉冲信号为“1”的时段内,触发器的两个输出端的状态均输出“1”,此种情况下,若CP 时钟脉冲信号从“1”状态,跳变为“0”的输入状态,则触发器的两个输出状态为不确定状态。

根据特性方程以及电路的初始状态,作出电路的输出端时序图如图6.3所示。

6.4 主从RS 触发器输入信号的波形如图P6.4(a )、(b )所示。

数字电路第6章习题参考答案

0

n

0

1 1 1

1

0 0 1

1

0 1 0

0

0 0 0

1

1 1 1

0

0 1 1

0

1 0 1

Q2

0 0 0

CP3 Q2 Q3

n 1

0

n

1

0

1

0

1

0

1

0 0 0

0

0 0 0

0

0 1 1

0

0 0 0

Q3

1

1

1 1

n

0

0 0 1

0

1 1 0

1

0 1 0

CP4 CP Q4

n 1

0

0 0 0

00

1000

Q1 n 0 1 0 1 0 1 0 1 0

11 10

0111

Q2n+1 0 1 1 0 0 1 1 0 0

01 11 10

0110

1 0 1 0 1 0 1 0 0

00 01

0101

11 10

10

Q2 n 0 0 1 1 0 0 1 1 0

01

Q4n+1 0 0 0 0 0 0 0 1 0

00 01 11 10

0 1 1 0

X

1 0 0

X

0 0 1

X

1 0 0

Q3n Q2n z Q1 n 00 01 11 10

0 1 1 0 0 0 X X 0 X

1

1

1

X

X

X

从6.9--6.19 共11道题,都是关于74LS90、 74LS160、 74LS194的习题。现将它们总结如下: 异步式2-5-10进制集成计数器74LS90功能表

蒋立平版数字逻辑电路与系统设计习题答案

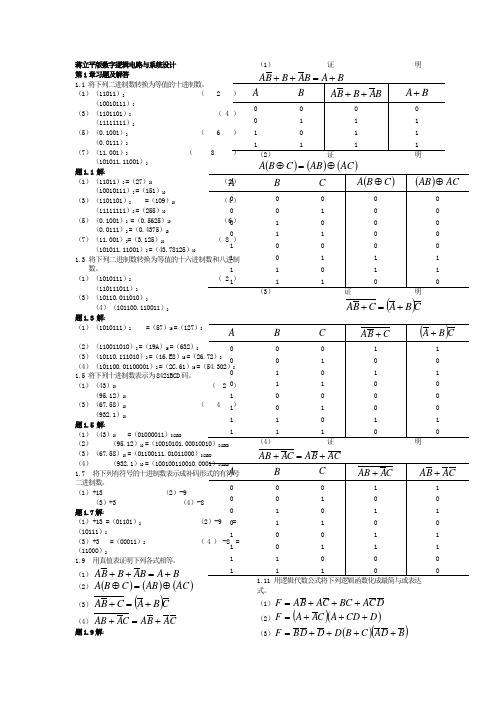

蒋立平版数字逻辑电路与系统设计 第1章习题及解答1.1 将下列二进制数转换为等值的十进制数。

(1) (11011)2(2(10010111)2 (3) (1101101)2(4 (11111111)2 (5) (0.1001)2 (6 (0.0111)2 (7) (11.001)2 (8 (101011.11001)2题1.1 解: (1) (11011)2 =(27)10(10010111)2 =(151)10(3) (1101101)2 =(109)10 (11111111)2 =(255)10(5) (0.1001)2 =(0.5625)10 (0.0111)2 =(0.4375)10(7) (11.001)2 =(3.125)10 (101011.11001)2 =(43.78125)101.3 数。

(1) (1010111)2(110111011)2 (3) (10110.011010)2(4) (101100.110011)2 题1.3 解: (1) (1010111)2=(57)16 =(127)8(2) (110011010)2 =(19A )16 =(632)8 (3) (10110.111010)2 =(16.E8)16 =((4) (101100.01100001)2 =(2C.61)16 =1.5 将下列十进制数表示为8421BCD 码。

(1) (43)10 (95.12)10 (3) (67.58)10 ( (932.1)10题1.5 解:(1) (43)10 =(01000011)8421BC D(2) (95.12)10 =(10010101.00010010)8421BC D (3) (67.58)10 =(01100111.01011000)8421BC D (4) (932.1)10 =(1.7 将下列有符号的十进制数表示成补二进制数。

(1) +13 (2)−9 (3)+3 (4)−题1.7解:(1) +13 =(01101)2 ((10111)2(3) +3 =(00011)2 ((11000)21.9 用真值表证明下列各式相等。

数字集成电路--电路、系统与设计(第二版)课后练习题 第六章 CMOS组合逻辑门的设计-Chapter 6 Designing

4

Chapter 6 Problem Set

VDD F G

A B

A

A B

A

Figure 6.6 Two-input complex logic gate.

11.

Design and simulate a circuit that generates an optimal differential signal as shown in Figure 6.7. Make sure the rise and fall times are equal.

2

VDD E 6 A A 6 B 6 C 6 D 6 F A B C D 4 4 4 4 E 1 A B C D E 4 4 4 4 E 1 6 F 6 B 6 C 6 D

Chapter 6 Problem SetVDD 6Circ来自it ACircuit B

Figure 6.2 Two static CMOS gates.

Digital Integrated Circuits - 2nd Ed

3

2.5 V

PMOS

M2 W/L = 0.5μm/0.25μm Vout Vin M1 W/L = 4μm/0.25μm NMOS Figure 6.4 Pseudo-NMOS inverter.

a. What is the output voltage if only one input is high? If all four inputs are high? b. What is the average static power consumption if, at any time, each input turns on with an (independent) probability of 0.5? 0.1? c. Compare your analytically obtained results to a SPICE simulation.

精品文档-数字电路与系统设计(第二版)(邓元庆)-第6章

第6章

从表6- 1中可以看出,为了得到应该输出的电压,只要保

证输入D2D1D0=100时输出电压UO = 0即可。为此,在求和放大器的 输入端增加了偏移电压UB和偏移电阻RB。根据图6- 8所示电路, 为 了使输入D2D1D0=100时输出电压UO = 0,电流IΣ和偏移电流IB之和 必须为零,则有:

n1

Di 2i

i0

(6-9) (6-10)

第6章 3. 倒T型电阻网络DAC电路

图6- 7所示为4位倒T型电阻网络DAC电路的原理图, 它同样 由R- 2R电阻网络、单刀双掷模拟开关(S0、S1、S2和S3)、 基准电 压UREF和求和放大器四部分构成。它与T型电阻网络DAC电路的区别在 于:

① 电阻网络呈倒T型分布。

第6章

4. 双极性DAC电路

偏移二进制码是在带符号二进制码的基础上加上一个偏移 量得到的。n位二进制数D 的偏移二进制码为

DB = DC+2n

(6- 14)

式中2n 就是偏移量,DC是n位二进制数D 的补码。例如一个正的3 位二进制数D = (+110)2,其补码为(0110)2,则对应的偏移二进制 码为:

U LSB

| U REF 2n

|

(6-16)

第6章

满量程输出电压UFSR定义为:输入数字量的所有位均为1 时, DAC输出模拟电压的幅度。有时也把UFSR称为最大输出电压 Umax。 对于n位DAC电路,满量程输出电压UFSR为

U FSR

2n 1 2n

| U REF

|

(6-17)

对于电流输出的DAC,则有ILSB和IFSR两个概念,其含义与 ULSB和UFSR相对应。有时也将ULSB和ILSB简称为LSB,将UFSR和IFSR简称 为FSR(Full Scale Range)。

《数字电路与系统设计》第6章习题答案概要

e a er a410101…X /Z0/01/0X /Z11…100…6.3对下列原始状态表进行化简: (a解:1列隐含表: 2进行关联比较3列最小化状态表为:a/1b/0bb/0a/0aX =1X =0N (t/Z (tS(t(b解:2进行关联比较: 3e:e r a94行' 试分析题图6.6电路,画出状态转移图并说明有无自启动性。

解:激励方程:略状态方程:略状态转移表:状态转移图该电路具有自启动性。

6.7 图P6.7为同步加/减可逆二进制计数器,试分析该电路,作出X=0和X=1时的状态转移表。

解:题6.7的状态转移表X Q 4nQ 3nQ 2nQ 1nQ 4n +1Q 3n +1Q 2n +1Q 1n +1Z 0 0 0 0 0 1 1 1 1 1 0 1 1 1 1 1 1 1 0 0 0 1 1 1 0 1 1 0 1 0 0 1 1 0 1 1 1 0 0 0 0 1 1 00 1 0 1 1 0 0 1 0 1 1 1 0 1 0 0 0 1 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 0 0 0 0 1 0 0 0 0 1 1 1 0 0 01 1 1 0 1 1 0 0 0 0 1 1 0 0 1 0 1 0 0 0 1 0 1 0 1 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 1 0 0 1 0 00 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 0 0 0 1 0 1 0 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 11 0 1 0 0 1 1 0 1 0 0 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 0 0 1 1 1 0 1 0 1 1 1 1 0 0 0 0 1 1 0 0 0 1 0 0 1 0 1 1 0 0 1 1 0 1 0 0 1 1 0 1 0 1 0 1 1 0 1 1 0 1 1 1 1 0 0 0 1 1 1 0 0 1 1 0 1 0 1 1 1 0 1 1 1 1 0 0 1 1 1 1 0 1 1 1 1 1 11 1116.8分析图6.8电路,画出其全状态转移图并说明能否自启动。

数字设计原理与实践第6章答案

6.20 指出用一块或多块74x138或74x139二进制译码器以及与非门,如何构建下面每个单输出或多输出的逻辑功能(提示:每个实现等效于一个最小项之和)。

解:a )∑=Z Y X F ,,)7,4,2(b )∑∏==C B A C B A F ,,,,)2,1,0()7,6,5,4,3(c) ∑=D C B A F ,,,)12,10,2,0(或d) ∑=Z Y X W F ,,,)14,12,10,8,5,4,3,2(e) ∑=Y X W F ,,)5,4,2,0( ∑=Y X W G ,,)6,3,2,1(f) ∑=C B A F ,,)6,2( ∑=E D C G ,,)3,2,0(6.21 图X5-21电路有什么可怕的错误?提出消除这个错误的方法。

解:该电路中两个2-4译码器同时使能,会导致2个3态门同时导通,出现逻辑电平冲突。

为解决这一问题,在EN_L 至1G (或2G )的线路上加一个反相器,使两路门不可能同时导通。

6.29 二进制加法器的和的第3个数位S 2为输入x 0、x 1、x 2、y 0、y 1、y 2的函数,试写出它的代数表达式:假设c 0=0,不要试图“乘开”或最小化表达式。

解:00000001)(y x c y x y x c ⋅=⋅++⋅=001111111112)()(y x y x y x c y x y x c ⋅⋅++⋅=⋅++⋅= ))((001111222222y x y x y x y x c y x s ⋅⋅++⋅⊕⊕=⊕⊕=6.38 假设要求设计一种新的组件:优化的十进制译码器,它只有十进制输入组合。

与取消6个输出的4-16译码器相比,怎样使这样的译码器价格降至最低?写出价格最低译码器的全部10个输出的逻辑等式。

假设输入和输出高电平有效且没有使能输入。

⋅⋅'C==1ABC=3⋅'Y⋅B⋅'2AY'Y'⋅'⋅'D⋅'AB⋅'CD=CY⋅'0AB⋅=Y'C6A⋅C=7⋅Y⋅BBY'C⋅'BA5A=⋅4A=Y⋅'⋅CBY⋅D98A=ADY'⋅=6.52 画出一个电路的逻辑图,该电路采用74x148判定优先级,要求8个输入I0~I7为高电平有效,I7的优先级最高。

VHDL数字电路设计教程第六章习题答案

P6.1library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_1 isport(clk:in std_logic;d_out:out std_logic_vector(5 downto 0)); end;architecture bhv of chp6_1 issignal count: std_logic_vector(5 downto 0); signal temp: std_logic_vector(5 downto 0); beginprocess(clk)beginif clk'event and clk='1' thencount<= count+1;if count="100000" then count<="000000";end if;end if;end process;process(clk)beginif clk'event and clk='0' thentemp<=temp+1;if temp="0111111" then temp<="000000"; end if;end if;end process;d_out<=count+temp;end;P6.3solution1library ieee;use ieee.std_logic_1164.all;entity chp6_3 isport(x:in std_Logic_vector(7 downto 1);y:out std_logic_vector(2 downto 0)); end;architecture bhv of chp6_3 isbeginprocess(x)beginif x(7)='1' then y<="111";elsif x(6)='1' then y<="110";elsif x(5)='1' then y<="101";elsif x(4)='1' then y<="100";elsif x(3)='1' then y<="011";elsif x(2)='1' then y<="010";elsif x(1)='1' then y<="001";else y<="000";end if;end process;end;solution2library ieee;use ieee.std_logic_1164.all;entity chp6_3_2 isgeneric(n:integer:=3);port(x:in std_logic_vector(2**n-1 downto 0);y:out integer range 0 to 2**n-1); end;architecture bhv of chp6_3_2 isbeginprocess(x)variable temp:integer range 0 to 2**n-1; beginfor i in x'range loopif x(i)='1' thentemp:=i;exit;end if;end loop;y<=temp;end process;end;P6.4library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_4 isgeneric (n:integer:=8);port(clk:in std_logic;clk_out:out std_logic);end;architecture bhv of chp6_4 issignal rst:std_logic;signal temp:std_logic_vector(2 downto 0); beginprocess(clk,rst)beginif rst='1' thentemp<="000";elsif clk'event and clk='1' thentemp<=temp+1;end if;end process;rst<='1' when temp="111" else'0';clk_out<=temp(2);end;P6.5library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_5 isgeneric (n:integer:=7);port(clk:in std_logic;clk_out:out std_logic);end;architecture bhv of chp6_5 issignal temp:std_logic_vector(2 downto 0); signal cout:std_logic;beginprocess(clk)beginif clk'event and clk='1' thentemp<=temp+1;if temp="110" then temp<="000";end if;end if;end process;cout<='1' when temp="110" else'0';clk_out<=cout;end;P6.6library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity chp6_6 isport(clk,start,stop,reset:in std_logic;dig1,dig2,dig3:out std_logic_vector(3 downto 0)); end;architecture bhv of chp6_6 issignal sec1:integer range 0 to 10;signal sec2:integer range 0 to 6;signal min:integer range 0 to 10;beginprocess(clk,start, stop,reset)variable count1:integer range 0 to 10;variable count2:integer range 0 to 6;variable count3:integer range 0 to 10;beginif reset='1' thencount1:=0;count2:=0;count3:=0;elsif clk'event and clk='1' thenif start='1' and stop='0' thencount1:=count1+1;if count1=10 thencount1:=0;count2:=count2+1;if count2=6 thencount2:=0;count3:=count3+1;if count3=10 thencount3:=0;end if;end if;end if;end if;end if;sec1<=count1;sec2<=count2;min<=count3;end process;dig1<=conv_std_logic_vector(sec1,4);dig2<=conv_std_logic_vector(sec2,4);dig3<=conv_std_logic_vector(min,4);end;P6.8use ieee.std_logic_1164.all;entity chp6_8 isgeneric(n:integer:=8);port(input:in std_logic_vector(n-1 downto 0);output:out std_logic);end;architecture bhv of chp6_8 isbeginprocess(input)variable temp:std_logic_vector(n-1 downto 0); begintemp(0):=input(0);for i in 1 to n-1 looptemp(i):=input(i) xor temp(i-1);end loop;output<=temp(n-1);end process;end;P6.9library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_9 isgeneric(n:integer:=4);port(input:std_logic_vector(n-1 downto 0);output:out integer range 0 to n);end;architecture bhv of chp6_9 isbeginprocess(input)variable temp:integer range 0 to n;begintemp:=0;for i in 0 to n-1 loopif input(i)='1' thentemp:=temp+1;end if;end loop;output<=temp;end process;end;P6.10use ieee.std_logic_1164.all;entity chp6_10 isgeneric(n:integer :=8);port(din:in integer range 0 to n-1;dout:out std_logic_vector(n-1 downto 0));end;architecture bhv of chp6_10 isbeginprocess(din)beginfor i in 0 to n-1 loopif din=i then dout<=(i=>'1', others=>'0');end if;end loop;end process;end;P6.16library ieee;use ieee.std_logic_1164.all;entity chp6_16 isgeneric (n:integer:=8);port(a,b:in std_logic_vector(n-1 downto 0);cin:in std_logic;s:out std_logic_vector(n-1 downto 0);cout:out std_logic);end;architecture bhv of chp6_16 issignal carry:std_logic_vector(n downto 0);beginprocess(a,b,cin,carry)begincarry(0)<=cin;for i in 0 to n-1 loops(i)<=a(i) xor b(i) xor carry(i);carry(i+1)<=(a(i) and b(i)) or (a(i) and carry(i)) or (b(i) and carry(i));end loop;cout<=carry(n);end process;end;说明:本次答案均为课上讨论过的,P6.11-P6.15均可参考第五章答案,可以利用对应语句将其放入进程中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

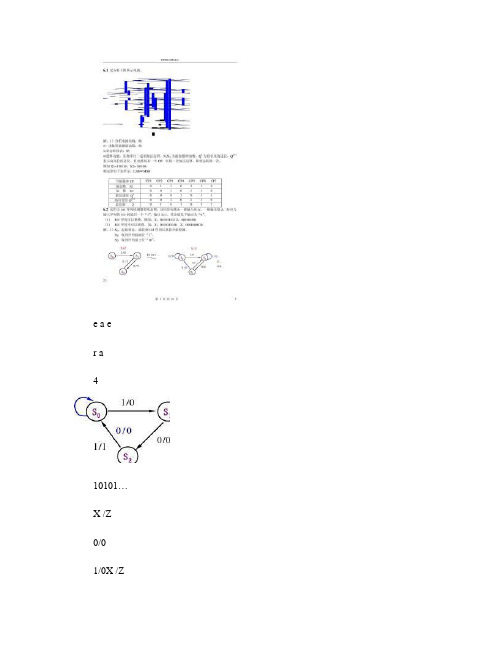

e a e

r a

4

10101…X /Z

0/0

1/0X /Z

11…100…

6.3对下列原始状态表进行化简: (a

解:1列隐含表: 2进行关联比较

3列最小化状态表为:

a/1

b/0

b

b/0a/0a

X =1X =0N (t/Z (tS(t

(b

解:2进行关联比较: 3

e

:e r a

94

行

' 试分析题图6.6电路,画出状态转移图并说明有无自启动性。

解:激励方程:略状态方程:略

状态转移表:

状态转移图该电路具有自启动性。

6.7 图P6.7为同步加/减可逆二进制计数器,试分析该电路,作出X=0和X=1时的状态转

移表。

解:题6.7的状态转移表

X Q 4n

Q 3n

Q 2n

Q 1n

Q 4n +1

Q 3n +1

Q 2n +1

Q 1n +1

Z 0 0 0 0 0 1 1 1 1 1 0 1 1 1 1 1 1 1 0 0 0 1 1 1 0 1 1 0 1 0 0 1 1 0 1 1 1 0 0 0 0 1 1 0

0 1 0 1 1 0 0 1 0 1 1 1 0 1 0 0 0 1 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 0 0 0 0 1 0 0 0 0 1 1 1 0 0 0

1 1 1 0 1 1 0 0 0 0 1 1 0 0 1 0 1 0 0 0 1 0 1 0 1 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 1 0 0 1 0 0

0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 0 0 0 1 0 1 0 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 1

1 0 1 0 0 1 1 0 1 0 0 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 0 0 1 1 1 0 1 0 1 1 1 1 0 0 0 0 1 1 0 0 0 1 0 0 1 0 1 1 0 0 1 1 0 1 0 0 1 1 0 1 0 1 0 1 1 0 1 1 0 1 1 1 1 0 0 0 1 1 1 0 0 1 1 0 1 0 1 1 1 0 1 1 1 1 0 0 1 1 1 1 0 1 1 1 1 1 1

1 1

1

1

6.8分析图6.8电路,画出其全状态转移图并说明能否自启动。

C

B

1J C 11K 1J C 11K 1J

C 1

1K

C P

Q Q Q 1

23

106682400.doc

Q 3Q 2Q 1

偏离态能够进入有效循环,因此该电路具有自启动性。

逻辑功能:该电路是一个M=5的异步计数器。

6.9用IKFF 设计符合下列条件的同步计数器电路。

当X=0时为M=5的加法计数器,其状态为0,1,2,3,4。

106682400.doc

解:M=M 1×M 2=63

6.23 试说明图6.23电路的模值为多少,并画出74160(Ⅰ的Q 0、Q 1、Q 2、Q 3端,74160

(Ⅱ的Q 0和⎺R D 端的波形,至少画出一个周期。

解:M=15

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 (ⅠQ 0 (ⅠQ 1 (ⅠQ 2 (ⅠQ 3 (ⅡQ 0 ⎺R D

6.24 试写出图6.24中各电路的状态编码表及模长。

解:(1异步清0,8421BCD 码 (2异步置9 5421BCD 码

M=5 M=8

B

h 0A

b v a e

I w 9

P B

P P P 解:M 1=6,M 2=8 电路的模长应为6和8的最小公倍数24,即M=24。

106682400.doc

6.28写出图6.28的模长及第一个状态和最后一个状态。

解:M1=7,M2=8 电路的模长应为7和8的最小公倍数56,即M=56。

解: 解:

Q Q Q Q 3

2

6.33 在上题中,若要求其输出为8421BCD 译码显示时,即计数状态为01,02, (11 12编码。

试再用一片7490和一个JKFF 实现电路。

解:

1

2

A

749Q 10R 01029192R S S 0C P C P Q 3Q 2Q 1C 1Q 1J 1K Q R

S 1

1C P

&

1

Q 4Q 3Q 2Q 1

Q 0

6.34 试用一片7490和一片八选一数据选择器74151实现图6.14输出波形Z 。

CP

Z

解: T i t

N S i z

B

7

49

Q 1

3R 01029192

R S S 0C P C P

Q 2Q 1Q 0 D D D D 0 1

3

412

D 74 D A A A 2

E N

Y

5

6

7

D D 1

V c c Z C P

6.35 用DFF 设计移位型序列信号发生器,要求产生的序列信号为(1 11110000…(2111100100…。

解:

(1电路图为:

1D C 1S 1D C 1S 1D C 1S 1D

C 1

S C P

Z Q 3

Q 2Q 1Q 0Q 3

C

解:状态编码表为:(其中Q

因此M=10。

6.39试写出图6.39的74194输出端的编码表及数据选择器输出端F 处的序列信号。

解: F 处的序列为:010*******。

6.40 写出图6.40中74161输出端的状态编码表及74151输出端产生的序列信号。

解: F 处的序列信号为:1111000110。

6.41 试写出图P6.41中74194输出端Q 0处的序列信号。

解:Q 0处的序列信号为:01110100110001。

6.42 用74194设计序列信号发生器产生序列信号:

(11110010,…; (2101101,…。

解:(1

(2

题6.42(2电路图 6.43 试用74161、74151及少量与非门实现如下功能:当S=0时,产生序列1011010;当

S=1时,产生序列1110100。

解:

6.44试用74161、74151及若干与非门设计一电路同时输出两个不同的序列信号:

Z 1=111100010和Z 2=101110001。

(不另加控制信号解:

题6.44电路图

6.45 设计一个小汽车尾灯控制电路。

小汽车左、右两侧各有3个尾灯,要求:

(1左转弯时,在左转弯开关控制,左侧3个灯按题图P 6.45所示周期性地亮与灭; (2右转弯时,在右转弯开关控制,左侧3个灯按题图P 6.45所示周期性地亮与灭; (3左、右两个开关都作用时,两侧的灯做同样的周期地亮与灭;

(4在制动开关(制动器作用时,6个尾灯同时亮。

若在转弯情况下制动,则3个转向尾灯正常动作,另一侧3个尾灯则均亮。

图P 6.45

解:电路图如下:

1 1 1

题6.45电路图

106682400.doc 6.46 已知由 T213 构成的电路如图 P6.46 所示,试作出 QA,QB,QC,QD,QCC 的波形。

解:题 6.46 波形图第 21 页共 21 页 21。