德州仪器面向毫微微蜂窝基站推出DSP TCI6484

Ti公司DSP技术发展历程和现状及其应用实例分析

Ti公司DSP技术发展历程和现状及其应用实例分析TI 拥有超过70 年的悠久历史,于1996 年开始致力于公司转型,专注于为信号处理市场生产半导体,并带动了无线和移动因特网市场的巨大变革。

这一转型以及随之进行的一系列收购、资产剥离和其它动作,使TI 成为当今一流的半导体公司之一。

在过去的几年中,TI 仍在不断地投资于未来、开发新技术和提高财务稳健度。

TI 已经从最近的市场低迷中成功脱身,并达到前所未有的有利位置,而且已经开始探索实时信号处理技术为电子世界带来的潜力。

随着信息能够随时随地在移动因特网中不断普及以及宽带进入家庭,TI 从信号处理不断提高的重要性中受益匪浅。

信号处理是一种技术,此技术反映了公司在数字信号处理器(DSP) 和模拟信号处理器方面的研发能力。

数字信号处理器(DSP) 和模拟信号处理器是电子业许多发展最快的细分市场的发展引擎。

DSP完美适用于任何零延迟的应用领域。

数字信号处理器(DSP) 是一种专用微处理器,能够以极高的精确度即时执行各种数学运算,这使其当之无愧地成为实时处理应用领域的理想解决方案。

TI DSP 可用于处理大规模、多类型信息,其中包括声音、影像以及视频等。

TI DSP 的应用与市场领域包括:数字蜂窝电话、无线基站、DSL 调制解调器、线缆调制解调器、因特网音频设备自1982年以来,TI成为数字信号处理(DSP)解决方案全球的领导厂商及先驱,为全球超过30,000个客户提供创新的DSP和混合信号/模拟技术,应用领域涵盖无线通讯、宽带、网络家电、数字马达控制与消费类市场。

为协助客户更快进入市场抢得先机,TI提供简单易用的开发工具及广泛的软硬件支持,并与DSP解决方案供应商组成庞大的第三方网络,帮助他们利用TI技术发展出超过1,000种产品,使服务支持更加完善。

电信是和娱乐是推动DSP创新的两次浪潮。

前者的数字化电话系统、DSL、有线Modem,802.11以及数字蜂窝电话第一次为DSP提供了前所未有的广阔舞台,后者对性能、功耗的更高要求、流媒体、以及数量庞大的消费人群则推动了DSP的进一步应用。

电压环控制策略

摘要在电力测试仪表及其校验装置中,往往要求高精度的工频恒流源,并且要求恒流源的输出幅值可调,市场上的恒流源在精度、稳定度、幅值、价格等方面无法同时满足要求,对于这一类恒流源往往需要自行设计。

本文首先给出了设计的性能参数,之后对恒流源的工作原理进行了分析,提出了高精度工频恒流源的设计方法,介绍了方案中关键电路的设计要点,详细说明了恒流源的单片机电路控制设计和软件校正的方法,最后给出试验数据和结论。

本人主要研制开发了电压信号源,提出了电压闭环控制策略。

通过电压信号控制电流源输出。

电流源最大输出功率在是300W,最大输出电流可以达到36A,输出频率可以在40至60Hz间变化。

先进的直接数字频率合成芯片(DDS)AD9851作为本文系统的信号发生芯片。

滤波电路采用了二阶有源低通滤波电路加一阶高通滤波电路的形式,有效滤除了AD9851输出信号时的高频噪音和直流分量,提高了正弦频率信号的质量。

所搭建的电路元件性能会受温度以及输出电流的影响,导致输出误差会大于0.1%。

针对这个问题,本文提出了电压环控制策略。

16位D/A芯片可以控制输出信号的增益,通过模拟乘法器对正弦波进行调制,就可以实现对正弦波幅值的控制。

最后,本人对电压电流转换电路、功率放大电路、硬件反馈电路构成的总电路进行了仿真,测了实验数据。

通过结果可以验证电流源设计的正确性,为整套装置的可行性提供了重要依据。

关键词:功率放大器,电压控制,模拟乘法器,模数转换,数模转换AbstractIn the power testing instrument and its calibration device,high precision constant current source is ofen needed .And constant current source output amplitude adjustment are also needed . Constant current source on the market can not meet the requirements of accuracy, stability, amplitude, prices, etc at the same time. This kind of constant current source is needed to be designed.This paper presents the performance parameters first ,then analyzes the working principle of the constant-current source ,puts forward the design method of the high-precision power-frequency constant-current source,introduces the key point of the significant circuit,gives the method of microcontroller circuit control design and software design ,finally gives test data and conclusionsMy work is mainly the research and development of the voltage source,and to propose closed loop voltage control strategy. The current source can output maximum power at 300W, the maximum current can reach 36A, the maximum output frequency can vary between 40 to 60Hz. In my paper,advanced direct digital synthesizer chip (DDS) AD9851 systems is the chip signal generator,its filter circuit is using the form of a second-order low-pass filter circuit and the first-order high-pass filter circuit in series, it can filter high-frequency noise and DC component effectively, and improve the quality of the sinusoidal frequency signal. The structure of circuit element properties will be affected by the temperature and output current.Thus,output signal can’t reach accuracy of 0.1%.In view of this problem, this paper introduces the voltage loop control strategy. 16-bit DA-chip can achieve the control of amplitude of sine wave. Through the modulation of the sine wave by analog multiplier , we can control the sine wave amplitude.Lastly, I operate a simulation of the total circuit which includes the voltage current converter, power amplifier, feedback hardware circuits, and gain the experimental data. The results can verify the correctness of the current source design ,and they provide an important basis for the feasibility of the entire device.Keyword:power magnifier,voltage control,analog multiplier,AD conversion,DA conversion目录摘要 (I)ABSTRACT ........................................................................................................................................... I I 1 绪论 (1)1.1恒流源的研究背景 (1)1.2恒流信号源的概念及技术指标 (1)1.3方案选择 (2)2 信号的产生 (5)2.1频率的控制 (5)2.1.1 设计基础 (5)2.1.2 频率控制的详细设计 (9)2.2AD9851输出滤波电路 (13)2.316位D/A转换芯片DAC8501 (15)2.4模拟乘法器 (17)2.4.1 模拟乘法器特性 (17)2.4.2 外部电路 (19)2.5档位切换电路 (20)3 功率放大 (22)3.1方案1 (22)3.2方案2 (22)4 信号反馈 (25)4.1信号调理电路 (25)4.2电压控制硬件工作原理 (27)4.3真有效值转换芯片的原理与应用 (27)4.3.1 AD637内部结构 (27)4.3.2 真有效值转换芯片标准电路 (28)4.3.3 高精度外部调整电路 (29)4.416位A/D采样芯片ADS8325 (30)4.5控制的策略 (33)5 软件设计 (34)5.1软件整体设计 (34)5.2中断设计 (34)6 仿真分析 (36)7 总结 (38)致谢 (39)附录 (40)附录1软件程序 (40)附录2电路总图 (53)参考文献 (54)1 绪论1.1 恒流源的研究背景恒流源是一种能向负载提供恒定电流的电源装置,输出的电流与外部影响无关,在外界电网电源产生波动和阻抗特性发生变化时仍能使输出电流保持恒定。

半导体行业深度研究:全球WiFi芯片的竞争格局及市场潜力

市场数据(人民币)市场优化平均市盈率18.90 国金半导体指数1941 沪深300指数3989 上证指数3084 深证成指11160 中小板综指11229相关报告 1.《芯片动能强,估计修正近尾声,库存风险升-《2021年&202...》,2022.5.3 2.《看好新能源、智能汽车产业链机会-创新中心双周报》,2022.4.5 3.《乌俄关系紧张,半导体材料供应风险分析-半导体材料点评》,2022.2.13 4.《EDA 工具:芯片产业基础,国产快速突围-EDA 行业深度》,2021.12.31 5.《IC 设计:看好汽车和AIoT 细分赛道投资机会-IC 设计行业深...》,2021.12.31 邵广雨 联系人 shaoguangyu @ 赵晋 分析师 SA C 执业编号:S1130520080004 zhaojin1@ 全球WiFi 芯片的竞争格局及市场潜力 投资建议 ⏹ 行业策略:我们认为WiFi 芯片应该是无线通讯芯片领域内未来最具有成长潜力的细分市场,从WiFi 4/5到WiFi 6/7,每一次WiFi 规格的升级都在不断地提升带宽及芯片价值,降低延时提高响应速度,以此满足不同的终端产品的需求。

从WiFi 4/5时代的物联网、智能家居到WiFi 6/7时代的VR/AR 、4K 超高清视频,不同终端需求对于更高性能的要求始终推动着WiFi 的升级换代。

目前WiFi 6在WiFi 芯片中的渗透率约为20%,疫情导致的需求暴涨将推动WiFi 6加速渗透,尤其是远程教学、在线协同办公、视频会议等需求的爆发,这些对高带宽、低延时有较高要求的应用场景加速了WiFi 6/7产品更新。

我们预计到2025年,WiFi 6/7产品的占比将接近50%。

从细分市场来看,WiFi 6芯片在智能手机端和家用路由器端渗透率较高,而在物联网芯片端,归因于性价比、功耗等因素,导入速度将落后两到三年。

⏹ 推荐组合: 我们首次推荐买入WiFi 芯片相关科技产业,给予买入评级。

智能融合cSoC:多通道FFT共享处理器使用FPGA纤维说明书

Application Note AC381February 20121© 2012 Microsemi Corporation SmartFusion cSoC: Multi-Channel FFT Co-Processor Using FPGA FabricTable of ContentsIntroductionThe SmartFusion ® customizable system-on-chip (cSoC) device integrates FPGA technology with a hardened ARM ® Cortex™-M3 processor based microcontroller subsystem (MSS) and programmable high-performance analog blocks built on a low power flash semiconductor process. The MSS consists of hardened blocks such as a 100 MHz ARM Cortex-M3 processor, peripheral direct memory access (PDMA), embedded nonvolatile memory (eNVM), embedded SRAM (eSRAM), embedded FlashROM (eFROM), external memory controller (EMC), Watchdog Timer, the Philips Inter-Integrated Circuit (I 2C),serial peripheral interface (SPI), 10/100 Ethernet controller, real-time counter (RTC), GPIO block, fabric interface controller (FIC), in-application programming (IAP), and analog compute engine (ACE).The SmartFusion cSoC device is a good fit for applications that require interface with many analog sensors and analog channels. SmartFusion cSoC devices have a versatile analog front-end (AFE) that complements the ARM Cortex-M3 processor based MSS and general-purpose FPGA fabric. The SmartFusion AFE includes three 12-bit successive approximation register (SAR) ADCs, one first order sigma-delta DAC (SDD) per ADC, high performance signal conditioning blocks, and comparators. The SmartFusion cSoCs have a sophisticated controller for the AFE called the ACE. The ACE configures and sequences all the analog functions using the sample sequencing engine (SSE) and post-processes the results using the post processing engine (PPE) and handles without intervention of Cortex-M3 processor.Refer to the SmartFusion Programmable Analog User’s Guide for more details.This application note describes the capability of SmartFusion cSoC devices to compute the Fast Fourier Transform (FFT) in real time. The Multi Channel FFT example design can be used in medical applications, sensor network applications, multi channel audio Spectrum analyzers, Smart Metering, and sensing applications (such as vibration analysis).This example design uses the Cortex-M3 processor in the SmartFusion MSS as a master and the FFT processor in the FPGA fabric as a slave. All three of the SmartFusion cSoC A2F500’s ADCs are used for data acquisition. The example design uses Microsemi’s CoreFFT IP and the advanced peripheral bus interface (CoreAPB3). A custom-made APB3 interface has been developed to connect CoreFFT with the MSS via CoreAPB3. The Cortex-M3 processor uses the PDMA controller in the MSS for the data transfer and thus helps to free up the Cortex-M3 processor instruction bandwidth.A basic understanding of the SmartFusion design flow is assumed. Refer to Using UART with SmartFusion - Microsemi Libero ® SoC and SoftConsole Flow Tutorial to understand the SmartFusion design flow.Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1Design Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2Design Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2Implementing Multi Channel FFT on EVAL KIT BOARD . . . . . . . . . . . . . . . . . . . . . . . . . 7Running the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8Conclusion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9Appendix A – Design Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10SmartFusion cSoC: Multi-Channel FFT Co-Processor Using FPGA Fabric2Design OverviewThis design example demonstrates the capability of the SmartFusion cSoC device to compute the FFT for multiple data channels. The FFT computation is a complex task that utilizes extensive logic resources and computation time. In general, for N number of channels, N number of FFT IP’s are needed to be instantiated, which in turn utilize more logic resources on the FPGA. A way to avoid this limitation is to use the same FFT logic for multiple input channels.This design illustrates the implementation of a Multichannel FFT to process multiple data channels through a single FFT and store FFT points in a buffer. The FFT computes the input data read from each channel and stores the N-point result in the respective channel’s allocated buffer. The channel multiplexing is done once each channel buffer has been loaded with the FFT length.Computing frequency components for a real time data of six channels is described in this application note. For sampling the input signals the AFE is used and the complex FFT computation is implemented in the fabric of the SmartFusion cSoC device. The Cortex-M3 processor in the MSS of the SmartFusion cSoC handles the buffer management and channel muxing.Figure 1 depicts the block diagram of six channel FFT co-processor in FPGA fabric.Design DescriptionThe design uses CoreFFT for computing the FFT results. You can download the core generator for CoreFFT at /soc/portal/default.aspx?r=4&p=m=624,ev=60.The design example uses a 512-point and 16-bit FFT. A custom-made APB3 interface has been developed to connect CoreFFT IP with the MSS’s FIC. The CoreFFT output data is stored in a 512x32FIFO within the fabric. The FIFO status signals are given in Table 1 on page 3. The status signals indicate that FFT is ready to receive data and data is available in the output of FIFO. These status signals are mapped to the GPIOs in the MSS. The Cortex-M3 processor can read the GPIOs to handle flow control in the data transfer process from the MSS to CoreFFT.Figure 1 • Multi Channel FFT Block DiagramDesign Description3Figure 2 shows the block diagram of logic in the fabric with custom-made APB3 bus.The data valid signal (ifiD_valid) is generated in custom logic whenever the master needs to write data into the input buffer of the FFT to process through the APB3 interface. The FFT_IP_RDY signal indicates the status of the input buffer of the FFT. If the input buffer is full, the FFT_IP_RDY goes low. The master can read the FFT_IP_RDY signal to get the FFT input buffer status. The FFT generates the processed data with a data valid signal (ifoY_valid). The processed data is stored in the FIFO. When FIFO is not ready to receive output data, it can stop the data fetching from the FFT by pulling down the ifiRead_y signal. The status signal FFT_OP_RDY is used to indicate to the master that processed data is available in the FIFO. FFT_OP_RDY goes High whenever processed data is available in the FFT output buffer.The master can use AEMPTY_OUT or EMPTY_OUT to determine whether the FIFO is empty and all the processed data has been read. Refer to the CoreFFT Handbook for more details on architecture and interface signal descriptions.Three ADCs are configured to have two channels, each channel with 100 ksps sampling rate. The external memory is used for input and output buffers. For each channel, one input buffer having length double to the length of FFT i.e. 1024 words and one output buffer having length equal to the length of FFT i.e. 512 words are used. After each channel's input buffer has 512 points required for the full length of the FFT, each channel, one after the other, streams its points from the FIFO through the FFT. During the FFT computational period, the sampled data values of each channel are stored in the second half of the input buffer. Once the FFT computations for the First half of input buffer completes then the points in the second half of the input buffer will be streamed to FFT. This operation utilizes a ping-pong method. The Cortex-M3 processor is used for data management, that is, buffering the sampled points and data routing or muxing of these values to the FFT computation block. Sampling of the real time data is done by the ACE. The PDMA handles the data transfer between the external SRAM (eSRAM) buffers and CoreFFT logic in FPGA fabric.Figure 2 • CoreFFT with APB Slave InterfaceTable 1 • FIFO Status Signals with DescriptionsSignalDescription FFT_IP_RDYFFT is ready to receive the Input from the master processor FFT_OP_RDYProcessed data is ready in output buffer of FFT AEMPTY_OUTOutput FIFO is almost empty EMPTY_OUT Output FIFO is emptySmartFusion cSoC: Multi-Channel FFT Co-Processor Using FPGA Fabric4Figure 3 shows the implementation of multi channel FFT on the SmartFusion cSoC device.Hardware ImplementationThe MSS is configured with an FIC, clock conditioning circuit (CCC), GPIOs, EMC and a UART. The CCC generates 80 MHz clock, which acts as the clock source. The FIC is configured to use a master interface with an AMBA APB3 interface. Four GPIOs in the MSS are configured as inputs that are used to handle flow control in data transfer from MSS to FFT coprocessor. The EMC is configured for Region 0as Asynchronous RAM and port size as half word. The UART_0 is configured for printing the FFT values to the PC though a serial terminal emulation program.ADC0, ADC1, and ADC2 are configured with 12-bit resolution, two channels and the sampling rate is set to approximately 100 KHz. Figure 4 on page 5 shows the ACE configuration window.Figure 3 • Implementation of Multi Channel FFT on the SmartFusion cSoCDesign Description5The APB wrapper logic is implemented on the top of CoreFFT and connected to CoreAPB3. A FIFO of size 512*32 is used to connect to CoreFFT output.CoreAPB3 acts as a bridge between the MSS and the FFT coprocessor block. It provides an advanced microcontroller bus architecture (AMBA3) advanced peripheral bus (APB3) fabric supporting up to 16APB slaves. This design example uses one slave slot (Slot 0) to interface with the FFT coprocessor block and is configured with direct addressing mode. Refer to the CoreAPB3 Handbook for more details on CoreAPB3 IP .For more details on how to connect FPGA logic MSS, refer to the Connecting User Logic to the SmartFusion Microcontroller Subsystem application note.The logic in the FPGA fabric consumes 18 RAM blocks out of 24. We cannot use eSRAM blocks for implementing CoreFFT as the transactions between these SRAM blocks and FFT logic are very high and are time critical.Figure 5 on page 6 illustrates the multi channel FFT example design in the SmartDesign.Figure 4 • Configure ACESmartFusion cSoC: Multi-Channel FFT Co-Processor Using FPGA Fabric6Table 2 summarizes the logic resource utilization of the design on the A2F500M3F device.Software ImplementationThe Cortex-M3 processor continuously reads the values from ACE and stores the values into the input buffers. If the first 512 points are filled then the processor initiates the FFT process. In the FFT process,the input buffers are streamed one after other to the CoreFFT with the help of PDMA. Using another channel of PDMA the output of FFT is moved to the corresponding channel output buffers.During the FFT process the Cortex-M3 processor stores the sampled values into the second half of the input buffers. Once the FFT process completes the first half of input buffer, then the second half of the input buffer are streamed to CoreFFT.Figure 5 • SmartDesign Implementation of Multi Channel FFTTable 2 • Logic Utilization of the Design on A2F500M3FCoreFFTOther Logic in Fabric Total Ram Blocks14418 (75%)Tiles 78424718313 (72.1%)Implementing Multi Channel FFT on EVAL KIT BOARD7The CALL_FFT(int *) application programmable interface (API) initiates the PDMA to transfer input buffer data to the FFT in the fabric. Before initiating PDMA it checks for FFT whether or not it is ready to read the data. The CALL_FFT(int *) API also checks if the output FIFO is empty so that all the FFT out values have been already read. When the input buffer has points equal to the full length of FFT, then it will be called.The Read_FFT() API initiates the PDMA for reading the FFT output values from FIFO in fabric to the corresponding output buffer. After reading all the values it calls the CALL_FFT() API with the next channel buffer to compute the FFT for next channel. This is done for all channels. After completion of FFT computation for all channels, if the continuous variable is not defined, it will print the FFT output values on the serial terminal. When FFT_OP_READY interrupt occurs then this API will be called.The GPIO1_IRQHandler() interrupt service routine occurs on the positive edge of FFT_OP_READY signal. It calls Read_FFT() API. This interrupt mechanism is used to read the sample values continuously while computing the FFT.If continuous variable is defined, then the FFT is computed without any loss of data samples. If #define continuous line is commented then after every completion of FFT computation of all channels the FFT output is printed on serial terminal. The printed values are in the form of complex numbers.The ping-pong mechanism is used for input data buffer to store the samples continuously. For each channel the input buffer length is double of the full FFT length. While computing the FFT for the first half of the buffer, the new sample values are stored in the second half of the input buffer and while computing the FFT for second half of buffer, the new sample values are stored in first half of the input buffer.Customizing the Number of ChannelsYou can change the design depending on your requirement. Configure the ADC (Figure 4 on page 5)with the required number of channels and required sampling rate. In SoftConsole project change the parameter value NUM_CHANNELS according to the ADC configuration. Edit the main code for reading ADCs data into buffers according to ACE configuration.Throughput CalculationsThe actual time to get 512 samples with 100 ksps is 5.12 ms. Each channel is configured to 100 ksps, so for every 5.12 ms we will have 512 samples in the input buffers.The actual time taken to compute the FFT for each channel is the sum of time taken to transfer 512points to CoreFFT, FFT computation time, and time to read FFT output to the output buffer.•Total time for computing FFT = (time taken to receive 512 data + computational latency for 512points + time taken to store 512 data) = 512*5 + 23292 + 512*5 =28412 clks •Time to compute FFT for 6 channels = 28412*6 = 170472 clksTime to compute FFT for six channels is 2.1309 ms (If CLK is 80 MHz). It is less than half the sample rate of 5.12 ms.If only one channel is configured with maximum sampling rate (600 ksps) then time to get 512 samples with 600 ksps is 0.853 ms. Time to compute FFT for these 512 samples is 0.355 ms. If you configure three ADCs with maximum sampling rate (1800 ksps) then time to compute the FFT for these three channels will be 1.065 ms which is higher than the sampling time. In this there is a loss of some samples.The design works fine up to 1440 ksps.Implementing Multi Channel FFT on EVAL KIT BOARDTo implement the design on the SmartFusion Evaluation Kit Board the FFT must be 256 point and 8 bit because the A2F200 device has less RAM blocks and logic cells. The ADC channels must be selected for only ADC0 and ADC1. Figure 6 on page 8 shows the implementation of multi channel FFT on the SmartFusion cSoC (A2F200M3F) device.SmartFusion cSoC: Multi-Channel FFT Co-Processor Using FPGA Fabric8Table 3 summarizes the logic resource utilization of the design with 256 points 8-bit FFT on A2F200M3F device.Running the DesignProgram the SmartFusion Evaluation Kit Board or the SmartFusion Development Kit Board with the generated or provided *.stp file (refer to "Appendix A – Design Files" on page 10) using FlashPro and then power cycle the board.For computing continuous FFT values for the all six signals sampled through the ADCs, uncomment the line #define continuous in the main program. The FFT output values are stored in the rdata buffer. This buffer is updated for every computation of FFT.For printing the FFT values on serial terminal (HyperTerminal or PuTTy), comment the line #define continuous in the main program.Figure 6 • Implementation of Multi Channel FFT on the SmartFusion Evaluation Kit BoardTable 3 • Logic Utilization of the Design on A2F200M3F DeviceCoreFFTOther Logic in Fabric Total Ram Blocks718 (100%)Tiles 3201853286 (66%)Conclusion9Connect the analog inputs to the SmartFusion Kit Board with the information provided in Table 4.Invoke the SoftConsole IDE, by clicking on Write Application code under Develop Firmware in Libero ®System-on-Chip (SoC) project (refer to "Appendix A – Design Files") and launch the debugger. Start HyperTerminal or PuTTY with a baud rate of 57600, 8 data bits, 1 stop bit, no parity, and no flow control.If your PC does not have the HyperTerminal program, use any free serial terminal emulation program such as PuTTY or Tera Term. Refer to the Configuring Serial Terminal Emulation Programs Tutorial for configuring the HyperTerminal, Tera Term, or PuTTY .ConclusionThis application note describes the capability of the SmartFusion cSoC devices to compute the multi channel FFT. The Cortex-M3 processor, AFE, and FPGA fabric together gives a single chip solution for real time multi channel FFT system. This design example also shows the 6-channel data acquisition system.Table 4 • SettingsChannelEvaluation Kit Development Kit Channel 173 of J21 (signal header)ADC0 of JP4Channel 274 of J21 (signal header)ADC1 of JP4Channel 377 of J21 (signal header)77 of J21 (signal header)Channel 478 of J21 (signal header)78 of J21 (signal header)Channel 585 of J21 (signal header)Channel 686 of J21 (signal header)Figure 7 • FFT Output Data for 1 kHz Sinusoidal Signal on PUTTYSmartFusion cSoC: Multi-Channel FFT Co-Processor Using FPGA Fabric10Appendix A – Design FilesThe Design files are available for download on the Microsemi SoC Product Groups website:/soc/download/rsc/?f=A2F_AC381_DF.The design zip file consists of Libero SoC projects and programming file (*.stp) for A2F200 and A2F500.Refer to the Readme.txt file included in the design file for directory structure and description.51900249-0/02.12© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at .Microsemi Corporate HeadquartersOne Enterprise, Aliso Viejo CA 92656 USAWithin the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996。

TCI6484:单芯片DSP

的 S C( L 单级单元) ML 多级单元) AN 『存 。 和 C( N D^ J

QV GA 色 彩 显 示

GB re R 1 容 1 G p S T 并 支 持 高 达 10 / 屏等 。所 有这些特征 都为手机用 户带来 了全新 的体验并强 Di r S 兼 v . b s AAl 5 , 5 MB

台 的 推 出 , 旨在 降 低 智 能 手 机 的 成 本 ,推 动 智 能 手 机 的进

‘

步普及 。 Vn o … 的 开 发丛 于 A M9 6 J 拥 有 多 种 多媒 体 特 in 一 R 2E,

如具有 mp g / 2 3 e 4H. 硬件 的多媒体数字信 号编解 码器 、 6 T 68 CI4 4支 持 3 Mb s的 符 号 速 率 处 理 ,能 满 足 各 种 性 , 4 p

而优化 的高性能加速器与外设接 口。

改进 ,叮确保在 使 多级 N N A D闪存时发生 的误码率 处 丁

另外还增 加了 自动决于 哪用存储 合适的可靠性 水平 。 C

暖甄矗踊 容量以及快速 访问存储数 据的能力 。T 6 8 CI4 4实现 了高达 取数据时 能 自动纠正位错误 。

借助 双倍数据速率 ( R ) DD 2 存储 器接 口, 新产品访 问外

V 0 1)1 : 1 n wsMo i d e操作系 统的开放 式 部存储数 据的速度 与前代芯片相 比提 高 了 2 %。更快存取 (C 8 8  ̄ 基于微 软 Wi o bl 5 in 一 Wi。 速度有利 于降低时延 。 对数据处理强度较 大的应用 ( 如实时 移 动平 台 Vn o …一 n 新 的应 用处 理器和 开放式移动平 会 议与流 媒体等) ,时 延 问题 会 严 重 影 响 使 用 效 果 。 T 68 CI4 4不仅 降低 了时延 ,还支 持 3 Mb s的符 号速 率处 4 p 理, 是实现更高密度与更低成 本基站 的理想平 台。

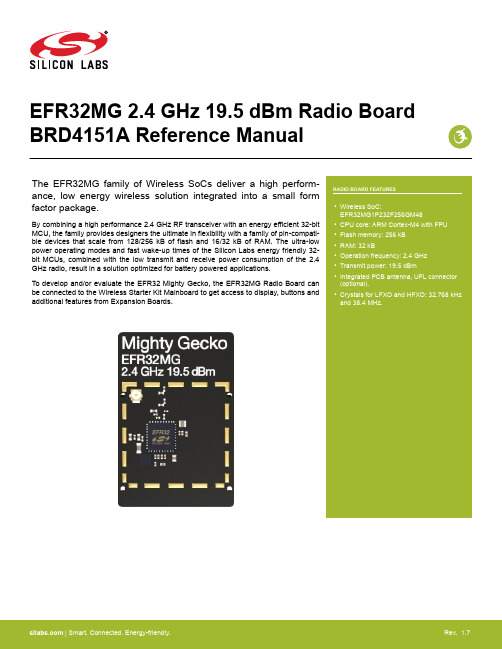

Silicon Labs EFR32MG 2.4 GHz 19.5 dBm 无线模组板参考手册说明书

EFR32MG 2.4 GHz 19.5 dBm Radio BoardBRD4151A Reference Manualance, low energy wireless solution integrated into a small formfactor package.By combining a high performance 2.4 GHz RF transceiver with an energy efficient 32-bitMCU, the family provides designers the ultimate in flexibility with a family of pin-compati-ble devices that scale from 128/256 kB of flash and 16/32 kB of RAM. The ultra-lowpower operating modes and fast wake-up times of the Silicon Labs energy friendly 32-bit MCUs, combined with the low transmit and receive power consumption of the 2.4GHz radio, result in a solution optimized for battery powered applications.To develop and/or evaluate the EFR32 Mighty Gecko, the EFR32MG Radio Board canbe connected to the Wireless Starter Kit Mainboard to get access to display, buttons andadditional features from Expansion Boards.Introduction 1. IntroductionThe EFR32 Mighty Gecko Radio Boards provide a development platform (together with the Wireless Starter Kit Mainboard) for the Silicon Labs EFR32 Mighty Gecko Wireless System on Chips and serve as reference designs for the matching network of the RF inter-face.The BRD4151A Radio Board is designed to operate in the 2400-2483.5 MHz band with the RF matching network optimized to operate with 19.5 dBm output power.To develop and/or evaluate the EFR32 Mighty Gecko, the BRD4151A Radio Board can be connected to the Wireless Starter Kit Main-board to get access to display, buttons and additional features from Expansion Boards and also to evaluate the performance of the RF interface.2. Radio Board Connector2.1 IntroductionThe board-to-board connector scheme allows access to all EFR32MG1 GPIO pins as well as the RESETn signal. For more information on the functions of the available pin functions, see the EFR32MG1 data sheet.2.2 Radio Board Connector Pin AssociationsThe figure below shows the pin mapping on the connector to the radio pins and their function on the Wireless Starter Kit Mainboard.GND F9 / PA3 / VCOM.#RTS_#CS 3v3UIF_BUTTON1 / PF7 / P36P200Upper RowNC / P38NC / P40NC / P42NC / P44DEBUG.TMS_SWDIO / PF1 / F0DISP_ENABLE / PD15 / F14UIF_BUTTON0 / PF6 / F12DISP_EXTCOMIN / PD13 / F10VCOM.#CTS_SCLK / PA2 / F8#RESET / F4DEBUG.TDO_SWO / PF2 / F2DISP_SI / PC6 / F16VCOM.TX_MOSI / PA0 / F6PTI.DATA / PB12 / F20DISP_EXTCOMIN / PD13 / F18USB_VBUS5VBoard ID SCLGND Board ID SDAUSB_VREG F7 / PA1 / VCOM.RX_MISO F5 / PA5 / VCOM_ENABLE F3 / PF3 / DEBUG.TDI F1 / PF0 / DEBUG.TCK_SWCLK P45 / NC P43 / NCP41 / NCP39 / NCP37 / High / SENSOR_ENABLEF11 / PF5 / UIF_LED1F13 / PF7 / UIF_BUTTON1F15 / PC8 / DISP_SCLK F17 / PD14 / DISP_SCS F19 / PB13 / PTI.SYNC F21 / PB11 / PTI.CLK GNDVMCU_INVCOM.#CTS_SCLK / PA2 / P0P201Lower RowVCOM.#RTS_#CS / PA3 / P2PD10 / P4PD11 / P6GND VRF_INP35 / PD15 / DISP_ENABLE P7 / PC9P5 / PC8 / DISP_SCLK P3 / PC7P1 / PC6 / DISP_SI P33 / PD14 / DISP_SCSP31 / PD13 / DISP_EXTCOMIN P29 / NCP27 / NC P25 / NC P23 / NC P21 / NC P19 / NC P17 / NC P15 / NC P13 / PC11P11 / PA1 / VCOM.RX_MISO P9 / PA0 / VCOM.TX_MOSI UIF_BUTTON0 / PF6 / P34UIF_LED1 / PF5 / P32UIF_LED0 / PF4 / P30DEBUG.TDO_SWO / PF2 / P28DEBUG.TMS_SWDIO / PF1 / P26DEBUG.TCK_SWCLK / PF0 / P24PTI.SYNC / PB13 / P22PTI.DATA / PB12 / P20PTI.CLK / PB11 / P18VCOM_ENABLE / PA5 / P16PA4 / P14PC10 / P12DEBUG.TDI / PF3 / P10PD12 / P8Figure 2.1. BRD4151A Radio Board Connector Pin MappingRadio Board Connector3. Radio Board Block Summary3.1 IntroductionThis section gives a short introduction to the blocks of the BRD4151A Radio Board.3.2 Radio Board Block DiagramThe block diagram of the EFR32MG Radio Board is shown in the figure below.Figure 3.1. BRD4151A Block Diagram3.3 Radio Board Block Description3.3.1 Wireless MCUThe BRD4151A EFR32 Mighty Gecko Radio Board incorporates an EFR32MG1P232F256GM48 Wireless System on Chip featuring 32-bit Cortex-M4 with FPU core, 256 kB of flash memory and 32 kB of RAM and a 2.4 GHz band transceiver with output power up to 19.5 dBm. For additional information on the EFR32MG1P232F256GM48, refer to the EFR32MG1 Data Sheet.3.3.2 LF Crystal Oscillator (LFXO)The BRD4151A Radio Board has a 32.768 kHz crystal mounted.3.3.3 HF Crystal Oscillator (HFXO)The BRD4151A Radio Board has a 38.4 MHz crystal mounted.3.3.4 Matching Network for 2.4 GHzThe BRD4151A Radio Board incorporates a 2.4 GHz matching network which connects the 2.4 GHz TRX pin of the EFR32MG1 to the one on-board printed Inverted-F antenna. The component values were optimized for the 2.4 GHz band RF performace and current con-sumption with 19.5 dBm output power.For detailed description of the matching network, see Chapter 4.2.1 Description of the 2.4 GHz RF Matching.| Smart. Connected. Energy-friendly.Rev. 1.7 | 33.3.5 Inverted-F AntennaThe BRD4151A Radio Board includes a printed Inverted-F antenna (IFA) tuned to have close to 50 Ohm impedance at the 2.4 GHz band.For detailed description of the antenna see Chapter 4.5 Inverted-F Antenna.3.3.6 UFL ConnectorTo be able to perform conducted measurements, Silicon Labs added an UFL connector to the Radio Board. The connector allows an external 50 Ohm cable or antenna to be connected during design verification or testing.Note: By default the output of the matching network is connected to the printed Inverted-F antenna by a series component. It can be connected to the UFL connector as well through a series 0 Ohm resistor which is not mounted by default. For conducted measurements through the UFL connector the series component to the antenna should be removed and the 0 Ohm resistor should be mounted (see Chapter 4.2 Schematic of the RF Matching Network for further details).3.3.7 Radio Board ConnectorsTwo dual-row, 0.05” pitch polarized connectors make up the EFR32MG Radio Board interface to the Wireless Starter Kit Mainboard. For more information on the pin mapping between the EFR32MG1P232F256GM48 and the Radio Board Connector, refer to Chapter 2.2 Radio Board Connector Pin Associations.4. RF Section4.1 IntroductionThis section gives a short introduction to the RF section of the BRD4151A.4.2 Schematic of the RF Matching NetworkThe schematic of the RF section of the BRD4151A Radio Board is shown in the following figure.U1BPath Inverted-F Antenna2.4 GHz Matching Figure 4.1. Schematic of the RF Section of the BRD4151A4.2.1 Description of the 2.4 GHz RF MatchingThe 2.4 GHz matching connects the 2G4RF_IOP pin to the on-board printed Inverted-F Antenna. The 2G4RF_ION pin is connected to ground. For higher output powers (13 dBm and above) beside the impedance matching circuitry it is recommended to use additional harmonic filtering as well at the RF output. The targeted output power of the BRD4151A board is 19.5 dBm. As a result, the RF output of the IC is connected to the antenna through a four-element impedance matching and harmonic filter circuitry.For conducted measurements the output of the matching network can also be connected to the UFL connector by relocating the series R1 resistor (0 Ohm) to the R2 resistor position between the output of the matching and the UFL connector.4.3 RF Section Power SupplyOn the BRD4151A Radio Board the supply pin of the RF Analog Power (RFVDD) is connected directly ot the output of the on-chip DC-DC converter while the supply for the 2.4 GHz PA (PAVDD) is provided directly by the mainboard. This way, by default, the DC-DC converter provides 1.8 V for the RF analog section, the mainboard provides 3.3 V for the PA (for details, see the schematic of the BRD4151A).4.4 Bill of Materials for the 2.4 GHz MatchingThe Bill of Materials of the 2.4 GHz matching network of the BRD4151A Radio Board is shown in the following table.Table 4.1. Bill of Materials for the BRD4151A 2.4 GHz 19.5 dBm RF Matching Network | Smart. Connected. Energy-friendly.Rev. 1.7 | 54.5 Inverted-F AntennaThe BRD4151A Radio Board includes an on-board printed Inverted-F Antenna tuned for the 2.4 GHz band. Due to the design restric-tions of the Radio Board the input of the antenna and the output of the matching network can't be placed directly next to each other. Therefore, a 50 Ohm transmission line was necessary to connect them. The resulting impedance and reflection measured at the output of the matcing network are shown in the following figure. As it can be observed the impedance is close to 50 Ohm (the reflection is better than -10 dB) for the entire 2.4 GHz band.Figure 4.2. Impedance and Reflection of the Inverted-F Antenna of the BRD4151A| Smart. Connected. Energy-friendly.Rev. 1.7 | 65. Mechanical DetailsThe BRD4151A EFR32 Mighty Gecko Radio Board is illustrated in the figures below.45 mmFigure 5.1. BRD4151A Top View5 mm ConnectorConnectorFigure 5.2. BRD4151A Bottom ViewMechanical DetailsRev. 1.7 | 7EMC Compliance 6. EMC Compliance6.1 IntroductionCompliance of the fundamental and harmonic levels is tested against the following standards:• 2.4 GHz:•ETSI EN 300-328•FCC 15.2476.2 EMC Regulations for 2.4 GHz6.2.1 ETSI EN 300-328 Emission Limits for the 2400-2483.5 MHz BandBased on ETSI EN 300-328 the allowed maximum fundamental power for the 2400-2483.5 MHz band is 20 dBm EIRP. For the unwan-ted emissions in the 1 GHz to 12.75 GHz domain the specified limit is -30 dBm EIRP.6.2.2 FCC15.247 Emission Limits for the 2400-2483.5 MHz BandFCC 15.247 allows conducted output power up to 1 Watt (30 dBm) in the 2400-2483.5 MHz band. For spurious emmissions the limit is -20 dBc based on either conducted or radiated measurement, if the emission is not in a restricted band. The restricted bands are speci-fied in FCC 15.205. In these bands the spurious emission levels must meet the levels set out in FCC 15.209. In the range from 960 MHz to the frequency of the 5th harmonic it is defined as 0.5 mV/m at 3 m distance (equals to -41.2 dBm in EIRP).Additionally, for spurious frequencies above 1 GHz, FCC 15.35 allows duty-cycle relaxation to the regulatory limits. For the EmberZNet PRO the relaxation is 3.6 dB. Therefore, the -41.2 dBm limit can be modified to -37.6 dBm.If operating in the 2400-2483.5 MHz band the 2nd, 3rd and 5th harmonics can fall into restricted bands. As a result, for those the -37.6 dBm limit should be applied. For the 4th harmonic the -20 dBc limit should be applied.6.2.3 Applied Emission Limits for the 2.4 GHz BandThe above ETSI limits are applied both for conducted and radiated measurements.The FCC restricted band limits are radiated limits only. Besides that, Silicon Labs applies those to the conducted spectrum i.e., it is assumed that, in case of a custom board, an antenna is used which has 0 dB gain at the fundamental and the harmonic frequencies. In that theoretical case, based on the conducted measurement, the compliance with the radiated limits can be estimated.The overall applied limits are shown in the table below.Table 6.1. Applied Limits for Spurious Emissions for the 2.4 GHz Band | Smart. Connected. Energy-friendly.Rev. 1.7 | 87. RF Performance7.1 Conducted Power MeasurementsDuring measurements, the EFR32MG Radio Board was attached to a Wireless Starter Kit Mainboard which was supplied by USB. The voltage supply for the Radio Board was 3.3 V.7.1.1 Conducted Measurements in the 2.4 GHz bandThe BRD4151A board was connected directly to a Spectrum Analyzer through its UFL connector (the R1 resistor (0 Ohm) was removed and a 0 Ohm resistor was soldered to the R2 resistor position). During measurements, the voltage supply for the board was 3.3 V provi-ded by the mainboard. The supply for the radio (RFVDD) was 1.8 V provided by the on-chip DC-DC converter, the supply for the power amplifier (PAVDD) was 3.3 V (for details, see the schematic of the BRD4151A). The transceiver was operated in continuous carrier transmission mode. The output power of the radio was set to the maximum level.The typical output spectrum is shown in the following figure.Figure 7.1. Typical Output Spectrum of the BRD4151AAs it can be observed, the fundamental is slightly lower than 19.5 dBm and the strongest unwanted emission is the double-frequency harmonic and it is under the -37.6 dBm applied limit.Note: The conducted measurement is performed by connecting the on-board UFL connector to a Spectrum Analyzer through an SMA Conversion Adapter (P/N: HRMJ-U.FLP(40)). This connection itself introduces approximately a 0.3 dB insertion loss.RF PerformanceRev. 1.7 | 97.2 Radiated Power MeasurementsDuring measurements, the EFR32MG Radio Board was attached to a Wireless Starter Kit Mainboard which was supplied by USB. The voltage supply for the Radio Board was 3.3 V. The radiated power was measured in an antenna chamber by rotating the DUT 360degrees with horizontal and vertical reference antenna polarizations in the XY , XZ and YZ cuts. The measurement axes are shown inthe figure below.Figure 7.2. DUT: Radio Board with the Wireless Starter Kit Mainboard (Illustration)Note: The radiated measurement results presented in this document were recorded in an unlicensed antenna chamber. Also the radi-ated power levels may change depending on the actual application (PCB size, used antenna, and so on). Therefore, the absolute levels and margins of the final application are recommended to be verified in a licensed EMC testhouse.7.2.1 Radiated Measurements in the 2.4 GHz bandFor the transmitter antenna, the on-board printed Inverted-F antenna of the BRD4151A board was used (the R1 resistor (0 Ohm) was mounted). During the measurements the board was attached to a Wireless Starter Kit Mainboard (BRD4001 (Rev. A02) ) which was supplied through USB. During measurements, the voltage supply for the board was 3.3 V provided by the mainboard. The supply for the radio (RFVDD) was 1.8 V provided by the on-chip DC-DC converter, the supply for the power amplifier (PAVDD) was 3.3 V (for details, see the schematic of the BRD4151A). The transceiver was operated in continuous carrier transmission mode. The output power of the radio was set to the maximum level.The results are shown in the table below.Table 7.1. Maximums of the Measured Radiated Powers of BRD4151AAs it can be observed, thanks to the high gain of the Inverted-F antenna, the level of the fundamental is higher than 19.5 dBm. The strongest harmonic is the double-frequency one but its level is under -45 dBm.RF PerformanceEMC Compliance Recommendations 8. EMC Compliance Recommendations8.1 Recommendations for 2.4 GHz ETSI EN 300-328 complianceAs it was shown in the previous chapter, the radiated power of the fundamental of the BRD4151A EFR32 Mighty Gecko Radio Board complies with the 20 dBm limit of the ETSI EN 300-328 in case of the conducted measurement but due to the high antenna gain the radiated power is higher than the limit by 2 dB. In order to comply, the output power should be reduced (with different antennas, de-pending on the gain of the used antenna, the necessary reduction can be different). The harmonic emissions are under the -30 dBm limit. Although the BRD4151A Radio Board has an option for mounting a shielding can, that is not required for the compliance.8.2 Recommendations for 2.4 GHz FCC 15.247 complianceAs it was shown in the previous chapter, the radiated power of the fundamental of the BRD4151A EFR32 Mighty Gecko Radio Board complies with the 30 dBm limit of the FCC 15.247. The harmonic emissions are under the -37.6 dBm applied limit both in case of the conducted and the radiated measurements. Although the BRD4151A Radio Board has an option for mounting a shielding can, that is not required for the compliance.Board Revisions 9. Board RevisionsTable 9.1. BRD4151A Radio Board RevisionsNote: The silkscreen marking on the board (e.g., PCBxxxx A00) denotes the revision of the PCB. The revision of the actual Radio Board can be read from the on-board EEPROM.Errata 10. ErrataTable 10.1. BRD4151A Radio Board ErrataDocument Revision History 11. Document Revision HistoryRevision 1.72016-11-20Minor editorial updates.Revision 1.62016-10-31Corrected error in radio board connector pinout diagram.Revision 1.52016-05-24Updating Board Revisions content. Fixing Errata description.Revision 1.42016-05-05Adding Introduction chapter; moving SoC Description chapter (short ver.) to Block Description chapter. Minor improvements.Revision 1.32016-02-11Addign RF Section Power Supply chapter. Minor improvements.Revision 1.22016-01-28Fixing image render problem.Revision 1.12015-25-25Updating Inverted-F Antenna Chapter and radiated measurement results based on board revision B02.Revision 1.02015-11-27Initial release.Table of Contents1. Introduction (1)2. Radio Board Connector (2)2.1 Introduction (2)2.2 Radio Board Connector Pin Associations (2)3. Radio Board Block Summary (3)3.1 Introduction (3)3.2 Radio Board Block Diagram (3)3.3 Radio Board Block Description (3)3.3.1 Wireless MCU (3)3.3.2 LF Crystal Oscillator (LFXO) (3)3.3.3 HF Crystal Oscillator (HFXO) (3)3.3.4 Matching Network for 2.4 GHz (3)3.3.5 Inverted-F Antenna (4)3.3.6 UFL Connector (4)3.3.7 Radio Board Connectors (4)4. RF Section (5)4.1 Introduction (5)4.2 Schematic of the RF Matching Network (5)4.2.1 Description of the 2.4 GHz RF Matching (5)4.3 RF Section Power Supply (5)4.4 Bill of Materials for the 2.4 GHz Matching (5)4.5 Inverted-F Antenna (6)5. Mechanical Details (7)6. EMC Compliance (8)6.1 Introduction (8)6.2 EMC Regulations for 2.4 GHz (8)6.2.1 ETSI EN 300-328 Emission Limits for the 2400-2483.5 MHz Band (8)6.2.2 FCC15.247 Emission Limits for the 2400-2483.5 MHz Band (8)6.2.3 Applied Emission Limits for the 2.4 GHz Band (8)7. RF Performance (9)7.1 Conducted Power Measurements (9)7.1.1 Conducted Measurements in the 2.4 GHz band (9)7.2 Radiated Power Measurements (10)7.2.1 Radiated Measurements in the 2.4 GHz band (10)8. EMC Compliance Recommendations (11)8.1 Recommendations for 2.4 GHz ETSI EN 300-328 compliance (11)8.2 Recommendations for 2.4 GHz FCC 15.247 compliance (11)9. Board Revisions (12)10. Errata (13)11. Document Revision History (14)Table of Contents (15)Silicon Laboratories Inc.400 West Cesar Chavez Austin, TX 78701USASimplicity StudioOne-click access to MCU and wireless tools, documentation, software, source code libraries & more. Available for Windows, Mac and Linux!IoT Portfolio /IoTSW/HW/simplicityQuality/qualitySupport and CommunityDisclaimerSilicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.Trademark InformationSilicon Laboratories Inc.® , Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.。

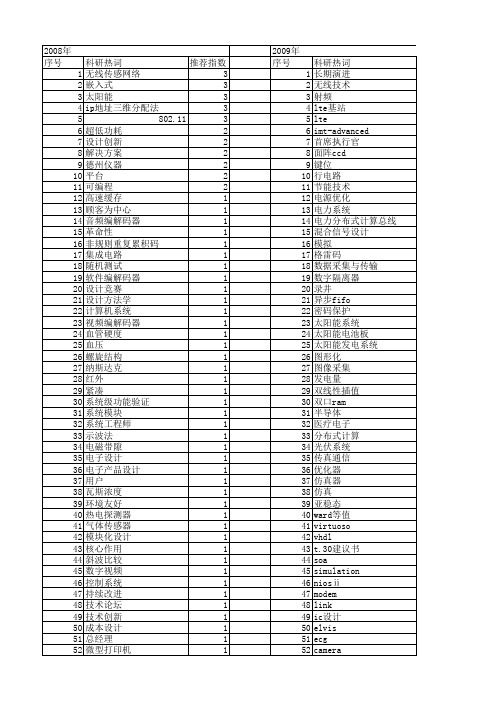

【电子技术应用】_设计创新_期刊发文热词逐年推荐_20140725

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

53 cadence设计系统公司

107 avc 108 altera公司

1 1

推荐指数 2 2 2 2 2 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

开拓创新 开发人员 开发 度分布 差分进化 局域谐振 媒体处理器 奥林匹克竞赛 套装软件 套件 多agent系统 基本理念 可配置性 可持续性 变电站自动化系统 原材料 印刷电路板 卡尔 半导体器件 医疗产品 创新设计 创新 分布式 光学辐射 便携设备 低密度奇偶校验码 低功耗设计技术 产品开发 产品外形 交指结构 亚太区 中国 ⅱ world sopc soc quicklogic公司 proⅱ processor polar p89c58x2 nios(r) ⅱprocessor nios mc68hc908 iec61850 ics i/o结构 fpga fifo ddr存储控制器 csos can总线 bragg散射

科研热词 长期演进 无线技术 射频 lte基站 lte imt-advanced 首席执行官 面阵ccd 键位 行电路 节能技术 电源优化 电力系统 电力分布式计算总线 混合信号设计 模拟 格雷码 数据采集与传输 数字隔离器 录井 异步fifo 密码保护 太阳能系统 太阳能电池板 太阳能发电系统 图形化 图像采集 发电量 双线性插值 双口ram 半导体 医疗电子 分布式计算 光伏系统 传真通信 优化器 仿真器 仿真 亚稳态 ward等值 virtuoso vhdl t.30建议书 soa simulation niosⅱ modem link ic设计 elvis ecg camera

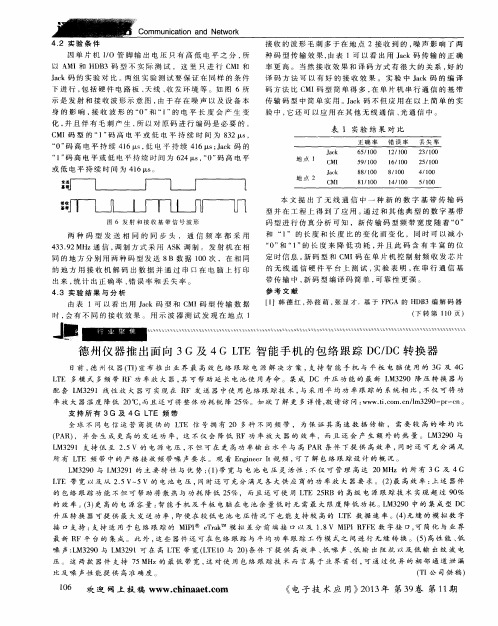

德州仪器推出面向3G及4GLTE智能手机的包络跟踪DC/DC转换器

支 持所有 3 G及 4 G L TE 频 带

全 球 不 同 电信 运 营商提 供 的 L T E信号拥有 2 0 多种 不 同 频 带 , 为 保 证 其 高 速 数 据 传 输 , 需 要 较 高 的 峰 均 比 ( P AR) , 并 会 生 成 更 高 的 发 送 功 率 ,这 不 仅 会 降 低 RF功 率 放 大 器 的 效 率 ,而 且 还 会 产 生 额 外 的 热 量 。 L M3 2 9 0与

定 时信 息 。 新码型 和 C MI码 在 单 片 机 控 制 射 频 收 发 芯 片 的 无线 通信 硬 件平 台 上钡 4 试, 实验 表 明 , 在 串 行 通 信 基

带传 输 中 , 新 码型 编译码 简单 , 可靠性 更强 。

参 考 文 献

[ 1 】韩 德 红 , 孙筱萌 , 张 显 才 .基 于 F P G A的 H D B 3编 解 码 器

验 中, 它还 可 以应用 在其他 无线 通信 、 光 通信 中 。

身 的影 响 , 接 收 波形 的 “ 0” 和“ 1 ” 的 电 平 长 度 会 产 生 变

化 , 并 且伴 有 毛刺产 生 , 所 以对原码 进行 编码 是必 要 的。 C MI码 型 的 “ 1 ” 码 高 电 平 或低 电平 持 续 时 间 为 8 3 2 s , “ 0 ” 码高 电平持 续 4 1 6 s , 低 电 半持 续 4 1 6 t x s ; J a c k码 的

德 州仪 器 推 出面 向 3 G及 4 G L T E 智 能 手机 的包 络 跟 踪 D C / D C转 换 器

DSP2.0:一站式整合化技术营销平台_DCCI

C目录一、数字营销发展脉络 (1)1、数字营销发展形态,数据化、精准化、程序化发展趋势 (1)2、程序化购买模式应运而生 (1)二、程序化购买概述 (2)1、程序化购买在美国 (2)2、程序化购买在中国 (2)3、未来中国程序化购买模式发展趋向 (3)三、解读DSP (4)1、DSP营销效能 (4)2、DSP发展趋向 (4)四、悠易互通DSP2.0 (6)1、产品概述 (6)2、核心优势 (7)3、@iR成功投放案例 (7)五、程序化购买客户应用 (12)1、产品认知情况 (12)2、产品使用情况 (12)3、未来产品需求 (12)附录:国内市场主要DSP产品概览(拼音序) (14)DCCI简介 (16)一、数字营销发展脉络1、数字营销发展形态,数据化、精准化、程序化发展趋势二十世纪90年代互联网的兴起,数字营销开始进入营销从业者的视野。

从最初的展示广告,发展到搜索引擎广告,再到如今社交广告、视频广告、移动广告的蓬勃发展。

随着技术上的不断突破和网民行为的不断变迁,以及广告主对广告效果的不断追求,网络营销本身也在不断的发生演变。

数字营销行业不断走向数据化、精确化、程序化。

如今网民行为日益向碎片化发展,不断从原来的每户网站向社会化网络、视频网站、移动端迁移,网民需求也日益个性化,相应的数字营销方式也在发生转变。

数字营销一方面朝着愈加实时、精准的方向发展,从单纯的呈现信息到主动响应网民需求,到渗透用户关系链、实时感知用户,数字营销对于网民需求把握的精准程度正在逐步提升;另一方面在精准的基础上,数字营销正加速提升整体的营销效率,从媒体的广泛覆盖到关键字响应用户需求,到受众细分的广告网络,再到针对移动终端个体用户,数字营销的营销效率愈来愈快。

而当用户行为在多种数字媒体以及多种网络终端的冲击下变得碎片化时,大数据时代正在悄然来临。

数据在数字营销过程中所发挥的作用将愈加重要,借助数据的力量我们有机会更加深入、全面的洞察消费者,能够更加清晰的理解不同营销渠道的营销效果,以及各个因素对于营销效果的影响,同时数据为程序化营销奠定坚实基础,使得营销者能够借助程序化购买平台与工具实现大规模、精准定位的自动化、程序化购买。

德州仪器推出业界首款超低功耗FRAM微控制器

可 有 效 降 低 硬 件 购 置 成 本 。 这 项

创 新 的 色 彩 技 术 不 仅 能 够 满 足 OE 厂 商 和 终 端 用 户 当 前 的 需 M

求 , 同 时 也 兼 顾 了 未 来 的 市 场 应 用趋势 。

化 技 术 高 峰 论 坛 、 A C 中 国 论 R

坛 、 工 业 控 制 电子 设 计 技 术 研 讨 会 、 绿 色 节 能 技 术 与 可 持 续 发 展 高 峰 论 坛 、2 1 再 制 造 产 业 大 会 0 1 及 汽 车 零 部 件 再 制 造 论 坛 、 工 程 机 械 行 业 信 息 化 发 展 论 坛 等 行 业 研 讨 活 动 ,在 制 造 业 可 持 续 发 展

需 要 微 米 级 精 度 , 或 者 被 测 目标

是 否 有 光 泽 或 表 面 黑 色 , 或 硬 体

现 场 的 最 大 亮 点 ,约 3 0家展 商 倾

或 软体 ,高 速、 高精 度、 无接 触

式的 L H测 量 传 感 器 都 可 以 提 供 可 靠 稳 定 的解 决 方案 。

的功 能 。

结 合 对 中 国 中 小 型 机 器 市 场 深 刻 理 解 ,第

一

期 发 布 将 推 出 一 体 化 编 程 组 态 软 件 C W 和 C

M i o 1 、M i o 3 c 80 r c 8 0两 类 P C, 最 高 可 达 4 r L 8

点 I / O。内置 U B端 口和 串口,OE 客户可 以 S M

场。

方案、节能设 备、节能效果评 估 、 绿 色 能 源 发 展 等 话 题 , 受 到 参 会

者 的关注。

代 与 基 于 闪存 和 E P OM 的微 ER

Femtocell家庭基站通信截获、伪造任意短信漏洞

Femtocell家庭基站通信截获、伪造任意短信漏洞阿⾥移动安全团队与中国泰尔实验室⽆线技术部的通信专家们⼀起,联合对国内运营商某型Femtocell基站进⾏了安全分析,发现多枚重⼤漏洞,可导致⽤户的短信、通话、数据流量被窃听。

恶意攻击者可以在免费申领⼀台Femtocell设备之后,迅速地将其改造成伪基站短信群发器和流量嗅探器,影响公众的通信安全。

家庭基站(Femtocell,⼜称飞蜂窝,Femto本意是10的-15次⽅)是运营商为了解决室内覆盖问题⽽推出的基于IP⽹络的微型基站设备,通常部署在⽤户家中,甚⾄直接放在桌⾯上。

随着运营商⽹络建设基本完成,宏站基本不再增加,Femtocell作为⽹优阶段解决信号覆盖盲区最有效的⼿段,倍受运营商青睐。

由于Femtocell通过IP与运营商核⼼⽹直接连接,并从⽤户侧来看,是完全合法的基站设备。

Femtocell⼀般安装在⽤户触⼿可及的位置上,这就使得⼀直躲在通信机房这⼀天然物理安全屏障庇护下的传统通信⼚商,终于要接受天下⿊客的检阅了。

然⽽,传统通信⼚商在开发过程中的安全意识淡薄,导致了通信设备的安全漏洞⽐⽐皆是。

近年来,BlackHat、DEFCON等安全⼤会上多次曝出Femtocell的安全问题。

漏洞细节已于2015年5⽉21⽇通报相关运营商,相关⼚家已经针对此漏洞对全⽹设备进⾏了紧急修复,⽬前漏洞已经修复完成。

出于推进安全研究的考虑,现在将漏洞的细节公开。

1 板卡概览1.1 设备的获得如何获得⼀台Femtocell设备呢?在2015年4⽉初,我给10086打电话,报告说屋⼦⾥的信号很差(事实的确如此)。

10086说如果家⾥有宽带,可以免费安装⼀台⼩基站。

过了两天,安装的⼯程师就上门来装了。

Femtocell设备典型的安装位置如下图所⽰:最⼤发射功率在30dBm,只有1W。

⽽⼀般的GSM基站功率⼤约在20W左右。

Femtocell安装之后,效果的确⾮常好。

【电子技术应用】_通信技术_期刊发文热词逐年推荐_20140725

科研热词 推荐指数 fpga 7 现场可编程门阵列 3 无线传感网络 3 无线传感器网络 3 数据采集 3 嵌入式系统 3 嵌入式技术 3 太阳能 3 ip地址三维分配法 3 802.11 3 超宽带 2 蓝牙技术 2 无线通信 2 差分算法 2 双向工频通信系统 2 仿真技术 2 zigbee 2 voip 2 sip 2 nios 2 mcu 2 dsp 2 高速数据传输 1 频移键控 1 频分复用 1 音频信号 1 面向业务 1 静态显示 1 隐训练序列 1 隐藏终端 1 阻抗匹配网络 1 闪速存储器 1 铃流检测 1 通信模型 1 通信标准 1 远程通信 1 远程抄表 1 运营商 1 软件平台 1 转换效率 1 身份欺骗 1 跳频 1 超窄带 1 赛灵思公司 1 调制 1 语音识别 1 识别引擎 1 设计行业 1 论坛 1 认知无线电 1 订阅 1 计算机技术 1

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106

TMS320TC16487:最新可扩展LTE平台三核数字信号处理器

TMS320TC16487:最新可扩展LTE平台三核数字信号处理

器

佚名

【期刊名称】《世界电子元器件》

【年(卷),期】2009(000)004

【摘要】日前,德州仪器宣布已成功开发出1.2GHzTMS320TC16487,该款运行频率高达3.6GHz的三核数字信号处理器完美结合了功能强大的软件库,全面优异的性能足以满足LTE的复杂算法要求,从而充分符合高密度MIPS的长期演进(LTE)无线标准。

利用TI最新LTE解决方案,OEM厂商可扩展其现有基站平台,以便在无需设计新电路板的情况下融入新的特性及更复杂的算法。

此外,TI专为LTE精心优化的软件库还充分利用了可显著提高当今系统效率的专用加速器与指令。

【总页数】1页(P23)

【正文语种】中文

【相关文献】

1.芯原宣布其ZSP数字信号处理器核及SoC平台将全面支持WebM [J],

2.德州仪器推出可扩展LTE平台 [J],

3.德州仪器推出功能强大的最新可扩展LTE平台 [J],

4.芯原宣布其ZSP数字信号处理器核及SoC平台将全面支持WebM [J], 本刊通

讯员

5.德州仪器推出功能强大的最新可扩展LTE平台 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

此外,TI还携手业界领先的毫微微蜂窝基站软件供应商Continuous Computing,共同将Trillium Femtocell Access Point软件协议栈向CI6484移植。通过提供这种捆绑式解决方案,OEM厂商可迅速据发展策略发展策略提供高度可靠的DSP解决方案,TI还可提供包括数据转换器、RF解决方案、放大器、时钟以及电源管理电源管理器件等在内的各种模拟产品。

德州仪器面向毫微微蜂窝基站推出DSP TCI6484

日前,德州仪器(TI)宣布推出新型高性能高性能量产数字信号处理器(DSP)解决方案TCI6484,可为设备制造商在毫微微蜂窝基站毫微微蜂窝基站市场上取得成功提供必要工具。

TI目前正向数家毫微微蜂窝基站OEM厂商提供DSP解决方案。传统的无线基础设施OEM厂商可充分利用业界领先的TMS320 TCI6484的优势,无需外部ASIC或FPGA即可支持MAC与PHY处理。这种可编程产品支持现场固件固件升级(field firmware upgrade),能够帮助基础设施OEM厂商以低成本方式进入毫微微蜂窝基站市场。随着市场的不断成熟,这种SoC+加速器解决方案将帮助基站OEM厂商设计出高度优化的解决方案。

供货情况

TCI6484产品现已开始供货。