max+plusⅱ的基本应用-波形输入练习 实验报告

max+plus2数电实验报告小红书

max+plus2数电实验报告小红书实验目的实验原理实验器材实验步骤实验结果实验分析实验结论实验目的本次实验旨在通过实践探究max+plus2数电的工作原理和应用,在实验中加深对数电原理的理解,同时提高实验操作能力和解决问题的能力。

实验原理max+plus2数电是一种常用的数字电路开发板,它集成了多种数字电路模块,可进行逻辑设计和数字信号处理等实验。

其主要原理是通过编程控制和数字信号的处理,在实验中能实现各种数字逻辑电路的功能。

实验器材本次实验所需的器材如下:1. max+plus2数电开发板2. 电源线3. 连接线4. 逻辑门模块5. LED灯模块6. 开关模块实验步骤1. 将max+plus2数电开发板连接到电源线,并将电源线插入电源插座,确保电源正常供应。

2. 根据实验设计的逻辑电路图,将逻辑门模块、LED灯模块和开关模块连接到max+plus2数电开发板的相应端口。

3. 打开开发板的电源开关,确保电源正常供电。

4. 编程控制max+plus2数电开发板,将相应的逻辑电路图转化为代码,并加载到开发板中。

5. 通过操作开发板上的开关,观察LED灯的亮灭情况,检查逻辑电路的功能是否正常。

实验结果经过一番调试和观察,实验结果如下:1. 当开关处于某个特定状态时,LED灯亮起。

2. 当开关处于其他状态时,LED灯熄灭。

实验分析通过实验结果的观察和分析,我们可以得出以下结论:1. max+plus2数电开发板可以通过编程控制,实现各种逻辑电路的功能。

2. 实验中所使用的逻辑门模块、LED灯模块和开关模块均能正常工作,与开发板配套使用效果良好。

3. 通过实验,我们进一步理解了逻辑电路的原理和工作方式。

实验结论本次实验通过实践操作max+plus2数电开发板,验证了其能够实现逻辑电路的功能。

实验结果表明,max+plus2数电开发板具有良好的稳定性和可靠性,可以作为数字电路实验的理想工具。

通过这次实验,我们不仅提高了实验操作能力,也深化了对数电原理的理解,为进一步学习和应用数字电路奠定了基础。

MAX+PLUS II 的高级使用(波形编辑、LPM类、高级使用)

第五章 MAX+PLUSⅡ的高级使用在第三章MAX+PLUSⅡ的基本应用已经介绍了MAX+PLUSⅡ基本的、通用的特性,包括文件编辑、综合仿真等内容。

但由于不同的CPLD/FPGA器件的资源和性能都有所不同,而且多种设计方法综合利用也有助于提高设计速度和设计质量,因此本章结合这些方面的内容介绍MAX+PLUSⅡ更高级的使用。

5.1 波形输入编辑逻辑电路的波形输入:打开MAX+PLUSⅡ,用鼠标点击新建,在图5-1中选择图5-1 波形编辑启动界面 选择*.WDF 文件“Waveform Editor”,在下拉框中选择”“.wdf”扩展名,然后“OK”即可启动波形编辑界面,如果编辑简单输入、输出逻辑关系,使用波形编辑输入比较简单。

如果输入、输出之间的关系比较复杂,使用波形编辑输入比图形输入和语言编辑要复杂。

但如果只知道输入、输出波形,而不知道具体电路时,采用波形编辑就显得非常有用。

例:用波形编辑输入设计一个“或”逻辑关系启动波形界面后(如图5-2),用鼠标双击编辑区的空白处,在弹出的对话框中添入输入、输出名称如a,b,c等。

每输入一个名称,都要在同一界面中选择“INPUT”或“OUTPUT”如图5-3所示。

本例中定义的输入、输出信号如图5-2所示。

下面就图5-2、5-3中的各个选项的含义及使用步骤介绍如下:1、在“Node Name:”框输入信号名称,在“Default Value”中输入默认值。

138图5-2 波形编辑界面图5-3 波形编辑中信号定义界面默认值的类型可以是‘0’、‘1’、‘X’、‘Z’四种。

如果信号是数组的形式定义139的,则可以在波形界面利用“Ungroup”展开后,双击单个信号进行修改。

默认值一般只用来仿真,综合后默认值都为0。

输入信号为数组时其命名规则与AHDL 的规则相同。

2、设置输入、输出类型在“I/O Type”中选择信号的输入、输出类型。

其中“Buried Node”与AHDL 语言中的“Variable”子段的含义相同,是定义内部变量。

Max+plusⅡ的使用

MAX+plusⅡ使用简介下面通过一个实例(exampl1)的设计过程,介绍MAX+plusⅡ的使用。

exampl1采用层次设计方法,exampl1电路由一个3位二进制计数器counter和一个3位2选1多路选择器mux2构成;而计数器又是由三个触发器tff1组成的,tff1是带异步清零、具有时钟使能的T触发器。

在本设计中,mux2用VHDL文本方式描述;tff1、counter 和exampl1分别用底层电路图、上层电路图和顶层电路图描述。

通过这个设计介绍以下几项内容:●建立子目录和设计项目●绘制电路图●书写VHDL文件●绘制高层电路图●编译和适配设计●建立电路输入信号的波形●仿真●定时分析1. 建立子目录和设计项目首先,在Windows窗口,用资源管理器为你的设计项目建立一个子目录,例如,d:\max2work\exampl ,你的设计项目的所有文件将都保存在该目录下。

其次,为你的设计项目tff1 命名,具体的做法是:启动MAX+plus,打开MAX+plus ⅡManagerr(程序管理器)窗口,点击File(文件)→Project(设计项目)→Name(名字)。

在Project Name对话框中键入设计项目名:tff1(带异步清零、具有时钟使能的T触发器)。

MAX+plusⅡManager 窗口的标题条变成MAX+plusⅡ- d:\max2work\exampl\ tff1 。

2. 建立tff1 电路图文件首先,建立tff1的电路图文件。

在MAX+plusⅡManager窗口,点击MAX+plusⅡ菜单→Graphic Editor(图形编辑器),打开Graphic Editor窗口。

点击File →Save As(另存为),在File Name对话框中键入电路图的名字(它应与设计项目的名字相同):tff1(后缀自动为.gdf)。

点击OK按钮,保存tff1.gdf文件。

然后,绘制tff1电路图(图1)。

MAX+plusⅡ_实验之入门教学

2.编译

单击MAX+plusⅡ→Compiler选项,即可打开编译器。另外,也 可以单击File→Project→Save & Compiler(保存文件同时编译)选项, 系统将把当前设计的若干文件存盘后,自动弹出编译器窗口,单击 【Start】按钮,编译器就开始对当前设计进行编译。

编译完成后,系统弹出错误和警告信息统计对话框,单击【确定】

3.元件符号的复制和移动

可单击准备复制的元件或用鼠标对该元件画矩形框(定位于某 一点,按下鼠标左键并向元件对角方向拖动),元件的轮廓变成红 色的粗实线,表示已经选中该元件,然后按住〈Ctrl〉键,对该元 件拖动,即可拖出一个被复制的元件。 元件需要移动时,可用鼠标拖动图形编辑区中的元件图形符号, 元件就能随着鼠标的滑动而任意移动。左键释放,则图形元件定位。 若要同时移动多个元件,可以用鼠标左键拉出一个大的矩形框,把 要移动的元件都包围起来。这样多个元件同时被选中,就可以一起 被移动了。

单击标题栏的Options→Snap to Grid(对齐网格)去掉前面的对 勾,以方便设置输入电平。

4.波形输入

选中 输入端,如: 然后点击窗口左侧的时钟信号源图标

Hale Waihona Puke 出现如图所示的对话框。例如:选择初始电平为“0”,时钟周期为“200ns”,倍数为“1” (时钟周期倍数只能为整数倍),单击 OK 确认。

打开MAX+PLUS II,输入设计项目和存盘 打开 ,

新建一个设计文件 使用原理图输入方法设计 必须选择打开原理图编辑器

进入MAX+plusII,建立一个新的设计文件 , 进入

选择Graphic Editor File选项后,接受gdf的默认扩展名,单击【OK】按 钮确认。进入图形编辑器的编辑环境。。

MAX+plusⅡ界面操作 VHDL输入练习

实验六MAX+plusⅡ界面操作VHDL输入练习一、实验目的1、熟练掌握MAX+plusⅡ的界面和基本操作步骤。

2、掌握VHDL输入的设计流程。

二、实验内容1、进一步熟悉MAX+plusⅡ的界面,练习软件的基本操作方法。

2、通过基本门电路、3-8译码器、选择器、半加器等设计,学习VHDL输入设计的全过程。

三、实验步骤1、建立新项目,确定工程文件名。

File/Project/Name…2、指定器件Assign/Device…3、建立新的输入文件:File/New…,选择输入方式。

4、设计程序输入。

5、编译。

MAX+plusⅡ/Compiler…或File/Project/Sav e&Compiler…6、引脚分配MAX+plusⅡ/Floorplan Editor…7、功能仿真①创建波形文件File/New… (.scf)②设置时间File/End time… ,设置网格间距Options/Grid size…③调输入/输出点Node/Enter Nodes from SNF…或窗口右击。

④给输入赋值,波形编辑。

⑤仿真MAX+plusⅡ/simulator…8、实验箱连线,打开电源。

9、下载MAX+plusⅡ/programmer…,观察结果。

10、创建功能模块File/Create Default Symbol…(一)基本门电路图1-1 基本门电路程序图1-2 基本门电路波形仿真图1-3 基本门电路引脚分配(二)3-8译码电路图2-1 3-8译码器电路程序图2-2 3-8译码器电路时序图(三)选择器图3-1 选择器程序图3-2 选择器时序图3-3 选择器引脚分配四、实验结论。

Maxplus软件的基本操作实验报告

实验一Maxplus 软件的基本操作一、实验目的1、熟悉Maxplus软件的基本操作,了解各种设计方法(原理图设计、文本设计、波形设计)2、熟悉VHDL语言,用VHDL语言写简单的程序3、熟悉组合逻辑设计的一般方法4、用逻辑图和VHDL语言设计一个异或门二、实验原理异或门是一种用途广泛的门电路。

典型应用都是作为加法器的单元电路。

异或门是2输入门,如果恰好输入之一为1,则输出为1.换句话说,如果两个输入是不同的,则异或门产生1输出。

即输入相同则输出为1,输入相异则输出为1。

逻辑组合:’·Y + X · Y’三、实验内容用VHDL语言设计一个异或门,当输入端同时输入0或1时,异或门产生1输出,否则,产生0输出。

运用Maxplus软件,仿真异或门的波形图。

逻辑符号图:四、真值表五、电路图输出函数的逻辑等式:OUT = (A’· B + A · B’)电路图:六、实验步骤1、根据真值表编写程序;2、进行仿真(仿真波形以及电路验证);3、延时分析七、实验解答1、异或门源代码异或门:******************************************************************** LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY xor2 ISPORT(a,b: IN STD_LOGIC;c : OUT STD_LOGIC);END ENTITY xor2;ARCHITECTURE bhv OF xor2 ISBEGINc<=a XOR b;END ARCHITECTURE bhv;2、波形仿真3、延时分析八、实验总结1、保存时,文件名一定要与实体名相同。

2、在仿真波形图之前一定要保存,并重新进行编译。

3、在波形图中观察静态冒险。

4、在programmer之前要再一次编译,否则出现的是前一个的结果。

MaxplusII学习总结

Max+Plus II 利用总结(一)Max+Plus II 是一个优秀的VHDL仿真和EPLD编程软件,它能够完成数字电路图、VHDL的仿真后优化,并将完成的POF文件下载到相应的可编程器件中。

它的编程-设置-仿真模式和OrCAD差不多,都要通过这三步。

拿电路图输入来讲,它需要第一输入电路图,选择编程器件型号,然后编译,在编译进程中能够通过观察rpt文件取得运算机对管脚的赋值,若是用户不中意能够自己赋值,方式是选择Maxplusii Floorplan Editor,再选择Layout Device View和Layout Current Assignments Floorplan,显示当前的管脚分派情形[注意那个地址需要说明的是关于每一个编辑器,MAXPLUSII都对其挪用不同的菜单组],在那个地址用户能够自己配置适合的管脚。

正确编译后就进入仿真时期,在仿真时期,第一挪用MAXPLUSII WaveForm Editor,设置仿真的时长和仿真的最小步长,然后选择需要仿真显示的管脚名称,编辑输入波形,就取得仿真结果,按Open SCF,就可观看仿真波形。

波形正确,也确实是达到特定的功能了,咱们就能够够将程序下载到EPLD中,具体方式是选择MAXPLUSII Programmer,然后配置pof文件,就通过下载电缆和编程器将程序烧写到相应的芯片中去。

所用到的功能有:Hierarchy Display:用以显示本工程(或项目)的结构,包括其文件组成等。

Graphic Editor:图形编辑器,用来输入数字电路图。

Symbol Editor:符号编辑器,用来编辑符号。

Text Editor:文本编辑器,用来编辑VHDL程序。

WaveForm Editor:波形编辑器,用来编辑仿真波形。

Floorplan Editor:管脚编辑器,用来配置芯片管脚。

Compiler:编译器,用来编译VHDL程序、电路等,具有过失功能。

Maxplus软件的基本操作实验报告

实验一Maxplus软件的基本操作一、实验目的1.熟悉Maxplus软件的基本操作,了解各种设计方法(原理图设计、文本设计、波形设计)2.用逻辑图和VHDL语言设计一个异或门。

二、实验内容1.用VHDL语言设计一个异或门2.用Maxplus软件仿真波形图3.设计芯片三、实验方法1.启动Maxplus II2.新建一个文本编辑文件,输入异或设计的VHDL语言3.编译。

点击file→save as,保存文件名为entity名称,扩展名为vhd,选择芯片类型为EPF10K20TI144-4,保存并编译,出现0 error,0 warnings则编译通过。

4.仿真波形。

点Max+plus II→Waveform editor,出现波形图的设置界面,然后点Node→Enter Nodes from SNF→list,将输入输出端添加到界面,并设置其周期和输入波形,保存后,点Max+plus II→Simulator,即可仿真出输出的波形。

5.设计芯片。

点Max+plus II→Floorplan editor,将Unassigned Nodes & 栏中,电路的输入输出节点标号直接用鼠标“拖到” 想分配的引脚上(a:88,b:89,c:12),点Max+plus II→programmer→configuer,然后就可以操作试验箱,观察异或门的工作情况。

四、实验过程异或门(XOR)用途:异或门是一种用途广泛的门电路。

典型应用是作为加法器的单元电路。

逻辑图真值表A B OUT0 0 00 1 11 0 11 1 0VHDL程序数据流描述:波形图芯片引脚分配四、实验总结初次使用Max plus,感觉它既新奇又复杂,再加上它的纯英文操作,增加了此软件的使用难度,不过由于对新事物的好奇,第一次实验还是比较有意思的。

实验初期,我们只能将VHDL语言写出来,对着一串代码我们却不知道如何处理,后来看过老师的操作后便初步会仿真波形和设计芯片了,并成功的将异或门写入芯片,完成其功能。

实验一 MAX-plusII及开发系统使用

实验一 MAX –plusII 及开发系统使用一、实验目的1、 熟悉MAX-plus Ⅱ的使用方法,以及EDA 的基本设计流程;2、 掌握基于文本(VHDL )和原理图输入方法设计简单的组合电路3、 初步掌握层次化设计的方法4、 熟悉DXT-B Ⅲ型EDA 试验开发系统的使用 二、主要实验设备PC 机一台,DXT-B3 EDA 实验系统一台。

三、实验原理EDA 技术系列实验是建立在数字电路基础上,采用先进的EDA 技术完成数字系统设计的一个更高层次的设计性实验。

它是借助大规模可编程逻辑器件(C PLD/FPGA ),采用在系统可编程技术(ISP ),利用电子设计自动化软件和硬件描述语言,在计算机平台上完成系统的设计、编译、仿真、逻辑综合、布局布线,并下载到大规模可编程逻辑器件。

最终完成专用集成电路(ASIC )或片上数字系统(SOC )的设计。

EDA 技术设计主要是在计算机平台上进行,因此实验方式,实验手段和实验仪器与传统的实验有很大的区别,主要体现在以下几个方面:1、 实验的核心部件是大规模可编程逻辑器件,实验的设计基本只针对CPLD/FPGA 进行。

通过相应的管脚安排,利用实验箱外围的辅助电路进行设计的硬件测试和验证。

2、 大规模可编程逻辑器件可重复下载,基本没有耗材;3、 设计的主要过程在计算机上进行,自动化程度高,人机交互性好,修改、验证实验简单.四、Max_plus Ⅱ 10.0的使用。

max+plus Ⅱ软件基本设计流程如图1-1所示:(一)新建项目文件一般可以是图形文件(文件后缀.gdf )或由硬件描述语言编写的文本文件(VHDL 编写的文件后缀为.vhd ,Verilog HDL 编写的文件后缀为.v )。

具体操作过程如下:在File 下拉菜单中选择New 将跳出如图1-2所示新建文件类型选择对话框,然后选择需要建立的文件类型。

四种文件类型分别为:图形编辑文件、符号编辑文件、文本图1-2新建文件类型图1-1 EDA 项目设计流程图编辑文件和波形编辑文件。

MAX+PLUSII的基本应用

实验一 MAX+PLUSII的基本应用——图形输入练习一实验目的1.掌握MAX+PLUSⅡ的安装及基本使用。

2.掌握MAX+PLUSⅡ基本输入法—图形输入工具按钮的使用。

二实验设备与仪器1.计算机2.MAX+PLUSⅡ工具软件三实验内容1.MAX+PLUSⅡ的安装。

2.在图形编辑软件中,进行调入元件符号、放臵元件、连线、放臵输入输出引脚及放臵节点标号等练习。

四实验原理1.在时序电路中,计数器的应用十分普遍,例如常用的分频电路都是由计数器构成,在状态机中也经常用到计数器。

设计一个60十进制同步计数器,可应用于钟表电路中。

电路主要由两个十进制同步计数器74LS160组成。

2.实验电路图如图1-1所示。

图1-1五实验步骤1.MAX+PLUSⅡ的安装,只要在安装向导的指引下,按步骤的顺序执行,即可完成。

2.MAX+PLUSⅡ安装完毕后,在第一次运行时需要进行License设臵,然后才可以使用。

3.启动MAX+PLUSⅡ软件,进入MAX+PLUSⅡ管理窗口。

进行设计项目的建立。

4.在MAX+PLUSⅡ管理窗口的File菜单下选择New选项或单击按钮,然后再选择Graphic Editor file后,单击OK按钮,可建立图形输入文件。

5.从库中调入元件符号。

在图形编辑区内双击鼠标左键或单击鼠标右键,在随后弹出的菜单中选择Enter Symbol即可直接键入元件名,调出元件,也可以选择元件库。

MAX+PLUSⅡ提供了4种库文件,其功能见表1-1所示。

表1-1 图形编辑器提供的库功能6.单击连线工具栏的按钮,光标变成,‚+‛形,单击连线起始端按住鼠标左键拖动至结束端松开,连线结束。

若要删除某连线,可单击连线使其变成高亮(红色),再按,Delete键,即可删除。

7.图形编辑时,在连线复杂的地方(总线),可用节点标号来连线。

用节点标号连线不区分大小写。

8.放臵输入输出引脚。

在符号库中调入元件符号对话框中,键入,input‛或,output‛即可将输入或输出引脚添加到电路图中,新放臵的输入输出引脚需要修改引脚名称。

Maxplus_Ⅱ基本操作方法

附录:Maxplus Ⅱ基本操作方法——图形输入法利用EDA工具进行原理图输入设计的优点是,设计者能利用原有的电路知识迅速入门,完成较大规模的电路系统设计,而不必具备许多诸如编程技术、硬件语言等新知识。

MAX+plusII提供了功能强大,直观便捷和操作灵活的原理图输入设计功能,同时还配备了适用于各种需要的元件库,其中包含基本逻辑元件库(如与非门、反向器、D触发器等)、宏功能元件(包含了几乎所有74系列的器件),以及功能强大,性能良好的类似于IP Core的巨功能块LPM库。

但更为重要的是,MAX+plusII还提供了原理图输入多层次设计功能,使得用户能设计更大规模的电路系统,以及使用方便精度良好的时序仿真器。

以传统的数字电路实验相比为例,MAX+plusII提供原理图输入设计功能具有显著的优势:∙能进行任意层次的数字系统设计。

传统的数字电路实验只能完成单一层次的设计,使得设计者无法了解和实现多层次的硬件数字系统设计;∙对系统中的任一层次,或任一元件的功能能进行精确的时序仿真,精度达0.1ns ,因此能发现一切对系统可能产生不良影响的竞争冒险现象;∙通过时序仿真,能对迅速定位电路系统的错误所在,并随时纠正;∙能对设计方案作随时更改,并储存入档设计过程中所有的电路和测试文件;∙通过编译和编程下载,能在FPGA或CPLD上对设计项目随时进行硬件测试验证。

∙如果使用FPGA和配置编程方式,将不会有如何器件损坏和损耗;∙符合现代电子设计技术规范。

传统的数字电路实验利用手工连线的方法完成元件连接,容易对学习者产生误导,以为只要将元件间的引脚用引线按电路图连上即可,而不必顾及引线的长短、粗细、弯曲方式、可能产生的分布电感和电容效应以及电磁兼容性等等十分重要的问题。

以下将以一位全加器的设计为例详细介绍原理图输入设计方法,但应该更多地关注设计流程,因为除了最初的图形编辑输入外,其它处理流程都与文本(如VHDL文件)输入设计完全一致。

VHDL实验指导书

实验一MAX plu sⅡ的使用【实验目的】1.掌握MAX plu sⅡ的使用2.掌握逻辑门的VHDL描述方法【实验内容】一、MAX plu sⅡ的设计流程1.创建设计输入文件(1)在“MAX2work”目录下创建自己的工作目录“mywork”,使得以后自己做的设计都保存在这个目录下。

(2)单击“file”菜单中的“new”选项,出现图1-1所示的新建文件窗口。

图1-1 新建文件窗口图(3)选择“Text Editor file”,单击“OK”按钮,出现文本编辑器,然后在文本编辑器里输入设计程序。

2.保存文件单击工具栏上的保存按钮,出现如图1-2所示的保存窗口。

图1-2 保存窗口图选择自己的工作目录,建立自己的文件名,保存所做的设计。

3.设置项目(1)选择菜单【File】/【Project】/【Set Project to Current File】命令,出现图1-3所示的窗口。

图1-3 设置项目窗口图设置项目名与设计文件名相同,一般软件会自动填入此项目名,这是后续处理必不可少的一步。

4.设定器件(1)选择菜单【Assign】/【Device】命令,出现图1-4所示的窗口。

图1-4 设定器件窗口图(2)在“Device Family”选项中选择所使用的系列芯片;在“Devices”中选择“AUTO”,让软件自动选择具体器件。

单击“OK”按钮,即设定好器件。

(3)单击工具栏上的保存按钮,保存好以上所有的设计和设置。

5.编译项目(1)选择菜单【MAX plu sⅡ】/【Compiler】命令,出现编译窗口,然后选择菜单命令【Processing】/【Functional SNF Extractor】如图1-5所示。

(2)单击“Start”按钮,开始编译,编译成功后,会出现1-6所示的窗口。

6.功能仿真(1)创建波形文件:在菜单栏中选择命令【File】/【New】,出现新建文件窗口,选择“Waveform Editor File”选项,如图1-7所示。

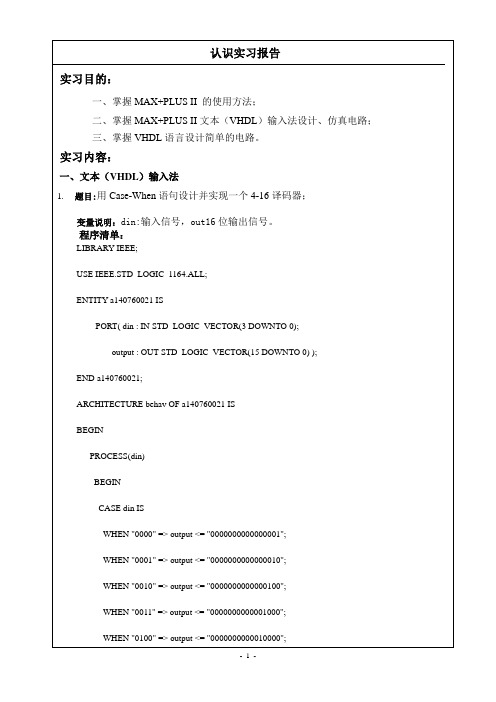

max+plus2实习报告

4. 用For- Loop语句设计并实现一个8位串入/并出移位寄存器变量说明:serial in:串入信号:,clk:时钟q:并出信号

程序清单:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY A440760021 IS

PORT(

5用If - Else语句设计并实现一个4位十六进制可逆计数器

变量说明: clk: 工作时钟,clr复位, q:输出计数信号,ud:正向,逆向计数,高电

Ud=0 逆向计数

:.

二、简单数字系统设计

题目:设计并实现一个能实现清零、计时、停止功能,可表示分、秒的数字秒表电路。

(提示:输入信号的频率可自行选择!)

…………………………

秒译码输出仿真波形图:

…………………………

整体仿真波形图:

1 未加入显示模块模拟输出观察是否正常:

简单的数字秒表设计完结;。

Max+plusⅡ在《数字电路》教学中的应用

Max+plusⅡ在《数字电路》教学中的应用Max+plusⅡ软件是一款高效的、非常灵活的数字电路开发设计软件,它提供了多种输入方法供设计者选用,利用合适的输入方法设计完数字系统之后,设计者可利用逻辑综合工具进行逻辑综合,并可以用仿真器进行软件仿真,使设计者能够尽早发现设计中的错误,缩短设计周期。

简要介绍了Max+plusⅡ在数字电路教学中的应用,并以用不同的输入方法设计一个16位二进制加法器为例,说明Max+plusⅡ的设计仿真过程,以期得到融传统教学方式和现代化设计理念为一体的教学效果。

标签:Max+plusⅡ;数字电路;逻辑综合1 引言Max+plusⅡ是Altera公司提供的FPGA/CPLD开发集成环境,Altera是世界上最大可编程逻辑器件的供应商之一。

Max+plusⅡ界面友好,使用便捷,被誉为业界最易用易学的EDA软件。

在Max+plusⅡ上可以完成设计输入、元件适配、时序仿真和功能仿真、编程下载整个流程,它提供了一种与结构无关的设计环境,使设计者能方便地进行设计输入、快速处理和器件编程。

本文以举例的形式介绍了EDA 的一种开发平台,即美国Altera公司开发的Max+plusⅡ在数字电路教学中的应用。

2 Max+plus Ⅱ简介2.1 Max+plus Ⅱ主要特点Max+plusⅡ开发系统的特点:(1)开放的界面。

Max+plusⅡ支持与Cadence,Exemplarlogic,Mentor Graphics,Synplicty,Viewlogic和其它公司所提供的EDA工具接口。

(2)与结构无关。

Max+plusⅡ系统的核心Complier支持Altera公司的FLEX10K、FLEX8000、FLEX6000、MAX9000、MAX7000、MAX5000和Classic可编程逻辑器件,提供了世界上唯一真正与结构无关的可编程逻辑设计环境。

(3)完全集成化。

Max+plusⅡ的设计输入、处理与较验功能全部集成在统一的开发环境下,这样可以加快动态调试、缩短开发周期。

电子线路实验Ⅱ课程设计报告_用MAX plusⅡ进行设计和仿真

南京信息工程大学电子线路实验Ⅱ课程设计报告电子与信息工程学院07通信工程(2)班姓名:学号:2009.6.1实验题目:用MAX+plusⅡ进行设计和仿真。

实验目的:(1)学习软件的使用方法及VHDL程序的基本语法;(2)用MAX+plusⅡ进行门电路、组合逻辑电路、触发器、可编程逻辑器件和时序电路等的仿真。

实验内容:一、MAX+plusⅡ软件的设计流程1)设计输入点击新建图标弹出如图1.1所示的新建文件类型对话框。

选取“Text Editorfile”使用文本设计方法,在弹出的文本编辑器中输入VHDL语言是设计代码并存盘,窗口显示如图1.2.下面以一个2输入与门的设计为例来描述这一操作。

图1.1 先输入源代码并存盘,文本编辑框效果如图 1.2所示。

将此文件保存为and2.vhd。

注意保存文件时一定要选择“vhd”的文件后缀,文件名必须与实体名相同。

另外,保存该文件的文件夹不能用中文命令,也不能为根目录。

这里是新建一个名为example的文件夹来保存and2.vhd文件的。

图1.2当要打开已存盘的文件时则可点击左上角的,在弹出如图1.3所示Open对话框中“Show in List”栏内,选中要打开的文件类型,再选中VHDL程序所在的文件夹,,在“Files:”框内选中VHDL程序名,这时在“File Name”栏里将显示相应VHDL程序的文件名。

点击“OK”按钮,就会弹出要打开的文件窗口。

2)新建一个项目在编辑并保存VHDL程序后,准备对其编译前,一定要先将该VHDL程序所对应的文件指定为一个项目。

新建一个项目的过程如下:在主菜单中选择“File”→“Project”→“Name…”,打开如图1.4所示的项目名称选择对话框。

在对话框“Directories”栏中,选择项目文件所在的文件夹,再在左边的“File”框里选中要建立项目的VHDL文件名,此时在“Project图1.3 图1.4Name”框内将显示要建立项目的VHDL文件名,再点击“OK”,回到初始界面。

第三章 MAX+PLUSⅡ的基本使用

第三章MAX+PLUSⅡ的基本使用3.1概述MAX+PLUSⅡ开发系统是易学易用的完全集成化的EDA设计开发环境。

目前已发行10.1 版本。

该软件与LATTICE公司的iSPEXPERT及XILINX的FOUNDATION等软件一样都是CPLD/FPGA的基本开发环境,是CPLD开发所必须的,它包含了开发CPLD器件的全过程。

本章将以MAX+PLUSⅡ的基本使用为基础介绍CPLD器件的开发方法,主要目的是利用最小的篇幅介绍开发CPLD器件的全过程,因此不可能面面具到,只能介绍最常用、最基本的特性。

但CPLD器件及其开发系统又是极其复杂的,因此在学习使用时应注意如下特点:1、MAX+PLUSⅡ的使用与学习一定要与CPLD硬件的学习相结合。

2、注意学习软件与动手练习相配合,只有多动手设计与调试才能真正掌设计思想与设计方法。

3、多参考相关的书籍或MAX+PLUSⅡ的帮助系统。

4、在学习过程中要与数字电路、计算机语言等课程进行比较,找出相同点与不同点,进行比较、类比地学习。

5、概念的区分与使用:(1)器件与符号:如在数字电路中7400为一个器件,在MAX+PLUS Ⅱ中器件一般被CPLD器件专用,而MAX+PLUSⅡ中调用的中小规模的器件都称为符号。

本文中有时出于习惯,也会在该使用“符号”的地方而使用“器件”名称,因此在碰到像“器件”、“符号”这样的词,一定要注意上下文的联系。

(2)模块与符号:传统习惯,一般是将一个电路抽象后形成模块,利用模块进行更高层次的设计。

而在MAX+PLUSⅡ中电路抽象后形成的模块依然称为“符号”。

因此在见到“模块”与“符号”这样的词语时,也要注意上下文的联系。

6、通过本章学习,逐步掌握层次电路的设计,设计过程的功能仿真和时序仿真,同时学会低层编辑,利用硬件实验系统进行硬件的验证。

MAX+PLUSⅡ与其它软件相比具有使用简单,操作灵活,支持得器件多,设计输入方法灵活多变等特点,掌握了MAX+PLUSⅡ后,对学习其它的EDA软件会有很大的帮助。

实验一MAX+PLUSⅡ软件的使用

实验一MAX+PLUSⅡ软件的使用一、实验目的:1、学习VHDL语言的基本指令及编程方法。

2、熟悉在PC机上运用MAX+PLUSⅡ软件和EPLD进行电路设计的设计和仿真过程。

二、实验设备:PC机三、实验内容:1、设计一个2选1数据选择器,并验证其功能。

用VHDL语言进行设计,并仿真设计结果。

真值表如下所示:2、用VHDL语言输入法设计一个四舍五入判别电路,其输入为8421BCD码,要求当输入大于或等于5时,判别电路输出为1;反之为0。

四、实验步骤:(一)2选1数据选择器的设计1、采用文本编辑器输入2选1数据选择器VHDL语言源程序,建立工程。

VHDL语言源程序如下所示:library ieee;use ieee.std_logic_1164.all;entity mux21 isport(a,b: in std_logic;s: in std_logic;y: out std_logic );end mux21;architecture mux_arch of mux21 isbeginy<=a when s='0' elseb when s= '1';end mux_arch;2、进行编译后,仿真结果如下所示:a、b为输入端,s为控制端,当s为0时,输出与a的值一致,反之与b的值一致。

(二)四舍五入判别电路的设计1、采用文本编辑器输入四舍五入判别电路VHDL语言源程序,建立工程。

VHDL语言源程序如下所示:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY m45 ISpORT(din: IN STD_LOGIC_VECTOR(3 DOWNTO 0);q : OUT STD_LOGIC);END ;ARCHITECTURE ART OF m45 ISBEGINq<= '1' WHEN din>=5 ELSE'0';END ;2、进行编译后,仿真结果如下所示:输入为0~4时,输出y为低电平,输入为5~15时输出为高电平,实现了四舍五入的功能。

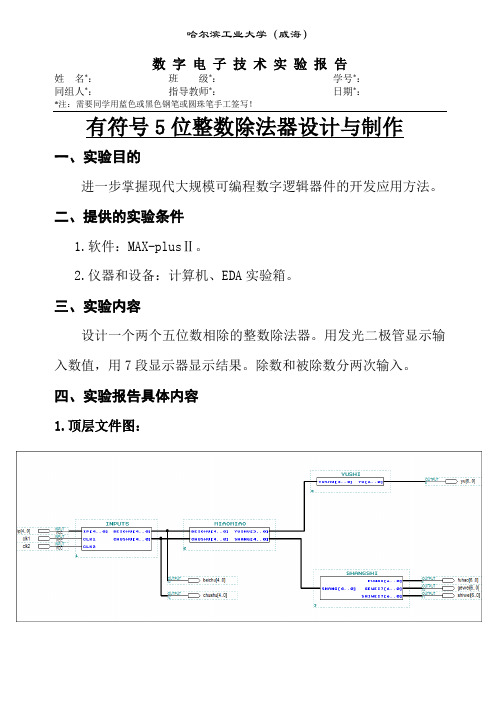

除法器maxplus2

哈尔滨工业大学(威海)数字电子技术实验报告姓名*:班级*:学号*:同组人*:指导教师*:日期*:*注:需要同学用蓝色或黑色钢笔或圆珠笔手工签写!有符号5位整数除法器设计与制作一、实验目的进一步掌握现代大规模可编程数字逻辑器件的开发应用方法。

二、提供的实验条件1.软件:MAX-plusⅡ。

2.仪器和设备:计算机、EDA实验箱。

三、实验内容设计一个两个五位数相除的整数除法器。

用发光二极管显示输入数值,用7段显示器显示结果。

除数和被除数分两次输入。

四、实验报告具体内容1.顶层文件图:仿真时序图:2.输入模块:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY inputs ISPORT( ip:in std_logic_vector(4 downto 0);clk1,clk2:in std_logic;beichu,chushu:out std_logic_vector(4 downto 0));END inputs;ARCHITECTURE shuju OF inputs ISBEGINPROCESSBEGINif clk1='1'thenbeichu<=ip(3 downto 0);end if;if clk2='1'thenchushu<=ip(3 downto 0);end if;END PROCESS;END shuju;功能:clk1=1时的输入值为被除数;clk2=1时的输入值为除数。

模块图:仿真时序图:3.除法器模块:源代码:LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_unsigned.all;ENTITY miaomiao ISPORT(beichu,chushu : IN STD_LOGIC_VECTOR( 4 downto 0); yushu : OUT STD_LOGIC_VECTOR( 3 downto 0);shang : OUT STD_LOGIC_VECTOR ( 4 downto 0));END miaomiao;ARCHITECTURE a OF miaomiao ISSIGNAL remain0,remain1,remain2,remain3 :STD_LOGIC_VECTOR( 6 downto 0);SIGNAL diver0,diver1,diver2,diver3 : STD_LOGIC_VECTOR( 6 downto 0);BEGINPROCESS (beichu,chushu)BEGINshang(4)<=beichu(4) xor chushu(4);remain3 <= "000" & beichu(3 downto 0);diver3 <= chushu(3 downto 0) & "000";if remain3 >= diver3 thenshang(3) <= '1';remain2 <= diver3;elseshang(3) <= '0';remain2 <= remain3;END IF;diver2 <= "0" & chushu(3 downto 0) & "00";if remain2 >= diver2 thenshang(2) <= '1';remain1 <= remain2 - diver2;elseshang(2) <= '0';remain1 <= remain2;END IF;diver1 <= "00" & chushu(3 downto 0) & "0"; if remain1 >= diver1 thenshang(1) <= '1';remain0 <= remain1 - diver1;elseshang(1) <= '0';remain0 <= remain1;END IF;diver0 <= "000" & chushu(3 downto 0);if remain0 >= diver0 thenshang(0) <= '1';yushu <= remain0 - diver0;elseshang(0) <= '0';yushu <= remain0(3 downto 0);END IF;END PROCESS;END a;模块图:仿真时序图:说明:符号通过异或实现:两符号相同,商符号为0;两符号相异,商符号为1.利用移位相减方法实现除法:先将被除数左边补三个零,除数右边补三个零,补成两个七位数,除数的第一于是,原被位对应除数的最后一位。