基于IEEE1149.1标准的通用测试机的设计与实现

jtag接口原理

jtag接口原理JTAG接口原理是一种基于IEEE Std 1149.1标准的测试和调试接口,用于在集成电路(IC)中进行电气测试、故障诊断和编程操作。

该接口是由四根线(TCK、TMS、TDI、TDO)和一根地线(GND)组成,可以通过这些线连接到目标IC的测试端口。

TCK(Test Clock)线提供时钟信号,用于同步数据的传输和操作的执行。

TMS(Test Mode Select)线用于控制JTAG状态机的状态转换,包括从一个状态进入另一个状态。

TDI(Test Data Input)线用于向目标IC发送测试数据或编程数据。

TDO (Test Data Output)线用于从IC中读取测试数据或编程数据。

在JTAG接口中,目标IC被组织成一系列的“链”或“路径”,每个路径上可能包含一个或多个JTAG设备。

这些设备通过将TDO线接到下一个设备的TDI线来实现级联连接。

这样,通过JTAG接口,可以从一个设备向另一个设备传递数据。

JTAG接口的工作原理基于状态机,在每个时钟周期,TMS线的状态决定当前的JTAG状态。

状态机根据状态,决定执行相应的操作,例如向目标IC发送指令、读取/写入数据、控制目标IC的输入/输出引脚等。

使用JTAG接口,可以进行多种功能,如电路故障诊断、芯片级别的板级测试和编程操作。

在调试过程中,JTAG接口可以用于读取目标IC中的内部寄存器值、存储器数据等,帮助分析程序执行状态和故障定位。

总之,JTAG接口是一种强大的测试和调试工具,通过发送和接收数据,在目标集成电路中实现测试、故障诊断和编程操作。

它提供了一种方便、高效的方式来访问目标IC的内部结构和状态,对于电子产品的开发、制造和维修具有重要意义。

boundaryscan应用实例 -回复

boundaryscan应用实例-回复什么是boundary scan技术?Boundary scan技术,又称JTAG(Joint Test Action Group)技术,是一种用于芯片级电路板测试和诊断的技术。

它使用了IEEE标准1149.1定义的边界扫描链(Boundary Scan Chain),通过在电路板上的闩锁功能来实现对芯片上的引脚的测试和调试。

Boundary scan技术的原理和功能如何工作?Boundary scan技术的原理基于一种边界扫描链结构(Boundary Scan Chain),该链将所有芯片引脚连接起来形成一个环。

这个环具有使能信号和测试控制信号,通过这些信号的控制,可以将测试数据从一个引脚传输到另一个引脚,实现对芯片引脚的测试和调试。

Boundary scan技术的功能主要有以下几个方面:1. 电路连通性测试:通过boundary scan技术,可以检测和诊断电路板上信号线的连通性是否良好,以及是否存在断路和短路。

2. 引脚功能测试:通过boundary scan技术,可以实时测试和诊断芯片引脚的功能是否正常。

这对于芯片级的调试和故障排除非常有用。

3. 元件配置和诊断:通过boundary scan技术,可以识别和配置电路板上的各种元件,例如存储器、逻辑门等。

这可以帮助工程师更好地了解电路板的组成和功能。

4. 容错性检查:通过boundary scan技术,可以检查电路板上的信号线是否遵循电气特性,例如正确的电阻和电容值。

这对于确保电路板的稳定性和可靠性至关重要。

Boundary scan技术的应用实例1. 电子设备制造:Boundary scan技术可以在生产线上用于测试和验证电子设备的电路板,以确保其质量和可靠性。

它可以有效地检测和排除电路板上的连通性问题和故障,提高生产效率和产品质量。

2. 电路板维修:当电子设备发生故障时,boundary scan技术可以用于定位和修复故障点。

探讨基于JTAG技术嵌入式系统测试各个阶段

探讨基于JTAG技术的嵌入式系统测试的各个阶段更新于2018-09-21 07:00:37文章出处:互联网IEEE1149.1边界扫描测试标准嵌入式测试JTAG技术引言IEEE 1149.1边界扫描测试标准(通常称为JTAG 1149.1或"dot 1">是一种用来进行复杂IC与电路板上的特性测试的工业标准方法,大多数复杂电子系统都以这种或那种方式用到了IEEE1149.1(JTAG>标准。

为了更好地理解这种方法,本文将探讨在不同年代的系统开发与设计中是如何使用JTAG的,通过借助过去有关JTAG接入的经验或投入,推动设计向新一代发展。

b5E2RGbCAP大多数复杂电子系统都以这种或那种方式用到了IEEE1149.1(JTAG>^准。

如果系统采用的是复杂FPGA或CPLD那么几乎可以肯定这些硬件是通过JTAG端口设置的。

如果系统利用仿真工具来调试硬件或软件,那么仿真工具也很可能是通过JTAG端口与微处理器对话。

而且,如果系统中采用了球栅阵列(BGA:封装的IC,那么JTAG也是测试BGA器件与底层印制电路板之间连接的最有效方法。

P1Ea nqFDPw支持EEE 1149.1边界扫描测试标准的IC与电路板都具备一个支持JTAG测试的4线串行总线(第5条线为可选的复位线>-TDI(测试数据输入>、TDO测试数据输出>、TMS测试模式选择>与TCK测试时钟〉。

该总线主要支持对焊点、电路板过孔、短路和开路等连接进行结构测试。

此外,许多CPLD和FPGA制造商也将JTAG作为其器件在系统编程与配置的标准方法。

JTAG不但支持结构(互连〉测试,如今还是一种用于在系统级实现配置、编程以及混合信号测试的标准方法。

DXDiTa9E3d但大多数设计团队都在新设计中对JTAG的应用更倾向于不一步到位,而是以一种更易掌控的方式慢慢转为全面利用JTAG接口。

有些团队规则(discipline>中广泛利用了JTAG 接口,有些则只利用了其中很有限的一部分。

jtag接口

JTAG接口1. 简介JTAG(Joint Test Action Group,联合测试行动小组)接口是一种用于测试和调试电子设备的标准接口。

它可以提供对设备内部的信号和状态进行非侵入性访问,方便测试和调试工作的进行。

2. JTAG接口的原理JTAG接口基于IEEE 1149.1标准而设计,通常由以下几个主要部分组成:2.1 TAP控制器TAP(Test Access Port,测试访问端口)控制器是JTAG接口的核心部分,它负责控制JTAG链上的各个设备进行测试和调试操作。

TAP控制器包含四个主要状态:Test-Logic-Reset (测试逻辑复位)、Run-Test/Idle(运行测试/空闲)、Select-DR-Scan(选择数据寄存器扫描)和 Select-IR-Scan(选择指令寄存器扫描)。

2.2 数据寄存器和指令寄存器JTAG接口通过数据寄存器和指令寄存器实现对设备内部信息的读取和写入。

数据寄存器用于存储设备内部的数据,指令寄存器用于存储控制设备的指令。

2.3 JTAG链JTAG链是由多个设备连接在一起形成的链路,每个设备都有一个JTAG接口用于进行测试和调试操作。

通过JTAG链,可以对所有设备进行统一的控制和访问。

3. JTAG接口的应用JTAG接口广泛应用于电子设备的测试和调试领域。

它可以用于以下几个主要方面:3.1 片上自检(BIST)JTAG接口可以用于进行片上自检(Built-In Self-Test,BIST)操作,通过读取和分析测试模式下设备内部的信号和状态,检测设备是否正常工作。

3.2 调试模式JTAG接口可以进入设备的调试模式,可以对设备进行单步调试、断点调试等操作,方便开发人员进行程序调试和故障排查。

3.3 仿真和验证JTAG接口还可以用于仿真和验证工作。

通过JTAG接口,可以将外部测试模式下的信号加载到设备内部进行仿真和验证工作。

4. JTAG接口的优势与其他调试和测试接口相比,JTAG接口具有以下几个显著的优势:4.1 非侵入性访问JTAG接口可以在不破坏原有电路功能的情况下,对设备内部信号进行读取和分析。

(新版)嵌入式系统设计师(中级)考试题库(含答案)

(新版)嵌入式系统设计师(中级)考试题库(含答案)单选题(总共129题)1.以下4种路由中,______路由的子网掩码是255.255.255.255。

A、远程网络B、静态C、默认D、主机答案:D解析:主机路由的子网掩码是255.255.255.255。

网络路由要指明一个子网,所以不可能为,默认路由是访问默认网关,而默认网关与本地主机属于同一个子网,其子网掩码也应该与网络路由相同,对静态路由也是同样的道理。

2.执行下面C语言程序段的结果是()。

main(){intx=l,a=l,b=l;switch(x){case0:b++;case1:a++;case2:a++;b++;}printf(”a=%d,b=%d“,a,b);}A、a=2,b=2B、a=3,b=2C、a=2,b=lD、a=3,b=3答案:B解析:switchcase语句语法,当匹配到了一个case条件,会从该条件开始往下执行其余所有条件语句,不再进行判断,因此这里x=1匹配到了case1,其会执行case1及case2的语句。

3.下面的一段C程序中,循环体语句______退出循环。

unsignedcharn;inttot al;n=50;while(n-->=0)?{total+=n;}A、执行49次后B、执行50次后C、执行51次后D、死循环,不会答案:D解析:本题考查C语言编程的基本知识。

在本题中考生需注意unsignedchar的用法,因为n为无符号整型,永远不会为负数,所以循环语句会陷入死循环,不会退出循环。

在实际的软件编程中一定要小心判断条件是否可达到。

4.以下关于直接存储器访问(DMA)的叙述中,错误的是()。

A、DMA是一种快速传递大数据的技术B、DMA将传输的数据从一个地址空间复制到另一个地址空间C、DMA数据传送过程中,由CPU和DMA控制器共同控制D、在DMA控制器控制下,主存和外设之间直接交换数据答案:C解析:DMA直接在主存和外设之间建立一条数据传输通道,无需CPU来控制传输过程,是一种快速传递大数据块的技术。

基于IEEE Std 1149.1-2001标准的TAP控制器设计

边 界扫 描测试 技术 在降低 产 品测试 成本 , 提高 产 品质 量 和可靠 性 以及 缩 短 产 品上 市 时 间 等方 面 有 显著 的 优点 .所 以 , 界扫 描技术 一 提 出就 受到 边 电子行 业 的关注 和广为 接受 , 目前 已得 到 了很 多应 用 ¨ .现在 , 一些 国际性 的大公 司 如 C rl . A oei J G, sT

A elg , getCso等公 司 已经 致 力 于开 发 满 euoi A in,i e l c

足相 关 测 试协议 的测试仪 器 和集成 电路 .

获 等功 能 .这 些 功 能 的实 现 是 由测 试控 制 逻 辑 来

控 制的 .测试 控制 逻辑 由两 条信号线 驱动 : 试 方 测 式 选 择 线 ( M ,T s M d e c e

要求 I 至少 有 四个 可利 用 的测 试 管脚 , 将 它 C中 或 们 附加到 其他 的功 能管 脚上 . 边界 扫描测 试技 术 的工作 原 理 是 :1 G 测试 J’ A 仪利 用一 个 四线 测 试接 口, 测试数据 以串行 方式 将 由 T I 人 到 边 界扫 描 寄 存 器 中 , 过 T D输 通 MS发 送

(C T K,T s Cok 线 .所 以 , et lc ) 整个 边 界 扫 描 测 试

1 关 于 I E t 9 1—2 0 E E Sdl4 . 1 01

19 9 0年 的 14 . 9 1标 准 并 没有 将 该 体 系 结 1 构 中 的问题 考虑得 很周 到 .在 后 来 的 1 年 中 , 0余 IE E E计算 机 协会对 该协议 进行 了不 断 的修订 和补 充 . 9 9年 , 布 了 I E t 14 . 19 发 E E Sd 19 4标 准 , 主要 解 决模 拟集 成 电 路 的可 测 试 性 问题 .由于 在 混 合 系统 中 , 拟模 块 和数 字模 块有 着 符种关 系 ,E E 模 IE 计 算 机协 会 又 对 14 . 19 1标 准进 行 了 修订 , 就 是 这 下 面 使用 到 的 I E tl4 . — 0 1 准 . E E Sd 9 1 2 0 标 1

Boundary Scan测试原理及实现

什么是边界扫描(boundary scan)?Boundary Scan测试原理及实现JTAG标准的IC芯片结构IEEE 1149.1 标准背景JTAG什么是边界扫描(boundary scan)?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器 (TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的用户特殊寄存器。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)TMS,TCK,TRST构成了边界扫描测试端口控制器(TAP controller),它负责测试信号指令的输入,输出,指令解码等,TAP controller是一个16位的状态机,边界扫描测试的每个环节都由它来控制,所以要对TAP controller有一个比较清楚的了解。

在后续的文章中还会向大家介绍边界扫描的其它方面。

边界扫描为开发人员缩短开发周期,并且提供良好的覆盖率和诊断信息。

JTAG协议规范1149.1和1149.7

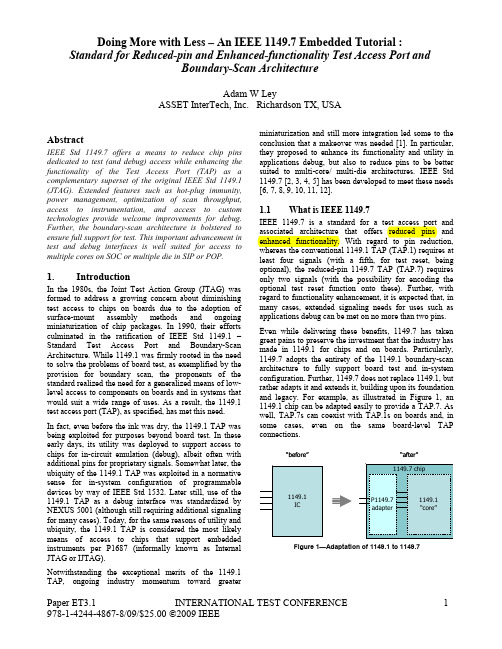

Doing More with Less – An IEEE 1149.7 Embedded Tutorial : Standard for Reduced-pin and Enhanced-functionality Test Access Port andBoundary-Scan ArchitectureAdam W LeyASSET InterTech, Inc. Richardson TX, USAAbstractIEEE Std 1149.7 offers a means to reduce chip pins dedicated to test (and debug) access while enhancing the functionality of the Test Access Port (TAP) as a complementary superset of the original IEEE Std 1149.1 (JTAG). Extended features such as hot-plug immunity, power management, optimization of scan throughput, access to instrumentation, and access to custom technologies provide welcome improvements for debug. Further, the boundary-scan architecture is bolstered to ensure full support for test. This important advancement in test and debug interfaces is well suited for access to multiple cores on SOC or multiple die in SIP or POP.1.IntroductionIn the 1980s, the Joint Test Action Group (JTAG) was formed to address a growing concern about diminishing test access to chips on boards due to the adoption of surface-mount assembly methods and ongoing miniaturization of chip packages. In 1990, their efforts culminated in the ratification of IEEE Std 1149.1 – Standard Test Access Port and Boundary-Scan Architecture. While 1149.1 was firmly rooted in the needto solve the problems of board test, as exemplified by the provision for boundary scan, the proponents of the standard realized the need for a generalized means of low-level access to components on boards and in systems that would suit a wide range of uses. As a result, the 1149.1 test access port (TAP), as specified, has met this need.In fact, even before the ink was dry, the 1149.1 TAP was being exploited for purposes beyond board test. In these early days, its utility was deployed to support access to chips for in-circuit emulation (debug), albeit often with additional pins for proprietary signals. Somewhat later, the ubiquity of the 1149.1 TAP was exploited in a normative sense for in-system configuration of programmable devices by way of IEEE Std 1532. Later still, use of the 1149.1 TAP as a debug interface was standardized by NEXUS 5001 (although still requiring additional signaling for many cases). Today, for the same reasons of utility and ubiquity, the 1149.1 TAP is considered the most likely means of access to chips that support embedded instruments per P1687 (informally known as Internal JTAG or IJTAG).Notwithstanding the exceptional merits of the 1149.1 TAP, ongoing industry momentum toward greater miniaturization and still more integration led some to the conclusion that a makeover was needed [1]. In particular, they proposed to enhance its functionality and utility in applications debug, but also to reduce pins to be better suited to multi-core/ multi-die architectures. IEEE Std 1149.7 [2, 3, 4, 5] has been developed to meet these needs [6, 7, 8, 9, 10, 11, 12].1.1What is IEEE 1149.7IEEE 1149.7 is a standard for a test access port and associated architecture that offers reduced pins and enhanced functionality. With regard to pin reduction, whereas the conventional 1149.1 TAP (TAP.1) requires at least four signals (with a fifth, for test reset, being optional), the reduced-pin 1149.7 TAP (TAP.7) requires only two signals (with the possibility for encoding the optional test reset function onto these). Further, with regard to functionality enhancement, it is expected that, in many cases, extended signaling needs for uses such as applications debug can be met on no more than two pins. Even while delivering these benefits, 1149.7 has taken great pains to preserve the investment that the industry has made in 1149.1 for chips and on boards. Particularly, 1149.7 adopts the entirety of the 1149.1 boundary-scan architecture to fully support board test and in-system configuration. Further, 1149.7 does not replace 1149.1, but rather adapts it and extends it, building upon its foundation and legacy. For example, as illustrated in Figure 1, an 1149.1 chip can be adapted easily to provide a TAP.7. As well, TAP.7s can coexist with TAP.1s on boards and, in some cases, even on the same board-level TAP connections.“before”“after”Figure 1—Adaptation of 1149.1 to 1149.71.2IEEE 1149.7 Key ObjectivesThe key objectives for 1149.7 fall broadly into three categories – system architecture, applications debug, and legacy infrastructure (to include test).Benefits for system architecture derive from the appropriate accommodation of multiple on-chip embedded TAP Controllers (EMTAPC), the reduction of pins, the adoption of glue-less star topology, independence from CPU/debug technology, and provisions for power management. Where intellectual property (IP) blocks may each contain EMTAPCs, multiples of these may be accommodated on a complex system-on-chip (SOC). While reduced pin count has inherent value with respect to miniaturization, consider as well that, in combination with the star topology, fewer pins better support the new 3D packaging methodologies such as system-in-package (SIP). These typically involve the stacking of die as shown in Figure 2; conversely, a daisy-chaining implementation is not only more difficult but also is not 1149.1 compliant. Of course, the same can be said for package-on-package (POP). Further, independence from particular CPU/debug technologies supports similar integrations even where chips may incorporate CPU IP from multiple sources. Facilities that permit the test logic to enter power-down modes support increasingly aggressive power management requirements.Figure 2—Star topology for a 3-die SIPFor applications debug, the TAP.7 provides advanced capability that reduces or eliminates the need for signaling beyond the two wires. Extensions provided include robust hot connect, increased throughput by way of scan optimization, higher operating frequency, and transport of background instrumentation data and/ or custom protocols. Of course, independence from CPU/debug technology also accrues here because uniform tool sets can support chips with heterogeneous CPUs.Finally, as concerns the legacy infrastructure, the objectives are two-fold – first, honor 1149.1 by preserving the test infrastructure that has been built up around it and on which the industry depends; and second, maintain a level of compliance such that existing intellectual property in chips, on boards, and in debug and test systems (DTS) can be adapted at low cost.2. Overview/ How it WorksAt the highest level of abstraction, 1149.7 provides for a chip-level TAP.7 Controller that bridges the conventional 1149.1-accessible System Test Logic (STL) to the four (five) or two (three) wires of the chip-level TAP.7 (the test reset signal is optional in either case). The STL has its own 1149.1 chip-level TAP Controller (CLTAPC) and all of the associated test logic architecture, including a chip-level boundary-scan register and related EXTEST, PRELOAD, and SAMPLE instructions.Seeking to extend 1149.1 in a compatible fashion, 1149.7 starts with the observation that the TAP Controller (TAPC) at the core of 1149.1 is a two-wire control means, even in the conventional series topology, as shown in Figure 3.TCK TDITDOTMSFigure 3—Conventional series topology, highlighting the starwiring for TCK/TMSPer 1149.1 convention, the starred TCK/TMS can only advance the TAPC state, which in turn invokes TDI/TDO for scan operations, but, absent instruction register scans, does not change the mode of the test logic. Thus, the key concept of 1149.7 continues with the observation that control extensions might be overlaid on sequences of TAPC states (more details on this later).Thus, 1149.7 adds its own commands and registers on which the other layers of extended functionality are based. These additional layers add scan formats, direct addressability, packetization of scan data (TMS, TDI, and/ or TDO information) onto the TMS wire (hence, re-designated TMSC), and finally packetization of non-scan information onto TMSC to provide for transport of background and/ or custom data.As such, 1149.7 supports a number of capability classes (six in number, designated as T0 - T5). So the TAP.7 Controller is configurable to support the required capability for a given implementation. The primary functional units are illustrated in Figure 4 and are designated as follows: Advanced Protocol Unit (APU), Extended Protocol Unit (EPU), Pin-Sharing Logic (PSL), and Reset and Selection Unit (RSU). The manner in which these items are invoked (or not) for given capability classes will be described in subsequent sections.TDI(C)nTRST EPU TAP.7TDO(C)TCK(C)TMS(C)TAP.7 ControllerFigure 4—Notional view of the 1149.7 architecture2.1 Capability classesRegardless of which capability class is implemented, a given TAP.7 must implement all of the mandatory features of its own class as well as those of all lower-numbered classes (T0 < T5). The classes are generally considered in two primary groupings: those which extend 4-wire operation (T0 – T3) and those which provide the reduced-pin, 2-wire operation (T4 – T5).T0–foundationAs the foundation of all TAP.7 capabilities, T0 begins with 1149.1-Specified behavior, such that the T0 STL is 100 percent compliant to 1149.1 including provisions for the mandatory chip-level boundary-scan architecture. With 1149.7 T0, the chip-level device identification register becomes mandatory.Of the TAP.7 Controller elements shown in Figure 4, only the RSU is permitted as an option; the other items are reserved for higher classes.Where the RSU is implemented, this would be done, as for any other class, to permit Escape Sequences and/ or Selection/Deselection Alerts to be available to manage the sharing of TAP.7 signaling across technologies and topologies. When the TAP.7 Adapter TAPC (ADTAPC) is deselected, the CLTAPC will be parked. These topics will be addressed in greater detail with T3 where the RSU becomes mandatory.Of particular note, even where the chip has multiple EMTAPCs, as might be the case for a complex SOC that implements a mix of several core IP blocks, the T0 STL shall provide 1149.1-Specified behavior from the Test-Logic-Reset TAPC state. 1149.7 identifies several means by which EMTAPCs can be selected under the control of the CLTAPC. A further method is defined for managing multiple die-level TAPCs in a similar manner for SIP. T1–commands and registersWith T1, the 1149.7 mechanism providing extended control by way of TCK/TMS is invoked to access 1149.7 commands and registers. These functions pertain to the EPU as illustrated in Figure 4. So, the EPU block of the TAP.7 Controller is present for T1. Otherwise, excepting the RSU, as for T0, all other blocks are reserved for higher classes.As described earlier, the extended control mechanism operates without disruption to the conventional 1149.1 TAPC state machine. Rather, it uses a particular state sequence, which is benign to normal 1149.1 operations, to initiate 1149.7-defined action.The state sequence of interest is known as a zero-bit DR scan (ZBS) and these are to be operated only while all of the CLTAPCs in the selected topology operate BYPASS or IDCODE so as to ensure that they do not disrupt normal system operation. In fact, ZBS detection is validated only when no IR scans have intervened since the last occurrence of the Test-Logic-Reset TAPC state.The progression of states that is recognized as a ZBS is illustrated in Figure 5.ScanCapture-DRExit1-DRExit2-DRUpdate-DRShift-DRPause-DR1110111abFigure 5—Zero-bit scan (ZBS)There are actually two different paths, labeled as “a” and “b” in Figure 5, that can implement a ZBS. In either case, the state sequence of interest is defined as follows: from the Select-DR-Scan TAPC state, proceed to the Update-DR TAPC state without passing the Shift-DR TAPC state. From the Test-Logic-Reset TAPC state, wherein the ZBS count is set to zero, the extended control mechanism is initiated when at least two ZBSs are detected before a subsequent non-zero-bit DR scan, which locks the ZBS count. A locked ZBS count of two provides access to the 1149.7 commands and registers. Locked ZBS counts greater than two access higher control levels that will not be detailed here.Once the ZBS count is locked, and a control level set, it is only unlocked when the control level is exited by entry to either the Select-IR-Scan or Test-Logic-Reset TAPC states or by certain 1149.7 commands and events that are used to synchronize T4 and T5 operations.At control level 2, commands are recognized, without the use of TDI/TDO pins, by counting the number of TCK(C)ticks in the Shift-DR TAPC state for two scans that immediately follow the completion of the non-zero-bit DR scan that locked the ZBS count. Each of these two primary command words is coded in 5 bits, ensuring that these counts need not exceed 31. All commands include two such parts for a total code length of 10 bits. In most cases, the command and register operations are concluded in these two parts but in some (only three) special cases a third part (a DR scan of a length determined by the control register addressed by the command) is required.T1 mandates a given minimum set of such commands and the registers that they address. Additionally, some commands, registers, and associated functions are optional, notably those that invoke directed test reset generation and request for functional reset.Additionally, T1 provides for power management through four modes of power control for the test logic. These four modes are: allow power down if TCK stops at logic one for more than 1 ms, allow power down if TCK stops at logic one for more than 1 ms in the Test-Logic-Reset TAPC state, allow power down if the device is in the Test-Logic-Reset TAPC state, and do not allow power down (the test logic is always powered).Given that a power-down mode is supported, the test logic is directed to resume powered operation when the Run-Test/Idle TAPC state is forced for at least 100 ms and at least 3 TCK(C) ticks.T2–scan formatsThe 1149.7 scan formats are introduced in T2. A T2 TAP.7 supports JScan0 – JScan2; other scan formats are reserved for higher classes.Of the TAP.7 Controller elements shown in Figure 4, for T2, as for T1, only the EPU is mandatory with the RSU permitted as an option; the other items are reserved for higher classes. For T2 versus T1, the EPU adds the commands and registers associated with the scan formats. As regards the function of these scan formats, JScan0 provides 1149.1-Specified behavior while JScan1 provides for the deselection of the CLTAPC in favor of a 1-bit scan path (so-called Super Bypass) that is active for IR scans as well as DR scans and JScan2 provides for activation/deactivation of the Super Bypass according to the value of an 1149.7 register.A T2 TAP.7 can opt either for JScan0 or JScan1 as its startup behavior. The latter case is described as providing hot-plug immunity since it should permit live connection (or disconnection) of the TAP.7 signals to be non-disruptive to the test logic.T3–direct addressabilityFinally, with T3, the star topology (4 wire), as in Figure 6, is supported. This comes by adding the means for direct addressability and the JScan3 scan format that provides for scans to star-4 topologies.Figure 6—Star-4 topologyOf the TAP.7 Controller elements shown in Figure 4, T3 adds the RSU as a mandatory element in addition to the EPU. For T3 versus T2, the EPU adds the commands and registers associated with direct addressability. Note that for T3, the TDI and TDO signals are re-designated as TDIC and TDOC, respectively.Concerning the RSU for T3, it is required to implement Escape Sequences for reset and for selection/ deselection and may optionally implement Selection and Deselection Alerts. Escape Sequences involve the detection and counting of a number of edges on TMS(C) driven while TCK(C) is held at logic 1. The count of such edges determines the action to be taken in response to the Escape Sequence. Alerts are specific predefined sequences of 128 bits as driven on TMS(C).The resource invoked for support of direct addressability is the TAP.7 Controller Address (TCA), as shown in Figure 7. The values corresponding to DEVICE_ID are inherited from the 1149.1 device identification register capture value for the CLTAPC. The assignment of the NODE_ID is made by some implementation-specific means that is not defined by 1149.7. The NODE_ID serves to distinguish multiple TAP.7s on a given topology branch where they are of the same device type.Figure 7—TAP.7 Controller Address (TCA)A key provision required to facilitate scans to the star-4 topology is the prevention of drive conflict on TDOC. The JScan3 format is managed so that when multiple TAP.7 Controllers are requested to participate, then drive on TDOC will be inhibited.As discussed in more detail in 4.1, test applications require the ability to coordinate the simultaneous entry of all devices of interest into and/ or through the Capture-xR, Update-xR, and Run-Test/Idle TAPC states. At first glance, the star topology would seem not to support this requirement. But in addition to the JScan3 scan format, T3 adds the Scan Selection Directives (SSD) to deal with this matter. The SSDs make use of Pause-xR TAPC states as parking states to which simultaneous scan captures aredirected and from which simultaneous scan updates are directed. Scan shift operations, as necessitated by the star topology are done on a device-by-device basis and are both directed from and to the Pause-xR TAPC states. T4–packetization of scan data (2-pin scan formats)With T4, a number of additional scan formats are added to support the advanced protocol, which is operated on two pins. The TCK/TMS pins are re-designated as TCKC/TMSC, respectively. The corresponding star-2 topology is illustrated in Figure 8. Note that TMSC is bidirectional.TMSCTCKCFigure 8—Star-2 topologyOf course, these additions require the provision of the APU of Figure 4. As well, since the TDIC/TDOC pins are optional since they are not used for 2-pin operation, where they are provided the PSL also becomes an option. Where a T4 TAP.7 does not provide the TDIC/TDOC pins in any configuration, it is described as narrow and designated as T4N. Where a T4 TAP.7 does have a configuration that provides the TDIC/TDOC pins, it is described as wide and designated as T4W.One of the more basic scan formats that supports the advanced protocol is OScan1. The serialization of the scan packet for OScan1 is illustrated in Figure 9. As shown, the TDI bit information is inverted. Also, for each cycle in which the TDO bit appears it is driven from the selected device in the target system back to the DTS.TCKCTMSC stateFigure 9—Scan packet serialization – OScan1Other scan formats in the OScan series provide for optimizations in which the scan packets omit bits that can be known to carry no significant information. An example worth noting is the OScan7 format which is optimized for downloads from the DTS to the target system. For OScan7, as illustrated in Figure 10, only the TDI bit information is included in the packets sent during Shift-xR TAPC states.TCKC nTDI nTDI nTDI nTDI nTDI nTDI nTDI nTDI nTDITMSC Shift-xRShift-xRShift-xRstateFigure 10—Scan packet serialization – OScan7Further performance optimization that can be obtained for T4 is by invoking falling-edge sampling for TMSC which, presuming hold times still can be met, delivers a degree of improvement in setup times that would allow the TCKC frequency to be increased (perhaps doubled).T5–transport of non-scan data (2-pin mode)At the top of the classes, T5 offers the capability to interleave transfers of non-scan data among the scan transfers. This is referred to as transport and has two variants – background data transport (BDX) and custom data transport (CDX).Both types of transport can use any combination of Run-Test/Idle, Pause-xR, and Update-xR TAPC states after which to insert transport packets. The distinction is that, whereas BDX has fixed allocation of I/O bandwidth available to the chip-level data channel, CDX has a custom allocation of I/O bandwidth as determined/ defined by the chip-level unit.2.2 Selection hierarchyWhile some aspects of the selection hierarchy have been described above, some additional detail is warranted as it is a key aspect of the 1149.7 system architecture.In general, where selection is enabled within the hierarchy, those items not selected are effectively offline/ parked and respond only to particular selection requests on the TAP.7 signaling. Those that are selected are online and respond to the TAP.7 signaling according to the protocols for which they are configured.Five levels in the selection hierarchy are elaborated below. For each level of the hierarchy, one or more selection mechanisms may pertain. - TechnologyWhere the 1149.7 technology can be placed offline, the TAP.7 signaling can be shared with other technologies- TopologyW here the constituent 1149.7 devices can be placed offline (a function required for T3 and above), the TAP.7 signaling can be shared among any topology branches, whether series, star-2, or star-4 - Adapter (i.e., ADTAPC)1149.7 devices comprising a selected topology branch will share TAP.7 signaling and, where the topology branch is star-2 or star-4, a given device may be selected for a given operation- Chip (i.e., CLTAPC)For a selected ADTAPC, the CLTAPC may be offline and will require selection when it must be operated- Core (i.e., EMTAPC)For a selected CLTAPC, given EMTAPC(s) of interest may be offline and will require selection when it (they) must be operated3.Implications for DebugIn many respects, 1149.7 was defined by and for the debug community. Thus, many of the implications, considerations, and supporting features have already been addressed in the elaboration of the basic 1149.7 functions as described above. Still some of these bear specific mention in this context.3.1Debug considerationsChief among the considerations for debug are ease and efficiency. Of course, these unfold across multiple dimensions and are often intertwined.EaseThe highest degree of visibility and control is required to drive the analysis tools that can get to the bottom of thorny problems that arise in today’s multi-threaded, multi-core, real-time embedded systems. 1149.7 promises to bring value to this equation by consolidating debug access for multiple cores onto a smaller number of chip pins.Other features tending toward ease of debug are the hot-plug immunity and system interrogation.EfficiencyCertainly 1149.7 enjoys a performance boost relative to 1149.1 with its various optimizations for scan throughput and its ability to improve link utilization by using otherwise idle non-scan states to transport background instrumentation data.3.2Debug featuresAs one would expect, 1149.7 brings a wealth of features to address debug ease and efficiency.Access consolidationSeveral aspects of the 1149.7 system architecture provide for access consolidation: management of EMTAPCs (T0), star topology (T3), pin reduction (T4N/T5N), and capability for the TAP.7 to transport background data and custom protocols (T5). All of these result in making debug instrumentation more accessible and, hence, easier to use. Hot-plug immunityLive connection without system disruption is vital and is enabled by the offline at startup (T3 or any with RSU) and Super Bypass at startup (T2) features. System interrogationA method for topology interrogation (T3) is provided and enumeration of controllers can be made by undirected allocation of Controller IDs (CID) (T3), as in Figure 11. These features allow the system architecture to be discovered by the debug tool at connect time.Each participating chip drives its AT[n]on wired-OR basis (logic 1 inactive)All supporting chips without CID participate;chips with a CID do not participate.For each participating chip, its aliasing targetAT[35:0] = TCA[34:0] + 0Final n?Each chip that detects that itsAT[n] != TDO drops outNext nThe chip that matched all 36 bitsof its AT to all 36 bits of TDOwins and gets the CIDFigure 11—CID Allocation, Undirected Optimization of scan throughputPerhaps above all, 1149.7 offers a great number of opportunities to optimize scan throughput. Super Bypass (T2) results in shorter scan chains for series topology. Star topology (T3) offers direct addressability and, hence, scan operation in only the target of interest.Advanced protocol (T4) offers still further improvements based on scan packet optimization on one hand and falling-edge timing (and thereby clock doubling) on the other.Improved link utilizationBDX and CDX (T5) allow the link to be used for transport of instrumentation data even during non-scan states, which would otherwise be idle.4.Implications for TestWhile 1149.7 primarily has been developed for the benefit of applications debug, it also has gone to considerable lengths to ensure that the test legacy of the original 1149.1 is honored. Among the several test-related provisions are the scan selection directives that ensure update/ capture/ run-test synchronization and the definition of suitable test languages.4.1Test considerationsWhile 1149.7 does not change radically how 1149.1 boundary scan/ test is being used today, there are some new considerations for test that arise with the 1149.7 architecture. Primary among these are the divergence inscan-state sequencing and series/star interoperability. Other considerations worth mention are hierarchical navigation, power control, and large-system applications. Scan-state sequencingThe typical test application has requirements for scan-state sequencing that necessitate coordination of application of stimuli across multiple distinct components (with their own boundary-scan registers) on a given unit under test (UUT). Consider the case where several components have distinct 3-state outputs on a shared wire junction. If the distinct output control cells in each of these components were not updated in a coordinated fashion, a contention could be present on the shared wire. The simplest means of such coordination is to ensure that all components pass simultaneously through the Update-DR TAPC state. As well, while it might not be necessary in some cases, the coordination of the acquisition of response generally also is required (or at least preferred). At the least, where specific response to given stimuli is required, the distinct responses for each component involved must all be acquired before the applied stimulus is changed. Here again, the simplest means for such is to ensure that all components pass simultaneously through the Capture-DR TAPC state (in fact, simultaneity may be strictly required in some special cases).Some test applications, such as the testing of advanced digital networks per IEEE Std 1149.6, have an additional requirement that all components participating in such testing must pass simultaneously through the Run-Test/Idle TAPC state.Conventional scan sequencing for test applications presuming series topology is illustrated in Figure 12.Run-Test-Idle1Select-DR-ScanCapture-DRExit1-DRExit2-DRUpdate-DRShift-DRPause-DR110111Figure 12—Scan-state sequence (conventional) for testapplications, series topologyThis conventional scan-state sequence can be broken down as follows:- (in yellow) all components on the UUT (series topology) pass through the Capture-DR TAPC state wherein responses (to a previously applied stimulus) are acquired in concert- (in red) all components on the UUT (series topology) enter and remain in the Shift-DR TAPC state until all responses have been exported and all new stimuli have been imported- (in blue) all components on the UUT (series topology) pass through the Update-DR TAPC state wherein new stimuli are applied in concert- (in grey) all components on the UUT (series topology) dwell in/ pass through the Run-Test/Idle TAPC state wherein transient stimuli may be generated in concert The divergence introduced by the 1149.7 star topology is that, due to shared wiring of TDIC and TDOC for star-4 or TMSC for star-2, only one component may be operated in the Shift-DR TAPC state at a time.Fortunately, we can take from the above discussion that the Shift-DR TAPC state is actually neutral to the requirements of the test application. Thus, the needs of the test application can be served, even for a star topology if each of the TAPC states Capture-DR, Update-DR, and Run-Test/Idle can be operated in concert across all of the UUT components of interest.It is for just this purpose that the scan selection directives (SSD) were devised. Figure 13 illustrates the scan-state sequence made possible by the SSDs (star topology).Run-Test-Idle1Select-DR-ScanCapture-DRExit1-DRExit2-DRUpdate-DRShift-DRPause-DR11111Figure 13—Scan-state sequence for test applications,modified for star topology。

JTAG电路的工作原理

JTAG电路的工作原理一、引言JTAG(Joint Test Action Group)是一种用于测试、调试和编程集成电路的标准接口。

它由IEEE 1149.1标准定义,广泛应用于现代电子设备中。

本文将详细介绍JTAG电路的工作原理。

二、JTAG电路的组成JTAG电路由多个部分组成,包括测试访问端口(TAP,Test Access Port)、测试数据寄存器(TDR,Test Data Register)、测试状态机(TSM,Test State Machine)和测试控制器(Test Controller)等。

1. 测试访问端口(TAP)TAP是JTAG电路的核心组成部分,它负责与外部设备进行通信。

TAP包含四个信号线,分别是TCK(Test Clock,测试时钟)、TMS(Test Mode Select,测试模式选择)、TDI(Test Data Input,测试数据输入)和TDO(Test Data Output,测试数据输出)。

这四根信号线通过TAP与外部设备进行数据交换。

2. 测试数据寄存器(TDR)TDR是JTAG电路中的一个重要组成部分,用于存储和处理测试数据。

它包含一个或多个数据寄存器,用于存储输入和输出的测试数据。

测试数据可以通过TAP的TMS和TDI信号线输入到TDR中,然后通过TDO信号线输出。

3. 测试状态机(TSM)TSM是JTAG电路中的一个关键组件,它负责控制测试过程中的状态转换。

TSM根据接收到的TMS信号控制TAP的状态转移,从而实现测试操作的顺序控制。

4. 测试控制器(Test Controller)测试控制器是JTAG电路的主控制单元,它负责协调TAP、TDR和TSM的工作,实现测试操作的控制和管理。

测试控制器可以通过外部接口与计算机或其他测试设备进行通信,接收测试指令并控制JTAG电路的工作。

三、JTAG电路的工作原理JTAG电路的工作原理可以简单描述为以下几个步骤:1. 初始化在开始测试之前,需要对JTAG电路进行初始化设置。

第四部分2:FPGA配置及片内调试技术

第四部分:FPGA设计基础(2)北京理工大学雷达技术研究所陈禾FPGA配置及片内调试技术{边界扫描原理{FPGA配置的基本方式{高级配置环境{基于嵌入式处理器的配置技术{基于Internet的可重构逻辑实现{ChipScope Pro片内调试系统边界扫描原理{IEEE Standard 1149.1 -Test Access Port and Boundary-Scan Architecturez JTAG是JOINT TEST ACTION GROUP组织最初提出的,最终由IEEE批准并且标准化的。

IEEE 1149.1一般也俗称JTAG调试标准。

z在JTAG调试标准当中,边界扫描(Boundary-Scan)是一个很重要的概念。

边界扫描技术的基本思想是在靠近芯片的输入输出管脚上增加一个移位寄存器单元。

因为这些移位寄存器单元都分布在芯片的边界上(周围),所以被称为边界扫描寄存器(Boundary-Scan Register Cell)。

边界扫描原理{当芯片处于调试状态的时候,这些边界扫描寄存器可以将芯片和外围的输入输出隔离开来。

通过这些边界扫描寄存器单元,可以实现对芯片输入输出信号的观察和控制。

{对于芯片的输入管脚,可以通过与之相连的边界扫描寄存器单元把信号(数据)加载到该管脚中去。

{对于芯片的输出管脚,也可以通过与之相连的边界扫描寄存器“捕获”(capture)该管脚上的输出信号。

边界扫描原理{在正常的运行状态下,这些边界扫描寄存器对芯片来说是透明的。

{芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。

{一般的芯片都会提供几条独立的边界扫描链,用来实现完整的测试功能。

边界扫描链可以串行的输入和输出,通过相应的时钟信号和控制信号,就可以方便的观察和控制处在调试状态下的芯片。

利用边界扫描链可以实现对芯片的输入输出进行观察和控制。

JTAG仿真接口电路设计

JTAG仿真接口电路设计

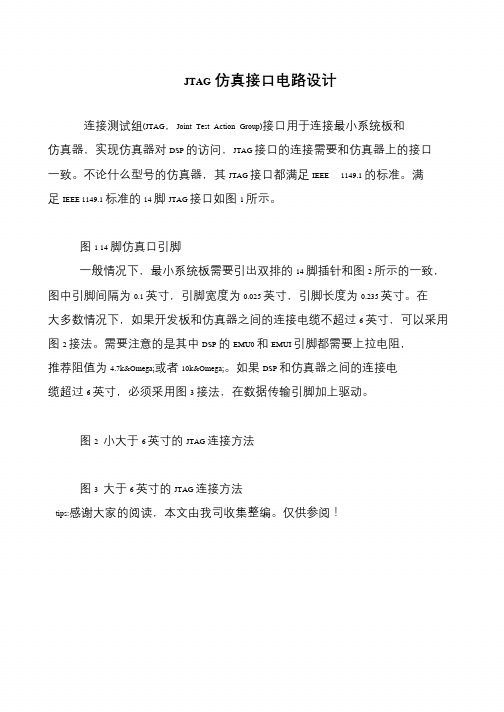

连接测试组(JTAG,Joint Test Action Group)接口用于连接最小系统板和仿真器,实现仿真器对DSP 的访问,JTAG 接口的连接需要和仿真器上的接口一致。

不论什么型号的仿真器,其JTAG 接口都满足IEEE 1149.1 的标准。

满足IEEE 1149.1 标准的14 脚JTAG 接口如图1 所示。

图1 14 脚仿真口引脚

一般情况下,最小系统板需要引出双排的14 脚插针和图2 所示的一致,图中引脚间隔为0.1 英寸,引脚宽度为0.025 英寸,引脚长度为0.235 英寸。

在大多数情况下,如果开发板和仿真器之间的连接电缆不超过6 英寸,可以采用

图2 接法。

需要注意的是其中DSP 的EMU0 和EMUI 引脚都需要上拉电阻,

推荐阻值为4.7kΩ或者10kΩ。

如果DSP 和仿真器之间的连接电缆超过6 英寸,必须采用图3 接法,在数据传输引脚加上驱动。

图2 小大于6 英寸的JTAG 连接方法

图3 大于6 英寸的JTAG 连接方法

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

边界扫描结构和IEEE 1149.1标准

这些公 司认为 在 当今这 种极具 竞争 的电子 市场 中 只有无 知识产 权的 结构才 能鼓 励一些 公司 提供引 入 到产品 开发 生产 和测试 价格可 控的 兼容集 成电 路 测试设 备和CAD软件 普遍 认为 边 界扫描 结构将 会 如RS- 2 32标准 适合 于计算 机外 围一样 适合 于开 发 生产和测试

边界扫 描寄存 器

B S

C B

S

B

C

S C

输

核

B S

B

入

S

C

输

管

C

心

促 进 I EEE 114 9. 1 发展 的 一个 重 要 因素 就 是 表 面 封装 技术的 不成 熟性 许多 情况下 如 果印刷 线 路 板是 电连接 的 很容易 就会 发现 表面 封装元 件 的 边界 扫描路 径提 供执行 器件 间的连 续性 测试的 唯 一 方法 通过 在一 个器件 的输 出缓存 处设 置一个 已 知 状态 并观 察另 外相连 器件 的输入 缓存 就能 很 容 易看 出印刷 线路板 PWB 是否 良好连 接 这一 简 单 的测 试显示 开路 通道 冷压 焊连接 压 焊桥或 在 I C缓存 器中由 静电 泄漏 ESD 造成的 失效 等PWB中 所 有常见的问 题 [ 1]

在 经 过大 约2 00 家主 要 跨国 电 子公 司 的几 千 人 的 合作 研究后 I EEE 114 9. 1作 为公共 的协 议和边 界 扫 描结 构 而 成为一 个行业 标准 开发I EEE 1149 . 1 的 过 程 中 早 期 作 出 贡 献 的 公 司 有 AT&T DEC Er i cs s on I BM Ni xd or f Ph i l i ps Si emens 和TI

jtag标准ieee1149.1解析

IEEE1149.1标准是一项用于测试和故障诊断集成电路的重要标准,而JTAG(Joint Test Action Group)是这项标准的主要推动者之一。

本文将对IEEE1149.1标准进行解析,从其定义、原理、应用等多个角度进行分析,帮助读者更好地理解和应用这一标准。

一、 IEEE1149.1标准的定义IEEE1149.1标准,也称为边界扫描标准或JTAG标准,是一项由IEEE 制定的用于测试集成电路的标准。

该标准于1990年发布,已被广泛应用于半导体工业、电子制造业等领域。

通过在芯片内部设置边界扫描链,可以实现对芯片内部连接和状态的测试和调试,从而提高了集成电路的可靠性和稳定性。

二、 IEEE1149.1标准的原理1. 边界扫描链IEEE1149.1标准的核心是边界扫描链(boundary scan ch本人n),通过在集成电路的引脚上添加扫描逻辑,实现了对芯片内部连接和状态的测试。

这种边界扫描链可以将芯片的内部引脚与外部引脚进行连接,从而实现对芯片内部信号的观测和控制。

2. TAP控制器IEEE1149.1标准还引入了TAP(Test Access Port)控制器,用于与边界扫描链进行通信和控制。

TAP控制器可以对边界扫描链进行初始化、数据传输和状态控制,从而实现对集成电路的测试和调试。

三、 IEEE1149.1标准的应用1. 芯片测试IEEE1149.1标准最主要的应用是用于集成电路的测试。

通过在芯片内部设置边界扫描链,可以实现对芯片内部连接和状态的测试,从而发现潜在的故障和缺陷。

2. 芯片调试除了测试功能,IEEE1149.1标准还可以用于集成电路的调试。

通过边界扫描链和TAP控制器,工程师可以对集成电路进行状态观测和信号控制,从而快速定位和分析故障原因。

3. 芯片编程IEEE1149.1标准还可以用于集成电路的编程。

一些可编程逻辑器件(如FPGA)可以通过边界扫描信息口进行编程,实现对逻辑器件内部配置和状态的控制。

测试技术标准——JTAG

JTAG接口JTAG(Joint Test Action Group;联合测试工作组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。

现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。

标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

中文名JTAG接口外文名Joint Test Action Group用途芯片内部测试接口TMS、TCK、TDI、TDO目录.1接口.▪ JTAG引脚定义.▪ JTAG芯片的边界扫描寄存器.▪ JTAG在线写Flash的硬件电路设计.▪使用TAP状态机的指令实行对Flash的操作.▪软件编程.▪电路设计和编程中的注意事项.2说明.3定义.▪ 14针JTAG接口.▪ 20针JTAG接口.▪ 10针JTAG接口接口编辑JTAG最初是用来对芯片进行测试的,JTAG的基本原理是在器件内部定义一个TAP(Test Access Port;测试访问口)通过专用的JTAG测试工具对内部节点进行测试。

JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。

如今,JTAG接口还常用于实现ISP(In-System Programmer,在系统编程),对FLASH等器件进行编程。

JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程然后再装到板上,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。

JTAG接口可对DSP芯片内部的所有部件进行编程。

JTAG引脚定义具有JTAG口的芯片都有如下JTAG引脚定义:TCK——测试时钟输入;TDI——测试数据输入,数据通过TDI输入JTAG口;TDO——测试数据输出,数据通过TDO从JTAG口输出;TMS——测试模式选择,TMS用来设置JTAG口处于某种特定的测试模式。

可选引脚TRST——测试复位,输入引脚,低电平有效。

一种兼容IEEE1149.1接口的模拟电压监测器的应用

一种兼容IEEE1149.1接口的模拟电压监测器的应用

杜影;王石记;安百岳

【期刊名称】《计算机测量与控制》

【年(卷),期】2010(018)010

【摘要】针对模拟电压监测的技术现状,提出以支持IEEE1149.1接口标准的模拟电压监测器进行电压监测电路设计;简要介绍了模拟电压监测器的基本结构、操作原理和应用方式;通过实际电压电路可测性设计方案的制定分析、实验和测试,说明了该电压监测器的优势和特点;同时,文中提出应用FPGA作为内建自测试(BIST)控制器执行监测操作,是边界扫描技术与BIST技术结合应用的一次创新;最后的应用结果表明,该监测器的使用为电路设计人员的可测性设计提供了一种新思路和参考方法.

【总页数】3页(P2427-2429)

【作者】杜影;王石记;安百岳

【作者单位】北京航天测控技术开发公司,北京,100041;北京航天测控技术开发公司,北京,100041;北京航天测控技术开发公司,北京,100041

【正文语种】中文

【中图分类】TP273

【相关文献】

1.高压、低电流电压监测器MAX6459及其应用 [J], 方佩敏

2.一种轻量级的Win32应用程序二进制接口兼容方案 [J], 周海洋;黄小大

3.程控交换机五号与中国一号信号模拟接口设备的兼容使用 [J], 尹培生

4.全兼容IEEE1149.1的MIPS CPU CORE可测性设计 [J], 陆正毅;孙承绶;程君侠

5.采用高压模拟/I^2L兼容工艺的用户线接口电路设计 [J], 于宗光;常桂兰;贺洁因版权原因,仅展示原文概要,查看原文内容请购买。

基于JTAG的CPLD测试配置方法研究

基于JTAG的CPLD测试配置方法研究摘要:在 CPLD的整个测试开发流程中,包括了静态和动态的测试。

CPLD测试系统有别于传统的元件测试环境,具有自身的特性。

测试平台要求有专门的EDA技术,其设计环境要求与当前主流 CPLD兼容,使用专用 EDA软件编写测试程序,再由 JTAG接口将其上传至 CPLD,再进行软硬件的测试。

关键词:JTAG;CPLD测试;配置方法引言JTAG (Joint Test Action Group)是 IEEE1149.1 (IEEE1149.1)的测试协议。

当前主流的 CPLD, FPGA, DSP等设备与传统的插头形式不同,都支持边缘扫描技术。

JTAG技术能够极大地提高测试效率,减少测试费用,因此 JTAG技术已被广泛地用于 LSI的检测与诊断。

在此基础上,采用 JTAG技术实现 CPLD的测试过程主要包括以下几个步骤:利用专用 EDA软件、先进的运动算法,实现对测试矢量的自动生成,并将其上传至 CPLD进行测试。

在实际应用中,要根据实际情况,选取适当的试验模型,对所需的测试矢量和所需矢量进行分析和处理,从而得出评价的结论。

一、CPLD整体结构分析第一,PLA模块。

PLA由“与门”阵列和“或门”阵列组成,可见 PLA中有56个“40”的“与门”数组和16个56输入的或门阵列。

PLA可以被配置成最多40个输入与或逻辑56个输入。

第二,MC模块。

MC的总体结构可以看作是一种具有设置/重置终端(包含 D、T、锁)的多功能触发器。

阵列和 PLA或数组。

特别的选择是由一个 SRAM dot的结构所控制的多路转换器来选择一个输入信号;时钟端还被 SRAM配置点所控制,它被选择为GCK0,GCK1,GCK2,或者 CTC,其中 PTC信号被作为 MC时钟的输入,而其输出被反馈到 AIM,而 other则被作为 I/OBLOCK的输入。

第三,输入输出I0模块。

I/O模块支持 LVTTL, LVCOMS, HSTL, SSTL等,这些标准的数据传输和接收。

智能仪器可测试性设计

精选PPT课件

22

常规BIT技术

• 边界扫描测试技术 边界扫描技术是一种扩展的BIT技术。它在 测试时不需要其他的辅助电路,不仅可以 测试芯片或者PCB的逻辑功能,还可以测 试IC之间或者PCB之间的连接是否存在故 障。边界扫描技术已经成为VLSI芯片可测 性设计的主流,IEEE也已于1990年确定了 有关的标准,即IEEE1149.1。

精选PPT课件

8

可测试性概述

• 可测试性设计优点 1.提高故障检测的覆盖率; 2.缩短仪器的测试时间; 3.可以对仪器进行层次化的逐级测试 4.降低仪器的维护费用。

• 可测试性设计缺点 1.额外的软/硬件成本; 2.系统设计时间增加。

精选PPT课件

9

固有测试性设计

• 总体设计 • 通用设计准则

精选PPT课件

精选PPT课件

14

BIT简介

• BIT的由来 传统的测试主要是利用外部的测试仪器(ETE) 对被测设备进行测试,ATE是ETE的自动化产 物。由于ATE费用高、种类多、操作复杂、人 员培训困难,而且只能离线检测,随着复杂系 统维修性要求的提高,迫切需要复杂系统本身 具备检测、隔离故障的能力以缩短维修时间。 所以,BIT在测试研究当中占据了越来越重要 的地位,成为维修性、测试性领域的重要研究 内容。在测试性研究中,BIT技术应用范围越 来越广,正发挥着越来越重要的作用。

精选PPT课件

4

可测试性概述

• 可测试性与可测试性设计 • 测试性要求 • 测试方案 • 可测试性设计优点

精选PPT课件

5

可测试性概述

• 可测试性

可测试性(Testability)是指产品能够及时准确地 确定其自身状态(如可工作,不可工作,性能下 降等)和隔离其内部故障的设计特性。 可控制性(Controllability) 可观测性(Observability) 可预见性(Predictability)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1 引言

在现代 电子应用 系统 中 ,随着超 大规模集成

电路 ( L I、表 面 安装 器 件 ( MD) 多芯 片 组 V S) S 、 件 ( M) MC 、多层 电路 板 ( C MP B)的发展 ,器 件

不仅可以对 电路进行互连测试 、总线测试 、上拉/ 下拉 电阻测试 、簇测试,还可 以对 F A H、C L LS PD 或 F G 等可编程器件进行在线编程。止是由于 PA

De i n a d Re l a i n o e e a se s d o sg n a i to fG n r l z Te t rBa e n

I EEE1 4 . t n a d 9 1S a d r 1

Z HONG , M E Bo NG t in c n e Sh o o Isu n t i c &O t- l t nc n ier g UA r ao S e poEe r is gnei ,B A,B in 0 8 ,C ia co E n e ig1 0 3 h ) j 0 n

Ab t a t F rs l i g t e ts r b e fcr u t n b a d s g rs se sa e h e i c e fg n r l sr c: o o v n h e tp o lms o ic iso o r -t e o y tm-tg ,t e d sgn s h me o e e a a tse a e n I e trb s do EEE 4 . tn a d i r s n e nt i a e . et se a e l ecr ut ’ n l ea do -iet ss 1 9 1s d sp e e td i h sp p r Th trc nr a i ic is o -i n f ln e t . 1 a r e z n I d i o , y u i g a mb d e e h olg ,s c sDSP PGA t , h e trwil a et e f au e ma lsz , n a dt n b sn n e e d d tc n o y u h a i ,F ec t e tse l h v h e tr sofs l ie - l w- o t g n r lp r o ea d e s - mb d n . o c s, e e a- u p s n a y e e me t Ke r : se ; e e a- u o e o -i et s; f-iet s; o n a y s a BI y wo ds Te tr g n r lp r s ; n l t o l e t b u d r -c n; T p n e n

有体积 小、功耗低 、通用性好和便 于嵌入到被测 电路板 等特点 。 [ 关键 词] 测试机;通用性 ;在线 测试 ; 离线测试 ;边界扫描 ;机 内测 试

[ 中图分类号] P 0 文献标识码] [ T 26[ A 文章编号]10 . 1 (0 60-0 3 4 0 61 X 20 )202 - 4 0

( 北京航 空航天 大学仪 器科学与光电工程 学院 ,北京 10 8 ) 0 0 3

[ 摘

要] 针对板级或 系统级 电路 的测试 问题 ,本文提 出了一种基 于 IE I4 . E E 191标准 的通用测试机 的设 计方

案,从 而实现 了对被测 电路 的在线和 离线 测试 。此 外,由于 D P P A 等嵌入式技术的使用 ,使整个 系统具 S 、F G

己成为一种必然的发展趋势【 。

在 D T 的众 多方法之 中,边界 扫描 ( S F B : bu dr s n o na c )是一种比较通用的技术。这种技术 y a

.

2 3

维普资讯

Jn 0 6V 1 7 . sr l o13 u e20 o. 2(ei .2 ) 3 No aN

上述 特 点 ,使边 界 扫描 技 术成 为 DF 研 究 的热 点 T

之一。此外,机 内测试 ( I )作为另一种常用的 BT D T技术,也得到了十分广泛的应用。BT是系统 F I

的安装密度 、元器件的管脚密度不断提高。在这种

情况 下 ,诸 如利用 万 用表 、示 波器 等来 测试 芯 片的 “ 针 ”式 传 统 测 试 方 法 已经 无法 满 足 测 试 的 需 探 要 。 丁是 ,对 电子 电路 进行 可测 试性 设 计 ( T) 二 DF

或设备本身为故障检测、诊断或隔离所提供的 自 动

测试 能力 。将 边 界 扫 描和 B T 结合 起来 ,可 以为 I

板级或系统级 电路提供非常好的故障检测和诊断能 力,冈此,受到人们越来越多的关注。 测试机作为 BT 测试中的核心部件,不仅要 I 为整个测试过程提供控制信号和测试激励,还要对

维普资讯

基于 IE 14 . 标准 的通用测试机 的设计. 实现 EE 19 1 j

钟波 等

20 0 6年 6月第 3 7卷第 2期 ( 总第 13期) 2

基于 I E 191 E El4 . 标准 的通用测试机 的设计 与实现

钟 波 ,孟 晓风

航 窄 电 子 技 术

A O C T C NO O VI NI S E H L GY

测试 结 果进行 分析 , 以便进 行故 障 定位 。 目前 ,绝

边 界 扫 描 测 试 的 基 本 过 程 是 :测 试 机 产 生 IE 14 . 测 试 总线 信 号 ,将 测 试 码 以 串行 移 位 E E 91 1 的方 式 由 T DI输 入边 界扫 描 单元 :然 后通 过 T MS 发送 测试 控制 命令 ,经 T AP控 制器 控制 B C 完 成 S 测试 码 的加载 和测 试 响应 的采集 :最后测 试 响应 以 串行 扫 描 的方 式 由 T O 送 到 测 试 机 进 行 分 析 处 D