EDA技术实用教程3版课件第3章

EDA课件第三章

tmp2:=d1 AND (NOT sel); tmp3:=tmp1 OR tmp2; tmp<=tmp3;

q<=tmp AFTER m; END PROCESS cale;

END ARCHITECTURE connect;

(2) 端口方向

端口方向用来定义外部引脚的信号方向是输入还 是输出。

凡是用“IN”进行方向说明的端口,其信号自端口 输入到构造体,而构造体内部的信号不能从该端口输 出。相反,凡是用“OUT”进行方向说明的端口,其信 号将从构造体内经端口输出,而不能通过该端口向构 造体输入信号。

实体说明

一个模块中仅有一 个设计实体。

实体 提供设计模块的接口信息,是VHDL设计电 路的最基本部分。

实体说明具有如下的结构:

ENTITY 实体名 IS

实体说明以“ENTITTY 实体名

[类属参数说明];

IS”开始至“END ENTITTY实体 名”结束。这里大写字母表示

实体说明的框架。实际上,对

此例中的外部引脚

ARCHITECTURE connect OF mux IS SIGNAL tmp:BIT; BEGIN

cale:PROCESS(d0,d1,sel) IS VARIABLE tmp1,tmp2,tmp3:BIT;

BEGIN tmp1:=d0 AND sel;

为d0,d1,sel,q 。

库(Library)是经编译后的数据的集合,它存放包集合 定义、实体定义、构造体定义和配置定义。

设计中的子程序和 公用数据类型的集合。

程序包

IEEE标准的标准程序包 设计者自身设计的程序包

包和库具有这样的关系:多个过程和函数汇集在一起构成包 集合,而几个包汇集在一起就形成一个库。

EDA课件第三章3 共59页

q<= i0 WHEN 0,

根据sel的不同值来 i0

i1 WHEN 1, i2 WHEN 2 ,

完成选择功能

i1

i2

mux q

i3 WHEN 3,

i3

‘X’ WHEN OTHERS;

a

b

4、 变量赋值语句

书写格式: 目的变量:=表达式; 意义:表达式的值替代目的变量的值,立即有效。

注意

1)两边的数据类型必须相同; 2)目的变量的类型和范围应事先给出; 3)右边的表达式可以是变量,信号或字符; 4)变量只在进程或子程序中使用,它无法传递 到进程之外。

条件信号赋值语句与进程中的多选择 if 语句等价:

PROCESS(sela, selb, a, b, c)

BEGIN

IF sela=‘1’ THEN

q <= a WHEN sela = ‘1’ ELSE b WHEN selb = ‘1’ ELSE c;

LIBRARY IEEE; USE IEEE.STD.LOGIC.1164.ALL; ENTITY dff IS

PORT(clk,d : IN STD_LOGIC; q : OUT STD_LOGIC);

END dff; ARCHITECTURE rtl OF dff IS BEGIN

PROCESS( clk ) BEGIN

*信号代入语句; * 变量赋值语句; * WAIT语句;

* IF语句;

* CASE语句;

* LOOP语句; * NEXT语句; * EXIT 语句;

2、 并发描述语句

VHDL的并发语句用来描述一组并发行为,它是并 发执行的,与程序的书写顺序无关。

*

语句(PROCESS);

2选1选择器的VHDL设计课件

3.1 多路①可以使用26个英文字母,数字0-9以及下划线“_”,且 只能以英文字母开头;

②不区分大小写;最长不超过64个字符;

③必须是单一下划线,且下划线前后都必须有英文字母 或数字;

6、端口定义语句port和端口模式 端口模式

IN 输入端口,定义的通道为单向只读模 OUT 式输出端口,定义的通道为单向输出模 INOUT 式 定义的通道确定为输入输出双向端口 BUFFER 缓冲端口,其功能与INOUT类似

3、界符 标点符号“;”表示VHDL中语句的结束;

3.1 多路选择器的VHDL描述

4、实体和结构体

实体和结构体是VHDL程序的两个基本组成部分;其中 实体主要用于定义电路或系统的外部端口;结构体用于定义 内部逻辑功能或电路结构。

ENTITY e_name IS PORT ( p_name : port_m

-- 注意,赋值条件的数据类型必须是boolean

3.1 多路选择器的VHDL描述

思考 ❖还有没有其它方法实现二选一? ❖n选一的多路选择器怎么设计?

3.1 多路选择器的VHDL描述

9、赋值符号<=

信号赋值符号“<=”,表示将符号右端的值赋值给左端的 信号; 10、关系运算符=

等号“=”没有赋值的含义,也不是相等的意思,而是 关系运算符,只是一种数据比较符号,其结果只有两种情况, 要么为真true,条件成立;要么为假false,条件不成立。 表达式 WHEN 赋值条件 ELSE

END ARCHITECTURE one ;

3.1 多路选择器的VHDL描述

3.1 多路选择器的VHDL描述

entity 实体

architecture 结构体

实体 mux21a1

EDA 技术实用教程 第3章

局部连线 宏单元的 乘积项 逻辑

共享扩展 项提供的 “与非” 乘积项

宏单元的 乘积项 逻辑

图3-28 共享扩展乘积项结构

KX

康芯科技

3.3 CPLD的结构与工作原理 的结构与工作原理

3.扩展乘积项 .

图3-29 并联扩展项馈送方式

KX

康芯科技

3.3 CPLD的结构与工作原理 的结构与工作原理

图3-46 JTAG BST 系统与与 FPGA器件 器件 关联结构图

KX

康芯科技

3.5 硬件测试技术

3.5.2 JTAG边界扫描测试 边界扫描测试

图3-47 JTAG BST选择命令模式时序 选择命令模式时序

3.5.3 嵌入式逻辑分析仪 Altera Signaltap II

EDA 技术实用教程

第 3 章 FPGA/CPLD 结构与应用

3.1 概

述

组合电路ቤተ መጻሕፍቲ ባይዱ

基本门

时序电路

输 入 …

输入 缓冲 电路

与 阵 列

或 阵 列

输出 缓冲 电路 …

输 出

基本PLD器件的原理结构图 图3-1 基本 器件的原理结构图

康芯科技

KX

3.1 概

述

3.1.1 可编程逻辑器件的发展历程 PROM (Programmable Read Only Memory) PLA (Programmable Logic Array) PAL (Programmable Array Logic) GAL (Generic Array Logic) EPLD CPLD

I/O6

一种PAL16V8的部分结构图 图3-17 一种 的部分结构图

eda技术实用教程

eda技术实用教程Part 1 EDA技术实用教程数据预处理一直是数据科学家中重要的任务之一。

因此,掌握数据预处理技能是必要的,而EDA(探索性数据分析)要比其他技术更为必要。

在这篇文章中,我们将介绍EDA的概念以及如何运用它来处理数据集。

我们还将介绍一些流行的EDA工具,以及如何在Python中使用这些工具。

探索性数据分析EDA是指探索性数据分析,是指分析数据以了解其特性的过程。

它有助于数据科学家洞察数据的基本特征,并为进一步的预测或分类建模做好准备。

EDA可以发现数据集中的异常值、缺失值或异常分布。

EDA工具大部分是可视化工具,能够帮助数据科学家更好地理解数据集。

EDA的主要目标如下:1.理解数据集的基本特征2.识别异常值和缺失值3.确定不同特征之间的关系4.绘制可视化图表,揭示数据分布模式EDA的实践在本节中,我们将介绍如何使用Python实施EDA技术。

安装Python和Jupyter Notebook首先,您应该安装Python和Jupyter Notebook。

这些是数据科学家日常工作所需的。

安装pandas和matplotlib在开始EDA之前,您需要确保安装了pandas和matplotlib这两个库。

它们是Python中的重要数据科学库,可以帮助您方便地读取和可视化数据。

pip install pandaspip install matplotlib读取数据集下面是一个读取数据集的例子。

import pandas as pddata=pd.read_csv("data.csv")数据集可视化在这里,我们将介绍如何使用Python中的matplotlib 库来可视化数据集。

散点图散点图是一个可视化数据关系的好方法。

在Python中,可以使用以下代码为两个变量(x和y)绘制散点图。

import matplotlib.pyplot as pltx=data['x']y=data['y']plt.scatter(x,y)plt.show()我们可以看到,在数据集中,x和y有一个很强的正相关关系。

《电子线路cad实用教程》第3章 原理图的绘制

序号 1 2 3 4 5 6 7 8 英文名称 HEADER PIN ANTENNA BATTER BELL BNC BRIDGE BUFFER 中文名称 插头 插针 天线 电池 电铃 电气节点 整流桥 缓冲器 序号 13 14 15 16 17 18 19 20 英文名称 CAPACITOR POL CAPVAR CON CRYSTAL DB9 DIODE DIODE VARACTOR DPY 中文名称 电解电容 可调电容 连接器 晶振 串口 普通二极管 变容二极管 数码管 序号 25 26 27 28 29 30 31 32 33 34 35 36 英文名称 MICROPHONE NPN PNP PHONEJACK PHOTO RES RESPACK SPEAKER SW-DIP SCR TRAN TRIAC 中文名称 麦克风 NPN型三极管 PNP型三极管 耳机插座 光电二极管 电阻 排阻 扬声器 多位开关 晶闸管 变压器 三端双向交 流开关

一、选取元件 方法3:在菜 单中有几个关于选取的 命令,如右图所示,可 以实现对元件的选取。

3.4 调整元件位置

二、剪贴元件 方法1:剪贴元件包括:元件的复制、剪切 和粘贴操作。在主工具栏中有两个与剪贴相关的图 标,如图所示。

3.4 调整元件位置

二、剪贴元件 方法2:剪贴命 令集中在菜单 Edit 中,如 图所示。

课堂演示

3.7 绘图工具的使用

一张电路图绘制好以后,通常要在电路图中添 加一些说明性的文字跟图形,这样既可以使得整个 图形美观,而且可以增加电路图的完整性跟说服力。 Ptotel 99 SE 为电路图提供了不具有电气特性的绘图 工具栏。

3.7 绘图工具的使用

1、绘图工具栏 通过执行 view 视图 /Toolbars 工具条 /Drawing Toolbar绘图工具条,绘图工具栏如下图所示。

EDA技术实用教程ppt

EDA技术及其发展 EDA技术的主要内容 EDA设计方法 EDA技术及EDA工具的发展趋势

第一章 EDA技术概况

1.1 EDA技术及其发展

1.什么是EDA? Electronic Design Automation 电子设计自动化

2. EDA技术定义 (广义定义)

半导体工艺设计自动化 可编程器件设计自动化 电子系统设计自动化 印刷电路板设计自动化 仿真与测试、故障诊断自动化 形式验证自动化 通称为EDA工程

1.4 EDA技术及EDA工具的发展趋势

1. EDA技术的发展趋势 (1)广度上:大型机——工作站——微机 (2)深度上: ESDA(Electronic System Design Automation ) CE(Concurrent Engineering 并行设计工程) SOC/SOPC ( system on a programmable chip 单 芯片集成)

3)计算机辅助工程设计CAE阶段

20世纪80年代初,出现了低密度的可编程逻辑 器件(PLA programmable array logic和GAL generic array logic),相应的EDA开发工具主 要解决电路设计没有完成之前的功能检测等问 题。 80年代后期,EDA工具已经可以进行初级的设 计描述、综合、优化和设计结果验证。

EDA技术极大的降低了硬件电路的设计难度,提 高了设计效率,是电子系统设计方法的质的飞跃

传统设计方法

自下而上(Bottom-up)的设计方法

优点

设计人员对于用这种方法进行设计比较熟悉 实现各个子块电路所需的时间短

缺点

一般来讲对系统的整体功能把握不足 实现整个系统的功能所需的时间长因为必须先将 各个小模块完成;使用这种方法对设计人员之间 相互进行协作有比较高的要求。

EDA技术及应用VHDL第三潭会生详解PPT学习教案

图7.5所示,对CNT9999进行逻辑 综合后的资源使用情况为:

Family:MAX7000S,Device: EPM7128SLC84-10,Total

macrocells:19/128(15%),Total pins:23/68(34%)。

第29页/共35页

图7.5 CNT9999的RTL视图

基本使用方法。 (2) 熟悉GW48-CK或其 他EDA实验开发系统的

基本使用方法。 (3) 学习VHDL基本逻辑 电路和状态机电路的综 第14页/共35页

设计并调试好一个由一条主干道和一条支干道的汇合点形成的十字交叉路口的 交通灯控制器,具体要求如下:

(1) 主、支干道各设有一个绿、黄、红指示灯,两个显示数码管。 (2) 主干道处于常允许通行状态,而支干道有车来才允许通行。当主干道允许通 行亮绿灯时,支干道亮红灯,而支干道允许通行亮绿灯时,主干道亮红灯。 (3) 当主、支干道均有车时,两者交替允许通行,主干道每次放行45 s,支干道 每次放行25 s,在每次由亮绿灯变成亮红灯的转换过程中,要亮5 s的黄灯作为过渡,

第24页/共35页

根据图7.5所示的实验电路结 构图NO.0和图7.1确定引脚的锁 定。选用EPM7128S-PL84芯片, 其引脚锁定过程如表7.1所示,其 中CLK接CLOCK2,CLR接键3,

ENA接键4,计数结果 DOUT[3..0]、DOUT[7..4]、 DOUT[11..8]、DOUT[15..12]经

锁定表格或文件。 (5) 记录系统仿真、逻辑综合及硬件验证结果。

(6) 记录实验过程中出现的问题及解决办法。 4.参考资料

本书4.3节、4.4节、4.5节、5.1节、5.2节和6.1节。

EDA 技术实用教程第3章

std_logic; OUT std_logic

•

同一结构体的多个进程之间是并行执行的关系。如下面三个进程: P1:PROCESS(a,b) P2:PROCESS(c,d) P3:PROCESS(d,e) 当d 发生变化时,执行P2,P3进程

3.1 多路选择器的VHDL描述

3.1.1 2选1多路选择器的VHDL描述

3.1 多路选择器的VHDL描述

3.1.2 相关语句结构和语法说明

5. 数据类型: integer boolean std_logic bit

6. 结构体表达

【例4-5】 ARCHITECTURE arch_name OF e_name IS [说明语句] BEGIN (功能描述语句) END ARCHITECTURE arch_name ; 说明语句说明与定义数据对象,类型,元件调用声明等 ,不是必须的。而功能描述语句必须,可并行语句、顺序 语句或其混合。

图3-3 mux21a功能时序波形

3.1 多路选择器的VHDL描述

3.1.2 相关语句结构和语法说明

1. 实体 描述器件外部情况及各信号端口基本性质

【例3-4】 ENTITY e_name IS PORT ( p_name : port_m data_type; ... p_namei : port_mi data_type ); END ENTITY e_name;

EDA 技术实用教程

第 3 章 VHDL设计初步

是什么是VHDL?

Very high speed integrated Hardware Description Language (VHDL)

是IEEE、工业标准硬件描述语言 用语言的方式而非图形等方式描述硬件电路

EDA技术及应用(第三版)章 (3)

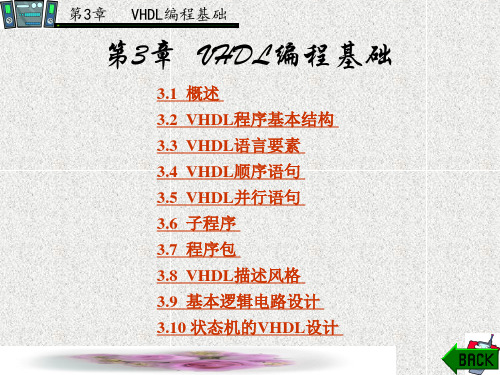

第3章 VHDL编程基础

(2) 设计要求:VHDL进行电子系统设计时可以不了解电路 的结构细节,设计者所做的工作较少;Verilog和ABEL语言进行 电子系统设计时需了解电路的结构细节,设计者需做大量的工 作。

(3) 综合过程:任何一种语言源程序,最终都要转换成门电 路级才能被布线器或适配器所接受。因此,VHDL语言源程序的 综合通常要经过行为级→RTL级→门电路级的转化,VHDL几乎 不能直接控制门电路的生成。而Verilog语言和ABEL语言源程序 的综合过程要稍简单,即经过RTL级→门电路级的转化,易于控 制电路资源。

第3章 VHDL编程基础

3.2 VHDL程序基本结构

3.2.1 VHDL程序设计举例 当我们使用一个集成电路芯片时,根据数字电子技术

的知识,至少需要了解三个方面的信息:① 该芯片符合什 么规范,是谁生产的,用户是否认可;② 该芯片有多少管 脚,每个管脚是输入还是输出,每个管脚对输入/输出有什 么要求;③ 该芯片各管脚之间的关系,以及能完成什么逻 辑功能。

第3章 VHDL编程基础

第3章 VHDL编程基础

3.1 概述 3.2 VHDL程序基本结构 3.3 VHDL语言要素 3.4 VHDL顺序语句 3.5 VHDL并行语句 3.6 子程序 3.7 程序包 3.8 VHDL描述风格 3.9 基本逻辑电路设计 3.10 状态机的VHDL设计

第3章 VHDL编程基础

第3章 VHDL编程基础

【例3.1】 74LS00的VHDL设计过程。 1.设计思路 根据数字电子技术的知识,我们知道74LS00是一个四2

输入与非门,亦即该芯片有四个2输入与非门组成,因此设 计时可先设计一个2输入与非门MYNAND2,如图3.1(a)所 示,再由四个2输入与非门构成一个整体MY74LS00,如图 3.1(b)所示。

EDA3

Architecture a of fenpin4 is type state is(s0,s1,s2,s3); signal nowstate:state; Begin Process(cp,clr) Begin If clr=„1‟ then Nowstate<=s0; Elsif cp‟event and cp=„1‟ then case Nowstate is when s0=> nowstate<=s1; when s1=>nowstate<=s2; when s2=> nowstate<=s3; when others=>nowstate<=s0; end case; End if; End process; Q<=„1‟ when nowstate=s3 else „0‟; End a;

If clr=„1‟ then Nowstate<=s0;Tc<=“000”; 简单交通灯 Elsif cp‟event and cp=„1‟ then case Nowstate is 红、黄、绿灯分别亮5、2、5秒。 when s0=> if tc=“100” then Entity light1 is nowstate<=s1; tc<=“000”; Port(cp,clr:in std_logic; else tc<=tc+1; end if; Q:out std_logic_vector(2 downto 0)); when s1=> End light1; if tc=“001” then nowstate<=s2; tc<=“000”; else tc<=tc+1; end if; when s2=> if tc=“100” then Architecture a of light1 is nowstate<=s0; tc<=“000”; type state is(s0,s1,s2); else tc<=tc+1;end if; signal nowstate:state; when others=> nowstate<=s0; tc<=“000”; Singal tc:std_logic_vector(2 downto 0); end case; Begin End if; Process(cp,clr) End process; Begin Q<=“100” when nowstate=s0 else “010” when nowstate=s1 else “001”; End a;

EDA技术及应用(第三版)章 (3)

第6章 VHDL设计应用实例

此乘法器的优点是节省芯片资源,它的核心元件只是 一个8位加法器,其运算速度取决于输入的时钟频率。若时 钟频率为100 MHz,则每一运算周期仅需80 ns。而若利用 备用最高时钟,即12 MHz晶振的MCS-51单片机的乘法指 令进行8位乘法运算,则仅单指令的运算周期就长达4 μs。 因此,可以利用此乘法器或相同原理构成的更高位乘法器 完成一些数字信号处理方面的运算。

A4: IN STD_LOGIC_VECTOR(3 DOWNTO 0); B4: IN STD_LOGIC_VECTOR(3 DOWNTO 0); S4: OUT STD_LOGIC_VECTOR(3 DOWNTO 0); CO4: OUT STD_LOGIC);

--4位二进制并行加法器 --低位来的进位 --4位加数 --4位被加数 --4位和 --进位输出

第6章 VHDL设计应用实例

6.2 8位乘法器的设计

1.系统设计思路 纯组合逻辑构成的乘法器虽然工作速度比较快,但占 用硬件资源多,难以实现宽位乘法器,而基于PLD器件外 接ROM九九表的乘法器则无法构成单片系统,也不实用。 这里介绍由8位加法器构成的以时序逻辑方式设计的8位乘 法器,此乘法器具有一定的实用价值。其乘法原理是:乘 法通过逐项位移相加原理来实现,从被乘数的最低位开始, 若为1,则乘数左移后与上一次和相加;若为0,则左移后 以全零相加,直至被乘数的最高位。从图6.7的逻辑图上可 以清楚地看出此乘法器的工作原理。

--与门开关

DIN: IN STD_LOGIC_VECTOR (7 DOWNTO 0); --8位输入

DOUT: OUT STD_LOGIC_VECTOR (7 DOWNTO 0)); --8位输出

EDA技术与应用(第3版)[江国强][电子教案]

![EDA技术与应用(第3版)[江国强][电子教案]](https://img.taocdn.com/s3/m/ef8f070af7ec4afe04a1df97.png)

(第3版)

江国强 编制

桂林电子科技大学

2020/4/3

1

▪ 第1章 EDA技术概述

目

▪ 第2章 ▪ 第3章

EDA工具软件使用方法 VHDL

▪ 第4章 Verilog HDL

录

▪ 第5章 ▪ 第6章

常用EDA工具软件 可编程逻辑器件

▪ 第7章EDA技术的应用

2020/4/3

2

第1章 EDA技术概述

2020/4/3

19

3. 波形输入方式

波形输入主要用于建立和编辑波形设计文件以及输 入仿真向量和功能测试向量。波形设计输入适合用于 时序逻辑和有重复性的逻辑函数,系统软件可以根据 用户定义的输入/输出波形自动生成逻辑关系。

波形编辑功能还允许设计者对波形进行拷贝、剪 切、粘贴、重复与伸展。从而可以用内部节点、触发 器和状态机建立设计文件,并将波形进行组合,显示 各种进制的状态值。还可以通过将一组波形重叠到另 一组波形上,对两组仿真结果进行比较。

2020/4/3

22

2. 逻辑优化和综合

逻辑优化是化简所有的逻辑方程或用户自建的宏, 使设计所占用的资源最少。综合的目的是将多个模块 化设计文件合并为一个网表文件,并使层次设计平面 化(即展平)。

3. 适配和分割

在适配和分割过程,确定优化以后的逻辑能否与 下载目标器件CPLD或FPGA中的宏单元和I/O单元适 配,然后将设计分割为多个便于适配的逻辑小块形式 映射到器件相应的宏单元中。如果整个设计不能装入 一片器件时,可以将整个设计自动分割成多块并装入 同一系列的多片器件中去。

2020/4/3

13

CAE(Computer Aided Engineering)是在CAD 的工具逐步完善的基础上发展起来的,尤其是人们 在设计方法学、设计工具集成化方面取得了长足的 进步,可以利用计算机作为单点设计工具,并建立 各种设计单元库,开始用计算机将许多单点工具集 成在一起使用,大大提高了工作效率。

EDA3

EDA 设计(二)课程设计报告姓名:学号:学院:自动化学院专业:自动化标题:乒乓球游戏机的设计南京理工大学2015 年 10 月导言EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

20世纪90年代,国际上电子和计算机技术较为先进的国家,一直在积极探索新的电子电路设计方法,并在设计方法、工具等方面进行了彻底的变革,取得了巨大成功。

在电子技术设计领域,可编程逻辑器件(如CPLD、FPGA)的应用,已得到广泛的普及,这些器件为数字系统的设计带来了极大的灵活性。

这些器件可以通过软件编程而对其硬件结构和工作方式进行重构,从而使得硬件的设计可以如同软件设计那样方便快捷。

这一切极大地改变了传统的数字系统设计方法、设计过程和设计观念,促进了EDA技术的迅速发展。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

本次实验我们使用了东南大学SE-5M型EDA实验开发平台系统,以Altera公司的MAX+plusⅡ10.0为开发软件,设计了一款乒乓游戏机。

接下来是仿真程序及仿真语言的学习:1、VHDL语言VHDL全名Very-High-Speed Integrated Circuit Hardware Description Language,诞生于1982年。

1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言。

自IEEE-1076(简称87版)之后,各EDA公司相继推出自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL接口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.2 简单可编程逻辑器件原理

3.2.2 PROM

A0 A1 … An−1

与阵列 (不可 编程) W p −1 p = 2n

W0 W1 …

或阵列 (可编程)

F0 F1 … Fm−1

图3-10 PROM的逻辑阵列结构 的逻辑阵列结构

3.2 简单可编程逻辑器件原理

3.2.2 PROM

A1 A0 或阵列 (可编程)

KX

康芯科技

3.5 硬件测试技术

3.5.2 JTAG边界扫描测试 边界扫描测试

图3-47 JTAG BST选择命令模式时序 选择命令模式时序

3.5.3 嵌入式逻辑分析仪

3.6 FPGA/CPLD产品概述 产品概述

3.6.1 Lattice公司 公司CPLD器件系列 公司 器件系列

1. ispLSI器件系列 器件系列

TDI TDO

TMS

TCK TRST

3.5 硬件测试技术

3.5.2 JTAG边界扫描测试 边界扫描测试

图3-44 边界扫描数据移位方式

3.5.2 JTAG边界扫描测试 边界扫描测试

图3-45 JTAG BST系统 系统 内部结构

KX

康芯科技

3.5.2 JTAG边界扫描测试 边界扫描测试

图3-46 JTAG BST 系统与与 FPGA器件 器件 关联结构图

3.2 简单可编程逻辑器件原理

3.2.5 GAL

图3-24 输出反馈结构

3.2 简单可编程逻辑器件原理

3.2.5 GAL

图3-25 简单模式输出结构

3.3 CPLD的结构与工作原理 的结构与工作原理

图3-25 简单模式输出结构

3.3 CPLD的结构与工作原理 的结构与工作原理

1.逻辑阵列块(LAB) .逻辑阵列块

3.2.2 PROM

A0 A1 … … An−1

地址 译码器 W p−1 p = 2n

W0 W1 … …

存储单元 阵列

F0 F1 … … Fm−1

0 1

W W W

= A = A

n −1 n −1

… A

1

A

0

图3-9 PROM基本结构 基本结构

… A1A0

2

n

−1

... = A n −1 … A1 A 0

图3-27 MAX7128S的结构 的结构

3.3 CPLD的结构与工作原理 的结构与工作原理

2.宏单元 . MAX7000系列中的宏单元 系列中的宏单元

逻辑阵列 乘积项选择矩阵 可编程寄存器

三种时钟输入模式 全局时钟信号 全局时钟信号由高电平有效的时钟信号使能 用乘积项实现一个阵列时钟

3.3 CPLD的结构与工作原理 的结构与工作原理

3.2 简单可编程逻辑器件原理

3.2.5 GAL

图3-20 寄存器模式组合双向输出结构

3.2 简单可编程逻辑器件原理

3.2.5 GAL

图3-21 组合输出双向结构

3.2 简单可编程逻辑器件原理

3.2.5 GAL

图3-22 复合型组合输出结构

3.2 简单可编程逻辑器件原理

3.2.5 GAL

图3-23 反馈输入结构

3.扩展乘积项 .

局部连线 宏单元的 乘积项 逻辑

共享扩展 项提供的 “与非” 乘积项

宏单元的 乘积项 逻辑

图3-28 共享扩展乘积项结构

3.3 CPLD的结构与工作原理 的结构与工作原理

3.扩展乘积项 .

图3-29 并联扩展项馈送方式

3.3 CPLD的结构与工作原理 的结构与工作原理

4.可编程连线阵列(PIA) .可编程连线阵列

3.2 简单可编程逻辑器件原理

3.2.3 PLA

A1 A0 或阵列 (可编程)

A1 A1 A0 A 0 与阵列(可编程)

图3-13 PLA逻辑阵列示意图 逻辑阵列示意图

F1

F0

3.2 简单可编程逻辑器件原理

3.2.3 PLA

A2

A1

A0

A2

A1

A0

F2

F1

F0

F2 F1

F0

图3-14 PLA与 PROM的比较 与 的比较

FPGA

3.1 概

述

可编程逻辑器件(PLD)

3.1.2 可编程逻辑器件的分类

简单 PLD

复杂 PLD

PROM

PLA

PAL

GAL

CPLD

FPGA

图3-2 PLD按集成度分类 按集成度分类

3.2 简单可编程逻辑器件原理

3.2.1 电路符号表示

图3-3 常用逻辑门符号与现有国标符号的对照

3.2 简单可编程逻辑器件原理

图3-34 Cyclone LE结构图 结构图

3.4 FPGA的结构与工作原理 的结构与工作原理

3.4.2 Cyclone/CycloneII系列器件的结构与原理 系列器件的结构与原理

图3-35 Cyclone LE普通模式 普通模式

3.4.2 Cyclone/CycloneII系列器件的结构与原理 系列器件的结构与原理

输入A 输入B 输入C 输入D 多路选择器

输入1 输入2 输入3 输入4

16×1 RAM

查找表 LUT

输出

0 0 0 0 0 1 1 0 0 0 0 0 0 0 1 1

查找表 输出

图3-32 FPGA查找表单元 查找表单元

图3-33 FPGA查找表单元内部结构 查找表单元内部结构

3.4.2 Cyclone/CycloneII系列器件的结构与原理 系列器件的结构与原理

EDA 技术实用教程

第 3 章 FPGA/CPLD 结构与应用

3.1 概

述

组合电路

基本门

时序电路

输 入 …

输入 缓冲 电路

与 阵 列

或 阵 列

输出 缓冲 电路 …

输 出

基本PLD器件的原理结构图 图3-1 基本 器件的原理结构图

3.1 概

述

3.1.1 可编程逻辑器件的发展历程 PROM (Programmable Read Only Memory) PLA (Programmable Logic Array) PAL (Programmable Array Logic) GAL (Generic Array Logic) EPLD CPLD

ispLSI1000E系列 系列 ispLSI5000V系列 系列 ispLSI2000E/2000VL/200VE系列 系列 ispLSI 8000/8000V系列 系列

2. ispMACH4000系列 系列

IspMACH 4000Z、ispMACH 4000V 、 ispMACH 4000Z 、

3.4.2 Cyclone/CycloneII系列器件的结构与原理 系列器件的结构与原理

图3-41 LUT链和寄存器链的使用 链和寄存器链的使用

3.4 FPGA的结构与工作原理 的结构与工作原理

3.4.2 Cyclone/CycloneII系列器件的结构与原理 系列器件的结构与原理

图3-42 LVDS连接 连接

0

D

Q Q

SL17 7 I1 2

11 10 R 01 00 11 10 R 01 00 SG0 SL06

19

I/O7

11 10 R 01 00 SG1

Vcc SL06

11 10 R 01 00

8

D

Q Q

SL16 15 I2 3

11 10 R 01 00 11 10 R 01 00 SG1 SL06

18

信号布线到LAB的方式 图3-30 PIA信号布线到 信号布线到 的方式

3.3 CPLD的结构与工作原理 的结构与工作原理

5.I/O控制块 . 控制块

器件的I/O控制块 图3-31 EPM7128S器件的 控制块 器件的

3.4 FPGA的结构与工作原理 的结构与工作原理

3.4.1 查找表逻辑结构

局部布线 进位输出 逻辑

寄存器链 输出

进位输出0 进位输出

进位输出1 进位输出

图3-36 Cyclone LE动态算术模式 动态算术模式

3.4.2 Cyclone/CycloneII系列器件的结构与原理 系列器件的结构与原理

图3-37 Cyclone LAB结构 结构

3.4.2 Cyclone/CycloneII系列器件的结构与原理 系列器件的结构与原理

3.2 简单可编程逻辑器件原理

3.2.4 PAL

A1

A0 A0

F0

A1 F1

F1

图3-15 PAL结构 结构

F0

图3-16 PAL的常用表示 的常表示0 CLK/I 0 1

3 4

7 8

11 12

15 16

19 20

23 24

27 28

31

11 10 R 01 00 SG1

Vcc SL07

11 10 R 01 00

I/O6

一种PAL16V8的部分结构图 图3-17 一种 的部分结构图

I/CLK 1

0

0

3 4

7 8

11 12

15 16

19 20

23 24

27 28

31

CLK

3.2.5 GAL I

I

OLMC

7

19 I/O/Q

2

8

OLMC

15

18 I/O/Q

3

16

OLMC

23

17 I/O/Q

I

4

24

OLMC

31

16 I/O/Q

LAB 进位输入 进位输入0 进位输入 进位输入1 进位输入 addnsub Data1 Data2 Data3 两个 2输入 输入 LUT (和 ) 和 两个 2输入 输入 LUT (进位 进位) 进位 同步装载 清零逻辑 寄 存 器 行、列和 直连线布线 进位输入 逻辑