AD1556ASZ;AD1555APZRL;AD1555APRL;AD1555APZ;AD1555BPZRL;中文规格书,Datasheet资料

PWM降压型DC-DC转换器MAX1556-MAX1556A-MAX1557简介

PWM降压型DC-DC转换器

MAX1556/MAX1556A/MAX1557简介

MAX1556/MAX1556A/MAX1557 是低工作电流(16micro;A)、固定频率的降压型调节器。

这些转换器具有高工作频率、低静态电流、低压差等特性,低

静态电流(27µA)使其非常适合用于1 节锂离子电池或3 节碱性/NiMH 电池供电的便携式装置。

MAX1556 最高可提供1.2A 电流,通过引脚可以选择

1.8V、

2.5V 与

3.3V 输出,或可调输出。

MAX1557 最高可提供600mA 电流,通过引脚可以选择1V、1.3V 与1.5V 输出,或可调输出。

MAX1556/MAX1556A/MAX1557 包含一个低导通电阻的内部MOSFET 开关和一个同步整流器,以最少的外部元件数提供高效、低压差指标。

采用专

有的拓扑结构,在高固定频率工作模式下,保证轻载和满载时都能保持优异的

性能。

1MHz PWM 开关频率使外部元件尺寸最小。

这两种器件都具有可调节的软启动,可以减小电池的瞬态负载变化。

MAX1556/MAX1556A/MAX1557 提供细小的10 引脚TDFN (3mm x 3mm)封装。

引脚配置:

关键特性:

●最高97%的效率

●1mA负载电流下95%的效率

●16µA低静态电流

●1MHz PWM 开关

●3.3µH小尺寸电感。

AD转换芯片介绍

高位高速AD、DA模数转换器(A/D)l 8位分辨率l TLV0831 8 位 49kSPS ADC 串行输出,差动输入,可配置为 SE 输入,单通道l TLC5510 8 位 20MSPS ADC,单通道、内部 S、低功耗l TLC549 8 位、40kSPS ADC,串行输出、低功耗、与 TLC540/545/1540 兼容、单通道l TLC545 8 位、76kSPS ADC,串行输出、片上 20 通道模拟 Mux,19 通道l TLC0831 8 位,31kSPS ADC 串行输出,微处理器外设/独立运算,单通道l TLC0820 8 位,392kSPS ADC 并行输出,微处理器外设,片上跟踪与保持,单通道l ADS931 8 位 30MSPS ADC,具有单端/差动输入和外部基准以及低功耗、电源关闭功能l ADS930 8 位 30MSPS ADC,单端/差动输入具有内部基准以及低功耗、电源关闭功能l ADS830 8 位 60MSPS ADC,具有单端/差动输入、内部基准和可编程输入范围l 10位分辨率l TLV1572 10 位 1.25 MSPS ADC 单通道 DSP/(Q)SPI IF S 极低功耗自动断电功能l TLV1571 1 通道 10 位 1.25MSPS ADC,具有 8 通道输出、DSP/SPI、硬件可配置、低功耗l TLV1549 10 位 38kSPS ADC 串行输出、固有采样功能、终端与 TLC154、TLC1549x 兼容l TLV1548 10 位 85kSPS ADC 系列输出,可编程供电/断电/转换速率,TMS320 DSP/SPI/QPSI Compat.,8 通道l TLV1544 10 位 85kSPS ADC 串行输出,可编程供电/断电/转换速率,TMS320 DSP/SPI/QPSI 兼容,4 通道l TLV1543 10 位 200 kSPS ADC 串行输出,内置自检测模式,内部 S,引脚兼容。

微雪电子 High-Precision AD DA Board 用户手册说明书

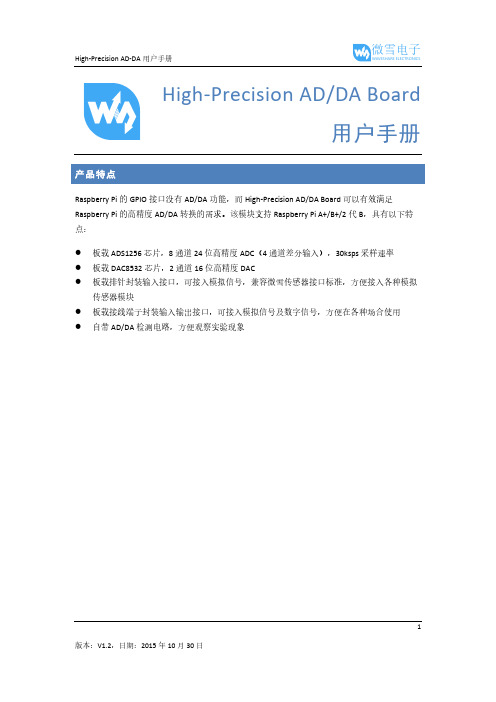

High-Precision AD/DA Board用户手册Raspberry Pi的GPIO接口没有AD/DA功能,而High-Precision AD/DA Board可以有效满足Raspberry Pi的高精度AD/DA转换的需求。

该模块支持Raspberry Pi A+/B+/2代B,具有以下特点:●板载ADS1256芯片,8通道24位高精度ADC(4通道差分输入),30ksps采样速率●板载DAC8532芯片,2通道16位高精度DAC●板载排针封装输入接口,可接入模拟信号,兼容微雪传感器接口标准,方便接入各种模拟传感器模块●板载接线端子封装输入输出接口,可接入模拟信号及数字信号,方便在各种场合使用●自带AD/DA检测电路,方便观察实验现象12板载资源[ 扩展接口]1.Raspberry Pi GPIO接口方便接入树莓派2.AD/DA输入输出接口(接线端子)方便在各种场合使用3.AD输入接口(排针)方便接入各种传感器模块(兼容微雪传感器接口标准)[ 器件介绍]4.7.68M晶振5.LM285-2.5提供ADC芯片工作基准电压6.光敏电阻7.LED输出指示灯8.10K电位器9.DAC853216位高精度DAC,2通道输出10.PWR LED电源指示灯11.ADS125624位高精度ADC,8通道(4通道差分输入)[ 跳线设置]12.ADC测试跳线13.DAC测试跳线14.电源配置跳线15.ADC参考地设置AD单端输入时,AINCOM为参考端,可接地或外部参考电平符号说明1)AD/DA输入输出接口(接线端子)(标号2)AD0-AD7:AD输入端AGND:模拟地GND:数字地VCC:工作电压(可通过电源配置跳线控制电压输出3.3V或者5V)DA0-DA1:DA输出端2)AD:AD输入接口(标号3)AD0-AD7:ADS1256模拟输入接口D0-D3:ADS1256的GPIO管脚(参考ADS1256数据手册)P22-P25:树莓派GPIO管脚AGND:模拟地3)LDR:光敏电阻(标号6)通过连接AD1和LDR之间的跳线,MCU可从AD1采集到该光敏电阻的输出电压。

常用的AD芯片

经常使用的A/D芯片之答禄夫天创作1. AD公司AD/DA器件AD公司生产的各种模数转换器(ADC)和数模转换器(DAC)(统称数据转换器)一直坚持市场领导地位,包含高速、高精度数据转换器和目前流行的微转换器系统(MicroConvertersTM )。

1.1 带信号调理、1mW功耗、双通道16位AD转换器:AD7705AD7705是AD公司出品的适用于低频丈量仪器的AD转换器。

它能将从传感器接收到的很弱的输入信号直接转换成串行数字信号输出,而无需外部仪表放大器。

采取Σ-Δ的ADC,实现16位无误码的良好性能,片内可编程放大器可设置输入信号增益。

通过片内控制寄存器调整内部数字滤波器的关闭时间和更新速率,可设置数字滤波器的第一个凹口。

在+3V电源和1MHz主时钟时, AD7705功耗仅是1mW。

AD7705是基于微控制器(MCU)、数字信号处理器(DSP)系统的理想电路,能够进一步节省成本、缩小体积、减小系统的复杂性。

应用于微处理器(MCU)、数字信号处理(DSP)系统,手持式仪器,分布式数据收集系统。

1.2 3V/5V CMOS信号调节AD转换器:AD7714AD7714是一个完整的用于低频丈量应用场合的模拟前端,用于直接从传感器接收小信号并输出串行数字量。

它使用Σ-Δ转换技术实现高达24位精度的代码而不会丢失。

输入信号加至位于模拟调制器前端的专用可编程增益放大器。

调制器的输出经片内数字滤波器进行处理。

数字滤波器的第一次陷波通过片内控制寄存器来编程,此寄存器可以调节滤波的截止时间和建立时间。

AD7714有3个差分模拟输入(也可以是5个伪差分模拟输入)和一个差分基准输入。

单电源工作(+3V或+5V)。

因此,AD7714能够为含有多达5个通道的系统进行所有的信号调节和转换。

AD7714很适合于灵敏的基于微控制器或DSP的系统,它的串行接口可进行3线操纵,通过串行端口可用软件设置增益、信号极性和通道选择。

AD-155A中文资料

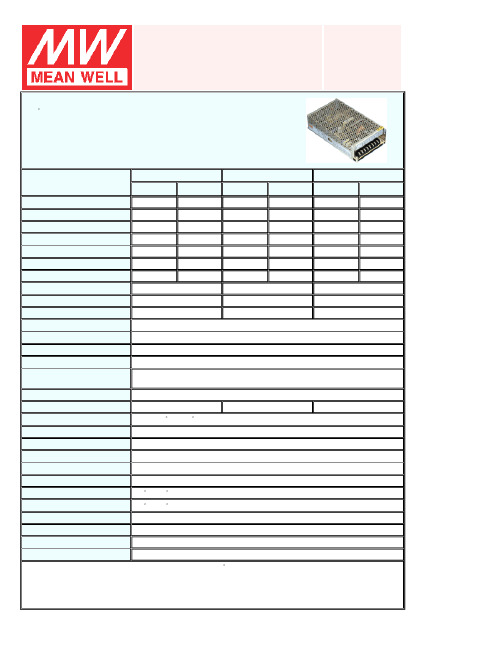

10min./1cycle, PERIOD FOR 60min. EACH AXES I/P - FG:1.5KVAC O/P - FG:0.5KVAC

- FG, O/P

- FG:500VDC / 100M Ohms ~ 90% RH

- 10 ºC ~ +60 ºC(REFER TO OUTPUT DERATING CURVE), 20% - 20 ºC ~ +85 ºC, 10% 199 * 110 * 50mm 1Kg UL1950, TUV EN60950 APPROVED CISPR22(EN55022)CLASS B,EN61000 ~ 95% RH CASE:906

RESET:AUTO RECOVERY CH1:115% ~ 135% TYPE:SHUTDOWN 10V ¡Ó 0.8V ºC (0 ~ 50 ºC) 1s, 90ms, 20ms / 230VAC 19.5V( +1.5V, - 1V ) 39V ¡Ó 2V

2s, 90ms, 16ms/115VAC PF>0.92 10 ~ 500Hz, 2G I/P - O/P:3KVAC I/P - O/P, I/P

- 4 - 2,3,4,5,6,8,11;ENV50204,EN61000

- 3 - 2, - 3

1.ALL PARAMETERS ARE SPECIFIED AT 230VAC INPUT, RATED LOAD, 25 ºC 70% RH. AMBIENT. 2.TOLERANCE¡G INCLUDE SET UP TOLERANCE, LINE REGULATION, LOAD REGULATION. 3.RIPPLE & NOISE ARE MEASURED AT 20MHz BY USING A 12" TWISTED PAIR TERMINATED WITH A 0.1uF & 47uF CAPACITOR. 4.LINE REGULATION IS MEASURED FROM LOW LINE TO HIGH LINE AT RATED LOAD. 5.LOAD REGULATION IS MEASURED FROM 20% TO 100% RATED LOAD, AND OTHER OUTPUT AT 60% RATED LOAD. 6.EACH OUTPUT PROVIDE UP TO MAXIMUM CURRENT, BUT TOTAL LOAD CAN NOT EXCEED MAX. OUTPUT POWER.

ADI(Analog Devices)CN-0348电路参考设计手册说明书

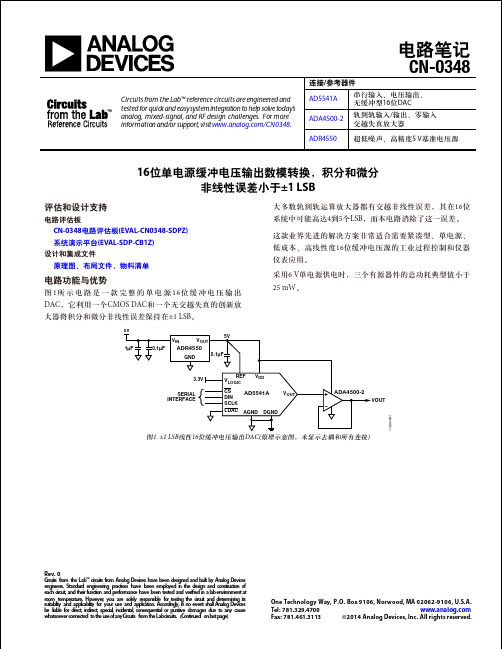

电路笔记CN-0348Circuits from the Lab™ reference circuits are engineered and tested for quick and easy s ystem integration to help solve today’s analog, mixed-signal, and RF design challenges. For more information and/or support, visit /CN0348.连接/参考器件AD5541A 串行输入、电压输出、无缓冲型16位DAC ADA4500-2 轨到轨输入/输出、零输入交越失真放大器ADR4550超低噪声、高精度5 V 基准电压源16位单电源缓冲电压输出数模转换,积分和微分非线性误差小于±1 LSBRev. 0C i r cu i t s fr o m t h e Lab ™ ci r cu i t s fr o m An al o gD evi ces h ave b een d esi g n ed an d b u i l t b y An al o g D evi ces en g i n eer s. St an d ar d en g i n eer i n g p r act i ces h ave b een emp l o yed i n t h e d esi g n an d co n st r u ct i o n o f each ci r cu i t , an d t h ei r fu n ct i o n an d p er fo r man ce h ave b een t est ed an d ver i ed i n a l ab en vi r o n men t at r o o m t emp er at u r e. H o wever , yo u ar e so l el y r esp o n si b l e fo r t est i n g t h e ci r cu i t an d d et er mi n i n g i t s su i t ab i l i t y an d ap p l i cab i l i t y fo r yo u r u se an d ap p l i cat i o n . Acco r d i n g l y, i n n o even t sh al l An al o g D evi ces b e l i ab l e fo r d i r ect , i n d i r ect , sp eci al , i n ci d en t al , co n seq u en t i al o r p u n i t i ve d amag es d u e t o an y cau se wh at so ever co n n ect ed t o t h e u se o f an y C i r cu i t s fr o m t h e Lab ci r cu i t s. (C o n t i n u ed o n l ast p ag e)One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www Fax: 781.461.3113 ©2014 Analog Devices, Inc. All rights reserved.ADR4550CS DIN SCLK LDAC3.3VV LOGIC V DDV OUTREF AGNDDGNDSERIAL INTERFACEAD5541AADA4500-26V5V11994-001V INGNDV OUT0.1µF0.1µF1µFVOUT图1. ±1 LSB 线性16位缓冲电压输出DAC(原理示意图,未显示去耦和所有连接)评估和设计支持电路评估板CN-0348电路评估板(EVAL-CN0348-SDPZ)系统演示平台(EVAL-SDP-CB1Z)设计和集成文件原理图、布局文件、物料清单电路功能与优势图1所示电路是一款完整的单电源16位缓冲电压输出DAC ,它利用一个CMOS DAC 和一个无交越失真的创新放大器将积分和微分非线性误差保持在±1 LSB 。

AD9260ASZ;AD9260ASZRL;中文规格书,Datasheet资料

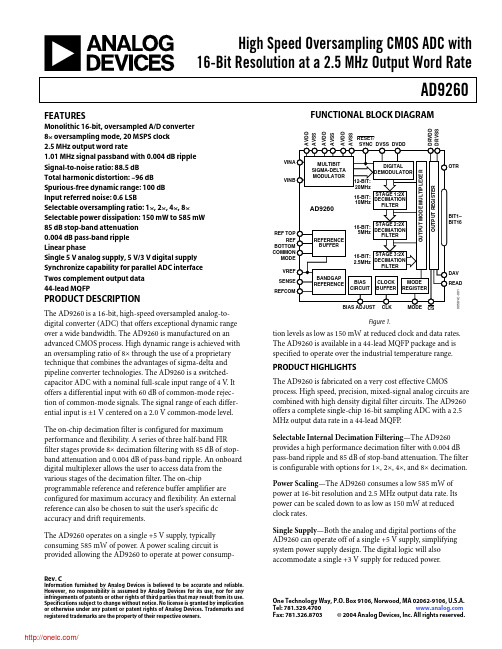

High Speed Oversampling CMOS ADC with16-Bit Resolution at a 2.5 MHz Output Word RateAD9260 Rev. CInformation furnished by Analog Devices is believed to be accurate and reliable.However, no responsibility is assumed by Analog Devices for its use, nor for anyinfringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: Fax: 781.326.8703© 2004 Analog Devices, Inc. All rights reserved.FEATURESMonolithic 16-bit, oversampled A/D converter8× oversampling mode, 20 MSPS clock2.5 MHz output word rate1.01 MHz signal passband with 0.004 dB rippleSignal-to-noise ratio: 88.5 dBTotal harmonic distortion: –96 dBSpurious-free dynamic range: 100 dBInput referred noise: 0.6 LSBSelectable oversampling ratio: 1×, 2×, 4×, 8×Selectable power dissipation: 150 mW to 585 mW85 dB stop-band attenuation0.004 dB pass-band rippleLinear phaseSingle 5 V analog supply, 5 V/3 V digital supply Synchronize capability for parallel ADC interfaceTwos complement output data44-lead MQFPPRODUCT DESCRIPTIONThe AD9260 is a 16-bit, high-speed oversampled analog-to-digital converter (ADC) that offers exceptional dynamic range over a wide bandwidth. The AD9260 is manufactured on an advanced CMOS process. High dynamic range is achieved with an oversampling ratio of 8× through the use of a proprietary technique that combines the advantages of sigma-delta and pipeline converter technologies. The AD9260 is a switched-capacitor ADC with a nominal full-scale input range of 4 V. It offers a differential input with 60 dB of common-mode rejec-tion of common-mode signals. The signal range of each differ-ential input is ±1 V centered on a 2.0 V common-mode level. The on-chip decimation filter is configured for maximum performance and flexibility. A series of three half-band FIR filter stages provide 8× decimation filtering with 85 dB of stop-band attenuation and 0.004 dB of pass-band ripple. An onboard digital multiplexer allows the user to access data from the various stages of the decimation filter. The on-chip programmable reference and reference buffer amplifier are configured for maximum accuracy and flexibility. An external reference can also be chosen to suit the user’s specific dc accuracy and drift requirements.The AD9260 operates on a single +5 V supply, typically consuming 585 mW of power. A power scaling circuit is provided allowing the AD9260 to operate at power consump-FUNCTIONAL BLOCK DIAGRAMD SOTRBIT1–BIT16DAVREAD581-C-1Figure 1.tion levels as low as 150 mW at reduced clock and data rates. The AD9260 is available in a 44-lead MQFP package and is specified to operate over the industrial temperature range. PRODUCT HIGHLIGHTSThe AD9260 is fabricated on a very cost effective CMOS process. High speed, precision, mixed-signal analog circuits are combined with high density digital filter circuits. The AD9260 offers a complete single-chip 16-bit sampling ADC with a 2.5 MHz output data rate in a 44-lead MQFP.Selectable Internal Decimation Filtering—The AD9260 provides a high performance decimation filter with 0.004 dB pass-band ripple and 85 dB of stop-band attenuation. The filter is configurable with options for 1×, 2×, 4×, and 8× decimation. Power Scaling—The AD9260 consumes a low 585 mW of power at 16-bit resolution and 2.5 MHz output data rate. Its power can be scaled down to as low as 150 mW at reduced clock rates.Single Supply—Both the analog and digital portions of the AD9260 can operate off of a single +5 V supply, simplifying system power supply design. The digital logic will also accommodate a single +3 V supply for reduced power.AD9260Rev. C | Page 2 of 44TABLE OF CONTENTSSpecifications.....................................................................................3 Clock Input Frequency Range....................................................3 DC Specifications.........................................................................3 AC Specifications..........................................................................4 Digital Filter Characteristics.......................................................6 Digital Filter Characteristics.......................................................7 Digital Specifications...................................................................9 Switching Specifications............................................................10 Absolute Maximum Ratings..........................................................11 Thermal Characteristics............................................................11 ESD Caution................................................................................11 Terminology....................................................................................12 Pin Configuration and Function Descriptions...........................13 Typical Performance Characteristics...........................................14 Typical AC Characterization Curvesvs. Decimation Mode.................................................................15 Typical AC Characterization Curves for 8× Mode................16 Typical AC Characterization Curves for 4× Mode................17 Typical AC Characterization Curves for 2× Mode................18 Typical AC Characterization Curves for 1× Mode................19 Typical AC Characterization Curves.......................................20 Additional AC Characterization Curves.................................21 Theory of Operation......................................................................23 Analog Input and Reference Overview.......................................24 Input Span...................................................................................24 Input Compliance Range...........................................................24 Analog Input Operation............................................................24 Driving the Input........................................................................25 Reference Operation......................................................................28 Digital Inputs and Outputs...........................................................30 Digital Outputs...........................................................................30 Mode Operation.........................................................................31 Bias Pin Operation.....................................................................32 Power Dissipation Considerations...............................................33 Digital Output Driver Considerations (DRVDD).................33 Grounding and Decoupling......................................................34 Evaluation Board General Description.......................................36 Features and User Controls.......................................................36 Shipment Configuration............................................................37 Quick Setup.................................................................................37 Application Information...........................................................38 Outline Dimensions.......................................................................43 Ordering Guide.. (43)REVISION HISTORY7/04—Changed from Rev. B to Rev. CChanged “trimpot” to “variable resistor” .....................Universal Updated Format................................................................Universal Updated Outline Dimensions......................................................43 Changes to Ordering Guide (43)5/00—Changed from Rev. A to Rev. B.1/98—Changed from Rev. 0 to Rev. A.AD9260Rev. C | Page 3 of 44SPECIFICATIONSCLOCK INPUT FREQUENCY RANGETable 1.Parameter—Decimation Factor (N)AD9260 (8) AD9260 (4) AD9260 (2) AD9260 (1) Unit CLOCK INPUT (Modulator Sample Rate, f CLOCK ) 1 1 1 1 kHz min20 20 20 20 M H z max OUTPUT WORD RATE (FS = f CLOCK /N) 0.125 0.250 0.500 1 kHz min2.5 5 10 20 MHz maxDC SPECIFICATIONSAVDD = +5 V , DVDD = +3 V , DRVDD = +3 V , f CLOCK = 20 MSPS, V REF = +2.5 V , Input CML = 2.0 V T MIN to T MAX unless otherwise noted,R BIAS = 2 kΩ. Table 2.Parameter—Decimation Factor (N) AD9260 (8) AD9260 (4) AD9260 (2) AD9260 (1) Unit RESOLUTION 16 16 16 12 Bits min INPUT REFERRED NOISE (TYP) 1.0 V Reference 1.40 2.4 6.0 1.3 LSB rms typ 2.5 V Reference 1 0.68 (90.6) 1.2 (86) 3.7 (76) 1.0 (63.2) LSB rms typ (dB typ) ACCURACY Integral Nonlinearity (INL) ± 0.75 ± 0.75 ± 0.75 ± 0.3 LSB typ Differential Nonlinearity (DNL) ± 0.50 ± 0.50 ± 0.50 ± 0.25 LSB typ No Missing Codes 16 16 16 12 Bits Guaranteed Offset Error 0.9 (0.5) (0.5) (0.5) (0.5) % FSR max (typ @ +25°C) Gain Error 2 2.75 (0.66) (0.66) (0.66) (0.66) % FSR max (typ @ +25°C)Gain Error 31.35 (0.7) (0.7) (0.7) (0.7) % FSR max (typ @ +25°C) TEMPERATURE DRIFT Offset Error2.5 2.5 2.5 2.5 ppm/°C typGain Error 222 22 22 22 ppm/°C typ Gain Error 3 7.0 7.0 7.0 7.0 ppm/°C typ POWER SUPPLY REJECTION AVDD, DVDD, DRVDD (+5 V ±0.25 V) 0.06 0.06 0.06 0.06 % FSR max ANALOG INPUT Input Span V REF = 1.0 V 1.6 1.6 1.6 1.6 V p p Diff. max V REF = 2.5 V 4.0 4.0 4.0 4.0 V p p Diff. max Input (VINA or VINB) Range +0.5 +0.5 +0.5 +0.5 V min +AVDD –0.5 +AVDD –0.5 +AVDD –0.5 +AVDD –0.5 V max Input Capacitance 10.2 10.2 10.2 10.2 pF typ INTERNAL VOLTAGE REFERENCE Output Voltage (1 V Mode) 1 1 1 1 V typ Output Voltage Error (1 V Mode) ± 14 ± 14 ± 14 ± 14 mV max Output Voltage (2.5 V Mode) 2.5 2.5 2.5 2.5 V typ Output Voltage Error (2.5 V Mode) ± 35 ± 35 ± 35 ± 35 mV max Load Regulation 4 1 V REF 0.5 0.5 0.5 0.5 mV max 2.5 V REF 2.0 2.0 2.0 2.0 mV max REFERENCE INPUT RESISTANCE 8 8 8 8 kΩ POWER SUPPLIES Supply Voltages AVDD +5 +5 +5 +5 V (± 5%)AD9260Rev. C | Page 4 of 44Parameter—Decimation Factor (N)AD9260 (8) AD9260 (4) AD9260 (2) AD9260 (1) Unit DVDD and DRVDD +5.5 +5.5 +5.5 +5.5 V max+2.7 +2.7 +2.7 +2.7 V min Supply Current IAVDD 115 115 115 115 mA typ134 mA max IDVDD 12.5 10.3 6.5 2.4 mA typ3.5 mA max IDRVDD0.450 0.850 1.7 2.6 mA typ POWER CONSUMPTION 613 608 600 585 mW typ 630 mW max1 VINA and VINB connect to DUT CML.2Including Internal 2.5 V reference. 3Excluding Internal 2.5 V reference. 4Load regulation with 1 mA load current (in addition to that required by AD9260).AC SPECIFICATIONSAVDD = +5 V , DVDD = +3 V , DRVDD = +3 V , f CLOCK = 20 MSPS, V REF = +2.5 V , Input CML = 2.0 V T MIN to T MAX unless otherwise noted, R BIAS = 2 kΩ. Table 3.Parameter—Decimation Factor (N) AD9260(8) AD9260(4) AD9260(2) AD9260(1) UnitDYNAMIC PERFORMANCE INPUT TEST FREQUENCY: 100 kHz (typ) Signal-to-Noise Ratio (SNR) Input Amplitude = –0.5 dBFS 88.5 82 74 63 dB typ Input Amplitude = –6.0 dBFS 82.5 78 68 58 dB typ SNR and Distortion (SINAD) Input Amplitude = –0.5 dBFS 87.5 82 74 63 dB typ Input Amplitude = –6.0 dBFS 82 77.5 69 58 dB typ Total Harmonic Distortion (THD) Input Amplitude = –0.5 dBFS –96 –96 –97 –98 dB typ Input Amplitude = –6.0 dBFS–93 –98 –96 –98 dB typ Spurious-Free Dynamic Range (SFDR) Input Amplitude = –0.5 dBFS 100 98 98 88 dB typ Input Amplitude = –6.0 dBFS 94 100 94 84 dB typ INPUT TEST FREQUENCY: 500 kHz Signal to Noise Ratio (SNR) Input Amplitude = –0.5 dBFS 86.5 82 74 63 dB typ80.5 dB min Input Amplitude = –6.0 dBFS 82.5 77 68 58 dB typ SNR and Distortion (SINAD) Input Amplitude = –0.5 dBFS 86.0 81 74 63 dB typ80.0 dB min Input Amplitude = –6.0 dBFS 82.0 77 68 58 dB typ Total Harmonic Distortion (THD) Input Amplitude = –0.5 dBFS –97.0 –92 –89 –86 dB typ–90.0 dB max Input Amplitude = –6.0 dBFS–95.5 –96 –89 –86 dB typ Spurious-Free Dynamic Range (SFDR) Input Amplitude = –0.5 dBFS 99.0 92 91 88 dB typ90.0 dB maxAD9260Rev. C | Page 5 of 44Parameter—Decimation Factor (N)AD9260(8) AD9260(4) AD9260(2) AD9260(1) Unit Input Amplitude = –6.0 dBFS98 100 91 82 dB typ INPUT TEST FREQUENCY: 1.0 MHz (typ) Signal-to-Noise Ratio (SNR) Input Amplitude = –0.5 dBFS 85 82 74 63 dB typ Input Amplitude = –6.0 dBFS 80 76 68 58 dB typ SNR and Distortion (SINAD) Input Amplitude = –0.5 dBFS 84.5 81 74 63 dB typ Input Amplitude = –6.0 dBFS 80 76 69 58 dB typ Total Harmonic Distortion (THD) Input Amplitude = –0.5 dBFS –102 –96 –82 –79 dB typ Input Amplitude = –6.0 dBFS–96 –94 –84 –77 dB typ Spurious-Free Dynamic Range (SFDR) Input Amplitude = –0.5 dBFS 105 98 83 80 dB typ Input Amplitude = –6.0 dBFS98 96 87 80 dB typ INPUT TEST FREQUENCY: 2.0 MHz (typ) Signal-to-Noise Ratio (SNR) Input Amplitude = –0.5 dBFS 82 74 63 dB typ Input Amplitude = –6.0 dBFS 76 68 58 dB typ SNR and Distortion (SINAD) Input Amplitude = –0.5 dBFS 81 73 62 dB typ Input Amplitude = –6.0 dBFS 76 69 58 dB typ Total Harmonic Distortion (THD) Input Amplitude = –0.5 dBFS –101 –80 –75 dB typ Input Amplitude = –6.0 dBFS–95 –80 –76 dB typ Spurious-Free Dynamic Range (SFDR) Input Amplitude = –0.5 dBFS 104 80 78 dB typ Input Amplitude = –6.0 dBFS100 83 79 dB typ INPUT TEST FREQUENCY: 5.0 MHz (typ) Signal-to-Noise Ratio (SNR) Input Amplitude = –0.5 dBFS 59 dB typ Input Amplitude = –6.0 dBFS 57 dB typ SNR and Distortion (SINAD) Input Amplitude = –0.5 dBFS 58 dB typ Input Amplitude = –6.0 dBFS57 dB typTotal H armonic Distortion (T H D)Input Amplitude = –0.5 dBFS –58 dB typ Input Amplitude = –6.0 dBFS–67 dB typ Spurious-Free Dynamic Range (SFDR) Input Amplitude = –0.5 dBFS 59 dB typ Input Amplitude = –6.0 dBFS 70 dB typINTERMODULATION DISTORTION f IN 1 = 475 kHz, f IN 2 = 525 kHz –93 –91 –91 –83 dBFS typ f IN 1 = 950 kHz, f IN 2 = 1.050 MHz –95 –86 –85 –83 dBFS typDYNAMIC C H ARACTERISTICSFull Power Bandwidth75 75 75 75 MHz typ Small Signal Bandwidth (A IN = –20 dBFS) 75 75 75 75 MHz typ Aperture Jitter2 2 2 2 ps rms typAD9260DIGITAL FILTER CHARACTERISTICSTable 4.Parameter AD9260 Unit 8× DECIMATION (N = 8)Pass-Band Ripple 0.00125 dB maxStop-Band Attenuation 82.5 dB minPass-Band 0 MHz min0.605 × (f CLOCK/20 MHz) MHz maxStop-Band 1.870 × (f CLOCK/20 MHz) MHz min18.130 × (f CLOCK/20 MHz) MHz maxPass-Band/Transition Band Frequency(–0.1 dB Point) 0.807 × (f CLOCK/20 MHz) MHz max(–3.0 dB Point) 1.136 × (f CLOCK/20 MHz) MHz maxAbsolute Group Delay113.55 × (20 MHz/f CLOCK) µs maxGroup Delay Variation 0 µs maxSettling Time (to ± 0.0007%)124.2 × (20 MHz/f CLOCK) µs max4× DECIMATION (N = 4)Pass-Band Ripple 0.001 dB maxStop-Band Attenuation 82.5 dB minPass-Band 0 MHz min1.24 × (f CLOCK/20 MHz) MHz maxStop-Band 3.75 × (f CLOCK/20 MHz) MHz min16.25 × (f CLOCK/20 MHz) MHz maxPass-Band/Transition Band Frequency(–0.1 dB Point) 1.61 × (f CLOCK/20 MHz) MHz max(–3.0 dB Point) 2.272 × (f CLOCK/20 MHz) MHz maxAbsolute Group Delay1 2.90 × (20 MHz/f CLOCK) µs maxGroup Delay Variation 0 µs maxSettling Time (to ± 0.0007%)1 5.05 × (20 MHz/f CLOCK) µs max2× DECIMATION (N = 2)Pass-Band Ripple 0.0005 dB maxStop-Band Attenuation 85.5 dB minPass-Band 0 MHz min2.491 × (f CLOCK/20 MHz) MHz maxStop-Band 7.519 × (f CLOCK/20 MHz) MHz min12.481 × (f CLOCK/20 MHz) MHz maxPass-Band/Transition Band Frequency(–0.1 dB Point) 3.231 × (f CLOCK/20 MHz) MHz max(–3.0 dB Point) 4.535 × (f CLOCK/20 MHz) MHz maxAbsolute Group Delay10.80 × (20 MHz/f CLOCK) µs maxGroup Delay Variation 0 µs maxSettling Time (to ± 0.0007%)1 1.40 × (20 MHz/f CLOCK) µs max1× DECIMATION (N = 1)Propagation Delay: t PROP13 ns maxAbsolute Group Delay (225 × (20 MHz/f CLOCK)) + t PROP ns max1 To determine overall Absolute Group Delay and/or Settling Time inclusive of delay from the sigma-delta modulator, add Absolute Group Delay and/or Settling Time pertaining to specific decimation mode to the Absolute Group Delay specified in 1 ×decimation.Rev. C | Page 6 of 44AD9260Rev. C | Page 7 of 44AD9260Rev. C | Page 8 of 44Table 5. Integer Filter Coefficients for First Stage Decimation Filter (23-Tap Half-Band FIR Filter)Lower CoefficientUpper CoefficientInteger ValueH(1) H(23) –1 H(2) H(22) 0 H(3) H(21) 13 H(4) H(20) 0 H(5) H(19) –66 H(6) H(18) 0 H(7) H(17) 224 H(8) H(16) 0 H(9) H(15) –642 H(10) H(14) 0 H(11) H(13) 2496 H(12)4048Table 6. Integer Filter Coefficients for Second Stage Decimation Filter (43-Tap Half-Band FIR Filter)Lower CoefficientUpper CoefficientInteger ValueH(1) H(43) 3 H(2) H(42) 0 H(3) H(41) –12 H(4) H(40) 0 H(5) H(39) 35 H(6) H(38) 0 H(7) H(37) –83 H(8) H(36) 0 H(9) H(35) 172 H(10) H(34) 0 H(11) H(33) –324 H(12) H(32) 0 H(13) H(31) 572 H(14) H(30) 0 H(15) H(29) –976 H(16) H(28) 0 H(17) H(27) 1680 H(18) H(26) 0H(19) H(25) –3204 H(20) H(24) 0H(21) H(23) 10274 H(22)16274NOTE: The composite filter undecimated coefficients (i.e., impulse response) in the 4× decimation mode can be determined by convolving the first stage filter taps with a “zero stuffed” version of the second stage filter taps (i.e., insert one zero between samples). Similarly, the composite filter coefficients in the 8× decimation mode can be determined by convolving the taps of the composite 4× decimation mode (as previously determined) with a “zero stuffed” version of the third stage filter taps (i.e., insert three zeros between samples).Table 7. Integer Filter Coefficients for Third Stage Decimation Filter (107-Tap Half-Band FIR Filter)Lower CoefficientUpper CoefficientInteger ValueH(1) H(107) –1 H(2) H(106) 0 H(3) H(105) 2 H(4) H(104) 0 H(5) H(103) –2 H(6) H(102) 0 H(7) H(101) 3 H(8) H(100) 0 H(9) H(99) –3 H(10) H(98) 0 H(11) H(97) 1 H(12) H(96) 0 H(13) H(95) 3 H(14) H(94) 0 H(15) H(93) –12 H(16) H(92) 0 H(17) H(91) 27 H(18) H(90) 0 H(19) H(89) –50 H(20) H(88) 0 H(21) H(87) 85 H(22) H(86) 0 H(23) H(85) –135 H(24) H(84) 0 H(25) H(83) 204 H(26) H(82) 0 H(27) H(81) –297 H(28) H(80) 0 H(29) H(79) 420 H(30) H(78) 0 H(31) H(77) –579 H(32) H(76) 0 H(33) H(75) 784 H(34) H(74) 0H(35) H(73) –1044 H(36) H(72) 0 H(37) H(71) 1376 H(38) H(70) 0H(39) H(69) –1797 H(40) H(68) 0 H(41) H(67) 2344 H(42) H(66) 0H(43) H(65) –3072 H(44) H(64) 0 H(45) H(63) 4089 H(46) H(62) 0H(47) H(61) –5624 H(48) H(60) 0 H(49) H(59) 8280 H(50) H(58) 0H(51) H(57) –14268 H(52) H(56) 0H(53) H(55) 43520 H(54)68508AD9260Rev. C | Page 9 of 44DIGITAL SPECIFICATIONSAVDD = +5 V , DVDD = +5 V , T MIN to T MAX unless otherwise noted. Table 8.ParameterAD9260 Unit CLOCK 1 AND LOGIC INPUTS High Level Input Voltage(DVDD = +5 V) +3.5 V min (DVDD = +3 V)+2.1 V max Low Level Input Voltage(DVDD = +5 V) +1.0 V min (DVDD = +3 V)+0.9 V max High Level Input Current (V IN = DVDD) ± 10 µA max Low Level Input Current (V IN = 0 V) ± 10 µA max Input Capacitance5pF typ LOGIC OUTPUTS (with DRVDD = 5 V)High Level Output Voltage (I OH = 50 µA) +4.5 V min High Level Output Voltage (I OH = 0.5 mA) +2.4 V min Low Level Output Voltage 2 (I OL = 0.3 mA) +0.4 V max Low Level Output Voltage (I OL = 50 µA) +0.1 V max Output Capacitance5 pF typ LOGIC OUTPUTS (with DRVDD = 3 V)High Level Output Voltage (I OH = 50 µA) +2.4 V min Low Level Output Voltage (I OL = 50 µA)+0.7V max1 Since CLK is referenced to AVDD, +5 V logic input levels only apply.2The AD9260 is not guaranteed to meet V OL = 0.4 V max for standard TTL load of I OL = 1.6 mA.ANALOG INPUTINPUT CLOCKDATA OUTPUTDAVREAD00581-C -008Figure 8. Timing DiagramAD9260Rev. C | Page 10 of 44INPUT CLOCKRESET DAV00581-C -009Figure 9. RESET Timing DiagramSWITCHING SPECIFICATIONSAVDD = +5 V , DVDD = +5 V , C L = 20 pF, T MIN to T MAX unless otherwise noted.分销商库存信息:ANALOG-DEVICESAD9260ASZ AD9260ASZRL。

ADI General RoHS Compliance Information说明书

1.RoHS compliant definitionADI defines RoHS compliant to mean Pb, Hg, Cd, Cr (+6), PBB, PBDE, DEHP, BBP, DBP and DIBP are not intentionally added during the manufacturing process and have upper concentration limits as defined below. In addition, RoHS compliant indicates the packages can withstand a peak reflow temperature of 255 +5/-0 deg C.RoHS Banned Substance CAS Number Maximum Concentration ValueHg (Mercury) 7439-92-1 1000 ppmPb (Lead) 7439-97-6 1000 ppmCd (Cadmium) 7440-43-9 100 ppmCr(+6) (Hexavalent Chromium) 18540-29-9 1000 ppmPBB (Polybrominated Biphenyl) - 1000 ppmPBDE (Polybrominated Diethyl Ether) - 1000 ppmDEHP (Bis(2-Ethylhexyl) phthalate ) - 1000 ppmBBP (Benzyl butyl phthalate) - 1000 ppmDBP (Dibutyl phthalate) - 1000 ppmDIBP (Diisobutyl phthalate) - 1000 ppm2.RoHS compliant package materials and terminal finishesADI offers RoHS compliant solutions for most of its products. Material sets have been qualified to withstand a +255°C (+5/-0°C) peak reflow temperature. The primary terminal finishes for plastic encapsulated and hermetic products are matte Sn plating with a post plating bake (1 hour at 150°C within 24 hours of plating, implemented between EIA date code 0518-0522), SnAgCu solder spheres, and Au plating. NiPdAu is also available for select products.3.Part naming convention for RoHS complianceThe ADI legacy standard naming convention for RoHS compliant products requires the letter "Z" as a suffix to the existing part number.All Hittite legacy products are RoHS Compliant. However, the Hittite Federal products standard naming convention for RoHS compliant products requires the letter "E" as a suffix to the existing part number.All LTC legacy products bearing the suffix "#PBF OR #TRPBF” after the part number are RoHS compliant.The suffix “Z”, “E” and "#PBF or #TRPBF" generally appears at the end of the part name (i.e. after the character that denotes the package style). For example:Standard Part Name RoHS Compliant Part NameADI Legacy Products ADM1024ARU-REEL ADM1024ARUZ-REELAD648KR AD648KRZHittite Legacy Products HMC6407LP5 HMC6407LP5EHMC199AMS8TR HMC199MS8ETRLTC Legacy Products LTC1517CS5-3.3 LTC1517CS5-3.3#PBFLTC6993MPS6-4#TR LTC6993MPS6-4#TRPBFCertain products introduced to the market as RoHS compliant only (i.e. there is no standard SnPb or SnPbAg finish on these parts) do not carry a "Z" suffix, but the data sheet, web product page, part marking, and labeling clearly indicate these products as RoHS compliant.All models intended to be offered as RoHS compliant are visible to customers through the WWW ordering guide.Customers should contact Local Sales or Distributors with any new product transition requests.4.Part marking convention for RoHS complianceRoHS compliant devices have a "#" symbol marked on the top or bottom of the package. Smaller packages, such as SOT23, SC70 and TSOT, are too small to accommodate an additional character, and as a result, there is no "#" marking on the package. For these smaller packages, a unique brand code is used to denote RoHS compliance.5.China RoHSAnalog Devices products considered as EU RoHS Compliant part, do not contain any China RoHS substance above the indicated levels set forth in the People’s Republic of China Electronic Industry Standard SJ/T 11364-2006 for theRequirements for Concentration Limits for Certain Hazardous Substances in Electronic Information Product.beling for RoHS complianceShipping containers for products compliant with RoHS regulations are labeled with “RoHS Compliant” and Chinaenvironment-friendly logos. The labels also contain the Pb free external finish code (i.e., e3, e1, etc) as specified in JEDEC JESD97 standard and MSL ratings.Shipping LabelLOGOS RoHS China Environment-Friendly Use Period or EFUP *RoHSCompliantRoHS ExemptSOT23 FCOL, , Flip chip CSP BGA and Flip chip BGA_ED labeled as “RoHS with Exemption” use lead contained solder bumps that fall under Exemption 15 Lead in solders to complete a viable electrical connection between semiconductor die and carrier within integrated circuit flip chip packages9.Reflow ProfileADI advises reflow profiles should conform to JEDEC J-STD-020 standard which can be downloaded from the JEDEC website under “Free Standards”./9.Backward and forward compatibilityBackward compatibility for matte Sn, NiPdAu and Au: ADI products with matte Sn, NiPdAu, and Au finishes are backward compatible with optimized SnPb reflow processes.Backward compatibility for SnAgCu: ADI products with SnAgCu solder finishes are not backward compatible with SnPb reflow processes.Forward compatibility for SnPb: ADI products with SnPb finish are not forward compatible with +255°C (+5/-0°C) reflow processes. Concerns include weak solder joints caused by Bi in the solder paste reacting with Pb delamination resulting from package material sets that are not +255°C (+5/-0°C) compatible, and solder ball voiding caused by Pb free solder paste outgassing into the solder ball.10.Matte Sn whisker dataMatte Sn is a widely available industry standard that has been in production for many years with excellent quality and reliability. All matte Sn plated devices undergo a post plating bake for 1 hour at 150 degrees C within 24 hours of plating to mitigate Sn whisker growth. Sn whisker testing is done based on the test methodology outlined in JEDEC JESD22A121 standard (Test Method for Measuring Whisker Growth on Tin and Tin Alloy Surface Finishes) with read-point intervals of 1000 hours or 500 cycles. Test results are in the table below.Criteria Maximum 20 um(Class 1a) Maximum 40 um(Class 2)Maximum 45 um(Class 2)Package Preconditioning Temperature HumidityStorage(30/60%RH, 4000 Hrs)High TemperatureHumidity Storage(55'C/85%RH, 4000 Hrs)Temperature Cycle(-55/+85'C,1500 Cyc)LFCSPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableLQFPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableMQFPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableMINISONo precon See QSOP results See QSOP results See QSOP results Precon @ 215-220'C See QSOP results See QSOP results See QSOP results Precon @ 260'C Acceptable Acceptable AcceptablePDIPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableCriteria Maximum 20 um(Class 1a) Maximum 40 um(Class 2)Maximum 45 um(Class 2)Package Preconditioning Temperature HumidityStorage(30/60%RH, 4000 Hrs)High TemperatureHumidity Storage(55'C/85%RH, 4000 Hrs)Temperature Cycle(-55/+85'C,1500 Cyc)PLCCNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptablePSOPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableQSOPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableSC70/ SOT143/ SOT23-3LdNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableSOIC_NNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableSOIC_WNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableSOT223No precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableSOT23No precon See QSOP results See QSOP results See QSOP results Precon @ 215-220'C See QSOP results See QSOP results See QSOP results Precon @ 260'C Acceptable Acceptable AcceptableSSOPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableTQFPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableTSSOPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable Acceptable11. RoHS Compliance for Evaluation BoardsAnalog Devices evaluation boards are specifically designed for the purpose of research and development and are made available solely on a business-to-business basis and are therefore excluded from the scope of the RoHS 2 Directive.。

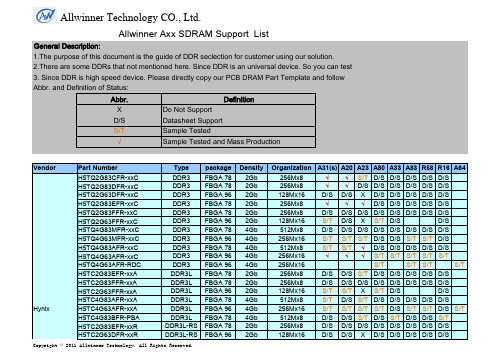

全志科技股份有限公司Allwinner A系列SDRAM支持列表说明书

Allwinner Axx SDRAM Support ListGeneral Description:1.The purpose of this document is the guide of DDR seclection for customer using our solution.2.There are some DDRs that not mentioned here. Since DDR is an universal device. So you can test3. Since DDR is high speed device. Please directly copy our PCB DRAM Part Template and followAbbr. and Definition of Status:Abbr.DefinitionX Do Not SupportD/S Datasheet SupportS/T Sample Tested√Sample Tested and Mass ProductionVendor Part Number Type package Density Organization A31(s)A20A23A80A33A83R58R16A64Hynix H5TQ2G83CFR-xxC DDR3FBGA 782Gb256Mx8√√S/T D/S D/S D/S D/S D/SH5TQ2G83DFR-xxC DDR3FBGA 782Gb256Mx8√√D/S D/S D/S D/S D/S D/SH5TQ2G63DFR-xxC DDR3FBGA 962Gb128Mx16D/S D/S X D/S D/S D/S D/S D/SH5TQ2G83EFR-xxC DDR3FBGA 782Gb256Mx8√√√D/S D/S D/S D/S D/SH5TQ2G83FFR-xxC DDR3FBGA 782Gb256Mx8D/S D/S D/S D/S D/S D/S D/S D/SH5TQ2G63FFR-xxC DDR3FBGA 962Gb128Mx16S/T D/S X S/T D/S D/SH5TQ4G83MFR-xxC DDR3FBGA 784Gb512Mx8D/S D/S D/S D/S D/S D/S D/S D/SH5TQ4G63MFR-xxC DDR3FBGA 964Gb256Mx16S/T S/T S/T D/S D/S S/T S/T D/SH5TQ4G83AFR-xxC DDR3FBGA 784Gb512Mx8S/T S/T√D/S D/S D/S D/S D/SH5TQ4G63AFR-xxC DDR3FBGA 964Gb256Mx16√√√S/T S/T S/T S/T S/TH5TQ4G63AFR-RDC DDR3FBGA 964Gb256Mx16S/T S/T S/T S/T H5TC2G83EFR-xxA DDR3L FBGA 782Gb256Mx8D/S D/S S/T D/S D/S D/S D/S D/SH5TC2G83FFR-xxA DDR3L FBGA 782Gb256Mx8D/S D/S D/S D/S D/S D/S D/S D/SH5TC2G63FFR-xxA DDR3L FBGA 962Gb128Mx16S/T S/T X S/T D/S D/SH5TC4G83AFR-xxA DDR3L FBGA 784Gb512Mx8S/T D/S S/T D/S D/S D/S D/S D/SH5TC4G63AFR-xxA DDR3L FBGA 964Gb256Mx16S/T S/T S/T S/T D/S S/T S/T D/S S/T H5TC4G83BFR-PBA DDR3L FBGA 784Gb512Mx8D/S D/S S/T D/S S/T D/S D/S S/TH5TC2G83EFR-xxR DDR3L-RS FBGA 782Gb256Mx8D/S D/S D/S D/S D/S D/S D/S D/SH5TC2G63DFR-xxR DDR3L-RS FBGA 962Gb128Mx16D/S D/S X D/S D/S D/S D/S D/SH5TC2G63FFR-xxR DDR3L-RS FBGA 962Gb128Mx16D/S D/S X D/S D/S D/S D/S D/SH5TC4G83AFR-xxR DDR3L-RS FBGA 784Gb512Mx8D/S D/S D/S D/S D/S D/S D/S D/SH5TC4G63AFR-xxR DDR3L-RS FBGA 964Gb256Mx16D/S D/S D/S D/S D/S D/S D/S D/SH5TC8G63AMR-PBA DDR3L FBGA 968Gb256Mx16x2CS D/S D/S X S/T S/T S/T S/T S/TH5TC8G83AMR-PBA DDR3L FBGA 788Gb512Mx8x2CS D/S D/S X D/S D/S D/S D/S D/SH5TC4G63CFR-PBA DDR3L FBGA 964Gb256Mx16D/S D/S D/S D/S D/S S/T S/T D/S S/T H9TKNNN8JDAPLR-NGN LPDDR28Gb128Mx32x2CS D/S X X D/S X D/S D/S XH9CCNNN8JTALAR-NTD LPDDR3FBGA 1788Gb128Mx32x2CS D/S X X S/T X S/T S/T XH9CCNNNBLTALAR-NTM LPDDR3FBGA 17816Gb256Mx32x2CS S/T S/TH9CKNNN8GTMPLR-NUH LPDDR3POP 1688Gb128Mx32x2CS S/T S/TH9CCNNNBJTMLAR-NUM LPDDR3POP 16816Gb256Mx32x2CSNanya(南亚)NT5CB128M8DN-xx DDR3FBGA 781Gb128Mx8D/S S/T X X X D/S D/S XNT5CB256M8GN-xx DDR3FBGA 782Gb256Mx8S/T S/T S/T D/S S/T D/S D/S S/TNT5CB256M8FN-xx DDR3FBGA 782Gb256Mx8S/T S/T S/T D/S D/S D/S D/S D/SNT5CB128M16HP-xx DDR3FBGA 962Gb128Mx16S/T S/T X S/T D/S D/SNT5CB128M16FP-xx DDR3FBGA 962Gb128Mx16D/S D/S X D/S D/S D/SNT5CB256M16BP-xx DDR3FBGA 964Gb256Mx16S/T S/T S/T S/T S/T D/S D/S S/TNT5CC512M8CN-xx DDR3L FBGA 784Gb512Mx8S/T S/T S/T D/S D/S D/S D/S D/SNT5CC256M16CP-xx DDR3L FBGA 964Gb256Mx16S/T D/S D/S D/S D/S D/S D/S D/SNT5CC256M16CP-DI DDR3L FBGA 964Gb256Mx16S/T S/T S/T S/T S/T S/T NT6CL256T32AQ-H2LPDDR3POP 1688Gb128Mx32x2CS S/T S/TNT6CL128M32AQ-H2LPDDR3POP 1684Gb128Mx32x1CS D/S D/SNT5CC256M16DP-DI DDR3L FBGA 964Gb256Mx16S/T S/T S/T S/T NT5CC128M16IP-DI DDR3L FBGA 962Gb128Mx16NT5CB64M16FP-DH DDR3FBGA 961Gb64Mx16NT6TL256T32AQ-G1LPDDR2POP 1688Gb128Mx32x2CS S/T S/TNT6TL128M32AQ-G0LPDDR2POP 1684Gb128Mx32x1CS S/T S/TNT5CC64M16GP-DI DDR3L FBGA 961Gb64Mx16Elpida EDJ2108BDBG-DJ-F DDR3FBGA 782Gb256Mx8D/S D/S D/S D/S D/S D/S D/S D/SEDJ4216EFBG-GN-F DDR3FBGA 964Gb256Mx16S/T S/T S/T S/T S/T D/S D/S S/TEDJ4208EFBG-GNL-F DDR3L FBGA 784Gb512Mx8S/T S/T D/S D/S D/S D/S D/S D/SEDJ4208EFBG-GN-F DDR3FBGA 784Gb512Mx8S/T S/T D/S D/S D/S D/S D/S D/SEDJ4216EFBG-GNL-F DDR3L FBGA 964Gb256Mx16S/T S/T S/T D/S S/T D/S D/S S/T S/T J2108DEBG-DJ-F DDR3FBGA 782Gb256Mx8D/S D/S D/S D/S D/S D/S D/S D/SAllwinner Technology CO., Ltd.ElpidaEDB8132B3MC-8D-F LPDDR28Gb128Mx32x2CS S/T X X S/T X D/S D/S XEDB8132B2MA-8D-F LPDDR28Gb128Mx32x2CS D/S X X S/T X D/S D/S XEDFA232A1MA-GD-F LPDDR316Gb256Mx32x2CS D/S X X D/S X D/S D/S XMicron MT41K256M8DA-125DDR3L FBGA 782Gb256Mx8D/S D/S S/T D/S D/S D/S D/S D/SMT41K128M16JT-125DDR3L FBGA 962Gb128Mx16S/T D/S X X X D/S D/S XMT41J128M16JT-107DDR3FBGA 962Gb128Mx16S/T S/T X X X D/S D/S XMT41K256M16HA-125DDR3L FBGA 964Gb256Mx16S/T D/S S/T S/T S/T D/S D/S S/T S/T MT41K512M8RH-125DDR3L FBGA 784Gb512Mx8D/S D/S S/T D/S D/S D/S D/S D/SMT41J256M8HX-15DDR3FBGA 782Gb256Mx8D/S D/S S/T D/S S/T D/S D/S S/TSAMSUNG K4B4G1646B-HCK0DDR3FBGA 964Gb256Mx16S/T S/T S/T D/S D/S S/T S/T D/SK4B2G1646E-BCK0DDR3FBGA 962Gb128Mx16S/T D/S X D/S D/S D/SK4B2G0846D-HCK0DDR3FBGA 782Gb256Mx8D/S D/S D/S D/S D/S D/S D/S D/SK4B2G1646Q-BCK0DDR3FBGA 962Gb128Mx16S/T D/S X D/S S/T D/S D/S S/TK4B4G1646Q-HYK0DDR3L FBGA 964Gb256Mx16S/T S/T S/T S/T S/T S/T S/T S/T S/T K4B8G1646Q-MYK0DDR3L FBGA968Gb256Mx16x2CS D/S D/S X D/S D/S S/T S/T D/SK4B4G1646D-BCK0DDR3FBGA964Gb256Mx16S/T K4E8E304ED-EGCF LPDDR3FBGA 1788Gb128Mx32x2CS D/S X X S/T X S/T S/T XK4E8E304ED-EGCE LPDDR3FBGA 1788Gb128Mx32x2CS D/S X X D/S X S/T S/T XK4E8E304ED-EGCC LPDDR3FBGA 1788Gb128Mx32x2CS D/S X X S/T X S/T S/T XK4E4E324ED-EGCF LPDDR3FBGA 1784Gb128Mx32x1CS S/T X X D/S X D/S D/S XK4P8G304EG-AGC2LPDDR2POP 1688Gb128Mx32x2CS S/T X X D/S X D/S D/S XK4E8E304EE-EGCE LPDDR3FBGA 1788Gb128Mx32x2CS D/S X X S/T X S/T S/T X S/T K4E6E304EE-EGCE LPDDR3FBGA 17816Gb256Mx32x2CS S/T S/TK4P8G304EQ-AGC2LPDDR2POP 1688Gb128Mx32x2CS S/T S/T S/T K4E8E304EE-AGCE LPDDR3POP 1688Gb128Mx32x2CS S/T S/TK4E4E164EB-EGCE LPDDR3FBGA 1784Gb128Mx32x1CS S/T S/TKingston(金士顿)D2516EC4BXGGB DDR3FBGA 964Gb256Mx16S/T S/T S/T D/S D/S S/T S/T D/SPSC/Mira (力晶)P3P4GF3BLF-GGN DDR3FBGA 784Gb512Mx8D/S S/T S/T D/S D/S D/S D/S D/S P3P4GF4BLF-GGN DDR3FBGA 964Gb256Mx16S/T S/T S/T D/S S/T D/S D/S S/T P3P4GF4BLF-GDJ DDR3FBGA 964Gb256Mx16D/S S/T S/T D/S D/S D/S D/S D/S P3P2GF3BLF-AGGN DDR3FBGA 782Gb256Mx8S/TAllwinner Technology CO., Ltd.Etron (钰创)EM6GE16EW5B-15H DDR3FBGA 964Gb 256Mx16S/T S/T S/T D/S D/S D/S D/S D/S EM6GD08EWUA-15H DDR3FBGA 782Gb 256Mx8D/S D/S S/T D/S S/T D/S D/S S/T EM6GD08EWUA-12H DDR3FBGA 782Gb 256Mx8D/SD/S S/T D/S D/S D/S D/S D/SEM6GD16EWXC-12HDDR3FBGA 962Gb 128Mx16EM6GE16EWXC-12HDDR3FBGA 964Gb 256Mx16S/T D/S D/S EM6GD08EWUC-12H DDR3FBGA 782Gb 256Mx8S/T D/S D/S EM6GE08EW8C-12H DDR3FBGA 784Gb 512Mx8S/TD/S D/SEM6GE16EWXD-12H DDR3FBGA 964Gb 256Mx16SCSemicon (华芯)HXB15H2G800BF-15H DDR3FBGA 782Gb 256Mx8S/T S/T S/T D/S D/S D/S HXB15H2G160BF-15H DDR3FBGA 962Gb 128Mx16D/S S/T X X X X HXB15H4G160BF-15HDDR3FBGA 964Gb 256Mx16S/T S/T S/T D/S S/T S/T HXB15H4G800BF-15H DDR3FBGA 784Gb 512Mx8D/S D/S S/T D/S D/S D/S HXB15H4G800AF-15HDDR3FBGA 784Gb 512Mx8D/S D/S S/T D/S D/SD/S HXB13H4G160BF(L)-13K DDR3L FBGA 964Gb 256Mx16D/S D/SD/S D/S D/S S/T S/T D/SHXB15H2G800BF-13K DDR3FBGA 782Gb 256Mx8S/THXB15H2G160BF-13KDDR3FBGA 962Gb 128Mx16PI (补丁)PMF511808DBR-KADN DDR3FBGA 782Gb 256Mx8D/S D/S S/T D/S D/S D/S PMF512816BBR-KADN DDR3FBGA 964Gb 256Mx16S/T S/T S/T D/S D/S S/T S/T D/S PMF511808BBRDDR3FBGA 782Gb 256Mx8D/S D/S S/T D/S D/S D/S eorex (森富)EM47DM0888SBA-150DDR3FBGA 781Gb 128Mx8D/S D/S X X X XEM47EM0888SBA-150DDR3FBGA 782Gb 256Mx8D/S D/S S/T D/S D/S D/S EM47CM1688SBB-150DDR3FBGA 961Gb 64Mx16D/S D/S X X X X EM47EM1688SBA-150DDR3FBGA 964Gb 256Mx16D/S S/T S/T D/S D/S D/S EM47EM3288SBA-150DDR38Gb 256Mx32S/T D/S X X XXGT (创芯)GT8UB128M16HP DDR3FBGA 962Gb 128Mx16S/T S/T X D/S D/S D/S GT8UB128M16BP DDR3FBGA 962Gb 128Mx16D/S S/T X D/S D/S D/S GT8UB256M16BP DDR3FBGA 964Gb 256Mx16S/T S/T S/T D/S D/S S/T S/T D/S GT8UB256M8EN-BG DDR3FBGA 782Gb 256Mx8D/S D/S S/T D/S D/S D/S GT8UB512M8EN-BGDDR3FBGA 784Gb512Mx8D/SD/S S/T D/S D/S D/SEG EG1L256M88BA12LH DDR3FBGA 782Gb 256Mx8D/S D/S S/T D/S D/S D/SAllwinner Technology CO., Ltd. EGElixir N2CB2G80GN DDR3FBGA 782Gb256Mx8D/S S/T S/T D/S D/S D/S N2CB4G16CP-DI DDR3FBGA 964Gb256Mx16D/S D/S S/T D/S D/S D/S华聆 xeme H2A402G1666ADBC DDR3FBGA 962Gb128Mx16H2A402G0866CD3C DDR3FBGA 782Gb256Mx8H2A404G0866ED9C DDR3FBGA 784Gb512Mx8H2C402G1666ADBC DDR3FBGA 962Gb128Mx16H2C402G0866CD3C DDR3FBGA 782Gb256Mx8H2C402G0866BD3C DDR3FBGA 782Gb256Mx8H2C404G0866ADEC DDR3FBGA 784Gb512Mx8H2C404G1666ADFC DDR3FBGA 964Gb256Mx16S/T S/T S/T S/T H2C404G0866CD8C DDR3FBGA 784Gb512Mx8H2C402G1666BDBC DDR3FBGA 962Gb128Mx16X X H2A402G0866CD3C DDR3FBGA 782Gb256Mx8XGCAI GDB41A32ED7-D1S LPDDR2POP 1684Gb128Mx32x1CS GDB42A32ED7-D1S(25nm)LPDDR2POP 1688Gb128Mx32x2CS GDB42A32ED7-D1S(30nm)LPDDR2POP 1688Gb128Mx32x2CS。

ADL5565差分放大器与AD9467 ADC接口电路设计说明书

为窄带、高中频、16位、250 MSPS 接收机前端设计带通滤波器的谐振匹配方法评估和设计支持设计和整合文件原理图、布局文件、物料清单电路功能与优势图1所示的电路是一款16位、250 MSPS 、窄带、高中频接收机前端,其中在ADL5565差分放大器与AD9467 ADC 之间提供最佳接口。

AD9467是一款缓冲输入16位、200 MSPS 或250 MSPS ADC ,具有约75.5 dBFS 的SNR 性能和介于95 dBFS 与98 dBFS 之间的SFDR 性能。

由于具有高输入带宽、低失真和高输出线性度,ADL5565差分放大器适合驱动中频采样ADC 。

本电路笔记介绍了如何设计接口电路和抗混叠滤波器才能在保持高性能的同时确保最低信号损耗的系统化过程。

使用谐振匹配方法来设计最平坦的巴特沃兹四阶带通滤波器,中心频率为200 MHz 。

电路描述使用差分放大器来驱动高速ADC 的优势包括信号增益、隔离和ADC 与源阻抗匹配。

ADL5565允许6 dB 、12 dB 或 15.5 dB 的引脚绑定增益调整。

或者,通过对输入应用两个外部电阻,可在0 dB 至15.5 dB 范围内实现更精细的增益步进。

此外,ADL5565具有高输出线性度、低失真、低噪声和宽输入带宽。

3 dB 带宽为6 GHz ,0.1 dB 平坦度为1 GHz 。

ADL5565能实现大于50 dB 的输出三阶交调截点(OIP3)。

10560-001图1. 使用ADL5565差分放大器和AD9467 ADC 完成窄带高中频应用的谐振滤波器设计电路笔记Rev.0Circuits from the Lab™ circuits from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any Circuits from the Lab circuits. (Continued on last page)One Technology Way, P .O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 /zh Fax: 781.461.3113 ©2012 Analog Devices, Inc. All rights reserved.为实现ADL5565和AD9467必须提供的最佳性能水平,必须严格遵循各数据手册中指定的设计原则。

ADX自动静态电机分析器系列说明书

ADXAutomated Static Motor Analyzer■Complete range of essential tests to determine motor health, analyze trends, and find faults.■These include high voltage tests for surge, PD,DC insulation resistance (IR, DA, PI), and DC HiPot (standard, step, or ramp).■Plus, low voltage testing for winding resistance,inductance, and capacitance.■Test voltages from 4 kV to 15 kV (and up to 40 kV coupled with a Megger Baker PPX.■Available with built-in armature hardware in the ADX 15A model.DESCRIPTIONFEATURESThe ADX family includes models designed to perform tests up to 15 kV. The five main options include 4 kV, 6 kV, 12 kV, 15 kV, and 15 kV-A (Armature). These analyzers can be coupled with PPX to increase test voltages to 30 kV or 40 kV for tests on high voltage motors, coils, and generators.The Megger Baker ADX is used for motor winding, coil, assembled motor, and generator testing. It will be used by Original Equipment Manufacturers, Industrial Maintenance Engineers, Motor Repair Shops, and Service Engineers working on equipment in the field for verification, validation, fault finding, and research; or to serve as part of a maintenance program. Tests Performed:■Winding Resistance ■Inductance ■Capacitance ■Insulation Resistance ■Dielectric Absorption (DA)■Polarization Index (PI)■DC HiPot ■DC Step-Voltage ■DC Continuous Ramped ■Surge analysis with EAR+™■Partial Discharge on Surge■Detachable IEC61010-compliant HV / LV Kelvin test leads ■PowerDB Dashboard secure cloud-based analysis software ■10.4-inch daylight viewable touch screen ■Industrial IP68 Waterproof Silicone Keyboard ■Choice of Manual, Automatic, or Sequence testing ■Screen-level context sensitive help ■Adaptable search capability ■Asset management tools ■Configurable Route based testing■Pulse-to-Pulse and Line-to-Line Error Area Ratio analysis ■Import existing databases from AWA and DX ■Android operating system■ 2 x USB ports and ethernet connection ■HDMI port for duplicating screens ■Wi-Fi and Bluetooth enabled ■Foldable viewing standBENEFITS■Asset-centric approach provides opportunities for turnkey testing.■Sequence mode leverages the approach for fully-automatic testing.■Data analysis features identify service needs and reduce down time.■Remote asset configuration via PowerDB Dashboard frees the ADX for testing needs.■Separating Asset from Installation opens opportunities for dataanalysis.DATA STORAGE, ANALYSIS, REPORT GENERATION, AND MANAGEMENTAll test results are saved and stored locally on the ADX, and are automatically synchronized with the cloud-based application PowerDB Dashboard for users with internet connection.Test results can be analyzed through Dashboard. Comparing current and historical data can reveal downward trends and other issues, indicating when action should be taken to service assets and avoid unplanned downtime.The built-in Report Generator provides on-board test result viewing that can be sent directly to a printer. Reports can be printed from the ADX wirelessly to a networked printer, or directly via a USB-connected printer. Data can be accessed securely through PowerDB Dashboard to view and download reports in either MS Word or PDF. Data can also be exported in other formats such as CSV.The ADX can function as an off-line system, utilizing PowerDB Print Engine software to create, edit, and print reports on a local computer. Data is transferred via ADX export to a USB drive, uploaded to a local computer, and edited as anMS Word document.ADX software allows users to easily create, view, and edit assets, test configurations, installations, and routes. The asset-centric approach provides administrators and management with all the tools needed to set up a turnkey environment, simplifying the asset testing process for operators.Asset configuration can be done directly on the ADX or remotely via PowerDB Dashboard. The integrated system allows access through any internet-connected device to create and edit assets, test configurations, installations, and routes. No matter where the changes are made, they are automatically synchronized between the ADX and PowerDB Dashboard via internet connection.EASE OF USEThe ADX has a large, 10.4-inch touch screen. The industrial-grade, daylight-viewable color display was designed to work in all environments. The user interface features large, intuitive icons for easy touch operation—even when an operator is wearing insulated electrical gloves.ADDITIONAL KEY FEATURES■High-definition graphical user interface displays surge test waveforms.■Displays DC HiPot results.■Displays hundreds of coil waveforms for quick analysis.■Stores reference waveforms for comparison coil testing.■Secure cloud-based data storage■Ability to create and edit assets and test configurations remotely through PowerDB Dashboard■Internal battery backup secures data due to unexpected power loss.ACCESSORIESMegger DLRO Connect systemUsed for low-voltage testing along with the RLC adapter.Number Description Part Number1014-0291 ADX modular lead, DLRO Connect accessories. Connects to the ADX RLC adapter andextension lead.1006-4602 Duplex connector extension lead3 m long. Connects to ADX modular lead and anyDLRO Connect termination.3 Duplex connector handspike probe with spring-loaded tips. 1006-4504 Duplex connector concentric handspike. 1006-4485 Duplex connector handspike twist probe with spring-loaded tips. 1006-4496 Duplex connector Kelvin clip 1. Touch-proof clip with adjustable jaws. 1006-4517 Duplex connector Kelvin clip 1. General-purpose heavy-duty clip. 1006-447Remote Test Status Indication Lights and Remote E-StopNumber Description1 Remote Test Status Indication Lights E-Stop (TSIL-ES).2 Remote Test Status Indication Lights (TSIL). A Stop Jumper must be installed on the open connector if a remoteE-Stop (1) is not used.Foot switchYou can connect the footswitch (optional) to the Megger Baker ADX host or auxiliary units; it works in parallel with the Start (PTT) button. The footswitch enables hands-free use of the unit and gives you additional operating position options.Surge Test Probes and ClipsThe Megger Baker ADX features accessories that facilitate surge testing including the Megger ADX Armature Surge Hand-held Probes (ADX-ASP), which are used during armature bar-to-bar testing.ADX Armature Surge ClipsThe ADX Armature Surge Clips (ADX-ASC) are commonly used during coil and DC motor testing. The longer middle section of the clips employs a shielded cable.ADX Armature Surge accessoryFor armature bar-to-bar surge testing, you can use the ADX Armature Surge accessory— (ADX ARM SRG).NOTICE: Armature surge test and other fixtures used with legacy equipment are not compatible with the ADX tester.SPECIFICATIONSPhysical specificationsModel Mass Size (W x D x H)ADX1546.3 lbs. (21 kg)18 x 23 x 8.5 in (457 x 584 x 216 mm) ADX15A50.7 lbs. lbs. (23 kg)18 x 23 x 8.5 in (457 x 584 x 216 mm) System specificationsParameter ValueInternal memory RAM 2GB DDR3Internal storage 8GB MMC and 480GB SSD DriveProcessor speed 1.0 Ghz (Quad core)User interface Capacitive touch screen, mouse, keyboard, stylus Platform AndroidDisplay 10.4-in touch screenResolution XGA 1024 x 768Bluetooth 4.1 / BLE with CSA2 supportWi-Fi 802.11 a/b/g/n Dual Band 2.4 / 5 GHzEthernet Gigabit Ethernet 10/100/1000 MbpsUSB flash drive USB 2.0Battery Backup 4+ hours standby timeLanguages supported—user interface and documentation localizationLanguage Regional TranslationsEnglishFrench EuropeSpanish Europe and Latin AmericaPortuguese Europe and BrazilGermanCzechRussianChinese Traditional and SimplifiedInstrument rating summaryParameter Variant / Option ValueInternal and operating environment Pollution degree 2Operating altitude ≤ 3,000 m (9,842 ft)Operating temperature 5–40° C (41–104° F)Operating humidity ≤ 80% RH for temperature up to 31°C (88° F),decreasing linearly to 50% RH at 40° C (104° F). Storage temperature 0–60° C (32–140° F)Ensure that the unit has sufficient time to warm to ambient temperature beforeoperating after storing the unit in a colder area.Storage humidity Less than 95% non-condensing.IP Rating IP40Mains Power Input 90–264 VAC, 47–63 Hz, 2.5 A,CAT II 300 VMaximum generated voltage Peak voltage for AC or DC test ADX4 Nominal 100 V–4 kV ADX6 Nominal 100 V–6 kV ADX12 Nominal 100 V–12 kV ADX15 Nominal 100 V–15 kV ADX15A Nominal 100 V–15 kVMaximum input voltage rating Must be connected only to isolated, de-energizedcircuits. See Caution below.Standard Kelvin 4-wire test leads voltage rating 16 kV DC peakCAUTIONThe ADX must be connected only to isolated, de-energized circuits. Connection to live circuitry can expose personnel to severe electrical shock risk, permanently damage tester, and void warranty. Refer to chapter 1, “General Operating and Safety Information” for complete information on safely connecting and operating the unit.DC IR and HiPot test specificationsParameter Variant ValueVoltage accuracy ± 2% ± 5 VMaximum output current 1.2 mADisplayed current resolution 1 nACurrent measurement resolution 16 pACurrent accuracy Test voltage 0–2 kV ± 4% ± 5 nATest voltage 2–4 kV ± 4% ± 10 nATest voltage 4–8 kV ± 4% ± 25 nA Overcurrent trip settings Adjustable to 1.2 mA Overcurrent trip settings IR measurement range 100 kΩ–1 TΩ IR measurement range Surge test specificationsParameter Variant ValueNominal surge capacitance 100 nFTypical surge energy 11.25 J at 15 kV Typical short circuit current 700 ARepetition rate 4 Hz nominal Minimum inductance 4 kV 70 µH6 kV 100 µH12 kV 120 µH15 kV 170 µHVoltage accuracy ±10%Surge with Partial Discharge (PD) test specificationsParameter ValueInception and extinction voltages (PDIV, PDEV) Measured per IEC 61934 Repetitive inception and extinction voltages (RPDIV, RPDEV) Measured per IEC 61934 Programmable PD threshold range (Resolution to 0.1 mV) 1.0–999 mVPD time scaling 1.024–26,400 µsResistance test specificationsParameter Value Measurement range 0.001 mΩ–1 MΩ4-wire measurement YesMaximum test current 10 AAccuracy ±2% ±0.25 mΩ Inductance test specificationsParameter Value Measurement range 0.01 µH–10 H (120 Hz)0.01µH–200 mH (1000 Hz)4-wire measurement YesTest frequency 120, 1000 Hz Capacitance test specificationsParameter Value Measurement range 0.01 nF–50 µF4-wire measurement YesTest frequency 4000 HzAccuracy ±5% ±1 nFADX testing and safety standards complianceStandard TopicIEC 61326-1 Ed. 2.0 2012-07 Electrical equipment for measurement, control, and laboratory use - EMC requirements –Table 1.FCC 47CFR: Part 15 Subpart B: 2020 Unintentional RadiatorsICES-003 Issue 7, October 2020 Limits and Methods of Measurement to Information Technology Equipment (includingDigital Apparatus).IEC 61010-031:2015 Safety requirements for electrical equipment for measurement, control, and laboratoryuse. Safety requirements for hand-held probe assemblies for electrical measurement andtest.IEC 61010-2-034:2017 Safety requirements for electrical equipment for measurement, control, and laboratoryuse. Particular requirements for measurement equipment for insulation resistance and testequipment for electric strength.IEC 62133-2:2017 Safety Test Standard of Li-IonCISPR 11:2009 +A1:2010, Class A Radiated Emissions and AC Mains Conducted EmissionsIEC 61000-3-2:2014 HarmonicsIEC 61000-3-3:2013 FlickerIEC 61000-4-2:2009 Electro-Static Discharge Immunity TestIEC 61000-4-3:2010 Radiated, Radio-Frequency, Electromagnetic ImmunityIEC 61000-4-4:2012 Electrical Fast Transient/Burst Immunity TestIEC 61000-4-5:2006 Immunity to SurgesIEC 61000-4-8:2010 Power Frequency Magnetic Field Immunity TestIEC 61000-4-11:2004 Voltage Dips/Interruptions Immunity TestORDERING INFORMATIONItem Description PartNumber Item Description PartNumberADX 44 kV Standard ADX with DC Insulation Resistance (IR, DA, PI), DC HiPot (standard, Step, Ramp), and Surge tests only. 1013-911 ADX 1212 kV Standard ADX with DC InsulationResistance (IR, DA, PI), DC HiPot (standard,Step, Ramp), and Surge tests only.1013-913ADX-4-RLC4 kV Standard ADX with RLC (low voltage Resistance, Inductance, and Capacitance), DC Insulation Resistance (IR, DA, PI), DC HiPot (standard, Step, Ramp), and Surge tests. 1013-916 ADX-12-RLC12 kV Standard ADX with RLC (low voltageResistance, Inductance, and Capacitance), DCInsulation Resistance (IR, DA, PI), DC HiPot(standard, Step, Ramp), and Surge tests.1013-918ADX-4-RLC-PD4 kV Standard ADX with RLC (low voltage Resistance, Inductance, and Capacitance), DC Insulation Resistance (IR, DA, PI), DC HiPot (standard, Step, Ramp), Surge, and Partial Discharge tests. 1013-920 ADX-12-RLC-PD12 kV Standard ADX with RLC (low voltageResistance, Inductance, and Capacitance), DCInsulation Resistance (IR, DA, PI), DC HiPot(standard, Step, Ramp), Surge, and PartialDischarge tests.1013-922ADX-4-RLC-PD-PPI4 kV Standard ADX with RLC (low voltage Resistance, Inductance, and Capacitance), DC Insulation Resistance (IR, DA, PI), DC HiPot (standard, Step, Ramp), Surge, and Partial Discharge tests. Includes Power Pack Interface. 1013-925 ADX-12-RLC-PD-PPI12 kV Standard ADX with RLC (low voltageResistance, Inductance, and Capacitance), DCInsulation Resistance (IR, DA, PI), DC HiPot(standard, Step, Ramp), Surge, and PartialDischarge tests. Includes Power PackInterface.1013-927ADX-66 kV Standard ADX with DC Insulation Resistance (IR, DA, PI), DC HiPot (standard, Step, Ramp), and Surge tests only. 1013-912 ADX-1515 kV Standard ADX with DC InsulationResistance (IR, DA, PI), DC HiPot (standard,Step, Ramp), and Surge tests only.1013-914ADX-6-RLC6 kV Standard ADX with RLC (low voltage Resistance, Inductance, and Capacitance), DC Insulation Resistance (IR, DA, PI), DC HiPot (standard, Step, Ramp), and Surge tests. 1013-917 ADX-15-RLC15 kV Standard ADX with RLC (low voltageResistance, Inductance, and Capacitance), DCInsulation Resistance (IR, DA, PI), DC HiPot(standard, Step, Ramp), and Surge tests.1013-919ADX-6-RLC-PD6 kV Standard ADX with RLC (low voltage Resistance, Inductance, and Capacitance), DC Insulation Resistance (IR, DA, PI), DC HiPot (standard, Step, Ramp), Surge, and Partial Discharge tests. 1013-921 ADX-15-RLC-PD15 kV Standard ADX with RLC (low voltageResistance, Inductance, and Capacitance), DCInsulation Resistance (IR, DA, PI), DC HiPot(standard, Step, Ramp), Surge, and PartialDischarge tests.1013-923ADX-6-RLC-PD-PPI6 kV Standard ADX with RLC (low voltage Resistance, Inductance, and Capacitance), DC Insulation Resistance (IR, DA, PI), DC HiPot (standard, Step, Ramp), Surge, and Partial Discharge tests. Includes Power Pack Interface. 1013-926 ADX-15-RLC-PD-PPI15 kV Standard ADX with RLC (low voltageResistance, Inductance, and Capacitance), DCInsulation Resistance (IR, DA, PI), DC HiPot(standard, Step, Ramp), Surge, and PartialDischarge tests. Includes Power PackInterface.1013-928Item Description PartNumber Item Description PartNumberADX-15A15 kV Standard ADX with DC Insulation Resistance (IR, DA, PI), DC HiPot (standard, Step, Ramp), and Surge tests only. Includes Armature testing hardware and accessories. 1013-915 Megger Baker Test Station Indication Lights(TSIL)Remote accessory box that displays flashingred light when actively testing and greenlight when no testing is in progress.1014-108ADX-15A-RLC-PD6 kV Standard ADX with RLC (low voltage Resistance, Inductance, and Capacitance), DC Insulation Resistance (IR, DA, PI), DC HiPot (standard, Step, Ramp), Surge, and Partial Discharge tests. Includes Armature testing hardware and accessories. 1013-924 Megger Baker Test Status Indication LightEquipment Stop (TSIL-ES)Remote accessory box for ADX equipmentstop with a button press. Also displaysflashing red light when actively testing andgreen light when no testing is in progress1014-109FootswitchAllows operators to initiate a test using thefoot switch rather than the ADX front panelpush-to-test switch during coil testing.1014-110 Pelicase 1014-115ADX Armature Surge Accessory 1014-103 ADX Backpack 1014-114 ADX Armature Surge Probes 1014-104 ADX Test Lead - 15kV Red and labeling kit 1014-116 ADX Armature Surge Clips 1014-105 ADX Test Lead - 15kV Black 1014-117ADX Low Voltage Kelvin Test Leads with Clips 1011-928 2 x ADX Duplex 3-meter test leads withDuplex pistol type probes1014-029ADX Low Voltage Kelvin Test Leads with Probes 1011-929 2 x DLRO Duplex 3-meter test leads - 4mmplugs to Connect system socket1014-072ADX Standard Test Lead Set 1014-106 ADX Keyboard 1014-111 ADX Custom Test Lead Set 1014-107 ADX Front Cover 1014-112For complete Megger Baker Instruments EU declarations of conformity visit https:///company/about-us/legal/eu-dofcCONTACT INFORMATIONSales Office: Megger Baker Instruments 4812 McMurry Avenue, Fort Collins, CO 80525, USATelephone: +1 970-282-1200Email: **********************Web: /baker。

低噪声、低功耗高精度运放的SPICE模型建立