2013-2014数字电路试卷乙

2013-2014(1)数字电子技术教学日历—64学时(1-7 12-16)

2.5 2。6 2.7 2。8

2.9 2.10 2.11

2.13(必做)

3.3 3. 4 3. 5 3. 7

3.8 3.9 3.10(b)

3.11 3.12 3.13 3.16

4. 1 4。2..4. 3 4。4

4.5 4. 6 4.7(双)

4.8(b)4.10 4.11

5.1概述

5.2时序逻辑电路的分析

续5。2

5.3时序逻辑电路的设计

续5。3

续5。3

续5。3

第四、五章习题课

第六章脉冲波形的产生与整形

6.1概述

6.2集成555定时器

续6。2

6.3多谐振荡器

6.4脉冲整形电路

第七章半岛体存储器

7.1概述

7.2存储器

第八章可编程逻辑器件

8.1概述

8.2可编程阵列逻辑

8.3通用阵列逻辑器件

五

一

三

五

一

三

五

一

三

五

一

三

五

一

三

五

一

三

五

一

三

五

一

三

五

一

三

五

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2ห้องสมุดไป่ตู้

2

2

2

2

2

2

2

2

2

第一章数字电路基础

1.1概述

1.2数制和码制

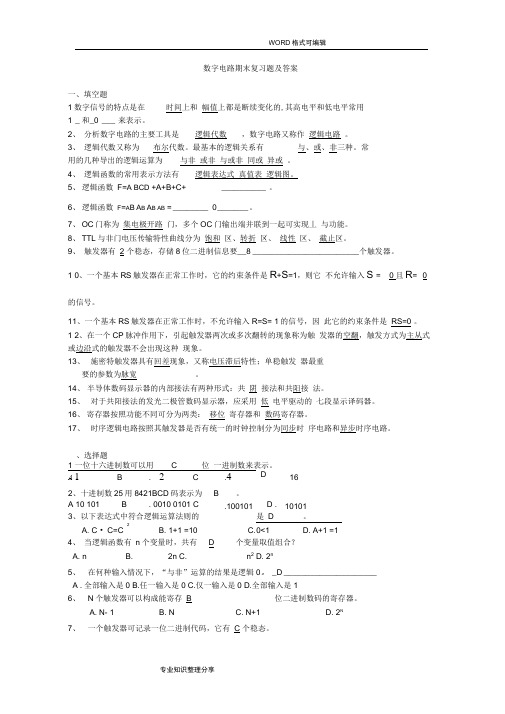

(完整版)数字电路期末复习试题和答案解析

数字电路期末复习题及答案一、填空题1数字信号的特点是在时间上和幅值上都是断续变化的,其高电平和低电平常用1 _ 和_0 ___ 来表示。

2、分析数字电路的主要工具是逻辑代数,数字电路又称作逻辑电路。

3、逻辑代数又称为布尔代数。

最基本的逻辑关系有与、或、非三种。

常用的几种导出的逻辑运算为与非或非与或非同或异或。

4、逻辑函数的常用表示方法有逻辑表达式真值表逻辑图。

5、逻辑函数F=A BCD +A+B+C+ __________ 。

6、逻辑函数F=A B A B A B AB = ________ 0 _______ 。

7、OC门称为集电极开路门,多个OC门输出端并联到一起可实现丄与功能。

8、TTL与非门电压传输特性曲线分为饱和区、转折区、线性区、截止区。

9、触发器有2 个稳态,存储8位二进制信息要__8 ________________________个触发器。

1 0、一个基本RS触发器在正常工作时,它的约束条件是R+S=1,则它不允许输入S = 0且R= 0的信号。

11、一个基本RS触发器在正常工作时,不允许输入R=S= 1的信号,因此它的约束条件是RS=0 。

1 2、在一个CP脉冲作用下,引起触发器两次或多次翻转的现象称为触发器的空翻,触发方式为主从式或边沿式的触发器不会出现这种现象。

13、施密特触发器具有回差现象,又称电压滞后特性;单稳触发器最重要的参数为脉宽。

14、半导体数码显示器的内部接法有两种形式:共阴接法和共阳接法。

15、对于共阳接法的发光二极管数码显示器,应采用低电平驱动的七段显示译码器。

16、寄存器按照功能不同可分为两类:移位寄存器和数码寄存器。

17、时序逻辑电路按照其触发器是否有统一的时钟控制分为同步时序电路和异步时序电路。

、选择题1 一位十六进制数可以用 C 位一进制数来表示。

A 1B . 2 C.4D162、十进制数25用8421BCD码表示为 B 。

A 10 101B . 0010 0101 C.100101 D .101013、以下表达式中符合逻辑运算法则的是D。

2013-2014年(13年1月份)南京跃捷联考电子电工试卷答案资料

考电子电工专业综合理论试卷本试卷分第Ⅰ卷(客观题)和第Ⅱ卷(主观题)两部分。

第Ⅰ卷第1页至第4页,第Ⅱ卷第5页至第12页。

两卷满分300分。

考试时间150分钟。

第Ⅰ卷(共120分)注意事项:1.答第Ⅰ卷前,考生务必按规定要求填涂答题卡上的姓名、考试证号等项目。

2.用2B铅笔把答题卡上相应题号中正确答案的标号涂黑。

答案不涂写在答题卡上无效。

一、单项选择题(本大题共22小题,每小题4分,共88分。

在下列每小题中,选出一个正确答案,将答题卡上相应题号中正确答案的字母标号涂黑)1.在如图所示的电路中电源电动势为E,内电阻为r。

闭合开关S,待电流达到稳定后,电流表示数为I,电压表示数为U,电容器C所带电荷量为Q,将滑动变阻器P的滑动触头从图示位置向a端移动一些,待电流达到稳定后,则与P移动前相比()A.U变小B.I变大C.Q增大D.Q减小2.两互感线圈如图(a)、(b)两种情况联接,若交流电压有效值U相同,若测I a=10A,I b=5A,则()A.a和c为同名端B.a和d为同名端C.b和c为异名端D.不确定同名端第1题图第2题图3.一电压U0=10 V的直流电通过电阻R,在时间t内产生的热量与一交流电流通过R/2时在同一时间内产生的热量相同,则该交流电的最大值为()A.10V B.5V C.52V D.102V 4.一组三角形联结的三相负载,总功率为3000W,当电源某一相线断路和负载的某一相断路时,这组负载所损耗的实际功率分别为()A.3000W3000W B.2000W 3000W C.1500W2000W D.2000W1500W5.如图所示电路,电压表V1的读数为10V,电压表V2的读数为18V,则电压表V的读数约为()A.28V B.35V C.25V D.20.6V6.在图示电路中,原电路处于稳态。

当t=0时开关S闭合,则电感L两端的u L(0+)的值为()A.0 V B.50 V C.100 V D.∞第5题图第6题图7.下列各图中____________不能振荡。

东南大学数逻实验考试2013-2014第二学期试题

数字逻辑电路实验试卷一(30日下午11系)一、设计电路:在同一时序同步实现Z1和Z2的输出波形。

要求:1.简单写出设计过程,画出原理图(30分)2.根据设计搭试电路(15分)3.静态验证Z1、Z2的输出并用双踪示波器或者逻辑分析仪观察Z1、Z2波形(25分)【需通过教师验收】4.根据双踪示波器或者逻辑分析仪观察结果,绘出输入时钟和Z1、Z2的波形(10分)【注:没有通过验收,绘出波形不得分】二、简答:1.设计的电路调试时发现触发器输出始终为1,应如何检查及排除?(10分)2.指出下面电路的输出。

(10分)(100分)答案:无一、教务处需要一考试监考装置:设定每场考试为2小时,假设一个时钟周期是10分钟,用两个数码管分别显示分钟的十位和小时的个位。

当到半小时的时候,红灯亮持续10分钟后灭,提醒监考老师没来的考生不得入场,在场的考生可以交卷离开。

当到1小时50分时,黄灯亮持续10分钟后灭,提醒监考老师考试时间将到,准备收卷。

要求:1.简单写出设计过程,画出逻辑电路图(30分)2.根据设计搭试电路(15分)3.用单脉冲验证电路并用双踪示波器或逻辑分析仪观察输入时钟和分钟的十位输出的Qm2、Qm1、Qm0输出波形【需通过教师验收】(25分)4.根据双踪示波器或者逻辑分析仪观察的结果,分别绘出输入时钟和分钟十位输出的Q m2、Q m1、Q m0输出波形。

(10分)【注:没有通过验收,绘出波形不得分】二、简答几个三态门的输出端是否允许短接?有无条件限制,应注意什么问题?OC门使用的注意点是什么?OC门的输出端是否允许短接,结果是什么?(20分)(100分)答案:无1、(问答题)一、设计一个简单的四路彩灯显示系统,演示花型为:L1——L4先向左次序点亮再向右次序点亮,即亮暗暗暗——暗亮暗暗——暗暗亮暗——暗暗暗亮——暗暗亮暗——暗亮暗暗——亮暗暗暗……要求:1、简单写出设计过程,画出逻辑电路图。

(30分)2、根据设计搭试电路。

数字电路试题五套(含答案)汇总

《数字电子技术》试卷一一、 填空(每空1分,共25分)1、(10110)2=( )10=( )16(28)10=( )2=( )16(56)10=( )8421BCD2、最基本的门电路是: 、 、 。

3、有N 个变量组成的最小项有 个。

4、基本RS 触发器的特征方程为_______ ,约束条件是 __.5、若存储器的容量是256×4RAM ,该RAM 有 ___存储单元,有 字,字长_____位,地址线 根。

6、用N 位移位寄存器构成的扭环形计数器的模是________.7、若令JK 触发器的J=K=T 则构成的触发器为_______.8、如图所示,Y= 。

9、如图所示逻辑电路的输出Y= 。

10、已知Y=D AC BC B A ++,则Y = ,Y/= 。

11、组合逻辑电路的特点是_________、___________;与组合逻辑电路相比,时序逻辑电路的输出不仅仅取决于此刻的_______;还与电路 有关。

二、化简(每小题5分,共20分)1、公式法化简++++(1)Y=ABC ABC BC BC A=+++(2)Y ABC A B C2、用卡诺图法化简下列逻辑函数=+++(1)Y BCD BC ACD ABDY=∑+∑(2)(1,3,4,9,11,12,14,15)(5,6,7,13)m d三、设下列各触发器初始状态为0,试画出在CP作用下触发器的输出波形(10分)四、用74LS161四位二进制计数器实现十进制计数器(15分)五、某汽车驾驶员培训班结业考试,有三名评判员,其中A 为主评判员,B 、C 为副评判员,评判时,按照少数服从多数原则,但若主评判员认为合格也可以通过。

试用74LS138和与非门实现此功能的逻辑电路。

(15分)P Q A Q B Q C Q D C T 74LS161 LD CPA B C D CrQ A 、Q B 、Q C 、Q D :数据输出端; A 、B 、C 、D :数据输入端; P 、T :计数选通端;r C :异步复位端;CP :时钟控制输入端;D L :同步并置数控制端;C :位输出端;六、试分析如图电路的逻辑功能,设各触发器的初始状态为0(15分)《数字电子技术》试卷一参考答案一、填空(每空1分,共25分)1、10(22)、16(16);2(11100)、16(1)C ;8421(01010110)BCD 。

计算机科学与技术专业《数字逻辑电路》考试题及答案(B)试卷

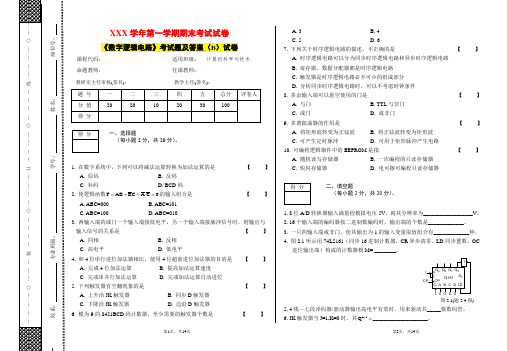

院系: 专业班级: 学号: 姓名: 座位号:XXX 学年第一学期期末考试试卷《数字逻辑电路》考试题及答案(B )试卷一、选择题(每小题2分,共20分)。

1. 在数字系统中,下列可以将减法运算转换为加法运算的是 【 】 A. 原码 B. 反码C. 补码D. BCD 码2. 使逻辑函数0C A C B AB F =++=的输入组合是 【 】 A. ABC=000 B. ABC=101C. ABC=100D. ABC=0103. 两输入端的或门一个输入端接低电平,另一个输入端接脉冲信号时,则输出与 输入信号的关系是 【 】 A. 同相B. 反相C. 高电平D. 低电平4. 和4位串行进位加法器相比,使用4位超前进位加法器的目的是 【 】 A. 完成4位加法运算B. 提高加法运算速度C. 完成串并行加法运算D. 完成加法运算自动进位 5. 下列触发器有空翻现象的是 【 】A. 上升沿JK 触发器B. 同步D 触发器C. 下降沿JK 触发器D. 边沿D 触发器6. 模为9的8421BCD 码计数器,至少需要的触发器个数是 【 】A. 3B. 4C. 5D. 67. 下列关于时序逻辑电路的描述,不正确的是 【 】 A. 时序逻辑电路可以分为同步时序逻辑电路和异步时序逻辑电路 B. 寄存器、数据分配器都是时序逻辑电路C. 触发器是时序逻辑电路必不可少的组成部分D. 分析同步时序逻辑电路时,可以不考虑时钟条件8. 多余输入端可以悬空使用的门是 【 】 A. 与门 B. TTL 与非门 C. 或门D. 或非门9. 多谐振荡器的作用是 【 】A. 将矩形波转变为正弦波B. 将正弦波转变为矩形波C. 可产生定时脉冲D. 可用于矩形脉冲产生电路 10. 可编程逻辑器件中的EEPROM 是指【 】A. 随机读写存储器B. 一次编程的只读存储器C. 快闪存储器D. 电可擦可编程只读存储器1. 8位A/D 转换器输入满量程模拟电压5V ,则其分辨率为__________________V 。

数字逻辑电路试题

院系: 专业班级: 学号: 姓名: 座位号:A. 4B. 3C. 6D. 57. 下列电路中属于时序逻辑电路的是【 】A. 加法器B. 数据分配器C. 计数器D. 译码器8. 下列关于门电路的使用,描述不正确的是 【 】A. TTL 与非门闲置输入端可以直接接电源B. 具有推拉输出结构的TTL 门电路的输出端可以直接并联使用C. CMOS 或门闲置输入端应接地D. CMOS 门电路的闲置输入端不允许悬空9. 为了降低555定时器组成多谐振荡器的振荡频率,外接R 、C 值应为 【 】A. 同时增大R 、C 值B. 同时减小R 、C 值C. 同比增大R 值减小C 值D. 同比增大C 值减小R 值 10. 若停电数分钟后恢复供电,下列选项中信息能够保持不变的是 【 】A. ROMB. 动态RAMC. MUXD. 静态RAM1. 8位D/A 转换器的理论分辨率是_____________________。

2. 64个输入端的编码器按二进制数编码时,输出端的个数是__________________。

3. 变量数相同时,下标编号相同的最大项i M 和最小项i m 的关系是_____________。

4. 图2.1所示集成计数器的模M=_____________________。

图2.1 (题2.4图)5. 共阳极接法数码显示器需要配用输出 电平有效的译码器。

二、填空题(每小题2分,共20分)6. 对于T 触发器,当T=______时,触发器处于保持状态。

7. 逻辑函数C B AB F +=的反函数F 为_____________________。

8. 5个变量的逻辑函数全部最大项有_____________________个。

9. 二进制数()20110.101110转换成十进制数是___________________。

10. 同步RS 触发器的特性方程中,约束条件为RS=0,说明这两个输入信号不能同时为_____________________。

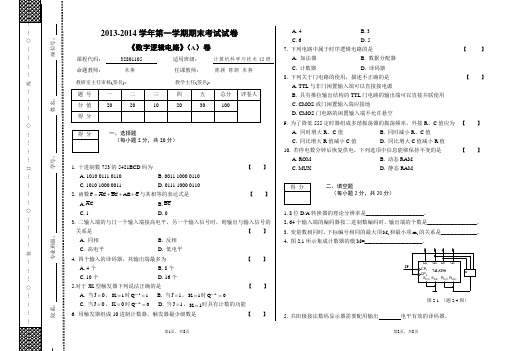

2013-2014(1)《数字电子技术》试题 - 副本

华 北 科 技 学 院2013/2014学年第 一 学期考试试卷一、填空题(每空1分,共20分) 1.()()()1610201.10110==2. 由于n 位二进制译码器的输出给出了n 变量的全部 ,因而用n 变量二进制译码器、或门或者与非门就能获得任何形式输入变量数为 的组合逻辑函数。

3. 集电极开路门的特点是:允许多个OC 门的输出端 ,实现“线与”的功能,但使用时必须外接 和 。

4.消除竞争-冒险现象的方法有 、 和引入选通脉冲等方法。

5.JK 触发器的功能包括 、 、 和 。

6.在时序逻辑电路中,根据输出信号的特点,时序逻辑电路可分为 和 两种。

7.施密特触发器的应用主要用于 、 和 等。

8.根据所采用的存储单元工作原理的不同,随机存储器可分为 和 。

二、选择题(每题2分,共20分)1.下列说法正确的是( )。

(A)双极型数字集成门电路是以场效应管为基本器件构成的集成电路(B)TTL 逻辑门电路是以晶体管为基本器件构成的集成电路(C)CMOS 集成门电路集成度高,但功耗较高 (D)TTL 逻辑门电路和CMOS 集成门电路不能混合使用2. 由开关组成的逻辑电路如图1所示,设开关A 、B 接通为“1”,断开为“0”,电图 1学院(部) 专业、班级 姓名 学号密封 装订 线灯亮为“1”,电灯暗为“0”,则该电路为()。

(A)“与”门(B)“或”门(C)“非”门(D)“与非”门3. 设图2触发器的初始状态为0,已知时钟脉冲CP波形如图所示,则Q端的波形为()。

(A) ①(B) ②(C) ③(D) ④4. 下列说法不正确的是( )。

(A)计数器是对时钟脉冲信号CP进图2行累积计数(B)计数器包括定时器、分频器、序列信号发生器和寄存器等常用电路(C)定时器是计满了一定数目的CP脉冲个数以后,电路输出一个信号,这个输出信号的周期等于定时时间(D)分频器是将频率高的信号作为时钟脉冲CP信号,计满N个CP脉冲信号后,产生一个输出信号Z5. 将一个最大幅值为5V的模拟信号转换为数字信号,要使模拟信号每变化10mV,数字信号的最低位发生变化,应选用( )位的A/D转换器。

2013-2014学年度第一学期高三六校联考计算机专业综合理论试卷

绝密★启用前2013-2014学年度第一学期六校期中联考调研测试计算机专业综合理论试卷本试卷分第Ⅰ卷(客观题)和第Ⅱ卷(主观题)两部分。

第Ⅰ卷1页至5页,第Ⅱ卷6页至20页。

两卷满分300分。

考试时间150分钟。

第I卷(共90分)注意事项:1.答第Ⅰ卷前,考生务必按规定要求填涂答题卡上的姓名、准考证号等项目。

2.用2B铅笔把答题卡上相应题号中正确答案的标号涂黑。

答案不涂写在答题卡上无效。

一、单项选择题(本大题共30小题,每小题2分,共60分。

在下列每小题中,选出一个正确答案,将答题卡上相应题号中正确答案的字母标号涂黑)1.按应用领域分类,火箭发射属于( )。

A.科学计算B.数据处理C.人工智能D.计算机辅助设计2.某R进制数(627)R=407,则R=________。

A.8 B.9 C.12 D.163.冯•诺依曼结构的计算机其工作原理一般都基于( )原理。

A.存储程序与程序控制B.二进制C.开关电路D.布尔代数4.CPU每进行一次操作,都要有时间开销。

下列几种周期按由降序排列的是( )。

A.时钟周期、CPU周期、指令周期B.CPU周期、指令周期、时钟周期C.指令周期、CPU周期、时钟周期D.CPU周期、时钟周期、指令周期5.加法运算后的进位位存放在( )A.状态标志寄存器中B.程序计数器PC中C.数据缓冲器DR中D.累加器ACC中6.操作数地址在指令中直接给出,这种寻址方式为( )。

A.直接寻址B.间接寻址C.立即寻址D.变址寻址7.若用2K*4位的芯片构成64KB的存储器,需用()。

A.8片B.16片C.32片D.64片8.PentiumⅢCPU 主频800MHZ,倍频系数为8,外频为( )MHZ。

A.800 B.100 C.8 D.1339.DDRIII内存接口通常为()脚A.180B.128C.240D.7210.下列ROM中主要用于存储主板、显卡BIOS并支持在线升级的是( )。

A.PROM B.EPROM C.ROM D.EEPROM11.某一款Intel CPU型号如下:Intel Core 2 Extreme QX9650(LGA775/3.00GHz/6MB L2×2),该参数中没有列出的项目是________。

2013-2014(1)计算机应用基础期末理论复习题

2013-2014(1)计算机应用基础期末理论复习题一、单选题1、MMX是指带有___________的CPU芯片。

CA、自动录音B、大量寄存器C、多媒体功能D、数据压缩2、现代信息技术建立在通讯技术、计算机技术和____________上。

CA、设备技术B、信息技术C、微电子技术D、电路制造技术3、串行接口RS232和USB相比较,在速度上是________。

BA、RS232快B、USB快C、根据情况不确定的D、相同的4、以下__________属于系统软件。

CA、AuthorwareB、CAI软件C、VC++D、FrontPage5、乐器数字接口的英文缩写是________。

CA、RS232CB、USBC、MIDID、FM6、目前按 USB2.0标准,USB的传输速率可以达到_______Mbps。

DA、56B、240C、256D、4807、人类生存和社会发展的基本资源是________。

BA、物质、金钱、石油、股票B、物质、能源、信息C、粮食、煤炭、电力、因特网D、物质、能源、因特网8、____________不被认为是操作系统中可用来支持多媒体的功能。

CA、具有多任务的特点B、采用虚拟内存管理技术C、支持多媒体信息检索功能D、具有管理大容量存储器的功能9、在PowerPoint 2010中,可利用__________来组织大型幻灯片,以简化其管理和导航。

BA、A.动画刷B、节C、占位符D、视图10、常用的IP地址包括ABC三大类,其中,A类地址的第一段取值介于:_______。

DA、1-172B、1-168C、128-191D、1-12611、在html中,“提交按钮”的type属性值为______________。

BA、formB、submitC、resetD、tijiao12、完整的微型计算机硬件系统一般包括外部设备和_________。

AA、主机B、中央处理器C、存贮器D、运算器和控制器13、现代信息技术的主体是__________等。

大学《数字电路与逻辑设计》期末试卷含答案

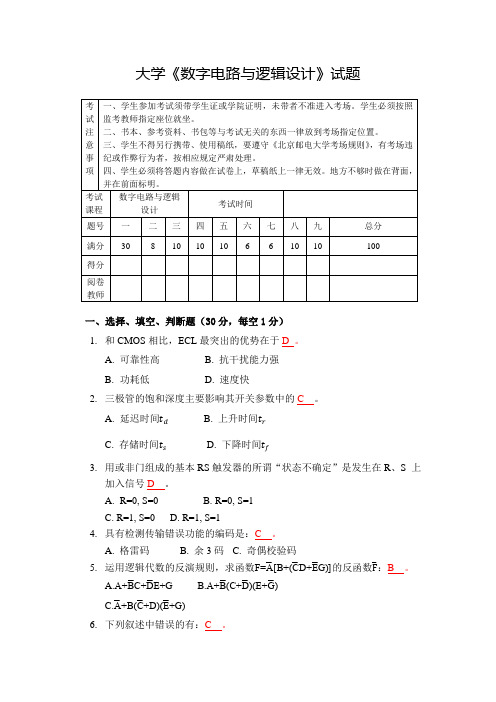

大学《数字电路与逻辑设计》试题一、选择、填空、判断题(30分,每空1分)1.和CMOS相比,ECL最突出的优势在于D 。

A.可靠性高B. 抗干扰能力强B.功耗低 D. 速度快2.三极管的饱和深度主要影响其开关参数中的C 。

A.延迟时间t dB. 上升时间t rC. 存储时间t sD. 下降时间t f3.用或非门组成的基本RS触发器的所谓“状态不确定”是发生在R、S 上加入信号D 。

A.R=0, S=0B. R=0, S=1C. R=1, S=0D. R=1, S=14.具有检测传输错误功能的编码是:C 。

A. 格雷码B. 余3码C. 奇偶校验码5.运用逻辑代数的反演规则,求函数F=A̅[B+(C̅D+E̅G)]的反函数F̅:B 。

A.A+B̅C+D̅E+GB.A+B̅(C+D̅)(E+G̅)C.A̅+B(C̅+D)(E̅+G)6.下列叙述中错误的有:C 。

A. 逻辑函数的标准积之和式具有唯一性。

B. 逻辑函数的最简形式可能不唯一。

C. 任意两不同的最小项之和恒等于1。

7. 函数F=(A+B+C̅)(A ̅+D)(C+D)(B+D+E)的最简或与式为:A 。

A.F=(A+B+C ̅)(A ̅+D)(C+D)B.F=(A+B+C ̅)(A ̅+D)C.F=ABC̅+A ̅D+CD 8. 逻辑函数F (A,B,C,D )=∑(1,3,4,5,6,8,9,12,14),判断当输入变量ABCD 分别从(1) 0110→1100,(2) 1111→1010时是否存在功能冒险:B 。

A. 存在,存在 B. 不存在,存在C.不存在,不存在9. 对于K =3的M 序列发生器,反馈函数为Q 2⊕Q 0,则产生M 序列:C 。

A. 1010100 B. 1110101 C. 111010010. 在进行异步时序电路的分析时,由于各个触发器的时钟信号不同,因此我们应该把时钟信号引入触发器的特征方程,对于D 触发器,正确的是:A 。

数字电路 期中答案及给分点

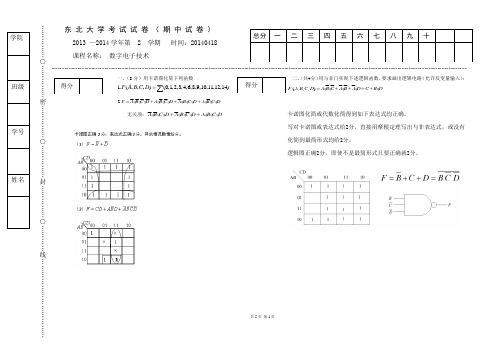

东北大学考试试卷(期中试卷)2013 —2014学年第 2 学期时间:20140418课程名称:数字电子技术二、(共4分)用与非门实现下述逻辑函数,要求画出逻辑电路(允许反变量输入):(,,,)F A B C D A B C A B A D C B D=++++卡诺图化简或代数化简得到如下表达式均正确。

写对卡诺图或表达式给2分,直接用摩根定理写出与非表达式,或没有化简到最简形式均给2分,逻辑图正确2分,即使不是最简形式只要正确就2分。

一、(8分)用卡诺图化简下列函数1.(,,,)(0,1,2,3,4,6,8,9,10,11,12,14)F A B C D=∑2.F A B C D A B C D A B C D A B C D=+++无关项:A B C D A B C D A B C D++共5页第1页图1 四、(2分)图2 所示逻辑门为CMOS 电路,写出电路输出F 的逻辑表达式。

图2三、(2分)写出图1电路中的输出F 和输入A 、B 之间的逻辑关系式。

共5页 第2页五、(3分)画出图3中共阴极LED 数字显示器与译码器的接线图。

图3七、(4分)用74138和与非门实现下列逻辑函数。

Y= ∑m(0,2,6,7)要求列出真值表和画出实现的逻辑图。

六、(5分)用加法器74LS283设计一个代码转换电路,将8421码转换为余3码。

要求写出设计步骤,并画出设计实现的逻辑图。

74LS283的引脚图见图4。

图4. 74LS283的引脚图……………○……………密……………○……………封……………○…………线………………………………共5页第3页. 表1 数据选择器74151的功能表共5页 第4页图5……………○……………密……………○……………封……………○…………线………………………………八、(6分)请用数据选择器74151和非门设计一个三人表决电路。

在表决一般问题时以多数同意为通过;在表决重要问题时,必须一致同意才能通过。

数字电子技术试卷3套含答案(大学期末复习资料).docx

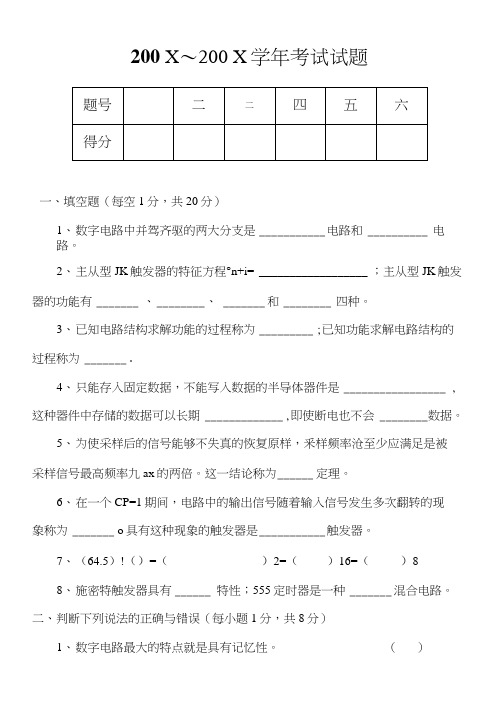

200 X〜200 X学年考试试题一、填空题(每空1分,共20分)1、数字电路中并驾齐驱的两大分支是___________ 电路和 __________ 电路。

2、主从型JK触发器的特征方程°n+i= __________________ ;主从型JK触发器的功能有_______ 、________ 、 _______ 和________ 四种。

3、已知电路结构求解功能的过程称为_________ ;已知功能求解电路结构的过程称为_______ o4、只能存入固定数据,不能写入数据的半导体器件是_________________ , 这种器件中存储的数据可以长期 _____________ ,即使断电也不会 ________ 数据。

5、为使采样后的信号能够不失真的恢复原样,釆样频率沧至少应满足是被采样信号最高频率九ax的两倍。

这一结论称为______ 定理。

6、在一个CP=1期间,电路中的输出信号随着输入信号发生多次翻转的现象称为_______ o具有这种现象的触发器是___________ 触发器。

7、(64.5)!()=()2=()16=()88、施密特触发器具有______ 特性;555定时器是一种_______ 混合电路。

二、判断下列说法的正确与错误(每小题1分,共8分)1、数字电路最大的特点就是具有记忆性。

()2、竞争冒险中凡电压毛刺为高电平时,均称为1冒险。

()3、数值译码器的输入量是十进制,输出量是二进制。

()4、仅具有翻转功能的触发器是T触发器。

()5、74LS90和74LS163都是具有自启动能力的集成计数器。

()6、集成电路74LS138是一个4线-10线的译码器。

()7、多谐振荡器输入三角波,输出可转换成方波。

()8、模5计数器至少需用两位触发器构成。

()三、选择题(每小题2分,共20分)1、由与非门组成的基本RS触发器不允许输入的变量组合g•斥是()A、00B、01C、10D、112、仅具有保持和翻转功能的触发器是()A、JK触发器B、D触发器C、T触发器D、同步触发器3、八输入端的编码器按二进制编码时,其输出端的个数是()A、2个B、3个C、4个D、6个4、用8421 BCD码作为代码的计数器,至少需要的触发器个数是()A、2个B、3个C、4个D、5个5、按触发方式的不同,双稳态触发器可分为()A、高电平触发和低电平触发B、电平触发或边沿触发C、上升沿触发和下降沿触发D、输入触发和时钟触发6、四位移位寄存器构成扭环形计数器时,可构成()计数器。

2014《数字逻辑设计》期末考试-试题及参考解答

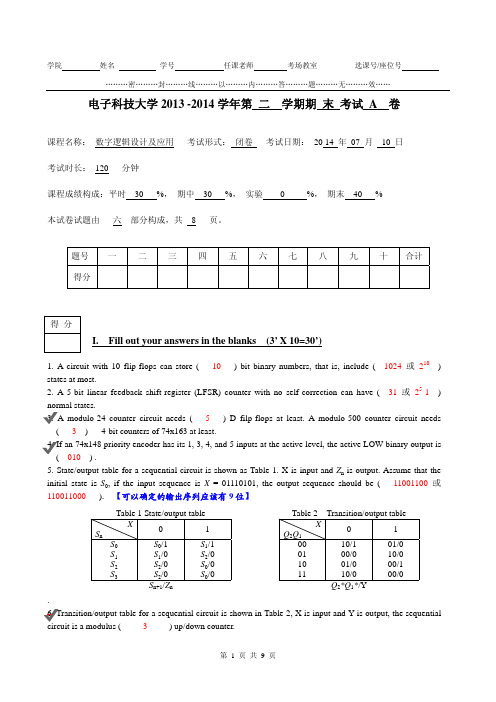

………密………封………线………以………内………答………题………无………效……电子科技大学2013 -2014学年第 二 学期期 末 考试 A 卷课程名称:_数字逻辑设计及应用__ 考试形式: 闭卷 考试日期: 20 14 年 07 月 10 日 考试时长:_120___分钟课程成绩构成:平时 30 %, 期中 30 %, 实验 0 %, 期末 40 % 本试卷试题由___六__部分构成,共__8___页。

题号 一 二 三 四 五 六 七 八 九 十 合计得分I. Fill out your answers in the blanks(3’ X 10=30’)1. A circuit with 10 flip-flops can store ( 10 ) bit binary numbers, that is, include ( 1024 或 210 ) states at most.2. A 5-bit linear feedback shift-register (LFSR) counter with no self-correction can have ( 31 或 25-1 ) normal states.3. A modulo-24 counter circuit needs ( 5 ) D filp-flops at least. A modulo-500 counter circuit needs ( 3 ) 4-bit counters of 74x163 at least.4. If an 74x148 priority encoder has its 1, 3, 4, and 5 inputs at the active level, the active LOW binary output is ( 010 ) .5. State/output table for a sequential circuit is shown as Table 1. X is input and Z n is output. Assume that the initial state is S 0, if the input sequence is X = 01110101, the output sequence should be ( 11001100 或110011000 ). 【可以确定的输出序列应该有9位】.3 ) up/down counter.n+1n 21………密………封………线………以………内………答………题………无………效……7. A serial sequence generator by feedback shift registers 74x194 is shown in Figure 1, assume the initial state is Q2Q1Q0 = 100, the feedback function LIN = Q2’Q1’ + Q2Q0’, the output sequence in Q2 is ( 100110循环输出 ).Figure 18. When the input is 01100000 of an 8 bit DAC, the corresponding output voltage is 3.76V. The output voltage range for the DAC is ( 0 ~ 9.99 或568221276.3+−×或9625576.3× )V. 【本题并未对误差范围进行要求,一般可保留2位小数。

2013 数字电路设计试卷答案

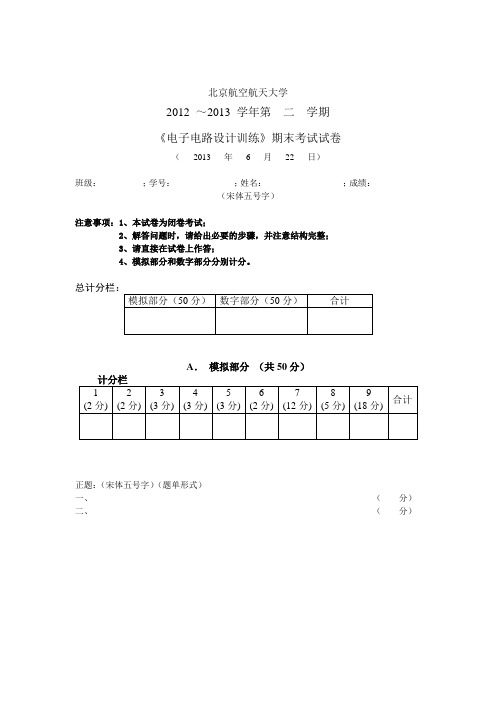

北京航空航天大学2012 ~2013 学年第二学期《电子电路设计训练》期末考试试卷(2013 年 6 月22 日)班级:__________;学号:______________;姓名:__________________;成绩:___________(宋体五号字)注意事项:1、本试卷为闭卷考试;2、解答问题时,请给出必要的步骤,并注意结构完整;3、请直接在试卷上作答;4、模拟部分和数字部分分别计分。

A.模拟部分(共50分)正题:(宋体五号字)(题单形式)一、(分)二、(分)B.数字部分(共50分)一、选择题(共5分,每空1分)1.综合是EDA设计流程的关键步骤,在下面对综合的描述中,____D____是错误的。

A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与FPGA/CPLD的基本结构相映射的网表文件;C.综合就是将行为描述逻辑转换成门级结构表示的一个映射过程;D.综合可理解为,用电路网表文件表示软件描述与给定硬件结构的映射过程,并且这种映射关系是唯一的。

2.不完整的IF语句,其综合结果可实现____A____。

A.时序逻辑电路B.组合逻辑电路C.双向电路D.三态控制电路3.P、Q、R都是同样大小的存储器类型变量,下面___C____表达式是正确的。

A.reg[n-1:0] P[m:1], Q, RB.reg[n-1:0] [m:1] P, Q, RC.reg[n-1:0] P[m:1], Q[m:1], R[m:1]D.reg[n-1:0] [m:1]P, [m:1]Q, [m:1]R4.下列程序中,always状态将描述一个带异步Nreset和Nset输入端的上升沿触发器,则下面___D____表述是正确的。

always@( )if(!Nreset)Q<=0;else if(Nset)Q<=1;elseQ<=D;A.posedge Nreset or posedge Clock or negedge NsetB.negedge Nreset or posedge Clock or negedge NsetC.negedge Nreset or negedge Clock or posedge NsetD.negedge Nreset or posedge Clock or posedge Nset5.下列表达式中正确的是____C____。

2014期末考试数电复习资料(含答案)

1. 以下表达式中符合逻辑运算法则的是 。

A.C·C=C2 B.1+1=10 C.0<1 D.A+1=1

2. 逻辑变量的取值和可以表示 。

A.开关的闭合、断开 B.电位的高、低 C.真与假 D.电流的有、无

4十进制数25用8421BCD码表示为 。

A.10 101 B.0010 0101 C.100101 D.10101

5在一个8位的存储单元中能够存储的最大无符号整数是 。

A.25610 B.12710 C.FF16 D.25510

4因为逻辑表达式A+B+AB=A+B成立所以AB=0成立。

5若两个函数具有不同的真值表则两个逻辑函数必然不相等。

6若两个函数具有不同的逻辑函数式则两个逻辑函数必然不相等。

7逻辑函数两次求反则还原逻辑函数的对偶式再作对偶变换也还原为它本身。

8与八进制数(47.3)8等值的数为 A. (100111.011)2 B.(27.6)16 C.(27.3 )16 D. (100111.11)2 9. 常用的BCD码有

。

A.奇偶校验码 B.格雷码 C.8421码 D.余三码 10与模拟电路相比数字电路主要的优点有

3. 逻辑代数中与普通代数相似的定律有 、 、 。摩根定律又称为 。

4. 逻辑代数的三个重要规则是 、 、 。

5逻辑函数F=

A+B+CD的反函数F= 。

10当8421奇校验码在传送十进制数810时在校验位上出现了1时表明在传送过

程中出现了错误。

三、填空题

1. 描述脉冲波形的主要参数有 、 、 、 、 、 、 。

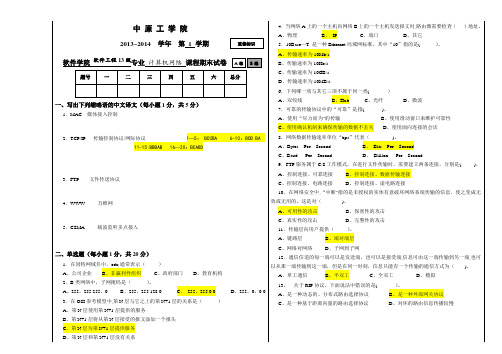

计算机网络题

本试卷共 4 页,此页为 B 卷第 1 页 (注:参加重修考试者请在重修标识框内打钩)

班级 姓名 学号 ………………………………………装……………………………订……………………………线………………………………………

本试卷共 4 页,此页为 B 卷第 2 页

班级 姓名 学号 ………………………………………装……………………………订……………………………线………………………………………

3.为什么要划分子网?子网掩码的作用是什么?3.答:划分子网是为了将一个大的网络分成几个小的网络,提高IP地址的利用率。

(2分)子网掩码是用来判断IP地址的哪一部分是网络号和子网号,哪一部分是主机号。

为完成各部分编号分离,需将IP地址和子网掩码进行“与"运算。

(2分)

4.简述CSMA/CD协议的工作原理?答:CSMA/CD即载波监听多路访问/冲突检测。

(1分)工作原理:某站点发送数据前,先监听信道是否空闲,若空闲,则立即发送数据。

若信道忙,继续监听信道,直到信道空闲。

在发送数据时,边发送边继续监听.若监听到冲突,则立即停止发送数据,等待一段随机时间,再重新尝试.

5.简述DNS服务器的作用,并写出至少三个顶级域名?DNS(域名系统)服务器的主要功能是进行域名解析,保存所负责域的域名层次结构信息.(2分)com、org、gov、edu、net、mil、int、cn、us、uk …(2分)

班级 姓名 学号 ………………………………………装……………………………订……………………………线………………………………………

班级 姓名 学号 ………………………………………装……………………………订……………………………线………………………………………。

[7] 2013-2014第2学期数电试卷B

![[7] 2013-2014第2学期数电试卷B](https://img.taocdn.com/s3/m/20b2198004a1b0717fd5ddd8.png)

安徽大学20 13 —20 14 学年第 二 学期 《 数字电子技术 》考试试卷(B 卷)(闭卷 时间120分钟)院/系 年级 专业 姓名 学号一、选择题(每题2分,共20分)1. 十进制数7.88对应的16进制数为()。

A. (7.E1)16B. (7.D1) 16C. (7.F1) 16D. (7.E2) 162. 逻辑函数1F A =⊕=()。

A. 0B. AC. 1D.A3. 用或非门构成基本RS 触发器发生竞争现象时,输入端的变化是( )。

A. 00→11B. 01→10C. 11→00D. 10→014. 以下式子中不正确的是( )。

A. 1A A ⋅=B. A A A ⊕=C. A B A B +=+D. 11A +=5. 已知同Y AB B AB =++,下列结果中正确的是( )。

A. YA =B.Y B =C. Y A B =+D. YA B=+6. 下列具有单次翻转特性的触发器是()。

A. 同步JK 触发器B. 主从JK 触发器C. 上升沿JK 触发器D.下降沿JK 触发器7. 下列论述错误的是()。

A. 数字比较器可以比较数字大小B. 实现两个一位二进制数相加的电路叫全加器C. 实现两个一位二进制数和来自低位的进位相加的电路叫全加器D. 编码器可分为普通全加器和优先编码器 8. 下列描述不正确的是()。

A. 触发器具有两种状态,当Q = 1时触发器处于1态B. 时序电路必然存在状态循环C. 异步时序电路的响应速度要比同步时序电路的响应速度慢D. 边沿触发器具有上升沿触发和下降沿触发两种方式,能有效克服同步触发器的空翻现象9. 要使JK 触发器在时钟脉冲作用下,实现输出1n n Q Q +=,则输入端信号应接为( )。

A . J = K = 0B . J = K = 1C .J = 1, K = 0D . J = 0, K = 110.设计一个同步10进制计数器,需要( )个触发器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

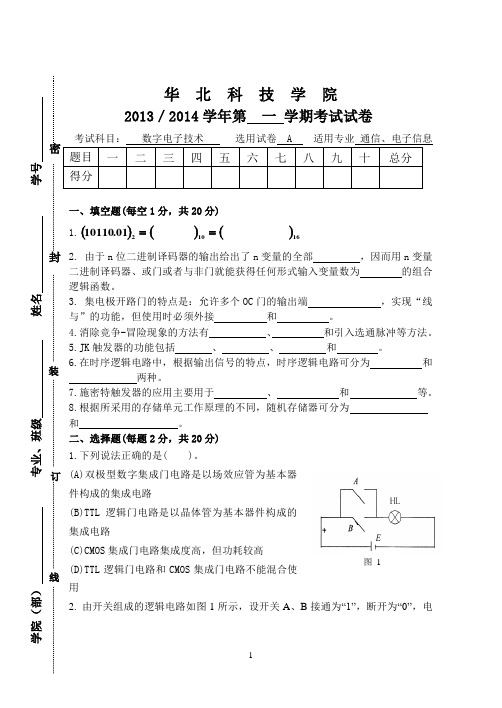

安顺学院2013—2014学年度第二学期期末考试试卷 《数字电子技术》试卷(乙卷)第1页(共6页)

2013-2014学年度 第二学期期末考试

数字电子技术基础 试卷

一、填空题(本大题共 8 小题17个空,每空2 分,共34分)

1. (10011.1)2=( )8=( )10

2.基本逻辑运算有_______、 、 3种。

3.描述逻辑函数各个变量取值组合和函数值对应关系的表格叫 。

4.若编码器要对有51个对象进行编码,则要求输出二进制代码位数为____________位。

5.基本RS 锁存器的特征方程为 ,约束条件是 。

6.若存储器的容量是256×4 RAM,该RAM 有 存储单元,有 字,字长 位,地址线 根。

7.在施密特电路,单稳态电路和多谐振荡器三种电路中,没有稳态的电路是 ,有一个稳态的电路是 ,有二个稳态的电路是 。

8.在PROM 、EPROM 、E 2

PROM 及Flash Memory 四种存储器中,可用光改写的是 。

二、选择题(本大题共 8 小题,每小题 2 分,共16 分)

题号 一 二 三 四 总分 得分

得分

得分

考生座位号

电子与信息工程

学院 2012 级 电子信息工程 专业 姓名 学号

―――――⊙――――――装――――――⊙―――――订―――――⊙――――――线――――――⊙―――――

考 生 答 题 不 得 超 过 此 线

试卷代码

0 8 0 7 0 1 0 1 3

安顺学院2013—2014学年度第二学期期末考试试卷

《数字电子技术》试卷(乙卷)第2页(共6页)

1. 十进制数25用8421BCD 码表示为( )。

A.10101 B.0010 0101 C.100101 D.11001

2.函数F=ABC+AB C +A B 的最简与或式是( )。

A.F=A+B B.F=A +C C.F=B+C D.F=B

3.若将一个同或门(输入端为A,B )当作反相器使用,则A 、B 端应( )。

A. A 或B 中有一个接1;

B. A 和B 并联使用;

C. A 或B 中有一个接0;

D. 同或门无法转换为反相器

4. 符合下面真值表的门电路是( )。

A B Y 0 0 0 0 1 1 1 0 1 1

1

0 A .与门 B .或门 C .同或门 D .异或门

5.下列代码属于8421BCD 码的是( )。

A .1010 B .1100 C .0111 D .1101

6.函数F=AB+BC ,使F=1的输入ABC 组合为( )。

A .ABC=000 B .ABC=010 C .ABC=101 D .ABC=110 7.要使JK 触发器在时钟脉冲作用下,实现输出n n Q Q =+1,则输入端信号应为

( )。

A .J =K =0

B .J =K =1

C .J =1,K =0

D .J =0,K =1

8.设计一个同步10进制计数器,需要( )触发器。

A .3个 B .4个 C .5个 D .10个

安顺学院2013—2014学年度第二学期期末考试试卷 《数字电子技术》试卷(乙卷)第3页(共6页)

三、化简函数(本大题共 3 小题,每小题 5 分,共15 分)

1. 用代数法化简函数:Y=()ABC B C +

2. 用代数法化简函数:C AB C B BC A AC C B A Y +++=),,(

3. 用卡诺图化简逻辑函数:

∑=)15,14,13,12,11,10,6,5,4,2(),,,(m D C B A Y

得分

―――――⊙――――――装――――――⊙―――――订―――――⊙――――――线――――――⊙―――――

考 生 答 题 不 得 超 过 此 线

安顺学院2013—2014学年度第二学期期末考试试卷 《数字电子技术》试卷(乙卷)第4页(共6页)

四、分析、设计题(本大题共3小题,共35分)

1.组合电路如图所示,分析该电路的逻辑功能。

(本题10分)

2.试设计一个4位的奇偶校验器,即当4位数中有奇数个1时输出为0,否则输出为1。

(本题15分)

&

&&&

¡

Ý1A B C

L

P

安顺学院2013—2014学年度第二学期期末考试试卷

《数字电子技术》试卷(乙卷)第5页(共6页)

3.分析图示的时序电路,写出驱动方程、输出方程、状态方程,画出电路的状态图。

(本题10分)

―――――⊙――――――装――――――⊙―――――订―――――⊙――――――线――――――⊙―――――

考 生 答 题 不 得 超 过 此 线

安顺学院2013—2014学年度第二学期期末考试试卷《数字电子技术》试卷(乙卷)第6页(共6页)。