锁相环频率合成器的研究与设计

数字锁相环的频率合成器设计

数字锁相环的频率合成器设计摘要:近几年来,无线通讯获得飞速发展。

随着其应用领域的不断扩张,市场对低功耗、低造价、高性能、高集成度的收发机的需要也越来越高。

在无线通信收发机中包含一个很重要的模块,频率合成器,它通过产生一系列与参考信号具有同样精度和稳定度的离散信号,为频率转换提供基准的本地震荡信号。

频率合成器设计的优劣直接影响到无线通信收发机的性能、成本,故其实现方式一直是一个挑战。

而本次课程设计仅考虑方案的实用性,即是实验室环境的局限性以及电子器件的价格等因素。

关键词:数字锁相环,分频,频率合成器一、选题的背景与意义随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副载波同步、图象处理等各个方面得到了广泛的应用。

数字锁相环不仅吸收了数字电路可靠性高、体积小、价格低等优点,还具有对离散样值的实时处理能力,已成为锁相技术发展的方向。

锁相环是一个相位反馈控制系统,在数字锁相环中,由于误差控制信号是离散的数字信号,而不是模拟电压,因而受控的输出电压的改变是离散的而不是连续的。

本文主要介绍了仿真技术的概念、特点、发展情况及其在控制系统的应用;分析了MATLAB/SIMULINK的功能及如何在MATLAB语言提供的仿真环境SIMULINK 下实行控制系统的仿真,并对数字锁相环进行仿真。

利用计算机对控制系统进行仿真与分析,是研究控制系统的重要手段;MATLAB软件、MCGS组态软件可成功地用于控制系统的仿真、分析及监控,在科研、生产和教学等领域具有广泛的应用前景和推广价值,从上面两方面看来,本课题数字锁相环技术的matlab/simulink仿真具有一定的研究价值。

二、研究内容与拟解决的主要问题本设计从模拟锁相环研究出发,掌握锁相环的基本工作原理,了解环路失锁、捕获、跟踪过程及环路锁定条件等。

掌握数字锁相环的工作原理,并用MATLAB语言对该系统进行设计,给出数字锁相环电路各个主要模块的设计过程及仿真结果,得到该系统的顶层电路。

答辩-锁相环频率合成器的的设计与制作

将设计好的PCB板交给工厂进行制板。

焊接与组装

将元器件按照PCB板上的焊盘逐一焊 接,完成整个电路板的组装。

元器件选择与采购

元器件选择

根据电路参数和性能要求,选择合适 的电阻、电容、电感等元器件,确保 电路性能稳定可靠。

元器件采购

通过电子市场或网上商城等渠道,购 买所需的元器件,确保质量可靠、价 格合理。P源自B板设计与制作PCB板设计

使用EDA工具进行PCB板的设计,包括层数、线宽、间距等参数的设置,以及元件的布局和布线。

PCB板制作

将设计好的PCB板交给工厂进行制板,确保PCB板的品质和精度符合要求。

焊接与组装

焊接

使用电烙铁或热风枪等工具,将元器件按照PCB板上的焊盘逐一焊接,确保焊点质量良好、无虚焊、无短路。

性能评估与优化建议

性能评估

根据测试结果,该锁相环频率合成器在 输出频率、相位噪声和杂散抑制等方面 均表现出较好的性能,符合设计要求。

VS

优化建议

针对测试过程中发现的问题,建议进一步 优化电路设计,提高杂散抑制性能;同时 加强生产工艺控制,确保产品的一致性和 可靠性。

05

总结与展望

设计制作过程中的收获与不足

03

锁相环频率合成器的制作

制作流程

确定设计目标

明确频率范围、输出功率、相位噪声 等性能指标。

原理图设计

根据设计目标,使用EDA工具进行原 理图设计,包括PLL电路、VCO电路、 分频器等。

电路板布局

根据原理图,进行PCB板的布局设计, 确保信号路径短、干扰小。

元器件选型与采购

根据电路参数和性能要求,选择合适 的电阻、电容、电感等元器件,并完 成采购。

锁相环频率合成器的设计

锁相环频率合成器的设计1方案设计在本系统中需要用到高性能的频率源作为混频信号的本振。

频率合成器的方案主要有三种:直接式、间接式和直接数字频率式。

直接式频率合成尽管有频率转换快的优点,但是其体积大的弱点无法适应现代系统要求。

直接数字式由于其工作频率较低且成本昂贵也不宜采用。

间接式频率合成技术是运用锁相和数字分频器相结合的技术对信号频率进行四则运算,谐波分量是利用锁相环的窄带滤波特性加以滤除的,由于它不采用传统的谐波发生器、倍频器等器件,从而使频率合成器结构简单,造价低,并且有良好的相位噪声特性,所以我们采用间接式频率合成方案。

间接式频率合成器的具体实现方案由很多,主要有混频锁相式、取样锁相式和数字分频锁相式三种。

我们采用的是数字分频锁相式的。

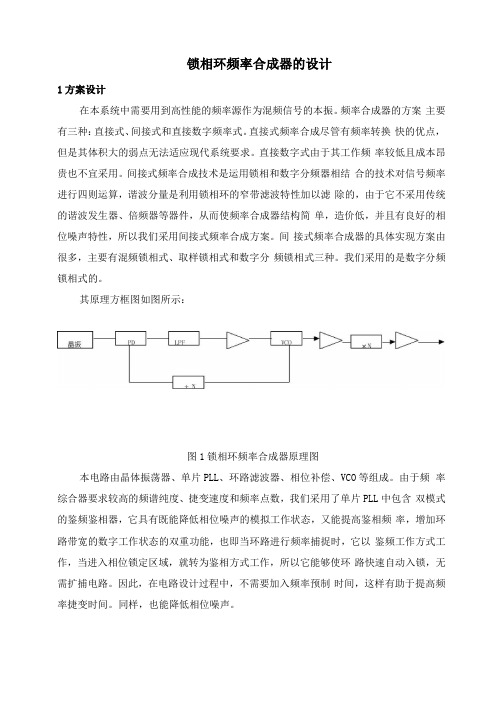

其原理方框图如图所示:图1锁相环频率合成器原理图本电路由晶体振荡器、单片PLL、环路滤波器、相位补偿、VCO等组成。

由于频率综合器要求较高的频谱纯度、捷变速度和频率点数,我们采用了单片PLL中包含双模式的鉴频鉴相器,它具有既能降低相位噪声的模拟工作状态,又能提高鉴相频率,增加环路带宽的数字工作状态的双重功能,也即当环路进行频率捕捉时,它以鉴频工作方式工作,当进入相位锁定区域,就转为鉴相方式工作,所以它能够使环路快速自动入锁,无需扩捕电路。

因此,在电路设计过程中,不需要加入频率预制时间,这样有助于提高频率捷变时间。

同样,也能降低相位噪声。

另外,对于输出频率大于2GHz的本振源,我们采用倍频法来得到微波毫米波段的输出信号。

需要在锁相环的输出后附加微波毫米波倍频组件,以得到更高的频率。

2各电路部件的实现2.1单片PLL为了满足小体积的要求,我们采用单片PLL频率合成技术,单片PLL频率合成技术是现代频率合成技术的一大革命,它使得P、L、S波段实现小型化、低相位噪声频率合成器成为可能。

在本方案中,我们采用Q3236来实现。

美国QUALCOMM公司推出的Q3236单片PLL 芯片,其性能优良,工作频率在0—2GHz,除此之外,Q3236还具有以下特性: 1)内设前置+ 10/11分频器2)输入灵敏度范围-10dBm— +10dBm3)鉴相器增益高达302mv4)输入驻波比小于2:15)程序控制端口TTL/CMOS兼容,8bit串行的或并行的数据线6)锁定指示7)参考分明比在1-16之间8) 2-128分频器的工作频率可达300MHz, 90—1295分频比的工作频率可达2GHz Q3236还包括以下几个功能部件:1)高速参考信号线性接收管和高速丫^的输出信号的线性接收器2)可以高频工作的+ 10/11双模前置分频器3)由M和人计数器组成的吞脉冲计数分频器4)可编程的参考分频器5)数字鉴频/鉴相器6)锁定/失锁检测电路7) TTL/CMOS兼容的并行接口和8位数据总线接口使用Q3236来实现锁相环路,只需外加一阶环路滤波器和丫8,参考分频比和分频比均采用外部控制模式。

锁相环频率合成器的设计-相关资料-仿真结果-论文参考62483

锁相环频率合成器的设计摘要:在通信领域中,锁相环频率合成器起着越来越重要的角色。

此论文是一篇介绍基于PROTEL的锁相环频率合成器设计的有关文章。

频率合成器是一个系统,最初产生的一系列频率为参考频率的整数倍,参考频率通常是固定的。

这样的合成器称为整数N 频率合成器。

频率合成器技术也不断前进,出现也很多新型的频率合成电路,并在通信电路中得到广泛使用。

锁相环由鉴相器、环路滤波器和压控振荡器组成。

频率合成一个或少量的高准确度高稳定的标准频率作为参考频率,由此导出多个或大量的输出频率.这些输出频率的准确度和稳定度和参考频率是一致的,频率合成器就是用来产生这些频率的部件.关键词:PROTEL 、锁相环、频率合成器、鉴相器The design of phase-locked loop frequency synthesizer Abstract: In the field of communications, phase-locked loop frequency synthesizer is playing an increasingly important role. This paper is an introduction of the design of PROTELPLL-based frequency Synthesis is a system, initially the frequency of a series of reference for the entire frequency several times, the reference frequency is usually fixed. This synthesizer called integer N Synthesis. Synthesis technology is constantly advancing, there are a lot of new frequency synthesizer circuit, and in the communications circuits are widely used. synthesizer .Phase-locked loop is componented by the phase detector, loop filter and VCO. Synthesis is that one or a small number of high-accuracy high-stability frequencys standard as a reference frequency, which derived more than a large number of output frequencys. The accuracy and stability of these output frequencys is consistented with the reference frequency, the frequency synthesizer is used to generate these frequency.Key words: PROTEL、Phase-locked loop 、Frequency synthesizer 、Phase detector第一章 锁相环路设计基础这一部分首先阐明了锁相环的基本原理及构成,导出了环路的相位模型和基本方程,概述了环路的工作过程,1.锁相环基本原理锁相环(PLL )是一个相位跟踪系统。

基于锁相环的频率合成器的设计

基于锁相环的频率合成器的设计随着现代技术的进展,具有高稳定性和精确度的频率源已经成为通信、雷达、仪器仪表、高速计算机及导航系统的主要组成部分。

高性能的频率源可通过频率合成技术获得。

随着大规模的进展,锁相式频率合成技术占有越来越重要的地位。

由一个或几个高稳定度、高精确度的参考频率源通过数字锁相频率合成技术可获得高品质的离散频率源。

1 锁相环频率合成器的原理1.1 锁相环原理锁相环(PLL)是构成频率合成器的核心部件。

主要由相位(PD)、压控(VCO)、环路(LP)和参考频率源组成。

锁相环是一种利用外部输入的参考信号控制环路内部振荡信号反馈控制。

他的被控制量是相位,被控对象是压控振荡器。

1所示,假如锁相环路中压控振荡器的输出信号频率发生变幻,则输入到相位比较器的信号相位θv(t)和θR(t)必定会不同,使相位比较器输出一个与相位误差成比例的误差Vd(t),经环路滤波器输出一个缓慢变幻的直流电压Vc(t),来控制压控振荡器输出信号的相位,使输入和输出相位差减小,直到两信号之间的相位差等于常数。

此时,压控振荡器的输出信号频率和输入信号频率相等,且环路处于锁定状态。

1.2 锁相环频率合成器原理2所示,锁相环频率合成器是由参考频率源、参考分频器、相位比较器、环路滤波器、压控振荡器、可变分频器构成。

参考分频器对参考频率源举行分频,输出信号作为相位比较器参考信号。

可变分频器对压控振荡器的输出信号举行分频,分频之后返回到相位比较器输入端与参考信号举行比较。

当环路处于锁定时有f1=f2,由于f1=fr/M,f2=fo/N,所以有fo=Nfr/M。

只要转变可变分频器的分频第1页共3页。

锁相频率合成器的设计

锁相频率合成器的设计

锁相频率合成器是一种电子设备,用于产生高精度、稳定的时钟信号。

它的设计基于锁相环(PLL)的原理,能够将输入的参考时钟信号锁定到输出时钟信号的频率,从而实现精确的频率合成。

锁相频率合成器的基本组成包括相锁环、参考时钟源、振荡器、分频器、相位检测器和控制电路等部分。

其中,相锁环是核心部件,其工作原理为将参考时钟信号和振荡器输出的信号进行比较,通过相位检测器不断调整振荡器的频率和相位,使其与参考时钟信号同步。

在设计锁相频率合成器时,需要考虑多种因素,如稳定性、相位噪声、抖动、锁定时间、输入输出频率范围等。

为了实现高精度的频率合成,通常会采用高品质的元器件和优化的电路设计,同时还需要进行严格的测试和调试。

锁相频率合成器广泛应用于通信、测量、计算机和工业控制等领域,为各种设备和系统提供高精度的时钟信号支持。

随着技术的不断进步,锁相频率合成器的设计也在不断升级和完善,以满足更加严格的应用需求。

- 1 -。

锁相环频率合成器的方案研究

锁相环频率合成器的方案研究随着大规模集成电路的发展,各种新型的频率合成器和频率合成方案不断涌现,利用锁相环频率合成技术研制出了很多频率合成集成电路。

本文介绍一种以摩托罗拉公司生产的MC145152 芯片的为基础的频率合成器。

这种锁相环频率合成器的稳定度和准确度与基准频率一致,从总体结构上看由单片机、锁相环及可编程分频器三部分组成。

其中可编程分频器是单片微机与锁相环之间的接口,同时也是组成数字锁相频率合成器的关键部件,在移动通信陆地电台等领域有着广泛的应用。

1 MC145152 芯片的特点及功能MC145152 是MOTOROLA 公司生产的大规模集成电路,是16 比特并行输入并行输入数据编程的双模锁相环频率合成器,该芯片内含参考频率振荡器、可供用户选择的参考分频器(分频比为8,64,128,256,512,1 024,1 160,2 048),双端输出的数字鉴相器、控制逻辑、10 比特可编程的÷N计数器(分频比为3~1 023)、6 比特可编程÷A计数器(计数范围为0~63)和锁定检测等部分。

其中,10 比特÷N计数器、6 比特÷A计数器、模拟控制逻辑和外接双模前置分频器组成吞脉冲程序分频器,吞脉冲程序分频器的总分频比为:N 总=NP+A,其内部组成框图如图1 所示。

(1)他与双模(P/(P+1))分频器同时使用,有一路双模分频控制输出MC。

当MC 为低电平时,双模分频器用(P+1)去除;当MC 为高电平时,双模分频器用模数P 去除。

(2)他有A 计数器和N 计数器两个计数器。

他们与双模(P/(P+1))分频器提供了总分频值(NP+A)。

其中,A、N 计数器可预置。

N 的取值范围为3~1023,A 的取值范围为0~63。

A 计数器计数期间,MC 为低电平;N 计数器计。

基于AD9850锁相环频率合成器的研究与设计

基于AD9850锁相环频率合成器的研究与设计摘要:本系统以51单片机为控制核心,由正弦信号发生模块组成。

采用数控的方法控制DDS芯片AD9850产生1Hz-35MHz正弦信号,1Hz-1MHz方波,输出方波频率为500KHz时上升沿和下降沿有点失真,幅度为5V,最高输出正弦波频率为35MHz无失真,幅度为0.6V。

测试信号发生模块产生的1kHz正弦信号。

关键词:直接数字频率合成,AD98501引言1.1课题研究的意义与作用1971年,美国学者j.Tierney等人撰写的“A Digital Frequency Synthesizer”-文首次提出了以全数字技术,从相位概念出发直接合成所需波形的一种新的频率合成原理。

限于当时的技术和器件水平,它的性能指标尚不能与已有的技术相比,故未受到重视。

近10年间,随着微电子技术的迅速发展,直接数字频率合成器(Direct Digital Frequency Synthesis简称DDS[2]或DDFS)得到了飞速的发展,它以有别于其它频率合成方法的优越性能和特点成为现代频率合成技术中的姣姣者。

具体体现在相对带宽宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号、可编程和全数字化、控制灵活方便等方面,并具有极高的性价比。

1.2 DDS的研究现状及发展趋势在频率合成(FS, Frequency Synthesis)领域中,常用的频率合成技术有模拟锁相环、数字锁相环、小数分频锁相环(fractional-N PLL Synthesis)等,直接数字合成(Direct Digital Synthesis-DDS)是近年来新的FS技术。

单片集成的DDS产品是一种可代替锁相环的快速频率合成器件。

DDS是产生高精度、快速变换频率、输出波形失真小的优先选用技术。

DDS以稳定度高的参考时钟为参考源,通过精密的相位累加器和数字信号处理,通过高速D/A变换器产生所需的数字波形(通常是正弦波形),这个数字波经过一个模拟滤波器后,得到最终的模拟信号波形。

锁相环与频率合成器实验讲义

锁相与频率合成技术实验讲义桂林电子科技大学通信实验中心实验一锁相环实验一、实验原理锁相环路实质是一个负反馈的相位差自动调节系统。

1、锁相环路的构成图1 锁相环基本框图1(1)鉴相器鉴相器是相位差转换成电压的变换器(θe / V变换器、相差/电压变换器),它把两个信号U2(t)和U1(t)的相位进行比较,产主对应于两个信号相位差θe的误差电Ud(t)。

图2(a) 鉴相器模型23图2(b )异或门鉴相曲线 图2(c )数字比相器的鉴频鉴相曲线4如图2(c )的数字比相器,其特性可以理解为:① 对于相位跳变信号,如f1输入已调2PSK 信号,f2输入载波信号,则鉴相器的输入输出信号为:图3 f 1 :PSK 信号图4 f 0: 载波信号图5 f 1 与f 0 的相差θe图6 鉴相器的输出电压Ud②对于频率跳变信号,如f1输入已调2FSK信号,由高低频率f H、f L组成,f2输入f L信号,则鉴相器的输入输出信号为:图7 f1:FSK信号图8 f0:FSK的f L信号图9 f1与f0 的相差θe5(2)环路滤波器环路滤波器的作用是滤除误差电压Ud(t)中的进行积分,以保证环路所要求的性能,增加系统的稳定性。

环路滤波器常用的类型有RC积分滤波器,无源比例积分滤波器,有源比例积分滤波器。

(3)压控振荡器VCO的技术指标:中心频率、频率变化范围、频率稳定度、相位噪声、压控线性度、压控灵敏度。

图11 压控振荡器控制电压/ 输出频率(Uc-ωO)特性曲线6同步带与捕获带同步带的测量方法:环路锁定之后,缓慢提高信号源的输入频率,直到输入输出频率不相等,测出Δωh H ;用同样方法测量Δωh L ,环路锁定之后,降低信号源的输入频率,直到输入输出频率不相等,测出ΔωL 。

图20 PLL同步带范围78同步带的测量方法:由于频率太低引起环路失锁之后,缓慢提高信号源的输入频率,直到输入输出频率不相等,测出Δωp H ;用同样方法测量Δωp L 。

锁相式数字频率合成器实验报告.

*******************实践教学*******************兰州理工大学计算机与通信学院2012年春季学期《通信系统基础实验》设计项目实验报告设计题目:锁相式数字频率合成器实验报告专业班级:设计小组名单:指导教师:陈昊目录一、设计实验目的 (3)二、频率合成基本原理 (4)2.1频率合成的概念 (4)2.2频率合成器的主要技术指标 (4)2.3锁相频率合成器 (5)三、锁相环技术 (6)3.1 锁相环工作原理 (6)3.2 锁相环CD4046芯片介绍 (6)四、基于锁相环技术的倍频器 (10)4.1 HS191芯片介绍 (10)4.2 基于锁相环技术的倍频器的设计 (12)4.2.1 工作原理 (12)3.2.2 Proteus软件仿真 (13)4.2.3 硬件实现 (14)4.2.4 锁相环参数设计 (15)五、总结与心得 (17)六、参考文献 (18)七、元器件清单 (19)一、设计实验目的1. 掌握VCO压控振荡器的基本工作原理。

2. 加深对基本锁相环工作原理的理解。

3. 熟悉锁相式数字频率合成器的电路组成与工作原理.。

二、频率合成基本原理2.1频率合成的概念频率合成是指由一个或多个频率稳定度和精确度很高的参考信号源通过频率域的线性运算,产生具有同样稳定度和精确度的大量离散频率的过程。

实现频率合成的电路叫频率合成器,频率合成器是现代电子系统的重要组成部分。

在通信、雷达和导航等设备中,频率合成器既是发射机频率的激励信号源,又是接收机的本地振荡器;在电子对抗设备中,它可以作为干扰信号放生器;在测试设备中,可作为标准信号源,因此频率合成器被人们称为许多电子系统的“心脏”。

早期的频率合成是用多晶体直接合成,以后发展成用一个高稳定参考源来合成多个频率。

20世纪50年代出现了间接频率合成技术。

但在使用频段上,直到50年代中期仍局限于短波范围。

60年代中期,带有可变分频的数字锁相式频率合成器问世。

基于单片机的锁相环频率合成器设计

基于单片机的锁相环频率合成器设计1. 引言在现代通信系统和电子设备中,频率合成器是一个非常重要的电路模块,用于产生稳定的高精度时钟信号。

锁相环频率合成器是一种常用的频率合成器,它通过锁相环技术来实现输入信号与输出信号之间的频率转换。

本文将重点研究基于单片机的锁相环频率合成器设计。

2. 锁相环原理2.1 相位比较器相位比较器是锁相环中最基本的模块之一,它用于比较输入信号与反馈信号之间的相位差。

常见的相位比较器有两种类型:数字型和模拟型。

数字型相位比较器采用数字逻辑电路实现,具有高速度和稳定性;而模拟型相位比较器采用模拟电路实现,具有更高精度。

2.2 低通滤波器低通滤波器用于滤除输出信号中的高频噪声,并提供平稳且稳定的控制电压给振荡器。

在锁相环中,低通滤波器通常采用RC滤波网络或者积分放大电路来实现。

2.3 振荡器振荡器是锁相环中的核心部件,它产生稳定的输出信号,并通过反馈回路与相位比较器进行相位比较。

常见的振荡器类型有晶体振荡器、LC振荡器和压控振荡器等。

在本设计中,我们选择晶体振荡器作为基准信号源。

3. 设计流程3.1 系统框图设计首先,我们需要进行系统框图设计,确定锁相环频率合成器的基本结构和各个模块之间的连接方式。

在本设计中,系统框图主要包括相位比较器、低通滤波器、数字控制模块和输出模块。

3.2 相位比较器设计根据系统需求和性能指标,选择合适的相位比较器类型,并进行电路设计和参数选取。

在本设计中,我们选择数字型相位比较器,并采用逻辑门电路实现。

3.3 低通滤波器设计根据系统要求和频率范围选择合适的低通滤波网络或者积分放大电路,并进行电路参数计算与仿真分析。

在本设计中,我们选择RC滤波网络作为低通滤波器。

3.4 数字控制模块设计设计数字控制模块,用于控制锁相环频率合成器的工作状态和频率设置。

在本设计中,我们选择单片机作为数字控制模块的核心芯片,并通过编程来实现频率设置和状态控制。

3.5 输出模块设计设计输出模块,用于输出锁相环频率合成器产生的稳定时钟信号。

锁相环频率合成器的原理与设计

2.1对于现代移动通信中的移动台来说,频率合成器是由锁相环路(PLL)构成的。

锁相环是一种相位负反馈系统,它利用环路的窄带跟踪与同步特性将鉴相器一端VCO的输出相位与另一端晶振参考的相位保持同步,实现锁定输出频率的功能,同时可以得到和参考源相同的频率稳定度。

一个典型的频率合成器原理框图如图1所示。

设晶振的输出频率为f r,VCO输出频率为fo,(1)其中R和N分别为参考分频器和主分频器的分频比,在外部设置并行或串行数据控制分频比,就可以产生出所需要的频率信号。

用锁相环构成的频率合成器具有频率稳定度高、相位噪声随着大规模集成电路的应用,参考分频器、鉴相器和主分频器以及进行程序控制的寄存器能够集成在一块芯片中,如图1中虚线框所示,这样整个电路就仅由一个PLL芯片、一片晶振、一片VCO以及环路滤波器等分立元件组成,大大锁相环是传递相位的闭环系统,只要研究环路的相位数学模型或其基本方程就可以获得环路的完整性能。

根据图1所示,设θi为晶振经R分频器分频之后的相位,θo为VCO输出相位,θo为VCO经N分频器分频之后的相位,θe为鉴相器的输出相位,环路的基本函数可以表示为:(1)2.2(1)在目前应用的小型频率合成器电路中,广泛采用电流泵型数字式鉴频鉴相器,其输出为数字的电流信号I(t),I(t)的宽度反映了两输入信号的相位差值,极性则反映了两输入信号的相位差的正负。

在鉴相器之后的环路滤波器将电流信号转变为电压,控制VCO的变化。

它具有(2)环路滤波器有无源和有源两种形式,考虑到体积与噪声等因素,在手机中一般采用无源三阶环路滤波器。

具体电路如图2该滤波器是由C C2、R R成的辅助滤波器所合成,可以将电流泵鉴相器输出的鉴相电流转换成控制电压。

辅助滤波器的作用是抑制鉴相频率的输出纹波,而对整个滤波器的极点没有影响,所以在推算环路方程时,可以不做考虑。

C C R该环路为三阶环路,在工程上可以进行近似,当满足C C10时,这一传递函数与采用理想积分滤波器的环路闭环传递函数完全相同,所以,采用该滤波器的辅助滤波器的选取以不影响环路带宽和截止频率要低于鉴相频率为度,但应注意C上包含了VCO变容管的并联电容,所以实际的C3 环路中相位噪声和锁定在通信接收机中,频率合成器的相位噪声是影响接收机性能的因素之一。

锁相环频率合成器的原理与设计

锁相环频率合成器的原理与设计2.1 锁相环的基本原理和基本公式对于现代移动通信中的移动台来说,频率合成器是由锁相环路(PLL)构成的。

锁相环是一种相位负反馈系统,它利用环路的窄带跟踪与同步特性将鉴相器一端VCO的输出相位与另一端晶振参考的相位保持同步,实现锁定输出频率的功能,同时可以得到和参考源相同的频率稳定度。

一个典型的频率合成器原理框图如图1所示。

设晶振的输出频率为fr,VCO输出频率为fo,则它们满足公式:(1)其中R和N分别为参考分频器和主分频器的分频比,在外部设置并行或串行数据控制分频比,就可以产生出所需要的频率信号。

用锁相环构成的频率合成器具有频率稳定度高、相位噪声小、电路简单易集成、易编程等特点。

随着大规模集成电路的应用,参考分频器、鉴相器和主分频器以及进行程序控制的寄存器能够集成在一块芯片中,如图1中虚线框所示,这样整个电路就仅由一个PLL芯片、一片晶振、一片VCO以及环路滤波器等分立元件组成,大大减小了体积,也降低了设计难度。

下面对锁相环同步状态下的线性性能进行分析。

锁相环是传递相位的闭环系统,只要研究环路的相位数学模型或其基本方程就可以获得环路的完整性能。

根据图1所示,设θi为晶振经R分频器分频之后的相位,θo为VCO输出相位,θ’o为VCO经N分频器分频之后的相位,θe为鉴相器的输出相位,环路的基本函数可以表示为:(1)闭环传递函数:2.2 锁相环的设计(1)鉴相器在目前应用的小型频率合成器电路中,广泛采用电流泵型数字式鉴频鉴相器,其输出为数字的电流信号I(t),I(t)的宽度反映了两输入信号的相位差值,极性则反映了两输入信号的相位差的正负。

在鉴相器之后的环路滤波器将电流信号转变为电压,控制VCO的变化。

它具有以下特点:①环路的相位锁定性能具有理想二阶环的特性。

②输出纹波小。

③具有鉴频鉴相的功能,鉴相范围宽,捕捉带等于同步带。

④便于集成,调整方便,性能可靠。

(2)环路滤波器环路滤波器有无源和有源两种形式,考虑到体积与噪声等因素,在手机中一般采用无源三阶环路滤波器。

锁相环CD4046设计频率合成器

目录一、设计和制作任务 (3)二、主要技术指标 (3)三、确定电路组成方案 (3)四、设计方法 (4)(一)、振荡源的设计 (4)(二)、N分频的设计 (4)(三)、1KHZ标准信号源设计(即M分频的设计) (5)五、锁相环参数设计 (6)六、电路板制作 (7)七、调试步骤 (8)八、实验小结 (8)九、心得体会 (9)十、参考文献 (9)附录:各芯片的管脚图 (10)锁相环CD4046设计频率合成器内容摘要:频率合成是以一个或少量的高准确度和高稳定度的标准频率作为参考频率,由此导出多个或大量的输出频率,这些输出的准确度与稳定度与参考频率是一致的。

在通信、雷达、测控、仪器表等电子系统中有广泛的应用,频率合成器有直接式频率合成器、直接数字式频率合成器及锁相频率合成器三种基本模式,前两种属于开环系统,因此是有频率转换时间短,分辨率较高等优点,而锁相频率合成器是一种闭环系统,其频率转换时间和分辨率均不如前两种好,但其结构简单,成本低。

并且输出频率的准确度不逊色与前两种,因此采用锁相频率合成。

关键词:频率合成器CD4046一、设计和制作任务1.确定电路形式,画出电路图。

2.计算电路元件参数并选取元件。

3.组装焊接电路。

4.调试并测量电路性能。

5.写出课程设计报告书二、主要技术指标1.频率步进 1kHz2.频率稳定度f ≤1KHz3.电源电压 Vcc=5V三、确定电路组成方案原理框图如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N,从而就得到N倍参考频率的稳定输出。

晶体振荡器输出的信号频率f1,经固定分频后(M分频)得到基准频率f1’,输入锁相环的相位比较器(PC)。

锁相环的VCO输出信号经可编程分频器(N分频)后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到:f1/M=f1’=f2/N 故f2=Nf’1 (f’1为基准频率)当N变化时,或者N/M变化时,就可以得到一系列的输出频率f2。

基于锁相环技术的频率合成器的研究

基于锁相环技术的频率合成器的研究锁相环技术是一种基于反馈控制的信号同步技术。

锁相环电路由相位检测器、低通滤波器、可变放大器、振荡器等组成,其中振荡器输出的参考信号与输入信号进行比较,通过反馈控制调整振荡器输出频率,从而使得两个信号的相位差趋近于零。

当两个信号相位差为零时,锁相环电路输出的频率就等于期望的合成频率。

其中,参考信号经过相位检测器和低通滤波器得到的误差信号,经过可变放大器进行放大,并与振荡器输出的信号进行叠加,得到反馈控制后的输出信号。

在基于锁相环技术的频率合成器中,关键的部分在于相位检测器的设计。

常见的相位检测器有比例相位检测器、积分相位检测器、PI相位检测器、PD相位检测器、PLL相位检测器等。

比例相位检测器适用于相位差较小时的情况,其输出的误差电压与相位差成正比。

积分相位检测器适用于相位差较大的情况,通过对误差电压进行积分,可以较快地跟踪和控制相位差。

PI相位检测器和PD相位检测器则是将比例相位检测器和积分相位检测器进行组合,综合利用它们的优点进行相位控制。

PLL相位检测器则是一种广泛使用的相位检测器,其采用二次环结构,具有相位跟踪速度快、稳定性好等优点。

除了相位检测器的设计外,基于锁相环技术的频率合成器中还需考虑频率分辨率、稳定性、带宽等因素。

频率分辨率取决于振荡器的精度,稳定性取决于振荡器的稳定度和相位检测器的性能,带宽则是反映锁相环电路跟踪所能达到的最大频率变化率。

为了提高基于锁相环技术的频率合成器的性能,有一些研究者提出了一些改进的方法,如多相锁相环频率合成器、数字锁相环频率合成器等。

多相锁相环频率合成器可以同时产生多路相位一致的输出信号,具有较高的相位稳定度;数字锁相环频率合成器则可以采用数字信号处理来实现相位检测器和滤波器,具有更高的精度和可编程性。

综上所述,基于锁相环技术的频率合成器具有简单、稳定、可靠、精度高等优点,广泛应用于无线通信、仪器测量、数字信号处理等领域。

一种级联锁相环频率合成器的设计与实现

一种级联锁相环频率合成器的设计与实现随着信息科技的发展,频率合成技术变得越来越重要。

由于频率合成器不仅能够提供精确控制的信号,而且具有高灵敏度、高精度、高稳定性和可靠性等优越特性,在很多领域,尤其是语音和数据传输领域,频率合成器被广泛应用。

级联锁相环(Cascaded Phase-Locked Loop,CPL)技术是一种先进的频率合成技术,能够提高抑制失真的能力,降低合成器的时钟数量,改进合成器的频率设计和合成器的工作稳定性。

因此,研究一种基于CPL技术的频率合成器具有重要意义。

本文以一种基于CPL技术的频率合成技术为研究对象,主要包括三个部分:基本原理、技术设计和实验验证。

首先,介绍CPL技术及其基本原理,着重介绍锁相环结构、锁相技术和差分分频结构等技术要素,并结合实际应用场景分析其优点和缺点。

其次,讨论多级CPL 合成器的技术设计,指出本研究中采用的多级CPL结构,分析各部分的构建原理,给出各部分的参数设定及其实现方法,并阐明其和其他结构的不同。

最后,给出通过FPGA实现本研究基于CPL技术的合成器系统,并对其进行实验验证,从实验结果可以看出,相比于传统合成器,本研究的基于CPL技术的合成器系统,具有较高的频率精度和稳定性,在信息传输领域有着更高的应用价值。

从以上内容可以看出,基于CPL技术的频率合成器已经成为一种先进的合成技术,具有抑制失真、降低合成器时钟数量、改进合成器频率设计及工作稳定性等优越性能,它受到了电子行业及其他行业的高度重视。

未来,将结合实际应用不断优化之前的CPL技术,构建更

先进的CPL合成器,并将其运用于更广泛的领域,以满足用户不断变化的应用需求。

一种电荷泵锁相环频率合成器的设计与研究的开题报告

一种电荷泵锁相环频率合成器的设计与研究的开题报告1. 研究背景电荷泵锁相环频率合成器是一种基于锁相环原理的频率合成器,主要用于产生高稳定度的高频信号。

在现代通信系统中,高稳定度的时钟信号对数据传输的精度和可靠性至关重要。

因此,研究与设计高稳定度的电荷泵锁相环频率合成器成为了一项重要的技术任务。

2. 研究目的本研究的主要目的是设计与研究一种高稳定度的电荷泵锁相环频率合成器,并对其性能进行评估。

具体包括以下几个方面:- 设计一种基于锁相环原理的电荷泵- 研究电荷泵锁相环频率合成器的工作原理- 选择合适的电路元件、设计合适的参数和优化电路结构,提高电路的性能- 对电荷泵锁相环频率合成器的性能进行测试和验证3. 研究内容本研究主要涉及以下内容:3.1 锁相环原理锁相环是一种基于反馈控制原理的电路系统,它的主要功能是将输入信号的频率和相位锁定到一个参考信号上。

在锁相环中,参考信号通常指定时钟信号,输入信号则是需要产生的高频信号。

3.2 电荷泵的设计电荷泵是锁相环电路中的一个重要组成部分,它的主要作用是将锁相环输出的低频信号转换为高频信号,在电路中扮演着倍频器的作用。

因此,电荷泵的设计对电路的性能具有重要影响。

3.3 电路的参数选择和优化为了提高电路的性能,需要选择合适的电路元件、设计合适的参数和优化电路结构。

本研究将针对以上问题进行深入研究,并寻求最优的设计方案。

4. 研究方案本研究的主要研究方案包括以下几个方面:4.1 研究锁相环原理及其工作研究锁相环的基本原理,分析其工作过程,建立数学模型、探究工作特性,并分析不同电路参数对锁相环的影响。

4.2 设计电荷泵设计电荷泵的电路结构及倍频器运作原理,对电荷泵进行实验验证,并对电荷泵电路的优化设计和参数调整进行理论分析和实验测试。

4.3 优化电路结构和参数采用仿真工具进行电路仿真,针对获得的仿真结果进行电路结构和参数的优化调整,以达到最佳性能。

4.4 性能测试在实验室中利用测试设备进行性能测试,评估电路的性能,验证电路设计的稳定性和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

锁相环频率合成器的研究与设计

作者:王亚洲

来源:《中国科技博览》2015年第20期

中图分类号:TN511 文献标识码:A 文章编号:1009-914X(2015)20-0210-01

前言

锁相环技术对于信号的调制与解调、信号的调频与解调以及信号频率合成电路都发挥着不容小觑的作用。

目前,在电子通信的各个领域中都随处可见锁相环频率合成器的身影,而且随着我国科技的不断进步与发展,无线通信以及便携式设备的快速发展,使得我们不满足于传统的锁相环技术,我们亟需新型的锁相环频率合成器以适应时代的需求,使我国的电子通信工程行业得到发展。

1. 锁相环以及频率合成器的相关概念

1.1锁相环的技术概述

对于锁相环来说,它是一种相位锁定环路,主要是由鉴相器、环路滤波器和压控振荡器组成,它与反馈放大器类似,不过它是一种负反馈的系统。

它不同于反馈放大器的最主要一点就是,反馈放大器反馈的物理量为电压或者电流,而对于锁相环,它则是一种关于相位的负反馈系统,反馈的物理量为相位。

而从“锁相环”这个名字也可以看出它最主要的作用就是锁相,即锁定相位。

相位则是信号的一个重要信息,因此锁相环它可以锁定相位并且可以使处在环路中的受控振荡器的输出相位与输入信号的相位保持一致,或者保持固定的差值。

说一个简单的应用,收音机解调的时候捕捉住载波就要锁定相位,否则解调就会出偏差。

1.2锁相环频率合成器的相关概念

锁相环频率合成器是以锁相环路为核心,增加分频器就可以构成锁相环频率合成器,它在我们日常生活中的通信系统以及数字系统中有着广泛的应用与使用价值。

在通信系统中,主要用于产生频率变换时所需的本振信号,而锁相环本身也可以用于信号调制和解调;另外在数字系统中,频率合成器在时钟行业有着更加重要的作用,频率合成器可以将时钟的信号质量明显地得到提升,使时钟的报时变得更加准确且不易受外源信号的干扰。

锁相环频率合成器是负反馈系统,以相位为反馈单位,将输入的信号与最终的压控振荡器输入信号进行比较,当输出信号不同于输入信号的时候,通过反馈系统将输出信号传到输入系统,输入系统接收到反馈的输出信号时,系统对差值进行电压的控制,调节输出系统的压控振荡器,如此循环往复可以使得最终的输出信号与输入信号的相位与频率相同,在理论上通过反馈系统控制的输出与输入系统的信号差可以为零。

锁相环频率合成器由于其低噪声、低功耗、高集成度的性能使得其应用更加广泛。

[1]

2. 频率合成器电路实现设计

对于锁相环频率合成器来说,鉴频鉴相器与电压泵是其重要的组成结构,因此对于此二者的设计就显得至关重要。

2.1鉴频鉴相器的设计

鉴频鉴相器在锁相环中用于检查参考信号与反馈信号之间的误差值,根据该差值的正负和大小输出一对宽度与差值成正比的脉冲UP和DN,这一对脉冲控制后面的电荷泵对环路滤波器进行充电和放电。

在鉴频鉴相器出现之前主要都是采用鉴相器来对锁相环中的相位进行检测。

鉴频鉴相器的出现使得对锁相环中的相位差能够更好地进行控制,是在鉴相器的基础上进行的改进。

鉴相器的种类也有很多,常见的有模拟乘法器、异或门鉴相器、J-K触发器等,此三种鉴相器当锁相环处于未锁定状态时,鉴相器输出为一个频率等于两信号频率差的正弦信号,不过由于这个正弦信号的正半周与负半周的波形不一致,很容易因为起始频率的差值小于捕捉范围而导致非零的直流成分的出现,这使得牵引压控振荡器输出频率出现波动变化,一直到锁相环进行锁定的时候才能够平稳下来,不过由于锁相环的锁定并不是很容易进行的,锁相时间会大大地增加,因此在实际应用中,锁相环的使用有其局限性。

因此为了使得锁相环能够在实际使用中更好更快地进行锁相环的锁相,减少其捕捉时间就需要对鉴相器进行改进,鉴频鉴相器也就随之产生。

对鉴频鉴相器的设计要求如下:PFD的输出电压随输入信号的相位差的变化曲线要求特性曲线为线性,同时线性的范围要足够大;此外对于鉴相灵敏度的也要进行要求,单位相位差产生的输出电压,V/rad。

一个理想的PFD鉴相灵敏度与输入信号的幅度没有关系,当鉴相特性不为线性时,一般我们定义ф=0点上的灵敏度;最后对于鉴相范围来说,理想情况为[-2π,2π],不过实际上还需要考虑复位时候的延迟效应,这样就导致鉴相的范围不能够达到4π,需要我们进一步考量。

2.2电荷泵的设计

电荷泵也是锁相环中的重要组成部分,它是一个直流与直流电之间的转换电路,经它的作用可以获得更高的直流电压,可以将相位误差转换为电流。

一般情况下,为了保证鉴频鉴相器和电荷泵组合的鉴相特性曲线的线性度,通常电荷泵的充放电电流大小是相同的,都等于Icp。

对于电荷泵来说,由于电路节点上都有寄生电容的存在,电荷泵开关开启的过程中控制脉冲需要对开关的栅电容充电,到达一定电压大小之后开关管才开,从而出现“死区”问题。

为了解决“死区”问题可以通过在鉴频鉴相器引入复位脉冲,不过这样做又会导致新问题的出现,使锁相环的杂散性能受到抑制,最终导致电流的泄漏以及电流及时间的失配问题等。

因此可以对电压泵进行图1的设计,图1中的(a)为电荷泵电流镜结构,是采用高摆幅的共栅共源结构进行电流源的充放电;图1(b)是电压跟随运算放大器,它是并不复杂的单级运放,作为电压跟随器消除电荷共享效应;图1(c)是充放电的开关,用于充放电电流的控制。

充放电的开关采取的是NMOS和PMOS互补的传输门,使得开关的电荷注入效应得到明显的改善,信号有上文所提到的鉴频鉴相器提供,通过图1(a)的作用产生信号的反相信号,避免反相路径间的延时失配。

如果输入电流为20μA的话,经过此电压泵的结构会使得输入电流进行镜

像的放大,设定为10倍放大倍数则可以得到输出的电流为200μA,如有其它倍数要求的电流,同理亦可获得。

[2]

(a)电荷泵电流镜结构(b)电压跟随运算放大器(c)充放电开关

3.锁相环频率合成器系统的环路参数设计

由于我国近年来卫星的成功发射以及我国北斗卫星导航系统的建立,GPS系统是我国要大力发展的领域。

而锁相环频率合成器可以在GPS接收机系统进行应用,不过由于GPS无线通信的频段有其自身的要求,而且还由于有着相关的标准,对GPS所在频带的信道状况进行控制以确保GPS接收机能够满足应用。

这些具体的设计要求主要为:在输入频率上的要求为16.368MHz,同时要注意为晶振输入,因为采用晶体振荡器输入信号会使得噪声性能变得更加优越,目前行业内的无线通信系统中的时钟源一般都是采取此种方式;在输出频率上的要求则为正交输出1571.328MHz;锁相环合成器要实现全集成以及滤波器内置的设计结构;锁相环频率合成器对于相位噪声以及锁定时间都有着不小的要求,从相位噪声上来说,不得大于-

80dBc/Hz @10KHz、-90dBc/Hz@100KHz、-115dBc/Hz@1MHz;而锁定时间一定要确保小于50μS。

4.结语

目前,锁相环技术早已渗透到我们日常生活的方方面面,从电视扫描同步、频率的解调与变换再到时钟的产生、数据时钟恢复、位同步等,电子通信领域锁相环频率合成器正在大放异彩,随着科技的进步,人们对其的需求也越来越高,锁相环频率合成器的研究与设计值得重视。

参考文献

[1] 金晶.CMOS射频频率综合器的研究设计与优化[D]. 上海:上海交通大学,2012.

[2] F.M. Gardner.锁相环技术(第3版)[M].北京.人民邮电出版社,2007,314—315.。