基于锁相环的频率合成器..

基于MC145151-2PPL频率合成器的设计

一

频 率 合 成 器 的 频 率分 辨 率 。 改 变 R数值 的 大 小 ,

准 频率源相组合 ,就能产生与标准信号源有相 同的频率稳定度、准确度的众多频率点。

可改变频率合成器的分辨率。由以上可以看 出 当环路锁定后,压控振荡器的输出频率严格 与 输入 频率 行相等 。同时在 一定 范围 内跟踪 输 入信号频率变化 ,具有 良好 的跟踪特性 。只要 L P F通频带设计合理,整个环路就具有 良好的

窄带滤波特性。

1 M C 1 4 5 1 5 1 - 2 锁相环 简介

MC1 4 5 1 5 1 - 2是 一 块 双 列 直 插 式 C M OS大 规 模 集 成 电路 , 由 4位 总 线 输 入 、 锁 存 器 选 通

个 高 稳 定度 的 标 准 频 率 f s , 经 参 考 分 频 器 进

:

R A 2 R A 1 R A o M c 1 4 5 1 5 1 — 2

: : M A X 3 0 8

;

随 着 移 动 通 信 、雷 达 技 术 以及 遥 测 、 遥

感测控技术不断发展 ,各种 系统对频 率源 的要 求越来越高 , 不但 要求频率稳定度和准确度高, 而且还要求能方便 的改变 收发频率。特别是无

图一 1 基 本锁相 环 频率合 成 器组 成框 图

【 关键词 】频率合成 V C O 锁相环 频率 源 分

频 器

广 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 1 广 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 1

基于NE564D锁相环频率合成器的设计

基于NE564D锁相环频率合成器的设计The Design of PLL Frequency Synthesizer Based on NE564D曾素琼(嘉应学院电子信息工程学院,广东梅州514015)Zeng Su-qiong(School of Electronics and Information Engineer, Jiaying University,Guangdong Meizhou 514015)摘要:设计基于NE564D的锁相频率合成器,对系统的实现作了详细描述,最后对系统作了实验验证及分析。

关键词:锁相环;锁相频率合成器;压控振荡器(VCO);NE564D中图分类号:TP273;TN915 文献标识码:B 文章编号:Abstract: In this paper, PLL frequency synthesizer based on NE564 is designed. The realization of the system was described in detail. Finally, experimental verification and analyzed of the system were made.Keywords: phase-locked loop; PLL frequency synthesizer; voltage-controlled oscillator (VCO);NE564DCLC number: TP273;TN915 Document code: B Article ID:1基于NE564D锁相环频率合成器的设计思路与系统框图锁相环NE564D是一种工作频率可高达50MHz的常用超高频集成锁相环,利用74LS393(74LS393是双四位二进制计数器)作为频率合成器的分频器,组成倍频锁相环频率合成器。

合成器输出频率为fo=Nfr。

式中fr为参考频率,通常是用高稳定度的晶体振荡器产生,对晶振频率固定之后获得的。

基于CD4046锁相环的数字频率合成器电路设计

文章编号 : 1 6 7 4 - 4 5 7 8 ( 2 0 1 3 ) 0 5 - 0 0 0 9 - 0 3

应 用 实 践

基于 C D 4 0 4 6锁 相 环 的 数 字频 率 合 成 器 电路 设 计

刘艳红

( 国营第七 八五 厂 , 山 西 太原 0 3 0 0 2 4 )

定时器产生 的电信号作为输入信 号 ( 参 考信号 ) f i 输入 4 0 4 6

相位 比较器一端 , 从 压控 振荡 器输 出信 号 f n经 可预置 分频 器( J 7 、 r 分频 ) 合 成后 得反 馈信 号 f b加 到相 位 比较 器 的另 一 端, 两个输入信号在相 位 比较 器 中进行 相位 或频率 比较 , 然

信号处理技术 , 它能严格跟踪相干信号频率 。利用锁 相环构 成的频率 合成 器电路结构 简单 , 输 出频率 成分 频谱 纯度 高 ,

是一个较好的频率 转换 系统 。

1 电路总体 设计 思路

该锁相环数字频率合成器 实现的主要 技术 指标为 : 输 入 频率 f i =1 0 0 H z ; 输 出频率 f o =1 0 0 H z ~9 9 . 9 k H z ; 分频 系数 Ⅳ为 1— 9 9 9之间的任意整数。其 总体框 架如图 1所示 :

摘 要: 主要介绍 C D 4 0 4 6锁相环 数字频率合成器的构成 电路及原理 。C D 4 0 4 6锁相 环数 字频 率合成 器主要 由 振荡源电路 、 1 / N可预置分频 器以及锁相 环电路 构成。其功能是将一给定 频率的输入信号 经频 率合成后产 生一 系 列的 Ⅳ倍频 率的输 出信号 。此频 率合 成器具有 系统稳定 、 精确度 高、 较 高的可选择 性与实用性等特 点。 关键词 : 频率合成 ;锁相环 ;C D 4 0 4 6 ;分频 器 中图分类号 : T N 7 4 2 . 1 文献标识码 : A

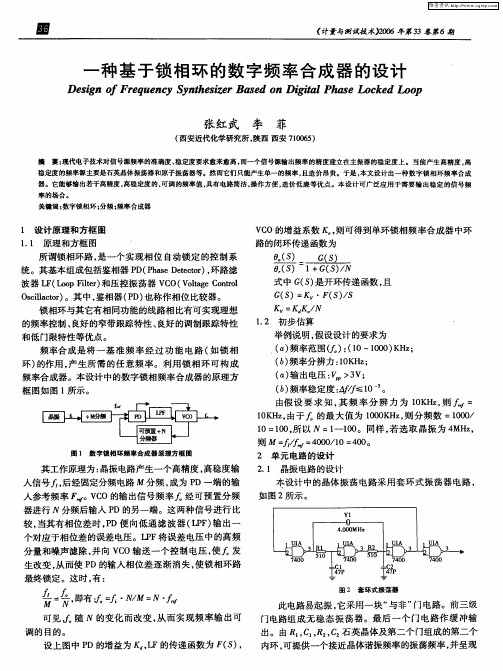

一种基于锁相环的数字频率合成器的设计

入信号 , 后经固定分频电路 分频 , 成为 P D一端的输 人参考频率 F 。 C V O的输出信号频率 经可预置分频 器进行 J 分频后输入 P 7 v D的另一端。这两种信号进行 比 较, 当其有相位差时 ,D便 向低通滤波器 ( P ) 出一 P LF 输 个对应 于 相位 差 的误差 电压 。L F将误 差 电压 中 的高 频 P 分量和噪声滤除 , 并向 V O输送一个控制 电压 , C 使 发 生改变 , 从而使 P D的输入相位差逐渐消失, 使锁相环路

( 西安近代化学研究所 , 陕西 西安 7 0 6 ) 10 5

摘 要: 现代电子技术对信 号源频率 的准确度 、 稳定度要求愈来愈高 , 而一个信 号源输 出频率的精度建立在主振器的稳定度上 。当前产生高精度 , 高

稳定度的频率源主要是 石英晶体振荡器 和原子振荡器等 。然而它们只能产生单一 的频率 。 且造价 昂贵 。于是 , 本文设计出一种数 字锁相环频率合成 器 。它能够输出若干高精度 。 高稳定度 的, 可调 的频率值 。 具有 电路简洁 , 操作方便 , 造价低 廉等优点 。本设计 可广泛应用 于需要输 出稳 定的信号频 率 的场合 。 关键词 : 数字锁相环 ; 分频 ; 频率合 成器

最 终锁 定 。这 时 , : 有

f

=

f

,

图 2 套 环 式 振 荡 器

即有 = ‘ / = ‘ NM N

此 电路 易 起振 , 采用 一 块 “ 非 ” 电路 。前 三 级 它 与 门

可见 随 』 v的变化而改变 , 从而实 现频率输 出可

调 的 目的。

门电路组成无稳 态振荡器 。最 后一个 门电路作缓 冲输 出 。由 尺 , 。尺 , 2 英 晶体及 第二 个 门组成 的第 二个 。C ,:c 石

基于CD4046锁相环的频率合成器设计

三、确定电路组成方案

原理框图(图1)如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N,从而就得到N倍参考频率的稳定输出。晶体振荡器输出的信号频率f1,经固定分频后(M分频)得到基准频率f2,输入锁相环的相位比较器(PC)。锁相环的VCO输出信号经可编程分频器(N分频)后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到:

图2 1——999分频器

五、锁相环参数设计

本设计中,M固定,N可变。基准频率f2定为100Hz,改变N值,使N=7001~7999,则可产生f2=700.1KHz—799.9KHz的频率范围。锁相环锁存范围:

fmax=800.00KHz

fmin=700.00KHz

则fmax/fmin=1.1

使用相位比较器PC2

(三)、N分频的设计

根据本次课程设计的要求,需设计一个N=7000-7999的分频计。通过方案的比较采用四块CD4522构成。CD4522是可预置数的二一十进制1/N减计数器。其引脚见附录。其中D1-D4是预置端,Q1—Q4是计数器输出端,其余控制端的功能如下:

PE(3)=1时,D1—D4值置进计数器EN(4)=0,且CP(6)时,计数器(Q1—Q4)减计数;CF(13)=1且计数器(Q1—Q4)减到0时,QC(12)=1 Cr(10)=1时,计数器清零。

3、拨动拨码盘,测输出频率

拨码盘

输出频率f(Hz)

输出波形

7000

700.00K

方波

7001

700.10K

方波

7051

705.10K

方波

7551

755.10K

基于LMX1501锁相环的频率合成设计

第 1期 1

电子元 器 件 主 用

El cr ni m p ne t& De c e to cCo o n vieApp iai s lc t on

Vo .0 No 1 I .1 1

NOV 008 .2

2 0 年 1 B 08 1

基于L 10锁相环 的频率合成设计 MX 5 1

1 L . 2 MX1O A的特 性及应 用 51

收 稿 1 :0 7 2 2 3期 2 0 —1 —1

者 1 819 。 2 /2 )

N 数 器 包 含 7 吞 咽计 数 器 ( 数 器)和 计 位 A计

1 位 可编 程 计 数器 ( 计 数 器) 1 B 。如果 输 入 的最后

一

11 H 输 入 频率 下 实 现6 /5 者 1 81 9 .G z 46 或 2 /2 除数 分 频 。L 1 0 A使 用 数 字锁 相 环 技 术 ,具 有 非 常 MX 5 1 稳 定 的线 性相 位检 测 特性 ,以及很 低 的本 振信 号

噪 声

1 81 9 2 /2 。如 果 控制 位 ( 低位 )为低 ,则 数 据信 最 号 被传 人N 数器 ( 计 可编程 除 数器) 。

0 引言

频率合 成 是从 一个 单 一频 率 的低频 晶体振 荡

器 中产生 多种 特别 精 确频 率 的一种 方 法 。在 大多

L MX10 A 定 频 率范 围最 高 为 1 H .工 5 1锁 .G z 1 作 电压为 2 — . V,3V时 的 电流 消耗 典 型值 为6 . 5 7 5

位控 制 数据位 为低 ,则数 据 பைடு நூலகம்1 位 移位 寄存 器 9

l 电 手元 器 件 盔 用 8

新型多功能锁相频率合成器lc7218的工作原理及其应用

新型多功能锁相频率合成器lc7218的工作原理及其应用在文章中,我会用从简到繁、由浅入深的方式来探讨新型多功能锁相频率合成器LC7218的工作原理及其应用。

我会多次提及该主题文字,并分享个人观点和理解。

文章将遵循知识的文章格式,包含总结和回顾性的内容,总字数大于3000字,不出现字数统计。

文章如下:新型多功能锁相频率合成器LC7218的工作原理及其应用一、简介新型多功能锁相频率合成器LC7218是一种集成了各种功能的电子元件,可以广泛应用于各种领域。

本文将从不同角度来探讨LC7218的工作原理及其应用。

二、LC7218的工作原理1. 时钟信号输入LC7218首先接收外部的时钟信号作为输入,通过内部的锁相环电路对时钟信号进行频率合成和同步处理。

2. 锁相环电路锁相环电路是LC7218内部的核心部分,它通过不断调整本身的输出频率和输入信号的频率,从而实现对输入信号的同步跟踪。

3. 频率合成在锁相环电路的控制下,LC7218可以对输入信号进行频率合成,产生稳定、精确的输出频率信号。

4. 输出控制LC7218还可以根据用户的需求,对输出信号进行控制和调节,以满足不同应用场景的要求。

三、LC7218的应用1. 通信系统在通信系统中,LC7218可以用于信号同步和频率合成,保证通信信号的稳定传输和接收。

2. 仪器仪表在各种仪器仪表中,LC7218可以用于时钟信号的同步和精确频率的输出,提高仪器的测量精度和稳定性。

3. 工业自动化在工业自动化领域,LC7218可以用于对各种控制信号的同步和精确频率输出,实现自动化生产和控制系统。

四、个人观点和理解个人认为,新型多功能锁相频率合成器LC7218的工作原理非常先进,应用范围广泛。

它不仅可以满足各种领域的需求,还可以提高系统的稳定性和精度。

在未来的发展中,LC7218有望成为各种电子系统中不可或缺的核心组件之一。

总结通过本文的介绍,我们对新型多功能锁相频率合成器LC7218的工作原理及其应用有了更深入的了解。

基于ADF4360—8的锁相环频率合成器的设计与实现

s y n he t s i z e r r e a c h e s 2 . 1 6 V( p e a k - p e a k ) , b e i n g a b l e t o d i r e c t i v e l y d r i v e t h e T T L c i r c u i t . T h e t e s t r e s u l t s s h o w t h a t

谢 亮 ,芦旭 ,吴成 英 。 ,杨 建青 ,樊战友

( 1 .中国科学院 国家授时 中心 ,西安 7 1 0 6 0 0 ; 2 .中国科学 院研究生 院 ,北京 1 0 0 0 3 9 ;

3 .湖北民族大学 ,恩施 4 4 5 0 0 0 )

摘要:为满足工程需要 ,设计并 实现 了一种基 于锁相环 芯片 A D F 4 3 6 0 — 8 的低噪声 高稳定度频率

he t o u t p u t s i g n a l s o f t h e r f e q u e n c y s y n he t s i z e r re a c h ra a c t e r i z e d b y g o o d s t a b i l i y, t l o w n o i s e a n d h i g h a mp l i t u d e .

XI E Li a n g 一, LU Xu 一, W U Che n g . yi n g , YAN G J i a n. q i n g , F AN Zh a n. yo u

f 1 . Na t i o n a l T i me S e r v i c e Ce n t e r , Ch i n e s eAc a d e my o f S c i e n c e s , Xi a l l 7 1 0 6 0 0 , Ch i n a ;

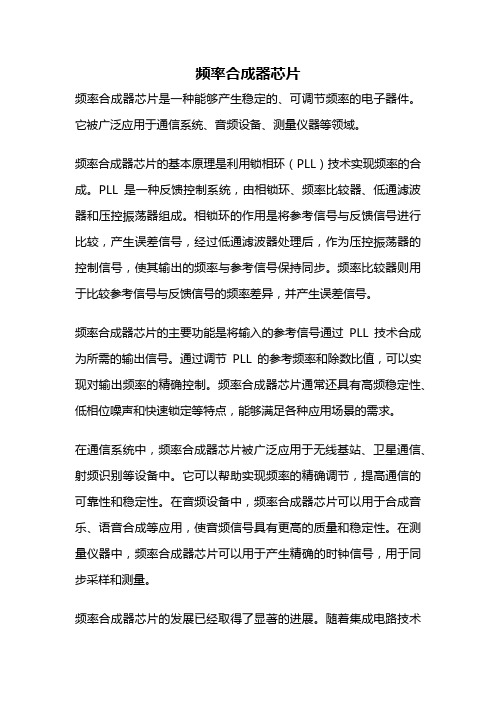

频率合成器芯片

频率合成器芯片频率合成器芯片是一种能够产生稳定的、可调节频率的电子器件。

它被广泛应用于通信系统、音频设备、测量仪器等领域。

频率合成器芯片的基本原理是利用锁相环(PLL)技术实现频率的合成。

PLL是一种反馈控制系统,由相锁环、频率比较器、低通滤波器和压控振荡器组成。

相锁环的作用是将参考信号与反馈信号进行比较,产生误差信号,经过低通滤波器处理后,作为压控振荡器的控制信号,使其输出的频率与参考信号保持同步。

频率比较器则用于比较参考信号与反馈信号的频率差异,并产生误差信号。

频率合成器芯片的主要功能是将输入的参考信号通过PLL技术合成为所需的输出信号。

通过调节PLL的参考频率和除数比值,可以实现对输出频率的精确控制。

频率合成器芯片通常还具有高频稳定性、低相位噪声和快速锁定等特点,能够满足各种应用场景的需求。

在通信系统中,频率合成器芯片被广泛应用于无线基站、卫星通信、射频识别等设备中。

它可以帮助实现频率的精确调节,提高通信的可靠性和稳定性。

在音频设备中,频率合成器芯片可以用于合成音乐、语音合成等应用,使音频信号具有更高的质量和稳定性。

在测量仪器中,频率合成器芯片可以用于产生精确的时钟信号,用于同步采样和测量。

频率合成器芯片的发展已经取得了显著的进展。

随着集成电路技术的不断发展,芯片的尺寸不断缩小,功耗不断降低,性能不断提高。

现代的频率合成器芯片已经具备了更高的工作频率、更低的相位噪声和更快的锁定时间。

同时,频率合成器芯片也在不断扩展其功能,例如加入了数字信号处理功能,可以实现更复杂的频率合成和调制。

然而,频率合成器芯片也面临一些挑战和限制。

由于其工作原理的特殊性,频率合成器芯片对输入信号的稳定性和纯度要求较高。

同时,频率合成器芯片的设计和制造也需要考虑功耗、面积和成本等因素。

因此,在设计和选择频率合成器芯片时,需要综合考虑各种因素,以满足具体应用的需求。

频率合成器芯片是一种重要的电子器件,它能够产生稳定的、可调节频率的信号,在通信、音频和测量等领域发挥着重要作用。

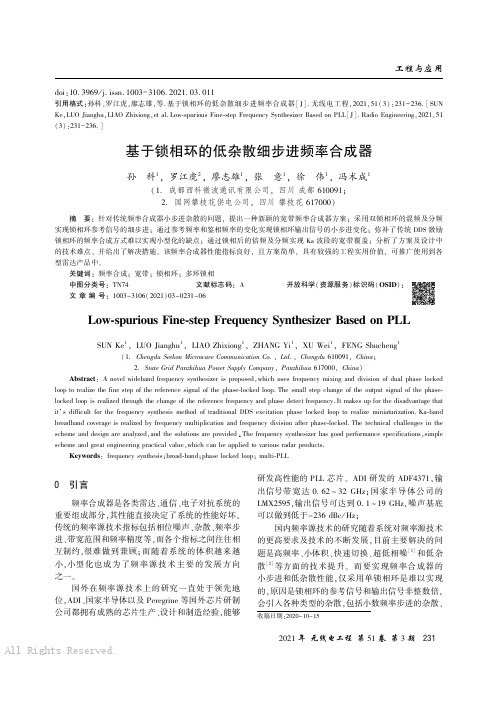

基于锁相环的低杂散细步进频率合成器

2021年无线电工程第51卷第3期231 doi:10.3969/j.issn.1003-3106.2021.03.011引用格式:孙科,罗江虎,廖志雄,等.基于锁相环的低杂散细步进频率合成器[J].无线电工程,2021,51(3):231-236.[SUNKe,LUO Jianghu,LIAO Zhixiong,et al.Low⁃spurious Fine⁃step Frequency Synthesizer Based on PLL[J].Radio Engineering,2021,51(3):231-236.]基于锁相环的低杂散细步进频率合成器孙 科1,罗江虎2,廖志雄1,张 意1,徐 伟1,冯术成1(1.成都西科微波通讯有限公司,四川成都610091;2.国网攀枝花供电公司,四川攀枝花617000)摘 要:针对传统频率合成器小步进杂散的问题,提出一种新颖的宽带频率合成器方案;采用双锁相环的混频及分频实现锁相环参考信号的细步进;通过参考频率和鉴相频率的变化实现锁相环输出信号的小步进变化;弥补了传统DDS 激励锁相环的频率合成方式难以实现小型化的缺点;通过锁相后的倍频及分频实现Ka 波段的宽带覆盖;分析了方案及设计中的技术难点,并给出了解决措施。

该频率合成器性能指标良好,且方案简单,具有较强的工程实用价值,可推广使用到各型雷达产品中。

关键词:频率合成;宽带;锁相环;多环锁相中图分类号:TN74文献标志码:A 开放科学(资源服务)标识码(OSID ):文章编号:1003-3106(2021)03-0231-06Low⁃spurious Fine⁃step Frequency Synthesizer Based on PLLSUN Ke 1,LUO Jianghu 1,LIAO Zhixiong 1,ZHANG Yi 1,XU Wei 1,FENG Shucheng 1(1.Chengdu Seekon Microwave Communication Co.,Ltd.,Chengdu 610091,China ;2.State Grid Panzhihua Power Supply Company ,Panzhihua 617000,China )Abstract :A novel wideband frequency synthesizer is proposed,which uses frequency mixing and division of dual phase lockedloop to realize the fine step of the reference signal of the phase⁃locked loop.The small step change of the output signal of the phase⁃locked loop is realized through the change of the reference frequency and phase detect frequency.It makes up for the disadvantage that it’s difficult for the frequency synthesis method of traditional DDS excitation phase locked loop to realize miniaturization.Ka⁃bandbroadband coverage is realized by frequency multiplication and frequency division after phase⁃locked.The technical challenges in the scheme and design are analyzed,and the solutions are provided The frequency synthesizer has good performance specifications,simple scheme and great engineering practical value,which can be applied to various radar products.Keywords :frequency synthesis;broad⁃band;phase locked loop;multi⁃PLL收稿日期:2020-10-150 引言频率合成器是各类雷达、通信、电子对抗系统的重要组成部分,其性能直接决定了系统的性能好坏,传统的频率源技术指标包括相位噪声、杂散、频率步进、带宽范围和频率精度等,而各个指标之间往往相互制约,很难做到兼顾;而随着系统的体积越来越小,小型化也成为了频率源技术主要的发展方向之一。

锁相环频率合成器原理

锁相环频率合成器原理锁相环频率合成器是一种广泛应用于无线通信系统和频率合成器中的电路。

它通过将输入信号的频率锁定到参考信号的频率上,实现对输入信号频率的稳定和精确控制。

锁相环频率合成器的原理是基于负反馈控制和锁相环电路。

锁相环频率合成器由三个主要组成部分组成:相位比较器、低通滤波器和电压控制振荡器。

首先,锁相环的参考信号和输入信号都被送入相位比较器。

相位比较器会将两个信号的相位进行比较,并输出相位差。

相位差是参考信号和输入信号之间相位的差异值。

接下来,相位差信号通过低通滤波器进行滤波,目的是消除高频噪声。

滤波器的作用是确保锁相环的输出信号是稳定的且没有抖动的。

经过滤波的相位差信号进入电压控制振荡器(VCO),VCO根据输入信号的相位差来调整自身的输出频率。

如果输入信号的频率低于参考信号的频率,那么相位差将是正值,VCO将增加输出频率。

如果输入信号的频率高于参考信号的频率,相位差将是负值,VCO将减小输出频率。

最后,VCO的输出信号通过反馈回路连接到相位比较器,与输入信号进行反馈。

这个反馈迫使VCO的输出频率与参考信号的频率越来越接近,最终达到精确的锁定。

锁相环频率合成器在无线通信系统中的应用非常广泛。

在接收方面,锁相环可以用于从复杂多路径传输的信号中恢复出原始信号,消除传播路径引起的相位偏差。

在发射方面,锁相环可以用于产生稳定的射频信号,通过倍频器和滤波器将原始频率倍增,然后放大后用于无线电通信。

此外,锁相环频率合成器还被广泛应用于频率合成器中,用于产生非常精确的时钟信号,以供数字电路和通信设备使用。

总结起来,锁相环频率合成器是一种将输入信号的频率锁定到参考信号的频率上的电路。

它通过相位比较、滤波和VCO调频的方式实现对输入信号频率的稳定和精确控制。

锁相环频率合成器在无线通信系统和频率合成器中有着广泛的应用,能够提供稳定的射频信号和精确的时钟信号,为无线通信技术的发展提供了重要支持。

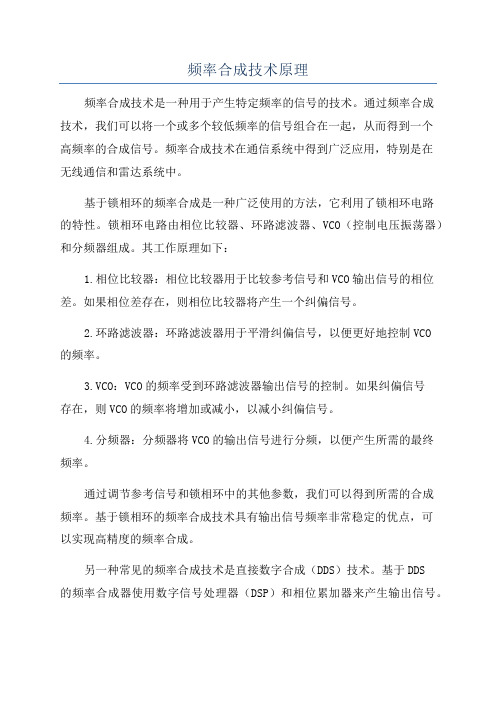

频率合成技术原理

频率合成技术原理频率合成技术是一种用于产生特定频率的信号的技术。

通过频率合成技术,我们可以将一个或多个较低频率的信号组合在一起,从而得到一个高频率的合成信号。

频率合成技术在通信系统中得到广泛应用,特别是在无线通信和雷达系统中。

基于锁相环的频率合成是一种广泛使用的方法,它利用了锁相环电路的特性。

锁相环电路由相位比较器、环路滤波器、VCO(控制电压振荡器)和分频器组成。

其工作原理如下:1.相位比较器:相位比较器用于比较参考信号和VCO输出信号的相位差。

如果相位差存在,则相位比较器将产生一个纠偏信号。

2.环路滤波器:环路滤波器用于平滑纠偏信号,以便更好地控制VCO的频率。

3.VCO:VCO的频率受到环路滤波器输出信号的控制。

如果纠偏信号存在,则VCO的频率将增加或减小,以减小纠偏信号。

4.分频器:分频器将VCO的输出信号进行分频,以便产生所需的最终频率。

通过调节参考信号和锁相环中的其他参数,我们可以得到所需的合成频率。

基于锁相环的频率合成技术具有输出信号频率非常稳定的优点,可以实现高精度的频率合成。

另一种常见的频率合成技术是直接数字合成(DDS)技术。

基于DDS的频率合成器使用数字信号处理器(DSP)和相位累加器来产生输出信号。

1.相位累加器:相位累加器是一个数字计数器,用于累加一个固定的相位步进值。

这个相位步进值由控制器传递给相位累加器,并决定了输出信号的频率。

2.数字信号处理器:DSP接收相位累加器的输出,并使用一种数学公式将其转换为合成频率的数字表示。

该数字信号随后通过数字模拟转换器(DAC)转换为模拟信号。

3.数字模拟转换器:DAC将数字表示的信号转换为模拟信号,该信号经过滤波器以消除数字转换过程中引入的噪声和失真。

基于DDS的频率合成技术具有输出频率范围广、相位和频率调节较灵活等优点。

然而,由于其使用了数字信号处理器,因此在高频率合成时可能会受到时钟频率的限制。

总的来说,频率合成技术是一种通过组合较低频率信号以产生特定频率的信号的方法。

集成电路课程设计——锁相环CD4046设计频率合成器

集成电路课程设计一-锁相环CD4046设计频率合成器学号:110800316 姓名:苏毅坚指导老师:罗国新2011年1月锁相环CD4046设计频率合成器实验目的:设计一个基于锁相环CD4046设计频率合成器范围是10k〜100K,步进为1K设计和制作步骤:确定电路形式,画出电路图。

计算电路元件参数并选取元件O组装焊接电路。

调试并测量电路性能。

确定电路组成方案原理框图如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N,从而就得到N倍参考频率的稳定输出。

晶体振荡器输出的信号频率n,经固定分频后(M分频)得到基准频率fi,,输入锁相环的相位比较器(PC)。

锁相环的VCO输出信号经可编程分频器(N分频)后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到:n/M=fF=f2/N 故f2=N『l (Fl为基准频率)当N变化时,就可以得到一系列的输出频率f2o设计方法(一)、振荡源的设计用CMOS与非门和1M晶体组成1MHz振荡器,如图14。

图中Rf使F1工作于线性放大区。

晶体的等效电感,Cl> C2构成谐振回路。

C1、C2可利用器件的分布电容不另接。

Fl、F2、F3 使用CD4049o(二)、N分频的设计N分频采用CD40103进行分频。

CD40103是BCD码8位分频器。

采用8位拨码开关控制分频大小。

输入的二进制大小即为分频器N分频。

图中RP1为1K排阻(三)、1KHZ标准信号源设计(即M分频的设计)根据4518的输出波形图,可以看出4518包含二分频、四分频、十分频,用二片CD4518 (共4个计数器)组成一个1000分频器,也就是三个十分频器,这样信号变为2Khz.再经过双D触发器,这样就可把2MHz的晶振信号变成500hz 的标准信号。

如下图所示:(四)4046锁相环的设计锁相环4046为主芯片。

电路图如下:500Hz信号从14脚输入。

3脚4脚接N分频电路,即40103分频电路。

基于ADF4106的锁相环频率合成器

1 引言在无线通信领域中,高性能频率源是通信设备、雷达、电子侦察和对抗设备、精密测量仪器的核心部件。

现代通信系统对频率源的精度、分辨率、转换时间及频谱纯度等提出了越来越高的要求,性能卓越的频率源均通过频率合成技术来实现。

本文所讨论的锁相环频率合成技术是基于锁相环路的同步原理,由一个高准确度、高稳定度的参考晶体振荡器,综合出大量离散频率的一种技术。

锁相环频率合成器是一种相位锁定装置,是一种频率稳定度较高的离散间隔型频率信号发生器。

2 锁相环频率合成器的基本原理锁相环是频率合成技术的基础。

锁相环路(PLL)通常由鉴相器(PD)、环路滤波器(LP)、压控振荡器(VCO)和可变程序分频器组成。

锁相环路是一个相位误差控制系统,它比较输入信号与压控振荡器输出信号之间的相位差,产生一个对应于两个信号相位差的误差电压,该误差电压经处理后去调整压控振荡器的频率(相位)。

当环路锁定时,输入信号与压控振荡器输出信号频差为零,相位差不再随时间变化,此时,误差控制电压为一固定值,压控振荡器输出频率与输入信号频率相等,即fo=fr。

锁相环路的这一特点,使它在自动频率控制中得到应用,以实现精确的频率控制。

环路在锁定时要得到一定的控制电压,则鉴相器必须有一个非零的输出,即,环路作用必须有相位差,相位差维持着两信号的同步,使输出信号频率稳定。

锁相环基本原理方框图如图1所示。

鉴相器又称比相器,对输入信号与环路输出信号的相位进行比较, 产生误差控制电压;环路滤波器滤除误差电压中的高频分量和噪声,以保证环路所要求的性能,增加环路的稳定性;压控振荡器的振荡频率受环路滤波器输出电压的控制,使压控振荡器输出信号频率向输入信号频率靠拢,两个信号间的相位差减小。

可变程序分频器的作用是使压控振荡器的输出频率经分频后再与参考频率进行相位比较,从而产生误差控制电压,并以误差控制电压来调整压控振荡器的相位。

锁相环路对高稳定度的参考振荡器(通常是晶体振荡器)锁定,环路串接可编程的程序分频器,通过编程改变程序分频器的分频比R、N,从而获得N/R倍参考频率的稳定输出。

可调有源分频器的设计与实现参考文献

可调有源分频器的设计与实现参考文献

在基于锁相环的频率合成器中,压控振荡器和分频器是决定其工作频率的主要模块。

为满足高频通信的需求,需要对这两个模块进行高速和低功耗的优化设计。

一般情况下,采用两种方法来改善电路的性能:一是改进工艺,二是优化电路结构。

频率合成器中的分频器模块包括双模分频器、可编程计数器、小数分频器等。

分频器的结构很多,主要可分为模拟分频器和数字分频器两种。

前者能提供的分频比有限,而后者能提供多种复杂的分频比。

在宽带多通道高速频率合成器的设计中,一般选择基于触发器实现的数字分频器。

工作频率在GHz以上的高速触发器,主要有以下两种结构:

第一种是源级耦合型(Source Couple Logic, SCL)结构,由于电路摆幅较小,因而工作速度较快,且功耗和噪声都比较低。

典型的SCL结构电路包括尾管电流源,由于晶体管无法做到小尺寸,导致输入电容很大,所以需要在SCL 分频电路中加入缓冲电路。

第二种是真单相时钟(True Single Phase Clocked, TSPC)结构,典型的结构是9管D触发器。

构成该电路结构的元件数目较少,因而电路的工作速度较快,且这种电路的功耗极低,故常在前置分频器中使用。

由于TSPC触发器是动态的单端输入结构,因而抗噪性能要低于差分输入结构的SCL触发器,另外论文网,TSPC触发器的输入信号需要很大的摆幅,否则无法正常分频。

近几年,根据不同的应用,出现许多基于上述触发器的改进结构。

在对数字

分频器的设计中,触发器的选择通常是考虑的重点,需要对频率范围、功耗、信号幅度等因素进行折中。

频率合成器设计

题目:频率合成器——基于4046的锁相环频率合成器一、课程设计目的:1.熟悉期间4046的基本原理和性能。

2.掌握频率合成器的原理和合成技术。

3.熟悉和掌握所学的各个器件,芯片,以及熟练的应用。

4.理解入锁和失锁的概念和原理。

5.融会贯通所学的高频知识,能够灵活的应用和设计。

6.理解和熟练分析基本的电路。

二、课程设计题目描述和要求:频率合成是以一个或少量的高准确度和高稳定度的标准频率作为参考频率,由此导出多个或大量的输出频率,这些输出的准确度与稳定度与参考频率是一致的。

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成。

频率合成器有直接式频率合成器、直接数字式频率合成器及锁相频率合成器三种基本模式,前两种属于开环系统,因此是有频率转换时间短,分辨率较高等优点,而锁相频率合成器是一种闭环系统,其频率转换时间和分辨率均不如前两种好,但其结构简单,成本低。

并且输出频率的准确度不逊色与前两种,因此采用锁相频率合成。

频率合成器是一个系统,最初产生的一系列频率为参考频率的整数倍,参考频率通常是固定的。

这样的合成器称为整数N频率合成器。

频率合成器技术也不断前进,出现也很多新型的频率合成电路,并在通信电路中得到广泛应用。

锁相环由鉴相器、环路滤波器和压控振荡器组成。

频率合成一个或少量的高准确度高稳定的标准频率作为参考频率,由此导出多个或大量的输出频率.这些输出频率的准确度和稳定度与参考频率是一致的,频率合成器就是用来产生这些频率的部件.技术要求:1.达到输出为4-10M赫兹。

2.频率间隔为5K 赫兹。

3.基于4046芯片的设计。

三、课程设计报告内容及原理:原理框图如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N ,从而就得到N 倍参考频率的稳定输出。

快电子期末50题参考答案

快电⼦期末50题参考答案快电⼦学 Questions 解答1.模拟信号转化为数字信号要实现时间轴上的离散化和幅度上的量化,请简要叙述根据被采样信号的特点如何从上述两个⽅⾯来选择合适的ADC?答:由于采样速率≤ADC转换速率,ADC按信号采样率即时间轴上的离散化程度可选择:快闪型(flash)、流⽔线型(pipelined)、Σ-Δ型、逐次⽐较型(SAR)、积分型。

其中积分型速度最慢,适合采样率低的信号。

根据幅度上的量化即按分辨率选择,由⾼到低有:Σ-Δ型、逐次⽐较型(SAR)、流⽔线型(pipelined)、积分型、快闪型(flash)2.简述量化噪声的特点?它与ADC 的分辨率有何关系?答:如果采样频率满⾜采样定理,则量化是A/D转换过程的唯⼀误差来,源它会使ADC分辨率变差3.简述Nyquist 采样定理?答:4.量化噪声与被采信号的RMS 值有何关系?如何调理被采信号和ADC 的输⼊动态范围适配?答:(RMS值即均⽅根)信噪⽐5.在信号采样——处理——信号重建过程中,防混叠滤波器和信号重建滤波器应处在什么位置?分别有何作⽤?答:可见防混叠滤波器应在采样之前,信号重建滤波器应在数字信号处理之后;防混叠滤波器可确保采样后不出现混叠现象,信号重建滤波器可由离散信号恢复出连续时间信号。

6.什么是ZOH 波形重建?ZOH 重建器中的信号重建滤波器理论上应该具有什么特点?答:利⽤ZOH滤波器进⾏波形重建,其脉冲响应为,频率域为;理论上应具有低频部的幅度响应平坦、⽆⾼频响应、线性相位的特点。

7.说明逐次逼近型ADC(Successive-approximation ADC)的原理和特点?逐次⽐较型AD由⼀个⽐较器和DA转换器通过逐次⽐较逻辑构成,从MSB开始,顺序地对每⼀位将输⼊电压与内置DA转换器输出进⾏⽐较,经n次⽐较⽽输出数字值。

特点:仅包括⼀个⽐较器,⼀个DAC,⼀个SAR和⼀个逻辑控制单元⼯作采⽤频率1MSPS,功耗⼩,成本低模拟设计强,输⼊带宽低,采样率低8.说明积分型ADC(Integration ADC)的原理和特点?将输⼊电压转换成时间(脉冲宽度信号)或频率(脉冲频率),然后由定时器/计数器获得数字值积分器对输⼊电压积分⼀个固定时间间隔,结束后将积分器切换到和输⼊信号极性相反的参考电压上,放电直⾄输出为0.电路简单,速率⾮常慢,输⼊带宽低、可以去除⾼频噪声9.说明流⽔线ADC(Pipeline ADC,Sub-ranging ADC)的原理和特点?原理特点10.画出基于1.5bit/Stage 的四级Pipeline ADC 的原理⽰意图,其中的数字校正处理的作⽤是什么?上图中m=1.5,N=4。

锁相 频率源

锁相频率源

锁相频率源是一种用于产生稳定、精确频率信号的设备。

它在许多科学研究和工程应用中起到至关重要的作用。

本文将介绍锁相频率源的原理、应用和发展趋势。

一、原理

锁相频率源是基于锁相环原理的一种频率合成器。

锁相环是一种负反馈控制系统,它通过比较输入信号和参考信号的相位差,调节输出信号的频率和相位,使其与参考信号同步。

锁相频率源的核心元件是锁相环电路,它由相位比较器、低通滤波器、电压控制振荡器和频率除法器等组成。

二、应用

锁相频率源广泛应用于各个领域。

在精密测量和实验中,锁相频率源常用于产生稳定的参考信号,用于同步数据采集、激光干涉测量等。

在通信系统中,锁相频率源可以提供高稳定度的时钟信号,保证数据传输的可靠性。

在雷达和卫星导航系统中,锁相频率源被用于精确测量距离和速度。

此外,锁相频率源还可以用于频率合成、信号调制和解调等应用。

三、发展趋势

随着科技的不断进步,锁相频率源的性能和应用领域也在不断扩展。

目前,研究人员正在努力提高锁相频率源的频率稳定度、相位噪声和调制带宽。

同时,他们也在探索新的锁相环拓扑结构和优化算法,

以提高锁相频率源的性能。

此外,随着微纳技术的发展,锁相频率源正朝着小型化、集成化和高度可靠化的方向发展。

总结:

锁相频率源是一种重要的频率合成器,它通过锁相环原理实现稳定、精确的频率输出。

锁相频率源在精密测量、通信系统、雷达和卫星导航等领域具有广泛的应用。

随着科技的进步,锁相频率源的性能和应用领域正在不断扩展,未来可期。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

综合课程设计频率合成器的设计与仿真前言现代通信系统中,为确保通信的稳定与可靠,对通信设备的频率准确率和稳定度提出了极高的要求. 随着电子技术的发展,要求信号的频率越来越准确和越来越稳定,一般的振荡器已不能满足系统设计的要求。

晶体振荡器的高准确度和高稳定度早已被人们认识,成为各种电子系统的必选部件。

但是晶体振荡器的频率变化范围很小,其频率值不高,很难满足通信、雷达、测控、仪器仪表等电子系统的需求,在这些应用领域,往往需要在一个频率范围内提供一系列高准确度和高稳定度的频率源,这就需要应用频率合成技术来满足这一需求。

本次实验利用SystemView实现通信系统中锁相频率合成器的仿真,并对结果进行了分析。

一、频率合成器简介频率合成是指以一个或少量的高准确度和高稳定度的标准频率作为参考频率,由此导出多个或大量的输出频率,这些输出频率的准确度与稳定度与参考频率是一致的。

用来产生这些频率的部件就成为频率合成器或频率综合器。

频率合成器通过一个或多个标准频率产生大量的输出频率,它是通过对标准频率在频域进行加、减、乘、除来实现的,可以用混频、倍频和分频等电路来实现。

其主要技术指标包括频率范围、频率间隔、准确度、频率稳定度、频率纯度以及体积、重量、功能和成本。

频率合成器的合成方法有直接模拟合成法、锁相环合成法和直接数字合成法。

直接模拟合成法利用倍频、分频、混频及滤波,从单一或几个参数频率中产生多个所需的频率。

该方法频率转换时间快(小于100ns),但是体积大、功耗大,成本高,目前已基本不被采用。

锁相频率合成器通过锁相环完成频率的加、减、乘、除运算,其结构是一种闭环系统。

其主要优势在于结构简化、便于集成,且频率纯度高,目前广泛应用于各种电子系统。

直接式频率合成器中所固有的那些缺点,在锁相频率合成器中大大减少。

本次实验设计的是锁相频率合成器。

二、锁相环频率合成器原理2.1 锁相环路设计基础这一部分首先阐明了锁相环的基本原理及构成,导出了环路的相位模型和基本方程,概述了环路的工作过程, 2.1.1锁相环基本原理锁相环(PLL )是一个相位跟踪系统。

最基本的锁相环方框图如图1所示。

它包括三个基本部件,鉴相器(PD ) 环路滤波器(LF )和压控振荡器(VCO )图1 锁相环的基本构成设参考信号()sin[()]r r r r u t U t t ωθ=+ (1)式中 Ur 为参考信号的幅度 ωr 为参考信号的载波角频率θr (t)为参考信号以其载波相位ωr t 为参考时的瞬时相位 若参考信号是未调载波时,则θr (t)= θ1=常数。

设输出信号为 0()cos[()]o o o u t U t t ωθ=+ (2) 式中 U o 为输出信号的振幅,ω0为压控振荡器的自由振荡角频率θ0 (t)为参考信号以其载波相位ω0t 为参考时的瞬时相位, 在VCO 未受控制 它是常数,受控之后他是时间函数。

则两信号之间的瞬时相位差为0000()(())(())()()e r r r r t t t t t θωθωθωωθθ=+-+=-+- (3)由频率和相位之间的关系可得两信号之间的瞬时频差为(4)鉴相器是相位比较器,它把输出信号u o (t)和参考信号u r (t)的相位进行比较,()()e r d t d t dtdtθθωω=--产生对应于两信号相位差θe (t)的误差电压u d (t)。

环路滤波器的作用是滤除误差电压u d (t)中的高频成分和噪声,以保证环路所要求的性能,提高系统的稳定性。

压控振荡器受控制电压u c (t )的控制,u c (t)使压控振荡器的频率向参考信号的频率靠近,于是两者频率之差越来越小,直至频差消除而被锁定。

因此,锁相环的工作原理可简述如下:首先,鉴相器把输出信号u o (t)和参考信号u r (t)的相位进行比较,产生一个反应两信号的相位差θe (t)大小的误差电压u d (t),u d (t)经过环路滤波器的过滤得到控制电压u c (t)。

u c (t)调整VCO 的频率向参考信号的频率靠拢,直至最后两者频率相等而相位同步实现锁定。

锁定后两信号之间的相位差表现为一固定的稳态值。

即(5)此时,输出信号的频率已偏离了原来的自由频率ω0[控制电压u c (t)=0时的频率],其偏移量由式(4)和式(5)得到为这时输出信号的工作频率已变为00()(())c c r d t dt t dt dtθωθωω+=+= (6) 由此可见,通过锁相环路的相位跟踪作用,最终可以实现输出信号与参考信号同步,两者之间不存在频差而只存在很小稳态相差。

2.1.2 基本环路方程为了建立锁相环路的数学模型,首先建立鉴相器、环路滤波器、压控振荡器的数学模型。

1. 鉴相器鉴相器(PD)又称相位比较器,它是用来比较两个输出信号之间的相位差 θe (t)。

鉴相器输出的误差信号u d (t)是相差θe (t)的函数。

鉴相器按其鉴相特性分为正弦型,三角形和锯齿波形。

作为原理分析,通常使用正弦型,较为典型的正弦鉴相器可用模拟乘法器与低通滤波器的串接构成。

其模型如图2所示:()lim 0e t d t dtθ→∞=00()r d t dtθωω=-图2 正弦鉴相器模型若以压控振荡器的载波相位ω0t 作为参考,讲输出信号u 0(t)与参考信号u r (t)变形,有:0002()cos[()]u t U t t ωθ=+01()sin[()]sin[()]r r r r r u t U t t U t t ωθωθ=+=+式中,θ2 (t)= θ0 (t),100()()()()r r r t t t t t t θωωθωθ=++=∆+将u 0(t)与u r (t)相乘,滤波2ω0分量,可得:12()sin[()()]()d d d e u t U t t U t θθθ=-=式中,U d (t)= K m U r U o /2,K m 为相乘器的相乘系数,单位为[1/V],U d 越大,在同样的θe (t)下,鉴相器的输出就越大。

因此,U d 在一定程度上反映了鉴相器的灵敏度。

θe (t)= θ1 (t)- θ2 (t)为相乘器输入电压的瞬时相位差。

下图是正弦鉴相器的数学模型和鉴相特性。

图3 正弦鉴相器的数学模型图4 正弦鉴相器的鉴相特性)2.环路滤波器环路滤波器(LF )是一个线性低通滤波器,用来滤除误差电压u d (t)中的高频分量和噪声,更重要的是它对环路参数调整起到决定性作用。

环路滤波器由线性原件电阻、电容、和运算放大器组成。

它是一个线性系统。

常用的环路滤波器有RC 积分滤波器、无源比例积分滤波器和有源积分滤波器三种。

下面以介绍有源比例积分滤波器为主。

有源比例积分滤波器有源比例积分滤波器由运算放大器组成。

当运放器开环电压增益A 为有限值时,它的传递函数为(7)式中'111222();R AR R C R C ττ=++=由图5可见,它也具有低通特性与比例作用。

相频特性也有超前校正的作用。

图5 有源比例积分滤波器及其特性3.压控振荡器压控振荡器(VCO )是一个电压-频率变换器,再换路政作为被控振荡器,它的振荡频率应随输入控制电压u c (t)的线性的变化,即(8)式中ωv (t)是VCO 的瞬时角频率,K 0是线性特性斜率,表示单位控制电压,可使VCO 角频率变化的数值。

因此又称为VCO 的控制灵敏度与增益系数,单位为[/rad s v •].在锁相环路中,VCO 的输出对鉴相器起作用的不是瞬时角频率,R 20(a )21()1()()1c d U s s F s A U s s ττ+==-'+0()()v d c t k u t ωω=+而是瞬时相位,即12()()()c t t t θθθ=-(9)将此式与u o (t )=U o cos [ω0t +θ2(t )],比较,可以知ω0t 为参考时的输出瞬时相位为2()sin ()()dd e K t U t F p pθθ= (10) 由此可见,VCO 在锁相环中起了一次积分作用,因此也称他为环路中的固有积分环节。

上式就是压控振荡器相位控制的模型,若对上式进行拉氏变换,可得到在复频域的表示式为VCO 的传递函数为 (11)下图为VCO 的复频域的数学模型。

图6 VCO 的复频域模型2.1.3 环路相位模型和基本方程上面分别得到了鉴相器,环路滤波器和压控振荡器的模型,将三个模型连接起来,就可以得到锁相环路的模型。

如下图7所示图7 锁相环路相位模型复时域分析时可用一个传输算子F(p)来表示。

其中(p=d/dt )是微分算子。

由22()()()cddc Us k ss k U s sθθ==上图可以得出锁相环路的基本方程。

(12) (13)将(9)代入(8)得(14) 设环路输入一个频率ωr 和相位θr 均为常数的信号,即式中,ω0是控制电压u c (t)=0时VCO 的固有振荡频率,θr 是参考输入信号的相位。

令则 (15) 将式(11)代入式(10)可得固有频率输入时的环路基本方程(16) 在闭环之后的任何时刻存在着如下关系:瞬时频差=固有频差-控制频差,记为0()v ωωω∆=∆-∆,即00()()r v r v ωωωωωω-=--- 2.1.4 锁相环工作过程的定性分析式(12)是锁相环路的基本方程,求解此方程,就可以获得锁相环路的各种性能指标,如锁定、跟踪、捕获、失锁等。

但要严格的求解基本方程式往往是比较困难的。

式中已认为压控振荡器的控制为线性,但因鉴相特性的非线性,基本方程是非线性方程。

又因为压控振荡器的固有积分作用,基本方程至少是一阶非线性微分方程。

若在考虑环路滤波器的积分作用,方程可能是高阶的。

1.锁定状态当在环路作用下,调整控制频差等于固有频差时,瞬间相差θe (t)趋向于一个固定值,并一直保持下去,即满足(17)此时认为锁相环路进入锁定状态。

2.跟踪过程122()()()()sin ()()c dd e t t t Kt U t F p pθθθθθ=-=101()()sin ()()()sin ()()e d e e p t p t K U t F p p t K t F p θθθθθ=-=-00()sin[]sin[()r r r r r r ru t U t U t t ωθωωωθ=+=+-+10100()()()r rr t t p t θωωθθωωω=-+=-=∆00()sin ()()e d e p t K U t F p θωθ=∆-lim ()0e t p t θ→∞=跟踪是在锁定的前提下,输入参考频率和相位在一定的范围内,以一定的速率发生变化时,输出信号的信号与相位以同样的规律跟随变化,这一过程称为环路的跟踪过程。