半导体制程概论

图解半导体制程概论1.

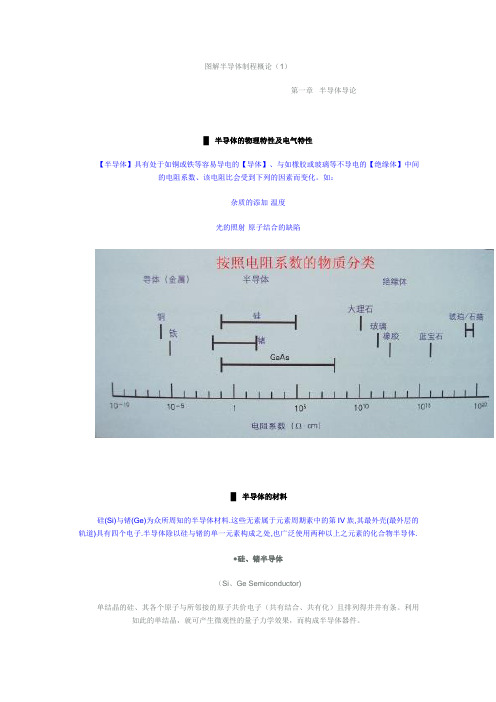

图解半导体制程概论(1)第一章半导体导论█半导体的物理特性及电气特性【半导体】具有处于如铜或铁等容易导电的【导体】、与如橡胶或玻璃等不导电的【绝缘体】中间的电阻系数、该电阻比会受到下列的因素而变化。

如:杂质的添加·温度光的照射·原子结合的缺陷█半导体的材料硅(Si)与锗(Ge)为众所周知的半导体材料.这些无素属于元素周期素中的第IV族,其最外壳(最外层的轨道)具有四个电子.半导体除以硅与锗的单一元素构成之处,也广泛使用两种以上之元素的化合物半导体.●硅、锗半导体(Si、Ge Semiconductor)单结晶的硅、其各个原子与所邻接的原子共价电子(共有结合、共有化)且排列得井井有条。

利用如此的单结晶,就可产生微观性的量子力学效果,而构成半导体器件。

●化合物半导体(Compound Semiconductor)除硅(Si)之外,第III族与第V族的元素化合物,或者与第IV族元素组成的化合物也可用于半导体材料。

例如,GaAs(砷化镓)、Gap(磷化砷)、AlGaAs(砷化镓铝)、GaN(氮化镓)SiC(碳化硅)SiGe(锗化硅)等均是由2个以上元素所构成的半导体。

█本征半导体与自由电子及空穴我们将第IV族(最外层轨道有四个电子)的元素(Si、Ge等),以及和第IV族等价的化合物(GaAs、GaN等),且掺杂极少杂质的半导体的结晶,称之为本征半导体(intrinsic semiconductor)。

●本征半导体(intrinsic semiconductor)当温度十分低的时候,在其原子的最外侧的轨道上的电子(束缚电子(bound electrons)用于结合所邻接的原子,因此在本征半导体内几乎没有自由载子,所以本征半导体具有高电阻比。

●自由电子(free electrons)束缚电子若以热或光加以激发时就成为自由电子,其可在结晶内自由移动。

●空穴(hole)在束缚电子成为自由电子后而缺少电子的地方,就有电子从邻接的Si原子移动过来,同时在邻接的Si原子新发生缺少电子的地方,就会有电子从其所邻接的Si原子移动过来。

半导体中段制程-概述说明以及解释

半导体中段制程-概述说明以及解释1.引言1.1 概述概述半导体中段制程是半导体制造过程中的一个重要阶段。

在半导体制造过程中,通常将整个过程分为前段制程、中段制程和后段制程三个阶段。

中段制程是在前段制程完成后,将晶圆表面的介电层、金属层等进行加工和处理的阶段。

在中段制程中,主要涉及到的工艺包括光刻、沉积、刻蚀、清洗等步骤。

光刻是中段制程中的重要步骤之一。

它通过使用光刻胶和掩模光罩,将光刻胶涂覆在晶圆表面上,并通过紫外光照射,将掩模上的图形转移到光刻胶上。

然后,通过化学处理,将光刻胶上未曝光部分或曝光后进行过浸蚀、清洗等处理,最终形成所需的图案。

沉积是中段制程中另一个重要的步骤。

它主要是将金属、介电材料等沉积在晶圆表面,形成所需的层。

常用的沉积方法包括物理气相沉积(PVD)、化学气相沉积(CVD)等,根据不同的材料和需求,选择适合的沉积方法。

刻蚀是中段制程的一项关键步骤,它通过使用化学气相或物理方法,将不需要的材料层进行去除或定义。

刻蚀方法包括湿法刻蚀、干法刻蚀等,根据材料的不同选择不同的刻蚀方式。

清洗是中段制程中不可或缺的一步。

它的主要目的是去除杂质、残留物以及刻蚀产物,保证晶圆表面的纯净度和平整度。

清洗过程主要包括超声清洗、化学清洗等方法。

总之,半导体中段制程是半导体制造过程中至关重要的一步。

通过精确的加工和处理,可以实现对晶圆表面的图案形成和层之间的连接,为后续的工艺步骤打下坚实的基础。

在不断发展的半导体技术中,中段制程的优化和改进对于提高半导体器件的性能和可靠性具有重要意义。

1.2 文章结构文章结构部分的内容可以包括以下内容:在本篇长文中,我们将对半导体中段制程进行详细的探讨和分析。

文章分为引言、正文和结论三个部分。

引言部分首先对半导体中段制程进行概述,包括其定义、作用以及在半导体工业中的重要性。

接着,介绍文章的结构和目的,以及本文所要探讨的主要内容。

正文部分将分为两个要点来详细讨论半导体中段制程。

图解光电半导体制程概论.

• 激光半导体的动作和使用方法 • 激光半 体也被称为“激光二极管”(Leser Diode).激光是一种通过 诱导放出来将光放大的器件。而发出人眼可以识别的波长的叫做 VLD(Visible Laser Diode). • 动作原理 • 激光半导体(LD与LED不同,不是由注入的少数载子简单地重新结合 起来,而是由于光的刺激而再结合起来,发出相位一致的光 来)。 而且,芯片的一对端面呈镜面状,由激光共振器构成。光在 该共振器内往返的过程中放大后,取出到芯片外部。 • 特征 • 因为LD的主体是被称为诱导放出的发光过程,因此可以得到波长及相 位整齐集中在一起(相干性)的光。为此,指向性及能量集中性相当 优良。

动作原理 将受光器件的光电二极管作为太阳电池使用。红外线LED发射光的话, 受光器件(太阳电池)就会产生光起电力。这个电力通过控制电路令 MOSFET的栅极电压上升,就能让MOSFET进入ON状态。控制电路能 缩短MOSFET的关闭时间,将OFF期间的栅极电压保持为0,防止 MOSFET误启动。

光继电器的动作原理

• 特征 • 作为对机器进行ON/OFF控制的器件,有机械式继电器(机械式接 点)。光继电器和信号用机械式继电器相比,具有以下优点。 • 动作速度较快 • 无机械性磨损,寿命长 • 可以实现小型、薄型化 • 用途 • 电话、交换机、调制解调器 • 测定器、测试器 • 光断路器的动作和使用方法 • 指以将发光器件和受光器件在套筒内一体化,通过光的遮光或反射以 检测出物体为目的的器件。

激光半导体的动作原理

激光半导体的外观

• 结晶的种类的振荡波长 • 使用的结晶材料不同,激光的振荡波长也不一样。 大致可分为如左图所示几大类。而且,可以由1个 器件发出2种不同波长振荡的二波长激光半导体也 已经大量生产。 • 主要的应用领域 • InGaAIP激光:光盘(DVD)、条形码读取头 • GaAIAS激光:光盘(CD/MD)、激光束打印机 • InGaAsP激光:光通信 • InGaN激光:光盘(HD-DVD、蓝光光碟)

半导体制程概论

分解

e-

A

B

分子

自由基

B A

e-

電漿蝕刻

• 氧化物蝕刻製程,在電漿中使用CF4 產生氟(F)的自由基e + CF4 CF3 + F + e 4F + SiO2 SiF4 + 2O

半导体制程概论

目標

• 列出至少三種使用電漿的IC製程 • 列出電漿中重要的三種碰撞 • 描述平均自由徑 • 解釋電漿在蝕刻和化學氣相沉積製程的好處 • 說出至少兩種高密度電漿系統

討論的主題

• 什麼是電漿? • 為什麼使用電漿? • 離子轟擊 • 電漿製程的應用

電漿製程的應用

• 化學氣相沉積 • 蝕刻 • 物理氣相沉積 • 離子佈植 • 光阻剝除 • 製程反應室的的乾式清洗

• 電子和中性原子或分子碰撞 • 把軌道電子「敲離」核的束縛

離子化

• 游離碰撞產生電子和離子 • 維持電漿的穩定

e- + A

A+ + 2 e-

離子化的說明

原子核

原子核

自由電子入射 撞擊軌道電子

軌道電子

兩個自由電子

激發-鬆弛

e- + A

A* + e-

A* A + hn (光)

• 不同的原子/分子有不同的頻率,也就是為什麼不同的氣體會發出不同的顏色.

氮化鈦分子從鈦靶表面濺射出來而使之沉積在晶圓表面

表7.1 矽烷的分解

碰撞

副產品

形成所需的能量

e- + SiH4

SiH2 + H2 + eSiH3 + H + eSi + 2 H2 + eSiH + H2 + H + eSiH2* + 2H + eSi* + 2H2 + eSiH2+ + H2 + 2 eSiH3+ + H + 2 eSi+ + 2H2 + 2 eSiH+ + H2 + H + 2 e-

半导体制程简介

阐述图形化工艺的基本原理和方法,包括光刻、刻蚀、镀膜等步骤,以及这些步骤对半导体性能 的影响。

掺杂与退火

讲解掺杂剂的种类和作用,以及掺杂工艺的基本步骤和退火工艺对半导体性能的影响。

制程环境与设备

制程环境

介绍半导体制造所需的环境条件 ,如洁净度、温度、湿度等,以 及这些环境因素对半导体性能的 影响。

03

常见的半导体材料有硅、锗、砷化03

半导体材料具有高纯度、低缺陷等 特性。

硅是最常用的半导体材料,具有资 源丰富、制备工艺成熟等优势。

锗是一种具有高迁移率的半导体材 料,适用于高速电子器件。

半导体产业概述

01

半导体产业包括半导体制造、半导体设备、半 导体材料等领域。

案例三:纳米半导体器件制程

总结词

纳米半导体器件制程是一种制造纳米级尺寸 的半导体器件的制程,具有高频率、低功耗 、小尺寸等特点。

详细描述

纳米半导体器件制程采用先进的纳米制造技 术,如纳米压印、电子束光刻等,将半导体 材料加工成纳米级别的器件。该制程在微电 子、光电子、生物医学等领域具有广泛的应 用前景。

5G和物联网的驱动

5G和物联网技术的发展将推动半导体产业持续增长,对低功耗、 高性能半导体的需求不断增加。

中国市场的崛起

中国半导体市场已成为全球最大的市场之一,政府支持力度大,产 业发展迅速,国际合作与竞争日益激烈。

国际合作与竞争

国际合作

随着半导体产业的发展,国际合作成 为提高技术水平和竞争力的重要手段 ,各国纷纷建立合作机制,加强技术 交流和联合研发。

详细描述

半导体技术可以用于开发太阳能、风能等新能源发电设备中的半导体器件,提高能源利用效率;同时 也可以用于环保领域的半导体传感器、气体检测器等设备的开发,实现环境污染的监测与治理。

半导体制程概论chapter5萧宏

微控器

真空系統 界面電路 板

Hong Xiao, Ph. D.

/HongXiao/Boo

10

k.htm

氣體輸送系統示意圖

MFC

MFC

MFC

至製程 爐管

控制閥 調壓器

氣體鋼瓶

Hong Xiao, Ph. D.

/HongXiao/Boo

晶圓 加熱線圈

石英 爐管

氣流

溫度

中心帶區 平坦帶區

Hong Xiao, Ph. D.

/HongXiao/Boo k.htm

距離

23

垂直式高溫爐, 製程位置

製程反應 室

晶圓

加熱器 塔架

Hong Xiao, Ph. D.

/HongXiao/Boo

• 氮化矽沉積的氮源:

– NH3, 刺鼻的, 讓人不舒服的味道, 具腐蝕性

• 多晶矽沉基的摻雜物

– B2H6, PH3 和 AsH3

• 吹除淨化的氣體

– N2

Hong Xiao, Ph. D.

/HongXiao/Boo

15

k.htm

退火源

• 高純度的氮氣 ,大部分的退火製程使用. • H2O 經常做為PSG 或 BPSG 再流動製程十

/HongXiao/Boo

39

k.htm

簡介

• 矽和氧產生反應 • 產生穩定的氧化物 • 廣泛的使用在 IC 製造

Si + O2 SiO2

Hong Xiao, Ph. D.

/HongXiao/Boo

40

k.htm

矽氧化製程

ownership (COO)】

Hong Xiao, Ph. D.

/HongXiao/Boo

半导体制造概论(完整流程详解)

半导体制造概论(完整流程详解)近几年來,随着电子科技、网路等相关技术的进步,以及全球电子市场消费水平的提升,个人计算机、多媒体、工作站、网路、通信相关设备等电子产品的需求激增,带动整个世界半导体产业的蓬勃发展,而在台湾,半导体业更俨然成为维系国家经济动脉的一个主力。

基本上半导体制造为一垂直分工细密且高附加价值的产业,其快速的成长也会带动其他外围产业的繁荣,下图所示为一典型的半导体产业体系架构。

在这个体系中,半导体制造,也就是一般所称的晶圆加工(Wafer fabrication),是资金与技术最为密集之处,伴随着晶圆加工的上游产业则包括产品设计(IC design)、晶圆制造(Wafer manufacture)、以及光罩(Photo mask)制造等,下游产业则更为庞大,其中包括一般所称半导体后段制程(Back-end processes)的IC 封装(Packaging)、测试(T esting)、包装(Assembly ),以及外围的导线架制造(Lead-frame manufacture )、連接器制造(Connector manufacture)、电路板制造(Board manufacture)等,此一结合紧密的产业体系,形成了今日台湾经济命脉之所系。

一、IC 设计(IC design)二、晶圆制造(Wafer manufacture)(一)长晶(CRYSTAL GROWTH)长晶是从硅砂中(二氧化硅)提煉成单晶硅,其制造过程是将硅石(Silica)或硅酸盐(Silicate)如同冶金一样,放入爐中熔解提煉,形成冶金级硅。

由于冶金级硅中尚含有杂质,因此,必须再用分馏及还原的方法将其纯化,形成电子级硅。

虽然电子级硅所含的硅的纯度很高,可达99.9999 99999 %,但是结晶方式还是很杂亂,又称为多晶硅,必须重排成单晶结构才可,因此再将电子级硅置入坩埚内加温融化,其系先将温度降低至一设定点,再以一块单晶硅为『晶种』,置入坩埚内,让融化的硅沾附在晶种上,再将晶种以边拉边旋转方式抽離坩埚,而沾附在晶种上的硅亦随之冷凝,形成与晶种相同排列的结晶。

半导体制程概论萧宏chapter10

17

問

• 一個半導體製造商在海岸線旁有它自己 的研發實驗室,而其製造廠在一個高海 拔的高原。研發實驗室所發展的製程卻 無法被直接應用在特定的製造廠,為什 麼?

Hong Xiao, Ph. D.

/HongXiao/Boo k.htm

18

答

• 在一個高海拔的高原上,常壓要比海平 面低很多。早期的APCVD反應器沒有一 個壓力控制系統,所以研發室與製造廠 的製程狀況有極大的差異,在研發室成 效極佳的製程未必能在製造廠運作良好 。

Hong Xiao, Ph. D. /HongXiao/Boo k.htm 2

CVD 氧化層 vs. 加熱成長的氧化層

SiO2

Si Si

SiO2 Si

熱成長薄膜

矽裸片晶圓

沉積薄膜

Hong Xiao, Ph. D.

/HongXiao/Boo k.htm

10

導體

Hong Xiao, Ph. D.

/HongXiao/Boo k.htm

化學氣相沉積

• • • • • • • • • • • 氣體或是氣相源材料引進反應器內 源材料擴散穿過邊界層並接觸基片表面 源材料吸附在基片表面上 吸附的原材料再基片表面上移動 在基片表面上開始化學反應 固態副產物在基片表面上形成晶核 晶核生長成島狀物 島狀物合併成連續的薄膜 其他氣體副產品從基片表面上脫附釋出 氣體副產品擴散過邊界層 氣體副產品流出反應器.

SiO2 (玻璃) 介電質 PECVD

APCVD&SACVDTM TEOS, O3 (ozone) Oxynitride Si3N4 W (鎢) WSi2 TiN Ti Cu SiH4, N2O, N2, NH3 PECVD SiH4, N2, NH3 LPCVD SiH4, N2, NH3 LPCVD C8H22N2Si (BTBAS) WF6 (六氟化鎢), SiH4, H2 WF6 (六氟化鎢), SiH4, H2 Ti[N (CH3) 2]4 (TDMAT) TiCl4

半导体制程概论20031208

IC 製作流程

前段流程

IC 設計 晶圓代工 光罩製作 Wafer Process 封裝 CP測試 切割 FT測試

後段流程

測試

IC 設計 & 佈局

清洗

封裝 晶圓

Wafer Process Flow

IC FAB

Metallization

Materials

CMP

Dielectric deposition

半導體製程概論

By 彭文炙 & 黃鴻鈞 SCH MKT Dept.

Y2003/12/08

內

容

IC 製作流程 薄膜沉積(Thin Film Deposition) 物理氣相沉積(PVD) 化學氣相沉積(CVD) 微影(Photolithography) 蝕刻(Etching) 濕蝕刻(Wet Etching) 乾蝕刻(Dry Etching) 氧化與熱處理(Oxidation & Thermal Process) 摻雜(Doping) 擴散(Diffusion) 離子植入(Ion Implant) 化學機械研磨(CMP) CMOS 製作流程

物理氣相沉積(PVD)

定義: PVD指藉由物理方式將薄膜覆蓋在所需 的晶片上,包含有蒸鍍法(Evaporation)及濺 鍍法(Sputtering)。 PVD主要應用在金屬層 之薄膜沉積。

蒸鍍法

靶材(Target)

藉由動能的轉換,將靶材表面的原子 移出。 金屬層 晶片

濺鍍法

Back

PVD機台主要之供應商:

顯 影 (Development)

顯影的目的是要將晶片表面部分經過曝光的 光阻層,藉著中和反應加以清除。控制顯影 的主要操作條件有:顯影時間、顯影劑的濃 度及溫度等。

半导体制程概论加热工艺

05 未来半导体制程加热工艺 的发展趋势

高温超导材料在加热工艺中的应用前景

01

高温超导材料具有零电阻特性,能够实现高效能量 传输,减少能源损失。

02

随着高温超导技术的不断发展,其在半导体制程加 热工艺中的应用将更加广泛。

03

高温超导加热工艺能够提高制程设备的能源利用效 率和生产效率,降低能耗和生产成本。

04 加热工艺在半导体制程中 的挑战与解决方案

加热均匀性问题

总结词

加热均匀性是半导体制程中面临的重要 问题,它直接影响到产品的质量和良率 。

VS

详细描述

在半导体制程中,加热不均匀会导致材料 性能不均、晶体生长不均等问题,从而影 响产品的性能和可靠性。为了解决这一问 题,需要优化加热装置的设计,提高加热 元件的热传导效率和均匀性。同时,采用 先进的温度控制技术,实时监测温度分布 ,调整加热元件的功率输出,确保温度均 匀。

1960年代

半导体激光器的发明,为光电子产业的发 展奠定了基础。

02 加热工艺在半导体制程中 的作用

加热使半导体材料达到熔融状态,然后 通过冷却结晶形成晶体结构,是制备单晶材料的 关键步骤。

化学反应促进

加热能够促进半导体材料中的化学反应,如氧化 、还原、掺杂等,以改变材料的电学和光学性质 。

半导体制程的发展历程

1940年代

晶体管的发明,标志着半导体制程技术的 起步。

1980年代至今

不断发展的纳米技术,使得半导体制程技 术不断向更小尺度发展,为微电子、光电 子等领域带来了更多的创新和应用。

1950年代

集成电路的发明,实现了电子元件的微型 化,推动了电子产业的发展。

1970年代

硅基集成电路的普及,使得电子产品的性 能和可靠性得到了极大的提高。

图解半导体制程概论1教材

图解半导体制程概论(1)第一章半导体导论█半导体的物理特性及电气特性【半导体】具有处于如铜或铁等容易导电的【导体】、与如橡胶或玻璃等不导电的【绝缘体】中间的电阻系数、该电阻比会受到下列的因素而变化。

如:杂质的添加·温度光的照射·原子结合的缺陷█半导体的材料硅(Si)与锗(Ge)为众所周知的半导体材料.这些无素属于元素周期素中的第IV族,其最外壳(最外层的轨道)具有四个电子.半导体除以硅与锗的单一元素构成之处,也广泛使用两种以上之元素的化合物半导体.●硅、锗半导体(Si、Ge Semiconductor)单结晶的硅、其各个原子与所邻接的原子共价电子(共有结合、共有化)且排列得井井有条。

利用如此的单结晶,就可产生微观性的量子力学效果,而构成半导体器件。

●化合物半导体(Compound Semiconductor)除硅(Si)之外,第III族与第V族的元素化合物,或者与第IV族元素组成的化合物也可用于半导体材料。

例如,GaAs(砷化镓)、Gap(磷化砷)、AlGaAs(砷化镓铝)、GaN(氮化镓)SiC(碳化硅)SiGe(锗化硅)等均是由2个以上元素所构成的半导体。

█本征半导体与自由电子及空穴我们将第IV族(最外层轨道有四个电子)的元素(Si、Ge等),以及和第IV族等价的化合物(GaAs、GaN等),且掺杂极少杂质的半导体的结晶,称之为本征半导体(intrinsic semiconductor)。

●本征半导体(intrinsic semiconductor)当温度十分低的时候,在其原子的最外侧的轨道上的电子(束缚电子(bound electrons)用于结合所邻接的原子,因此在本征半导体内几乎没有自由载子,所以本征半导体具有高电阻比。

●自由电子(free electrons)束缚电子若以热或光加以激发时就成为自由电子,其可在结晶内自由移动。

●空穴(hole)在束缚电子成为自由电子后而缺少电子的地方,就有电子从邻接的Si原子移动过来,同时在邻接的Si原子新发生缺少电子的地方,就会有电子从其所邻接的Si原子移动过来。

半导体制程概论萧宏

Hong Xiao, Ph. D.

12

第12页 ,共167页。

應用 : 微鏡面(Micro-mirror)

• 數位投影顯示 • 鋁—鈦合金 • 小晶粒 ,高反射力 • “家庭劇院 ”

Hong Xiao, Ph. D.

13

第13页 ,共167页。

應用 : 融合(Fuse)

或Co接觸之處形成 – 濕式蝕刻製程剝除未反應的Ti 或 Co – 選擇性的再次退火以增加傳導率

Hong Xiao, Ph. D.

19

第19页 ,共167页。

自我對準的鈦金屬矽化物的形成步驟

Ti-

多晶矽匣極

n+ n-

匣極氧化層 n- n+

鈦沉積

Ti TiS2i

多晶矽匣極

TiS2i TiS2i

n-

n-

Si 小開口的接觸窗 , 使用PVD填入金 屬的情形

第41页 ,共167页。

Al·Cu

W SiO 2

Si

使用CVD鎢填入

小開口的接觸窗

41

鎢 CVD

• WF6 為鎢的源材料 • 和SiH4 反應形成核層(nucleation layer) • 和H2 反應形成巨量的鎢沉積 • 需要一層氮化鈦來幫助鎢的黏附

Hong Xiao, Ph. D.

35

第35页 ,共167页。

氮化鈦

• 阻擋層

– 防止鎢擴散

• 附著層

– 幫助鎢附著在氧化矽的表面

• 抗反射層鍍膜 (ARC)

– 降低反射率和改進金屬圖案化微影技術的解 析度

– 防止小丘狀突出物和控制電遷移

• 可以藉由PVD 和 CVD製程來沉積

半导体制造概论(完整流程详解)

半导体制造概论(完整流程详解)近几年來,随着电子科技、网路等相关技术的进步,以及全球电子市场消费水平的提升,个人计算机、多媒体、工作站、网路、通信相关设备等电子产品的需求激增,带动整个世界半导体产业的蓬勃发展,而在台湾,半导体业更俨然成为维系国家经济动脉的一个主力。

基本上半导体制造为一垂直分工细密且高附加价值的产业,其快速的成长也会带动其他外围产业的繁荣,下图所示为一典型的半导体产业体系架构。

在这个体系中,半导体制造,也就是一般所称的晶圆加工(Wafer fabrication),是资金与技术最为密集之处,伴随着晶圆加工的上游产业则包括产品设计(IC design)、晶圆制造(Wafer manufacture)、以及光罩(Photo mask)制造等,下游产业则更为庞大,其中包括一般所称半导体后段制程(Back-end processes)的IC 封装(Packaging)、测试(T esting)、包装(Assembly ),以及外围的导线架制造(Lead-frame manufacture )、連接器制造(Connector manufacture)、电路板制造(Board manufacture)等,此一结合紧密的产业体系,形成了今日台湾经济命脉之所系。

一、IC 设计(IC design)二、晶圆制造(Wafer manufacture)(一)长晶(CRYSTAL GROWTH)长晶是从硅砂中(二氧化硅)提煉成单晶硅,其制造过程是将硅石(Silica)或硅酸盐(Silicate)如同冶金一样,放入爐中熔解提煉,形成冶金级硅。

由于冶金级硅中尚含有杂质,因此,必须再用分馏及还原的方法将其纯化,形成电子级硅。

虽然电子级硅所含的硅的纯度很高,可达99.9999 99999 %,但是结晶方式还是很杂亂,又称为多晶硅,必须重排成单晶结构才可,因此再将电子级硅置入坩埚内加温融化,其系先将温度降低至一设定点,再以一块单晶硅为『晶种』,置入坩埚内,让融化的硅沾附在晶种上,再将晶种以边拉边旋转方式抽離坩埚,而沾附在晶种上的硅亦随之冷凝,形成与晶种相同排列的结晶。

半导体制程及原理概述

製程及原理概述半導體工業的製造方法是在矽半導體上製造電子元件(產品包括:動態記憶體、靜態記億體、微虛理器…等),而電子元件之完成則由精密複雜的積體電路(Integrated Circuit,簡稱IC)所組成;IC之製作過程是應用晶片氧化層成長、微影技術、蝕刻、清洗、雜質擴散、離子植入及薄膜沉積等技術,所須製程多達二百至三百個步驟。

隨著電子資訊產品朝輕薄短小化的方向發展,半導體製造方法亦朝著高密度及自動化生產的方向前進;而IC製造技術的發展趨勢,大致仍朝向克服晶圓直徑變大,元件線幅縮小,製造步驟增加,製程步驟特殊化以提供更好的產品特性等課題下所造成的良率控制因難方向上前進。

半導體業主要區分為材料(矽品棒)製造、積體電路晶圓製造及積體電路構裝等三大類,範圍甚廣。

目前國內半導體業則包括了後二項,至於矽晶棒材料仍仰賴外國進口。

國內積體電路晶圓製造業共有11家,其中聯華、台積及華邦各有2個工廠,總共14個工廠,目前仍有業者繼紙擴廠中,主要分佈在新竹科學園區,年產量逾400萬片。

而積體電路構裝業共有20家工廠,遍佈於台北縣、新竹縣、台中縣及高雄市,尤以加工出口區為早期半導體於台灣設廠開發時之主要據點。

年產量逾20億個。

原理簡介一般固體材料依導電情形可分為導體、半導體及絕緣體。

材料元件內自由電子濃度(n值)與其傳導率成正比。

良好導體之自由電子濃度相當大(約1028個e-/m3),絕緣體n值則非常小(107個e-/m3左右),至於半導體n值則介乎此二值之間。

半導體通常採用矽當導體,乃因矽晶體內每個原子貢獻四個價電子,而矽原子內部原子核帶有四個正電荷。

相鄰原子間的電子對,構成了原子間的束縛力,因此電子被緊緊地束縛在原子核附近,而傳導率相對降低。

當溫度升高時,晶體的熱能使某些共價鍵斯鍵,而造成傳導。

這種不完全的共價鍵稱為電洞,它亦成為電荷的載子。

如圖1.l(a),(b)於純半導體中,電洞數目等於自由電子數,當將少量的三價或五價原子加入純矽中,乃形成有外質的(extrinsic)或摻有雜質的(doped)半導體。

半导体概论

半导体生产流程所谓的半导体,是指在某些情况下,能够导通电流,而在某些条件下,又具有绝缘体效用的物质;而至于所谓的IC,则是指在一半导体基板上,利用氧化、刻蚀、扩散等方法,将众多电子电路组成各式二极管、晶体管等电子组件,作在一微小面积上,以完成某一特定逻辑功能(例如:AND、OR、NAND等),进而达成预先设定好的电路功能。

自1947年12月23日第一个晶体管在美国的贝尔实验室(Bell Lab)被发明出来,结束了真空管的时代,到1958年TI开发出全球第一颗IC成功,又意谓宣告晶体管的时代结束,IC的时代正式开始。

从此开始各式IC不断被开发出来,集成度也不断提升。

从小型集成电路(SSI),每颗IC包含10颗晶体管的时代;一路发展MSI、LSI、VLSI、ULSI;MSI(Middle-scale integration)中等规模集成电路;LSI(Large-scale integration)大规模集成电路;VLSI(Very-Large-scale integration)甚大规模集成电路;ULSI(Ultra-Large-scale integration)超大规模集成电路再到今天,短短50年时间,包含千万个以上晶体管的集成电路已经被大量生产,并应用到我们的生活的各领域中来,为我们的生活带来飞速的发展。

不能想象离开半导体产业我们的生活将会怎样,半导体技术的发展状况已成为一个国家的技术状况的重要指针,电子技术也成为一个国家提高国防能力的重要途径。

半导产品类别目前的半导体产品可分为集成电路、分离式组件、光电半导体等三种。

A.集成电路(IC),是将一电路设计,包括线路及电子组件,做在一片硅芯片上,使其具有处理信息的功能,有体积小、处理信息功能强的特性。

依功能可将IC分为四类产品:内存IC、微组件、逻辑IC、模拟IC。

B.分离式半导体组件,指一般电路设计中与半导体有关的组件。

常见的分离式半导体组件有晶体管、二极管、闸流体等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

二.元件操作原理

矽晶體結構

矽的簡介

矽是現在各種半導體,使用最頻 繁的一種電子材料,它的來源極 廣,譬如我們腳下所踩的砂。它 的含量佔地球表層的25%,又極 易純化,製造容易而且經濟,因 此已經被人們用來做為積體電路 製作的主要材料達十年之久。在 元素週期表裡,它是排在三價的 鋁與五價的磷之間。

IC製程技術 四.IC製程技術

潔淨室介紹 CMOS製作流程 CMOS製作流程 清洗晶圓 氧化 化學氣相沉積( 化學氣相沉積(CVD) 微影 蝕刻(ETCH) 蝕刻(ETCH) 擴散 離子佈植(IMPLANT) 離子佈植(IMPLANT) 連結

潔淨室介紹

潔淨室的分類

我們可以由這一張 圖表來了解,以0.5um的 塵粒直徑為比較標準, 在1立方英吋的空間中, 直徑大於0.5um的塵粒有 一個,就稱為Class 1, 而直徑大於0.5um的塵粒 有十個,就稱為Class 10, 直徑大於0.5um的塵粒有 1000個,就稱為Class 1000,而目前各大半導 體積體 電路製造廠大部 份都在Class 10的環境下 製造。

標準清洗步驟

硫酸(H2SO4)介紹 硫酸(H2SO4)介紹 (H2SO4)

RCA清洗的過程中 我們會利用到的硫酸 (H2SO4),即是利用硫 酸 有很強的酸性、氧化 性、和脫水性。因為硫 酸的強脫水性可以破壞 許多的有機物質使之脫 水而碳化。另外,其強 酸性及強氧化性可將一 些附著在晶片上的金屬 予以氧化成硫酸鹽,再 利用純水加以溶除。

41.將元件予 以退火處理

晶圓清洗

清洗簡介

由於IC內各元件間線路相當的 細 小,因此在製造過程中,只要 有大氣中微細粉塵或製造過程中所 殘留下的污染源,如反應器壁落下 之金屬離子或乾式蝕刻後留下之殘 留物..等,掉落在晶片上,則容易 破壞晶片內的電路函數功能,進而 影 響其電路性能甚至無法工作。 我們除了要隔離外界的污染源, 操 作人員、設備所產生的粉塵及 其他污染源外,濕式清洗步驟在不 破壞晶圓表面之前提下,有效地清 除製程中所產生殘留之微塵金屬離 子 及 有 機 物 之 污 染 物 。

電路模擬分析

邏輯設計完成之後,接著要將每一個邏輯單元,轉化成實際的 電路元件符號,再依這些元件符號轉化成電路分析模擬程式,常用 的電路分析模擬程式為HSPICE等模擬軟體,檢查其模擬結果是否 符合我們所需的要求上圖為經過HSPICE所模擬出來的電性結果。

電路佈局

所謂電路的佈局,實際上就 是做電路分析及半導體製程的中 間橋梁,即是將我們在製程上所 會利用到在光罩(Mask)在這個時 候畫出來,即為電路佈局。當我 們做完電路佈局時, 還要利用 CAD的程式,檢查做的電路佈局 是否有缺失,確定沒問題之後, 再利用所做的電路佈局放入程式 中做電路分析模擬,看是否和先 前由SPICE所跑出來的結果是否一 致,如果不一致,則再從電路模 擬分析軟體重新做,再到電路佈 局,直到結果正確之後,再將電 路佈局的結果送出,去製做光罩 及 後 續 的 半 導 體 製 程 。

二氧化矽(SiO2)的製作方法有 二氧化矽(SiO2)的製作方法有 (SiO2)

1.熱氧化法 熱氧化法, 熱氧化法 2.沈積法 沈積法, 沈積法 3.陽極氧化法 陽極氧化法, 陽極氧化法 4.氧離子注入 氧化法。 氧離子注入 氧化法。 其中較常用的熱氧化法又可分為 1.乾氧化法 乾氧化法 2.濕氧化法 濕氧化法 3.純水氧化法 純水氧化法 4. 摻氯氧化法 。 而濕氧化法又有: 而濕氧化法又有 氧氧化法及氫氧合成濕氧化法。 普通濕 氧氧化法及氫氧合成濕氧化法。

CMOS製作流程( CMOS製作流程(一) 製作流程

1. 初始清洗

5. 去除氮化 矽

9. 負型井的 離子佈植

13. 氮化矽的 沈積

17. 去除氮化 矽

2. 前置氧化

6. 正型井離 子佈植

10. 負型井的 退火

14. 元件隔離 區光罩形成

18. 利用氫氟 酸去除閘極區 域的氧化層

3. 沈積氮化 矽

7. 退火及氧 化層形成

11. 去除二氧 化矽

15. 氮化矽蝕 刻

19. 閘極氧化 層的形成

4. 正型井光 罩形成

8. 去除氮化 矽

12. 前置氧化

16. 元件隔離 區氧化

20. 閘極多晶 矽的沈積

CMOS製作流程( CMOS製作流程(二) 製作流程

21.閘極光罩 的形成 25.PMOS源極 汲極製成 29.第一層金 屬接觸洞 33.將二氧化 矽塗上晶片表 面 37.第二層金 屬製成

鑽石結構

在三度空間中,矽晶體四個 最鄰近的原子便位在四面體的四 個角,每一個原子都停留在一個 中心位置,並且不會移動太遠, 在熱振動時,即以此位置為中心 做小幅動,我們稱此矽單晶結構 為鑽石結構。

矽的結構

晶體和非晶體本身都可以是 一種純物質,而晶體的特點,就 是材料以原子或分子,在三度空 間週期性排列著,矽晶體便是鑽 石結構做一規則週期性的排列。

邏輯設計

邏輯設計的目的是用已有的基本邏輯單元,來確定滿足邏輯要 求條件下的邏輯構成。這些基本的邏輯單元可以是及閘(And Gate)、 或閘(OrGate)、皆非閘(Nor Gate)等基本閘單元,由這些基本單元來 構成整個的積體電路。接著跑邏輯模擬軟體,確定所設計的邏輯沒 有問題上圖即為一個邏輯設計圖。

摻雜

所謂摻雜,就是在半導體的材料中加入電 子,或電洞,使半導體形成以電子,或以電洞 來傳導電信號。摻雜又可以分為 正摻雜 負摻雜

正摻雜

所謂正摻雜,就是在一個規 則排列的矽晶體中,摻入週期表 中三族的元素,由於要和矽鍵結 須要四個電子,所以少了一個電 子,即形成了一個電的空缺,我 們稱之為電洞,當外加一個電壓 時,電洞向負電位之處移動,形 成了電的傳導。此摻雜的區域即 稱為正型區(p-type region),主要 的傳導載子為電洞。

訊

自 動 化

在競爭激烈的產業 環境中,無人化的生產 工廠,已是未來企業所 追尋的目標。現今的工 業環境中使用電腦晶片 控制的機器人及自動化 生產設備不但可降低機 器對人的傷害,更可消 除人員因素所 造成的產 品差異性,使生產流程 可以標準化,提高產品 品質、節 省大量的人力 管理方便,製造出具有 競 爭 力 的 產 品 。

IC 電路設計流程 功能描述 邏輯設計 電路模擬分析 電路佈局

IC 電路設技流程

功能描述 邏輯設計 電路模擬分析 電路佈局 佈局的電路模擬 Check

YES

NO

生產製造

功能描述

要完成一個完整的積體電路晶片,首先就是要對這一個晶片 做完整的功能描述,例如要完成一個電腦CPU的晶片設計,就必 要將CPU所要處理的功能函數做完整的描述。例如上圖,我們要 設計一個簡單的計數器IC就要對每一個接腳的波形做描述,此即 為功能描述。

元件操作

何謂MOSFET

所謂MOSFET指的就是金屬─氧 化層─半導體電晶體(Metal-OxideSemiconductor Field-Effect Transistor),其結構就如同字面上 的意義,是由金屬、氧化層、及 半導體疊在一起所OSFET依其傳導的載子不 同可以分為PMOS及NMOS二種。 將這二種MOS合在一起使用則稱 為互補式金氧半電晶體,即為 CMOS。CMOS的好處就是省電, 因此在電路設計時,就是以 CMOS為基本的單元來設計。

個人電腦

積體電路在個人電腦 中的應用有如:資料處理 單元即一般所謂的中央處 理單元(CPU)、以及周邊 的輸出、入單元(如BIOS、 RAM、 ROM..等)。近年 來由於積體電路技術的發 展迅速,不僅將體積大大 的縮小了,而且功能也愈 來愈強速度更快。 發明, 使得個人電腦可以替代人 類處理許多複雜且重複性 高或具高危險性的工作。

CMOS工作原理 一) 工作原理(一 工作原理

當輸入端輸入為高電壓(1)時, NMOS導通,而PMOS不導通, 所以輸出端為低電壓(0)。

CMOS工作原理 二) 工作原理(二 工作原理

當輸入端輸入為低電壓(0)時, NMOS不導通,而PMOS導通,所 以輸出端為高電壓(1)。

IC電路設計 三.IC電路設計

‧一.IC 應用簡介 一 ‧二.元件操作原理 二 ‧三.IC電路設計 三 IC電路設計 ‧四.IC製程技術 四 IC製程技術

資料來源 : 國科會國家毫微米元件實驗室

一.IC 應用簡介

IC 演進 個人電腦 通訊 自動化 消費性電子產品 國防與太空

IC 演進

半導體工業自1947年發明電晶 體後,已經成為現代新興工業 的主 流,由於技術的迅速成長與突破, 使積體電路(Integration Circuit, IC) 之製造得以在短短的40年間由單一 的電晶體、電阻、電容等分離元件 (discrete Device)的組合發展到可以 容納數十個電晶體的小型積體電路 (SSI),再經歷至可容納數十萬個電 晶體的大型積體電路 (LSI),甚至擴 展到現今已經可以容納數千萬個電 晶體的極大型積體電路(ULSI)。這 種發展的速度是其它任何領域都無 法 與 之 相 比 的 。

負摻雜

所謂負摻雜,就是在一個規 則排列的矽晶體中,摻入週期表 中五族的元素,由於要和矽鍵結 須要四個電子,所以多一個電子, 即在摻雜原子的附近多出了一個 電子,當外加一個電壓時,電子 向正電位之處移動,形成了電的 傳導。此摻雜的區域即稱為負型 區 (n-type region),主要的傳導載 子為電子。

化學氣相沉積分類

化學氣相沈積(CVD)依照工作壓力及能 源形式主要可分 為: 1.常壓化學氣相沈積法 (APCVD) 常壓化學氣相沈積法 2.低壓化學氣相沈積法 (LPCVD) 低壓化學氣相沈積法 3.電漿增強式化學氣相沈積法 電漿增強式化學氣相沈積法(PECVD) 電漿增強式化學氣相沈積法 4.光反應式化學氣相沈積法 (PHCVD) 光反應式化學氣相沈積法