半导体制程技术导论Chapter_1导论

半导体基础知识ppt课件

多。这样所产生的电容就是扩散

电容CD。

(1-31)

CB在正向和反向偏置时均不能忽略。而反向偏置 时,由于载流子数目很少,扩散电容可忽略。

PN结高频小信号时的等效电路: rd

势垒电容和扩散电 容的综合效应

(1-32)

二极管:死区电压=0 .5V,正向压降0.7V(硅二极管) 理想二极管:死区电压=0 ,正向压降=0

受主原子。

硼原子

P 型半导体中空穴是多子,电子是少子。

(1-16)

三、杂质半导体的示意表示法

---- - - ---- - - ---- - - ---- - -

+ +++++ + +++++ + +++++ + +++++

P 型半导体

N 型半导体

杂质型半导体多子和少子的移动都能形成电流。

但由于数量的关系,起导电作用的主要是多子。 近似认为多子与杂质浓度相等。

稳压二极管的应用举例

i

iL

稳压管的技术参数:

UzW 10V, Izmax 20mA, ui

R

DZ

iZRL uo

Izmin 5mA

负载电阻 RL 10k。要求当输入电压由正常值发

生20%波动时,负载电压基本不变。

求:电阻R和输入电压 ui 的正常值。

解:令输入电压达到上限时,流过稳压管的电

(1-9)

空穴

+4

+4

+4

+4

自由电子 束缚电子

(1-10)

半导体制造技术导论萧宏台译本

半导体制造技术导论萧宏台译本摘要:一、半导体制造技术的概述二、半导体制造技术的发展历程三、半导体制造技术的重要性四、半导体制造技术的应用领域五、半导体制造技术的未来发展趋势正文:一、半导体制造技术的概述半导体制造技术是指通过一系列复杂的工艺步骤,将半导体材料制成具有特定功能和性能的集成电路和器件的过程。

半导体制造技术作为现代电子信息技术的基础,广泛应用于计算机、通信、家电等领域,对于推动科技发展和提高人类生活水平具有重要意义。

二、半导体制造技术的发展历程半导体制造技术的发展经历了几个阶段。

早期,人们主要通过手工操作和简单的设备进行半导体材料的加工。

随着科学技术的进步,半导体制造技术逐渐实现了自动化、智能化,制造工艺也日趋精密。

从20 世纪中叶开始,半导体制造技术进入了快速发展阶段,集成电路的集成度不断提高,尺寸不断缩小,性能不断提升。

三、半导体制造技术的重要性半导体制造技术对于现代科技和社会经济发展具有举足轻重的地位。

首先,半导体制造技术是信息技术产业发展的基础。

计算机、通信设备等电子产品的核心部件都是由半导体材料制成的。

其次,半导体制造技术对提高人民生活水平具有重要意义。

半导体技术在医疗、教育、交通等领域的应用,极大地改善了人们的生活质量。

最后,半导体制造技术是国家科技实力的重要体现。

一个国家在半导体制造技术领域的地位,往往能反映出这个国家在国际竞争中的实力。

四、半导体制造技术的应用领域半导体制造技术的应用领域非常广泛,主要包括以下几个方面:1.计算机:计算机处理器、内存等关键部件都是由半导体材料制成的。

2.通信:手机、无线通信基站等通信设备中,半导体器件占有重要地位。

3.家电:半导体技术在家电产品中的应用,如电视机、冰箱、空调等,使得这些产品更加智能化、节能化。

4.工业控制:半导体技术在工业控制领域的应用,提高了生产效率和产品质量。

5.医疗:半导体技术在医疗设备中的应用,如超声波、心电图等,提高了疾病诊断和治疗的水平。

半导体材料导论1-1PPT课件

(1)电导率: 半导体材料在室温下,它的电导率s在103~10-9S/cm之间,S为西门子,电导单位, 电导率s =1/r(电阻率) (W. cm) ; 一般金属为107~104S/cm; 绝缘体则<10-10,最低可达10-17。 同时,同一种半导体材料,因其掺入的杂质量不同,可使其电导率在几个到十几 个数量级的范围内变化,也可因光照和射线辐照明显地改变其电导率;

.

2

第一章:半导体材料综述

半导体已成为家喻户晓的名词,收音机是半导体的、电视机是半导体的、计 算器及计算机也是半导体的。那么哪些是半导体材料?它有哪些特征?

1 半导体材料的特征 半导体材料在自然界及人工合成的材料中是一个大的部类。顾名思义,半导体在其

电的传导性方面,其电导率低于导体,而高于绝缘体。它具有如下的主要特征。

BC 硼碳

Si P S 硅磷硫 Ge As Se 锗砷硒 Sn Sb Te I 锡锑碲碘

图1.1元素半导体在周期表中的位置

.

7

从图1.1也可以看出半导体材料与物质结构的密切关系。

处于III-A族的只有硼,其熔点高(2300oC),制备单晶困难,而且其载流子迁移率 很低,对它研究的不多,未获实际应用。 IV-A 族中第一个是碳,它的同素异形体之一金刚石具有优良的半导体性质,但制 备单晶困难,是目前研究的重点;石墨是碳的另一个同素异形体,系层状结构,难 以获得单晶,故作为半导体材料未获得应用。 IV-A族的第二个元素是硅,具有优良的半导体性质,是现代最主要的半导体材料。 再往下是锗,它具有良好的半导体的性质,是重要的半导体材料之一。 IV-A族的第四个元素锡在常温下的同素异形体为b-Sn,属六方晶系,但在13.2oC 以下 可变为立方晶系灰锡(a-Sn)。灰锡具有半导体性质,属立方晶系。在从bSn转化为a-Sn 的过程中,体积增大并变粉末,故难以在实际中应用。

【2017年整理】图解半导体制程概论

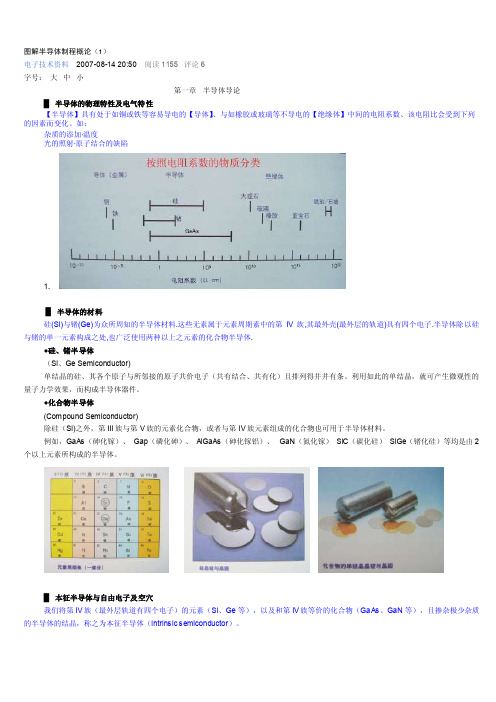

图解半导体制程概论(1)电子技术资料 2007-08-14 20:50 阅读1155 评论6字号:大中小第一章半导体导论█半导体的物理特性及电气特性【半导体】具有处于如铜或铁等容易导电的【导体】、与如橡胶或玻璃等不导电的【绝缘体】中间的电阻系数、该电阻比会受到下列的因素而变化。

如:杂质的添加·温度光的照射·原子结合的缺陷1.█半导体的材料硅(Si)与锗(Ge)为众所周知的半导体材料.这些无素属于元素周期素中的第IV族,其最外壳(最外层的轨道)具有四个电子.半导体除以硅与锗的单一元素构成之处,也广泛使用两种以上之元素的化合物半导体.●硅、锗半导体(Si、Ge Semiconductor)单结晶的硅、其各个原子与所邻接的原子共价电子(共有结合、共有化)且排列得井井有条。

利用如此的单结晶,就可产生微观性的量子力学效果,而构成半导体器件。

●化合物半导体(Compound Semiconductor)除硅(Si)之外,第III族与第V族的元素化合物,或者与第IV族元素组成的化合物也可用于半导体材料。

例如,GaAs(砷化镓)、Gap(磷化砷)、AlGaAs(砷化镓铝)、GaN(氮化镓)SiC(碳化硅)SiGe(锗化硅)等均是由2个以上元素所构成的半导体。

█本征半导体与自由电子及空穴我们将第IV族(最外层轨道有四个电子)的元素(Si、Ge等),以及和第IV族等价的化合物(GaAs、GaN等),且掺杂极少杂质的半导体的结晶,称之为本征半导体(intrinsic semiconductor)。

●本征半导体(intrinsic semiconductor)当温度十分低的时候,在其原子的最外侧的轨道上的电子(束缚电子(bound electrons)用于结合所邻接的原子,因此在本征半导体内几乎没有自由载子,所以本征半导体具有高电阻比。

●自由电子(free electrons)束缚电子若以热或光加以激发时就成为自由电子,其可在结晶内自由移动。

《半导体制造技术导论》读书笔记PPT模板思维导图下载

3.8 参考文献

3.7 小结

3.9 习题

第4章 晶圆制造

01

4.1 简介

02

4.2 为什 么使用硅 材料

03

4.3 晶体 结构与缺 陷

04

4.4 晶圆 生产技术

06

4.6 衬底 工程

05

4.5 外延 硅生长技 术

4.8 参考文献

4.7 小结

4.9 习题

第5章 加热工艺

01

5.1 简介

02

6.4 光刻技术的 发展趋势

6.5 安全性 6.6 小结

6.7 参考文献 6.8 习题

第7章 等离子体工艺

01

7.1 简介

02

7.2 等离 子体基本 概念

03

7.3 等离 子体中的 碰撞

04

7.4 等离 子体参数

06

7.6 直流 偏压

05

7.5 离子 轰击

7.7 等离子体工 艺优点

7.8 等离子体增 强化学气相沉积

10.9 工艺发展趋 势与故障排除

10.10 化学气相 沉积工艺发展趋 势

10.12 参考文献

10.11 小结

10.13 习题

第11章 金属化工艺

01

11.1 简 介

02

11.2 导 电薄膜

03

11.3 金 属薄膜特 性

04

11.4 金 属化学气 相沉积

06

11.6 铜 金属化工 艺

05

11.5 物 理气相沉 积

5.2 加热 工艺的硬 件设备

03

5.3 氧化 工艺

04

5.4 扩散 工艺

06

5.6 高温 化学气相 沉积

05

半导体制造技术导论

半导体制造技术导论

半导体制造技术是指利用诸如金属化学气相沉积技术、外延物理气相沉积技术、光刻技术、电抗沉积技术等复杂的生产工艺结构,以原材料(硅)作为基础,精细地编织出特定的晶体材料加工和芯片制造工艺的过程。

主要应用在半导体元件的制造和芯片封装等。

目前,半导体制造工艺结构分为三大部分:前处理、主处理和后处理。

前处理包括硅晶体生长、内层抗拉开口处理、外层处理、元件芯片封装、检测测试和组装。

主处理主要包括金属物理气相沉积、光刻、掩模、波峰焊、液相沉积和电抗沉积等。

后处理主要包括芯片封装、测试检测和组装工艺。

半导体制造技术是电子集成电路和电子元件的核心技术之一,它的成功主要取决于精细的工艺结构操作、严格的工艺控制,以及完整的质量控制体系,这些都是半导体制造技术取得成功的关键因素。

半导体制造概论(完整流程详解)

半导体制造概论(完整流程详解)近几年來,随着电子科技、网路等相关技术的进步,以及全球电子市场消费水平的提升,个人计算机、多媒体、工作站、网路、通信相关设备等电子产品的需求激增,带动整个世界半导体产业的蓬勃发展,而在台湾,半导体业更俨然成为维系国家经济动脉的一个主力。

基本上半导体制造为一垂直分工细密且高附加价值的产业,其快速的成长也会带动其他外围产业的繁荣,下图所示为一典型的半导体产业体系架构。

在这个体系中,半导体制造,也就是一般所称的晶圆加工(Wafer fabrication),是资金与技术最为密集之处,伴随着晶圆加工的上游产业则包括产品设计(IC design)、晶圆制造(Wafer manufacture)、以及光罩(Photo mask)制造等,下游产业则更为庞大,其中包括一般所称半导体后段制程(Back-end processes)的IC 封装(Packaging)、测试(T esting)、包装(Assembly ),以及外围的导线架制造(Lead-frame manufacture )、連接器制造(Connector manufacture)、电路板制造(Board manufacture)等,此一结合紧密的产业体系,形成了今日台湾经济命脉之所系。

一、IC 设计(IC design)二、晶圆制造(Wafer manufacture)(一)长晶(CRYSTAL GROWTH)长晶是从硅砂中(二氧化硅)提煉成单晶硅,其制造过程是将硅石(Silica)或硅酸盐(Silicate)如同冶金一样,放入爐中熔解提煉,形成冶金级硅。

由于冶金级硅中尚含有杂质,因此,必须再用分馏及还原的方法将其纯化,形成电子级硅。

虽然电子级硅所含的硅的纯度很高,可达99.9999 99999 %,但是结晶方式还是很杂亂,又称为多晶硅,必须重排成单晶结构才可,因此再将电子级硅置入坩埚内加温融化,其系先将温度降低至一设定点,再以一块单晶硅为『晶种』,置入坩埚内,让融化的硅沾附在晶种上,再将晶种以边拉边旋转方式抽離坩埚,而沾附在晶种上的硅亦随之冷凝,形成与晶种相同排列的结晶。

半导体工艺讲义Lec_01

EE143 General InformationInstructor : Prof. Nathan Cheung , Cory 513, 642-1615 ,Lecture Hours and Place: Tu &Th, 11am-12:30pm, Barrow 126Textbooks:1) Required EE143 Reader and lecturenotes2) Required R.C. Jaeger "Introduction To Microelectronics Fabricat “, 2 EditionndOffice Hours: Tue 1-2pm, Wed 1-3pm, and by appointment via e-mailHomework: Weekly homework assignments due on Thursdays. Grading: Midterm1 15%,Midterm2 15%, Final 30% ,Homework 10%, Lab 30% 5 Lab Sections(Tu 2-5pm,W 9-12am, W 2-5pm, Th 2-5pm, F 9-12am) to accommodate 70studentsProfessor Nathan Cheung, U.C. BerkeleyLab Sign-up required for ALL studentsSign-up sheets will be posted outside Cory 218 after Tue 5pm (1/22) . You have to sign up before Friday 1/24, 12 noon. If you don’t, we assume you are no longer enrolled.Lab assignments will be posted before next Monday (1/27) If havea lab assignment by 1/27, you will be officially enrolled 1) Telebear enrolled students with lab sign up have highest priority2) Telebear wait-listed students with lab sign up have secon priority 3) Students with lab sign up only will have third priority • There will be no lab session the first week of class. • Mandatory Safety Orientation Lab Section the week of 1/28 You can show up at ANY of the lab session for the 2nd week.You have to pass a safety quiz the same day • EE143 Reader available at Copy Central on Euclid 1/27 Professor Nathan Cheung, U.C. BerkeleyLectures, HW, Lab Manual, and News (check regularly)/~ee143/ Other Websites for EE143 Overview Device Physics/ Process Visualization – Highly recommended(Change the device parameters and watch the resultant space charge, energy bands , I-V , C-V etc)MEMS operation (Good collection of photos and /movies)/scripts/index.aspSIA Roadmap (Trend and Challenge)EE Basics (E40 course/http://www-material)/~ee40//TutProcessing TourProfessor Nathan Cheung, U.C.orial/What is EE143 allabout?• MicrofabricationPrinciples• Hands-on Fabricationfor IC and MEMSandTesting of IC andMEMSDevicesProfessor Nathan Cheung, U.C.EE143ChipLayoutProfessor Nathan Cheung, U.C.After resist patterning onnitride/pad oxide ProcessSimulation* Topography and DopantDistributionAfter Local Oxidation After Poly-Si Gate PatterningProfessor Nathan Cheung, U.C.1∝m = 10 cm = 10 m = 1000nm-4 -6 0.13 ∝mState-of-the-art Mass Production ICn + n+ ~ 200TransistorsDiameter of human hair~50∝m Professor Nathan Cheung, U.C.Advantages of Technology Scaling• More dies per wafer, lowercost• Higher-speed devices andcircuits Generation: 1.5µ1.0µ0.8µ0.6µ0.35µ0.25µIntel386™DXProcessorInte l486™DXProcessorPentium ®ProcessorPentiumII®Professor Nathan Cheung, U.C.Professor Nathan Cheung, U.C.MOSFET works down to 18nm channel length !Professor Nathan Cheung, U.C. BerkeleySIA roadmap / Memory and Logic Technology RequirementsYear of First ProductShipment1999 2001 2003 2006 2009 2012 180nm 150nm 130nm 100nm 70nm 50nmTechnology GenerationMin. Logic V dd (V)T ox Equivalent (nm) 1.8-1.53-41.5-1.22-31.5-1.22-31.2-0.91.5-2>50.9-0.6<1.5>50.6-0.5<1.0>5Equivalent MaximumE-field (MV/cm)5 5 5Nominal I @ 25o(∝A/∝m)(NMOS/PMOS)C 600/28036-72 600/28030-60600/28026-52600/28020-40600/28015-30600/28010-20onS/D ExtensionJunctionDepth, Nominal (nm) Professor Nathan Cheung, U.C.Source: Intel Developer Forum Professor Nathan Cheung, U.C.2002Example: PressureSensor BulkSiMicromachiningPyrexGlassSiSurfaceMicromachiningProfessor Nathan Cheung, U.C.MEMSActuatorsGear Speed ReductionMovable Mirror UnitResponsive Drug Delivery Turbine engine Professor Nathan Cheung, U.C.Commercial MEMSProducts• Optomechanical Displays–Texas Instruments’ Digital Micromirror Display(1996) Professor Nathan Cheung, U.C.MEMS-ICIntegration(Sandia National Lab)• ME MS fabricated in 12 m-deep trench – Filled with SiO2 and planarized usingCMPProfessor Nathan Cheung, U.C.Silicon-COmpatible OPtoelectronics (SCOOP)Si-BASED WAVEGUIDESProfessor Nathan Cheung, U.C. BerkeleyThe Brave NewWorld•Optical Communications network•Microelectromechanical systems(MEMS)•Nanotechnology/~dp10 Professor Nathan Cheung, U.C.Artificial Silicon Retina™(ASR)2mm, 1/1000” thick/index.h Professor Nathan Cheung, U.C.Professor Nathan Cheung, U.C.21 / 22Heterogeneous Integration of Optical Materials 1D and 0D - -Organic LED Displayoptical mediumSi & Si-GeLow power electronicsOptical waveguides / Photonic crystalsOpto-MEMS MEMSIII-VSemiconductorPhotonicsProfessor Nathan Cheung, U.C. BerkeleyEE143 Lecture#122 / 22 Prof. Peidong Yang, UCB(i) Co-axial heterostructure nanowire (COHN); (ii) longitudinal heterostructure nanowire (LOHN).Carbon Sheath aroundGe Core Nanostructure ZnO nanowire array grownonsapphire substrate using VLS processProfessor Nathan Cheung, U.C. Berkeley EE143 Lecture#1。

图解半导体制程概论1教材

图解半导体制程概论(1)第一章半导体导论█半导体的物理特性及电气特性【半导体】具有处于如铜或铁等容易导电的【导体】、与如橡胶或玻璃等不导电的【绝缘体】中间的电阻系数、该电阻比会受到下列的因素而变化。

如:杂质的添加·温度光的照射·原子结合的缺陷█半导体的材料硅(Si)与锗(Ge)为众所周知的半导体材料.这些无素属于元素周期素中的第IV族,其最外壳(最外层的轨道)具有四个电子.半导体除以硅与锗的单一元素构成之处,也广泛使用两种以上之元素的化合物半导体.●硅、锗半导体(Si、Ge Semiconductor)单结晶的硅、其各个原子与所邻接的原子共价电子(共有结合、共有化)且排列得井井有条。

利用如此的单结晶,就可产生微观性的量子力学效果,而构成半导体器件。

●化合物半导体(Compound Semiconductor)除硅(Si)之外,第III族与第V族的元素化合物,或者与第IV族元素组成的化合物也可用于半导体材料。

例如,GaAs(砷化镓)、Gap(磷化砷)、AlGaAs(砷化镓铝)、GaN(氮化镓)SiC(碳化硅)SiGe(锗化硅)等均是由2个以上元素所构成的半导体。

█本征半导体与自由电子及空穴我们将第IV族(最外层轨道有四个电子)的元素(Si、Ge等),以及和第IV族等价的化合物(GaAs、GaN等),且掺杂极少杂质的半导体的结晶,称之为本征半导体(intrinsic semiconductor)。

●本征半导体(intrinsic semiconductor)当温度十分低的时候,在其原子的最外侧的轨道上的电子(束缚电子(bound electrons)用于结合所邻接的原子,因此在本征半导体内几乎没有自由载子,所以本征半导体具有高电阻比。

●自由电子(free electrons)束缚电子若以热或光加以激发时就成为自由电子,其可在结晶内自由移动。

●空穴(hole)在束缚电子成为自由电子后而缺少电子的地方,就有电子从邻接的Si原子移动过来,同时在邻接的Si原子新发生缺少电子的地方,就会有电子从其所邻接的Si原子移动过来。

半导体制程技术导论

Hong Xiao, Ph. D. hxiao89@

Hong Xiao, Ph. D. /HongXiao/Boo k.htm 1

目標

讀完本章之後,你應該能夠:

• • • •

熟悉半導體相關術語的使用 描述基本的積體電路製造流程 簡明的解釋每一個製程步驟 半導體製程與你的工作或產品有相關性的 連結

/HongXiao/Boo k.htm

16

IC 設計: 第一顆IC

照片提供: 德州儀器

Hong Xiao, Ph. D. /HongXiao/Boo k.htm 17

IC 設計: CMOS 反相器

NMOS

Vin

Vdd

簡介

• • • • • 第一個電晶體, AT&T貝爾實驗室 , 1947 第一個單晶鍺, 1952 第一個單晶矽, 1954 第一個積體電路元件, 德州儀器, 1958 第一個矽積體電路晶片, 費爾查德照相機 公司, 1961

/HongXiao/Boo k.htm 4

原子的大小

Hong Xiao, Ph. D.

/HongXiao/Boo k.htm

15

IC 元件的限制

• • • • 原子大小: 數個埃( Å) 形成一個元件需要一些原子 一般最後的限制在100 Å 或 0.01 微米 大概30 個矽原子

arge Scale Integration) 極大型積體電路(Very Large Scale Integration) 超大型積體電路(Ultra Large Scale Integration) 特大型積體電路(Super Large Scale Integration)

MSI

半导体制造导论

第五章章前1至少列出三种重要的加热制程氧化,退火,沉积是三种重要的加热制程2说明直立式和水平式炉管的基本系统并列出直立式炉管的优点气体输送系统,制程炉管,控制系统,气体排放系统,装载系统。

LPCVD的话再加上真空系统优点:占地面积小,微粒污染较低,能够处理大量的晶圆,均匀性较佳,维修成本较低3.说明氧化制程氧化是最重要的制程之一,它是一种添加制程,把氧气加到硅晶圆上,在晶圆表面形成二氧化硅4.说明氧化前清洗的重要性氧化制程前的硅晶圆表面清洗是十分重要的,因为受到污染的表面会提供成核位置而形成二氧化硅多晶体层5.辨认干式氧化和湿式氧化制程及应用的差异性干式制程:闲置状态下通入净化氮气气体——闲置状态下通入制程氦气气体——在制程氮气流下把晶舟推入反映炉管——氮气氛围下升温——氮气分为下达到稳定温度——关闭氮气,通入氧气和氯化氢——关闭氧气,通入氮气,进行退火——氮气氛围下降温——氦气氛围下拉出晶舟——进行下一批操作湿式制程:闲置状态下通入净化氮气气体——闲置状态下通入制程氦气气体——通入氮气气流和大量氧气——通入氮气气流和大量氧气,推入晶舟——通入氮气气流和大量氧气,开始升温——通入氮气气流和大量氧气,达到稳定温度——注入氧气并关掉氮气——稳定氧气气流——打开氢氧气流,并点燃——稳定氢气流——利用氧气和氢气进行蒸汽氧化反应——关闭氢气,通入氧气——关闭氧气,通入氮气——进行下一批操作湿式氧化具有较高的生长速率,干式氧化的生长速率比湿式的低,但干式氧化生长的薄膜品质比湿式的好。

薄的氧化层如屏蔽氧化层,衬垫氧化层,栅极氧化层通常用干式氧化6.说明扩散处理扩散是一种物理现象,是因为分子受到热运动的驱动而使物质由浓度高的地方移向浓度低的地方7.说明为何离子注入可以可以取代扩散来对硅进行掺杂扩散无法单独控制掺杂物的浓度和接面深度,扩散是个等向过程。

离子注入能对掺杂物的浓度和掺杂物的分部提供较佳的控制8.举出至少三种高温沉积制程。

半导体制造概论(完整流程详解)

半导体制造概论(完整流程详解)近几年來,随着电子科技、网路等相关技术的进步,以及全球电子市场消费水平的提升,个人计算机、多媒体、工作站、网路、通信相关设备等电子产品的需求激增,带动整个世界半导体产业的蓬勃发展,而在台湾,半导体业更俨然成为维系国家经济动脉的一个主力。

基本上半导体制造为一垂直分工细密且高附加价值的产业,其快速的成长也会带动其他外围产业的繁荣,下图所示为一典型的半导体产业体系架构。

在这个体系中,半导体制造,也就是一般所称的晶圆加工(Wafer fabrication),是资金与技术最为密集之处,伴随着晶圆加工的上游产业则包括产品设计(IC design)、晶圆制造(Wafer manufacture)、以及光罩(Photo mask)制造等,下游产业则更为庞大,其中包括一般所称半导体后段制程(Back-end processes)的IC 封装(Packaging)、测试(T esting)、包装(Assembly ),以及外围的导线架制造(Lead-frame manufacture )、連接器制造(Connector manufacture)、电路板制造(Board manufacture)等,此一结合紧密的产业体系,形成了今日台湾经济命脉之所系。

一、IC 设计(IC design)二、晶圆制造(Wafer manufacture)(一)长晶(CRYSTAL GROWTH)长晶是从硅砂中(二氧化硅)提煉成单晶硅,其制造过程是将硅石(Silica)或硅酸盐(Silicate)如同冶金一样,放入爐中熔解提煉,形成冶金级硅。

由于冶金级硅中尚含有杂质,因此,必须再用分馏及还原的方法将其纯化,形成电子级硅。

虽然电子级硅所含的硅的纯度很高,可达99.9999 99999 %,但是结晶方式还是很杂亂,又称为多晶硅,必须重排成单晶结构才可,因此再将电子级硅置入坩埚内加温融化,其系先将温度降低至一设定点,再以一块单晶硅为『晶种』,置入坩埚内,让融化的硅沾附在晶种上,再将晶种以边拉边旋转方式抽離坩埚,而沾附在晶种上的硅亦随之冷凝,形成与晶种相同排列的结晶。

列出光刻工艺流程半导体制造技术导论

列出光刻工艺流程半导体制造技术导论下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!半导体制造技术导论:光刻工艺流程解析在现代科技的微观世界中,半导体制造技术扮演着至关重要的角色,其中光刻工艺是这一领域的核心步骤。

半导体制造技术导论萧宏台译本

半导体制造技术导论萧宏台译本

《半导体制造技术导论》是一本介绍半导体制造技术的著作,由萧宏台翻译成中文。

这本书从多个角度全面介绍了半导体制造技术的基本原理、工艺流程、设备和材料等内容。

萧宏台的译本在学术界和工程领域都有一定的影响,因为他在翻译过程中注重准确性和严谨性,使得读者能够更好地理解和掌握半导体制造技术的相关知识。

这本书对于从事半导体制造和相关领域的研究人员、工程师以及对该领域感兴趣的学生都具有一定的参考价值。

总的来说,萧宏台译本的《半导体制造技术导论》是一本值得阅读的权威著作。

半导体制造导论

半导体制造导论..................................... 砖爲w/pr#................................................................................. 第五章早刖1至少列出三种重要的加热制程氧化,退火,沉积是三种重要的加热制程2说明直立式和水平式炉管的基本系统并列出直立式炉管的优点气体输送系统,制程炉管,控制系统,气体排放系统,装载系统。

LPCVD的话再加上真空系统优点:占地面积小,微粒污染较低,能够处理大量的晶圆,均匀性较佳,维修成本较低3?说明氧化制程氧化是最重要的制程之一,它是一种添加制程,把氧气加到硅晶圆上,在晶圆表面形成二氧化硅4?说明氧化前清洗的重要性氧化制程前的硅晶圆表面清洗是十分重要的,因为受到污染的表面会提供成核位置而形成二氧化硅多晶体层5?辨认干式氧化和湿式氧化制程及应用的差异性干式制程:闲置状态下通入净化氮气气体——闲置状态下通入制程氦气气体——在制程氮气流下把晶舟推入反映炉管一一氮气氛围下升温一一氮气分为下达到稳定温度一一关闭氮气,通入氧气和氯化氢——关闭氧气,通入氮气,进行退火——氮气氛围下降温——氦气氛围下拉出晶舟一一进行下一批操作湿式制程:闲置状态下通入净化氮气气体------ 闲置状态下通入制程氦气气体通入氮气气流和大量氧气一一通入氮气气流和大量氧气,推入晶舟一一通入氮气气流和大量氧气,开始升温一一通入氮气气流和大量氧气,达到稳定温度一一注入氧气并关掉氮气一一稳定氧气气流――打开氢氧气流,并点燃一一稳定氢气流一一利用氧气和氢气进行蒸汽氧化反应――关闭氢气,通入氧气一一关闭氧气,通入氮气一一进行下一批操作湿式氧化具有较高的生长速率,干式氧化的生长速率比湿式的低,但干式氧化生长的薄膜品质比湿式的好。

薄的氧化层如屏蔽氧化层,衬垫氧化层,栅极氧化层通常用干式氧化6?说明扩散处理扩散是一种物理现象,是因为分子受到热运动的驱动而使物质由浓度高的地方移向浓度低的地方7?说明为何离子注入可以可以取代扩散来对硅进行掺杂扩散无法单独控制掺杂物的浓度和接面深度,扩散是个等向过程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

石英基板 光刻工艺:借助光刻胶将印在掩膜上的图形结构转移到硅片表面 光刻胶:批光照后能具有抗蚀能力的高分子化合物,用于在半导 体基件表面产生电路的形状。 正光刻胶:受光照部分发生降解反应而能为显影液所溶解。留下 的非曝光部分的图形与掩模版一致。 负光刻胶:受光照部分产生交链反应而成为不溶物,非曝光部分 22 被显影液溶解,获得的图形与掩模版图形互补。

2

目标

读完本章之后,你应该能够:

• • • •

熟悉半导体相关术语的使用 描述基本的集成电路制造流程 简明的解释每一个制程步骤 将你的工作或制造产品与半导体制造工艺 相结合,并建立它们之间的联系

3

主题

• • • • 简介 集成电路组件和设计 半导体制程 未来的走向

4

简介

• • • • • 第一个晶体管,AT&T贝尔实验室, 1947 第一个单晶锗, 1950 第一个单晶硅, 1952 第一个集成电路组件, 德州仪器, 1958 第一个硅集成电路芯片, 费尔查德照相机 公司, 1961

半导体制程技术导论 Chapter 1导论

王红江, Ph. D. fwang@ 江苏科技大学

1

参考书籍

• Hong Xiao. Introduction to Semiconductor Manufacturing Technology. SPIE. 2012 • 萧宏. 半导体制造技术导论. 电子工业出版社, 2012 • 施敏. 半导体器件物理与工艺. 苏州大学出版社, 2002 • Peter Van Zant. 芯片制造——半导体工艺制程实用 教程. 电子工业出版社 • Michael Quirk, Julian Serda. 半导体制造技术. 电子 工业出版社. 2009

5,000 ~ 100,000 100,000 ~ 10,000,000 10,000,000~ 1,000,000,000 超过 1,000,000,000

超大规模集成电路(Ultra Large Scale

Integration)

特大规模集成电路(Super Large Scale

Integration)

光刻和倍缩光刻

图片提供:SGS Thompson

23

晶圆制程

材料 无尘室生产厂房 金属化 晶圆 热处理 光刻版 光刻 设计

24

化学机械 研磨

介质沉积

测试

离子注入与 光刻胶

蚀刻与光 刻胶

封装

最后测试

原子的大小

16

IC组件的限制

• • • • 原子大小: 数个埃( Å) 形成一个组件需要一些原子 一般最后的限制在100Å或 0.01 微米 大概30 个硅原子

17

IC设计: 第一颗IC

照片提供: 德州仪器

18

IC设计: CMOS反相器

Vss

NMOS

Vin

Vdd

(a)

PMOS Vout

浅沟绝缘槽(STI) N-信道组件区 N-通道 Vt N-通道LDD N-通道S/D P-信道组件区 P-通道 Vt P-通道LDD P-通道S/D

12

整体的半导体工业道路图

1995 最小图形尺寸(mm) 0.35 1997 0.25 1999 0.15 1G 0.003 13M 0.2 7M 0.05 200~300 2001 0.13 4G 0.001 25M 0.1 13M 0.03 300 2004 0.10 16G 0.0005 50M 0.05 25M 0.02 300 2007 0.07 64G 0.0002 90M 0.02 40M 0.01 300~400

(b)

P型井区 第一层 金属

W n+ n+ P型井区 P型垒晶层i P型晶源

多晶硅匣极和局部互连

第一层金属,AlCu PMD STI p+ N型井区 p+

N型井 Contact 区

(c)

19

实际CMOS反相器版图

20

CMOS反相器的布局图和光刻版

相位移光刻版展示图 (光刻/倍缩光刻)

薄胶膜 铬金属图案 相位移涂布物

8

1961年费尔查德摄影机公司在硅晶 圆上制出的第一个集成电路

照片提供:Fairchild Semiconductor International

9

摩尔定律

• 1964年哥登‧摩尔(英特尔公司的共同创始人 之一) • 价格不变之下,计算机芯片上的组件数目, 几乎每12个月就增加一倍 • 1980年代减缓至每18个月 • 到目前仍属正确,预期可以维持到20152020年

13

DRAM 64M 256M 位数/芯片 位的单位成本(千分之 0.017 0.007

一美分)

微处理器 4M 晶体管数目/cm2 晶体管的单位成本(千 1

分之一美分)

7M 0.5 4M 0.1 200

ASIC 晶体管数目/cm2

晶体管的单位成本(千 分之一美分)

2M 0.3 200

晶圆尺寸 (mm)

10

摩尔定律(英特尔版本)

Transistors

Pentium III

10M 1M 100K

8086 4040 8080 80286 80486 80386

Pentium

10K

1KБайду номын сангаас

1975

1980

1985

1990

1995

2000

11

IC的尺度--集成电路芯片的积体化层级

积体化层级

小型集成电路(Small Scale Integration)

芯片尺寸与晶圆尺寸的相对性展示

芯片 或晶 粒

以0.28微米技术制造的 晶粒

以0.20微米技术 以0.14微米 技术

14

1997年NEC 制造最小的晶体管

下匣极

源极 n+ 上匣极 介电质 汲极 n+

超浅接面

P型芯片

小于0.014 微米 匣极的宽度

照片提供:NEC Corporation

15

IC几何上的限制

5

第一个晶体管, 贝尔实验室, 1947

照片提供:AT&T 档案财产,授 权同意本书翻 印使用

6

第一个晶体管的发明者

约翰‧巴定,威廉‧肖克莱 和 华特‧布莱登

照片提供:Lucent Technologies Inc.

7

1958年德州仪器的杰克克毕制造出 的第一个集成电路芯片(棒)

照片提供: 德州仪器

缩写

SSI

芯片内的组件数目

2 ~ 50

中型集成电路(Medium Scale Integration)

大规模集成电路(Large Scale Integration) 极大规模集成电路(Very Large Scale

Integration)

MSI

LSI VLSI ULSI SLSI

50 ~ 5,000