A Low Dropout, CMOS Regulator with High PSR over Wideband Frequencies

LM1085

−40˚C to 150˚C

Electrical Characteristics

Typicals and limits appearing in normal type apply for TJ = 25˚C. Limits appearing in Boldface type apply over the entire junction temperature range for operation.

60

LM1085-3.3, VIN = 6.3V

60

LM1085-5.0, VIN = 8V

60

LM1085-12 VIN = 15V

54

Adjust Pin Current LM1085

5.5

A

0.5

A

5.5

A

5.5

A

5.5

A

5.0

10.0

mA

5.0

10.0

mA

5.0

10.0

mA

5.0

10.0

mA

150˚C -65˚C to 150˚C 260˚C, to 10 sec

2000V

Operating Ratings (Note 1)

Junction Temperature Range (TJ) (Note 3)

Control Section

−40˚C to 125˚C

Output Section

3-lead TO-220

−40˚C to + 125˚C

Simplified Schematic

Part Number LM1085IS-ADJ LM1085ISX-ADJ LM1085IS-12 LM1085ISX-12 LM1085IS-3.3 LM1085ISX-3.3 LM1085IS-5.0 LM1085ISX-5.0 LM1085IT-ADJ LM1085IT-12 LM1085IT-3.3 LM1085IT-5.0

Richtek RT9049 500mA LDO调压器说明书

1DS9049-01 April 2011Ordering InformationNote :Richtek products are :` RoHS compliant and compatible with the current require-ments of IPC/JEDEC J-STD-020.` Suitable for use in SnPb or Pb-free soldering processes.ApplicationszCDMA/GSM Cellular Handsets z Portable Information Appliancesz Laptop, Palmtops, Notebook Computers z HandHeld Instrumentsz Mini PCI & PCI-Express Cards z PCMCIA & New CardsPin ConfigurationsGeneral DescriptionThe RT9049 is a high-performance, 500mA LDO regulator,offering extremely high PSRR and ultra-low dropout. The RT9049 is designed for portable RF and wireless applications with demanding performance and space requirements. The RT9049 quiescent current is as low as 115μA, further prolonging the battery life. The RT9049 also works with low-ESR ceramic capacitors, reducing the amount of board space necessary which is critical for power applications in hand-held wireless devices. The RT9049 consumes typical 1.35μA in shutdown mode and has fast turn-on time less than 40μs. The other features include ultra-low dropout voltage, high output accuracy,current limiting protection, and high ripple rejection ratio.The RT9049 is available in the SOT-23-5 package.Features500mA, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatorzWide Operating Voltage Ranges : 2.2V to 5.5V z Low Dropout : 250mV at 500mA z Ultra-Low-Noise for RF Applicationz Ultra-Fast Response in Line/Load Transient z Current Limiting Protection z Thermal Shutdown Protectionz High Power Supply Rejection Ratioz Only 10μF Output Capacitor Required for Stability z 1.35μA Shutdown Currentz TTL-Logic-Controlled Shutdown Input z RoHS Compliant and Halogen FreeSOT-23-5(TOP VIEW)Marking InformationFor marking information, contact our sales representative directly or through a Richtek distributor located in your area.Typical Application CircuitVOUTRT904912 : 1.2V2DS9049-01 April 2011Functional Pin DescriptionFunction Block DiagramENAbsolute Maximum Ratings (Note 1)z Input Voltage, V IN----------------------------------------------------------------------------------------------------------6Vz EN, V EN----------------------------------------------------------------------------------------------------------------------6Vz Power Dissipation, P D @ T A = 25°CSOT-23-5--------------------------------------------------------------------------------------------------------------------0.4Wz Package Thermal Resistance (Note 2)SOT-23-5, θJA---------------------------------------------------------------------------------------------------------------250°C/WSOT-23-5, θJC--------------------------------------------------------------------------------------------------------------25°C/Wz Lead Temperature (Soldering, 10 sec.)-------------------------------------------------------------------------------260°Cz Junction T emperature-----------------------------------------------------------------------------------------------------150°Cz Storage T emperature Range--------------------------------------------------------------------------------------------−65°C to 150°C z ESD Susceptibility (Note 3)HBM (Human Body Mode)----------------------------------------------------------------------------------------------2kVMM (Machine Mode)------------------------------------------------------------------------------------------------------200VRecommended Operating Conditions (Note 4)z Junction T emperature Range--------------------------------------------------------------------------------------------−40°C to 125°C z Ambient T emperature Range--------------------------------------------------------------------------------------------−40°C to 85°C Electrical Characteristics(V IN =2.7V, V EN= V IN, C IN =1μF, C OUT = 10μF(Ceramic, X7R), T A = 25°C, unless otherwise specified)DS9049-01 April 20113Note 1. Stresses listed as the above“Absolute Maximum Ratings”may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.Note 2. θJA is measured in the natural convection at T A = 25°C on a low effective thermal conductivity single layer test board of JEDEC 51-3 thermal measurement standard. The case position of θJC is on the package top of the package. Note 3. Devices are ESD sensitive. Handling precaution is recommended.Note 4. The device is not guaranteed to function outside its operating conditions.Note 5. Quiescent, or ground current, is the difference between input and output currents. It is defined by I Q = I IN-I OUT under no load condition (I OUT = 0mA). The total current drawn from the supply is the sum of the load current plus the ground pin current.Note 6. Regulation is measured at constant junction temperature by using a 2ms current pulse. Devices are tested for loadregulation in the load range from 10mA to 500mA.DS9049-01 April 2011 45DS9049-01 April 2011Line Transient Response Time (100μs/Div)3.62.6V IN (1V/Div)20−20V OUT(20mV/Div)V IN = 2.6V to 3.6V, V OUT = 1.2V, I OUT = 100mATypical Operating CharacteristicsOutput Voltage vs. Temperature1.1001.1251.1501.1751.2001.2251.2501.2751.300-50-25255075100125Temperature O u tp u t V o l t a g e (V )(°C)Quiescent Current vs. Temperature8090100110120130140-50-25255075100125Temperature Q ui e s c e n t C u r r e n t (μA )(°C)Load Transient ResponseTime (500μs/Div)V IN = 2.75V, V OUT = 1.2V, I OUT = 10mA to 100mAV OUT (5mV/Div)I OUT(50mA/Div)Power On-Off from EN Time (100μs/Div)V EN (1V/Div)V OUT (0.5V/Div)V IN = 2.75V, V OUT = 1.2V, I OUT = 50mALine Transient ResponseTime (100μs/Div)3.62.6V IN (1V/Div)20−20V OUT(20mV/Div)V IN = 2.6V to 3.6V, V OUT = 1.2V, I OUT = 10mA6DS9049-01 April 2011PSRR-70-60-50-40-30-20-1001020101001000100001000001000000Frequency (Hz)P S R R (d B )Load Transient ResponseTime (500μs/Div)V OUT (5mV/Div)I OUT(100mA/Div)V IN = 2.75V, V OUT = 1.2V, I OUT = 10mA to 300mANoiseTime (10msDiv)V OUT(100μV/Div)V IN = 4.5V (By Battery), V OUT = 1.2V, No LoadNoiseTime (10msDiv)V OUT(100μV/Div)V IN = 4.5V (By Battery), V OUT = 1.2V, I OUT = 10mA7DS9049-01 April 2011Applications InformationLike any low-dropout regulator, the external capacitors used with the RT9049 must be carefully selected for regulator stability and performance. Using a capacitor more than 1μF on the RT9049 is suitable. The input capacitor must be located at a distance of not more than 0.5 inch from the input pin of the IC and returned to a clean analog ground.The capacitor with larger value and lower ESR (equivalent series resistance) provides better PSRR and line-transient response.The output capacitor must meet both requirements for minimum capacitance and ESR in all LDOs application.The RT9049 is designed specifically to work with low ESR ceramic output capacitor in space-saving and performance consideration. Using a ceramic capacitor whose value is at least 10μF with ESR is > 45m Ω on the RT9049 output ensures stability. The RT9049 still works well with output capacitor of other types due to the wide stable ESR range.Figure 1. shows the curves of allowable ESR range as a function of load current for various output capacitor values.Output capacitor of larger capacitance can reduce noise and improve load transient response, stability, and PSRR.The output capacitor should be located at less than 0.5inch from the VOUT pin of the RT9049 and returned to a clean analog ground.Figure 1.Region of Stable C OUT ESR vs. Load CurrentEnableThe RT9049 goes into sleep mode when the Enable pin is in a logic low condition. During this condition, the pass transistor, error amplifier, and bandgap are turned off,reducing the supply current to 1.35μA typical. The Enable pin may be directly tied to V IN to keep the part on. The Enable input is CMOS logic and cannot be left floating.PSRRThe power supply rejection ratio (PSRR) is defined as the gain from the input to output divided by the gain from the supply to the output. The PSRR is found to be ⎟⎟⎠⎞⎜⎜⎝⎛ΔΔ×=Supply Error Gain log 20 PSRR Note that when heavy load measuring, Δsupply will cause Δtemperature. And Δtemperature will cause Δoutputvoltage. So the heavy load PSRR measuring is includes temperature effect.Current LimitThe RT9049 contains an independent current limiter, which monitors and controls the pass transistor's gate voltage,limiting the output current to 0.6A (typ.). The output can be shorted to ground indefinitely without damaging the part.Thermal ConsiderationsFor continuous operation, do not exceed absolute maximum operation junction temperature. The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surroundings airflow and temperature difference between junction to ambient.The maximum power dissipation can be calculated by following formula :P D(MAX) = (T J(MAX) − T A ) / θJAWhere T J(MAX) is the maximum operation junction temperature, T A is the ambient temperature and the θJA is the junction to ambient thermal resistance.For recommended operating conditions specification of RT9049, the maximum junction temperature is 125°C. The junction to ambient thermal resistance θJA is layout dependent. For SOT-23-5 package, the thermal resistanceRegion of Stable C OUT ESR vs. Load Current0.010.11101000.10.20.30.40.5Load Current (mA)R e g i o n o f S t a b l e C O U T E S R (Ω)8DS9049-01 April 20119DS9049-01 April 2011Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.Richtek Technology CorporationHeadquarter5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C.Tel: (8863)5526789 Fax: (8863)5526611Richtek Technology CorporationTaipei Office (Marketing)5F, No. 95, Minchiuan Road, Hsintien City Taipei County, Taiwan, R.O.C.Tel: (8862)86672399 Fax: (8862)86672377Email:*********************Outline DimensionA1HLSOT-23-5 Surface Mount Package。

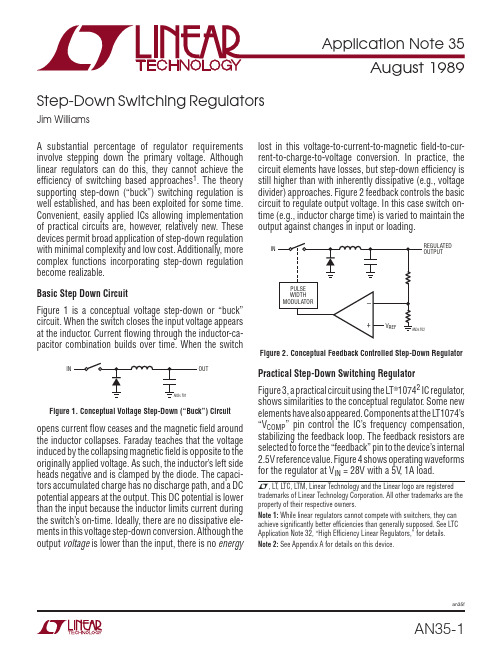

Step-Down Switching Regulators

Step-Down Switching RegulatorsJim WilliamsA substantial percentage of regulator requirements involve stepping down the primary voltage. Although linear regulators can do this, they cannot achieve the effi ciency of switching based approaches 1. The theory supporting step-down (“buck”) switching regulation is well established, and has been exploited for some time. Convenient, easily applied ICs allowing implementation of practical circuits are, however , relatively new. These devices permit broad application of step-down regulation with minimal complexity and low cost. Additionally, more complex functions incorporating step-down regulation become realizable.Basic Step Down CircuitF igure 1 is a conceptual voltage step-down or “buck” circuit. When the switch closes the input voltage appears at the inductor . Current fl owing through the inductor-ca-pacitor combination builds over time. When the switchINFigure 1. Conceptual Voltage Step-Down (“Buck”) Circuitopens current fl ow ceases and the magnetic fi eld around the inductor collapses. Faraday teaches that the voltage induced by the collapsing magnetic fi eld is opposite to the originally applied voltage. As such, the inductor’s left side heads negative and is clamped by the diode. The capaci-tors accumulated charge has no discharge path, and a DC potential appears at the output. This DC potential is lower than the input because the inductor limits current during the switch’s on-time. Ideally, there are no dissipative ele-ments in this voltage step-down conversion. Although the output voltage is lower than the input, there is no energylost in this voltage-to-current-to-magnetic fi eld-to-cur-rent-to-charge-to-voltage conversion. In practice, thecircuit elements have losses, but step-down effi ciency is still higher than with inherently dissipative (e.g., voltage divider) approaches. Figure 2 feedback controls the basic circuit to regulate output voltage. In this case switch on-time (e.g., inductor charge time) is varied to maintain the output against changes in input or loading.INFigure 2. Conceptual Feedback Controlled Step-Down RegulatorPractical Step-Down Switching RegulatorFigure 3, a practical circuit using the L T ®10742 IC regulator , shows similarities to the conceptual regulator . Some new elements have also appeared. Components at the L T1074’s “V COMP ” pin control the IC’s frequency compensation, stabilizing the feedback loop. The feedback resistors are selected to force the “feedback” pin to the device’s internal 2.5V reference value. F igure 4 shows operating waveforms for the regulator at V IN = 28V with a 5V , 1A load.L , L T , L TC, L TM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.Note 1: While linear regulators cannot compete with switchers, they can achieve signifi cantly better effi ciencies than generally supposed. See L TC Application Note 32, “High Effi ciency Linear Regulators,” for details.Note 2: See Appendix A for details on this device.T race A is the V SW pin voltage and T race B is its current. Inductor current 3 appears in T race C and diode current is T race D. Examination of the current waveforms allows determination of the V SW and diode path contributions to inductor current. Note that the inductor current’s waveform occurs on top of a 1A DC level. Figure 5 shows signifi cant duty cycle changes when V IN is reduced to 12V . The lower input voltage requires longer inductor charge times to maintain the output. The L T1074 controls inductor charge characteristics (see Appendix A for operating details), with resulting waveform shape and time proportioning changes.F igure 6 compares this circuit’s effi ciency with linear regulators in a common and important situation. Effi cient regulation under varying AC line conditions is a frequent requirement. The fi gure assumes the AC line has been transformed down to acceptable input voltages. The input voltages shown correspond to the AC line voltages given on the horizontal axis. Effi ciency for the LM317 and L T1086 linear regulators suffers over the wide input range.Note 3: Methods for selecting appropriate inductors are discussed in Appendix B.L1V INFigure 3. A Practical Step-Down Regulator Using the L T1074Figure 4. Waveforms for the Step-Down Regulator at V IN = 28V and V OUT = 5V at 1AAC LINE VOLTAGE800E F F I C I E N C Y (%)20406090100110120AN35 F06130801001030507090140Figure 6. Efficiency vs AC Line Voltage for the LT1074. LT1086 and LM317 Linear Regulators are Shown for ComparisonFigure 5. Waveforms for the Step-Down Regulator at V IN = 12V and V OUT = 5V at 1AA = 20V/DIVB = 1A/DIV D = 1A/DIVHORIZ = 5μs/DIVAN35 F04C = 0.2A/DIV ON 1A DC LEVELA = 20V/DIVB = 1A/DIV D = 1A/DIVHORIZ = 5μs/DIVAN35 F05C = 0.2A/DIV ON 1A DC LEVELThe L T1086 is notably better because its lower dropout voltage cuts dissipation over the range. Switching pre-regulation 4 can reduce these losses, but cannot equal the L T1074’s performance. The plot shows minimum effi ciency of 83%, with some improvement over the full AC line excursion. Figure 7 details performance. Effi ciency approaches 90% as input voltage rises. This is due to minimization of the effects of fi xed diode and L T1074 junc-tion losses as input increases. At low inputs these losses are a higher percentage of available supply, degrading effi ciency. Higher inputs make the fi xed losses a smaller percentage, improving effi ciency. Appendix D presents detail on optimizing circuitry for effi ciency.Note 4: See Reference 1.Dual Output Step-Down RegulatorFigure 8, a logical extension of the basic step-down con-verter , provides positive and negative outputs. The circuit is essentially identical to Figure 3’s basic converter with the addition of a coupled winding to L1. This fl oating winding’s output is rectifi ed, fi ltered and regulated to a –5V output. The fl oating bias to the L T1086 positive voltage regulator permits negative outputs by assigning the regulator’s output terminal to ground. Negative output power is set by fl ux pick-up from L1’s driven winding. With a 2A load at the +15 output the –5V output can supply over 500mA. Because L1’s secondary winding is fl oating its output may be referred to any point within the breakdown capability of the device. Hence, the secondary output could be 5V or , if stacked on the +15 output, 20V .Negative Output RegulatorsNegative outputs can also be obtained with a simple 2-ter-minal inductor . Figure 9 demonstrates this by essentially grounding the inductor and steering the catch diodes negative current to the output. A1 facilitates loop closure by providing a scaled inversion of the negative output to the L T1074’s feedback pin. The 1% resistors set the scale factor (e.g., output voltage) and the RC network around A1 gives frequency compensation. Waveforms for this circuit are reminiscent of Figure 5, with the exception that diodeINPUT VOL TAGEE F F I C I E N C Y (%)608010024AN35 F0740205070903010012101614202226183028Figure 7. Efficiency Plot for Figure 3. Higher Input Voltages Minimize Effects of Saturation Losses, Resulting in Increased EfficiencyL1: PULSE ENGINEERING, INC. #PE-6505028VINPUTAN35 F08Figure 8. Coupled Inductor Provides Positive and Negative Outputscurrent (T race D) is negative. T races A, B and C are V SW voltage, inductor current and V SW current respectively.Figure 11, commonly referred to as “Nelson’s Circuit,” provides the same function as the previous circuit, but eliminates the level-shifting op amp. This design accom-plishes the level shift by connecting the L T1074’s “ground” pin to the negative output. Feedback is sensed from circuit ground, and the regulator forces its feedback pin 2.5V above its “ground” pin. Circuit ground is common to input and output, making system use easy. Operating waveforms are essentially identical to Figure 10. Advantages of the previous circuit compared to this one are that the L T1074 package can directly contact a grounded heat sink and that control signals may be directly interfaced to the ground referred pins.The inductor values in both negative output designs are notably lower than in the positive case. This is necessitatedby the reduced loop phase margin of these circuits. Higher inductance values, while preferable for limiting peak cur-rent, will cause loop instability or outright oscillation.Current-Boosted Step-Down RegulatorF igure 12 shows a way to obtain signifi cantly higher output currents by utilizing effi cient energy storage in the L T1074 output inductor . This technique increases the duty cycle over the standard step-down regulator allowing more energy to be stored in the inductor . The increased output current is achieved at the expense of higher output voltage ripple.The operating waveforms for this circuit are shown in Figure 13. The circuit operating characteristics are similar to that of the step-down regulator (Figure 3). During the V SW (T race A) “on” time the input voltage is applied to one end of the coupled inductor . Current through the V SW pin (T race B) ramps up almost instantaneously (since inductor current (T race F) is present) and then slows as energy is stored in the core. The current proceeds into the inductor (T race D) and fi nally is delivered to the load. When the V SW pin goes off, current is no longer available to charge the inductor . The magnetic fi eld collapses, causing the V SW pin voltage to go negative. At this point similarity with the basic regulator vanishes. In this modifi ed version the output current (T race F) receives a boost as the magnetic fi eld collapses. This results when the energy stored in12V INPUT–5V OUTPUTFigure 9. A Negative Output Step-Down RegulatorFigure 10. Figure 9’s WaveformsA = 20V/DIVB = 1A/DIV D = 4A/DIVHORIZ = 5μs/DIVAN35 F10C = 4A/DIVthe core is transferred to the output. This current step circulates through C1 and D2 (T race E), somewhat increas-ing output voltage ripple. Not all the energy is transferred to the “1” winding. Current (T race C) will continue to fl ow in the “N” winding due to leakage inductance. A snubber network suppresses the effects of this leakage inductance. For lowest snubber losses the specifi ed tapped inductor is bifi lar wound for maximum coupling.Post Regulation-Fixed CaseIn most instances the L T1074 output will be applied directly to the load. Those cases requiring faster transient responseor reduced noise will benefi t from linear post regulation. In F igure 14 a 3-terminal regulator follows the L T1074 output. The L T1074 output is set to provide just enough voltage to the L T1084 to maintain regulation. The L T1084’s low dropout characteristics combined with a high circuit input voltage minimizes the overall effi ciency penalty.OUT VFigure 11. Nelson’s Circuit...A (Better) Negative Output Step-Down Regulator5V OUT10AVFigure 12. “Current Boosted” Step-Down Regulator. Boost Current is Supplied By Energy Stored in the Tapped InductorFigure 13. AC Current Flow for the Boosted RegulatorA = 50V/DIVB = 5A/DIVD = 10A/DIVE = 10A/DIVF = 10A/DIVHORIZ = 2μs/DIV AN35 F10C = 10A/DIVPost Regulation-Variable CaseSome situations require variable linear post regulation. F igure 15 does this with little effi ciency sacrifi ce. The L T1085 operates in normal fashion, supplying a variable 1.2V to 28V output. The remainder of the circuit forms a switched mode pre-regulator which maintains a small, fi xed voltage across the L T1085 regardless of its output voltage. A1 biases the L T1074 to produce whatever voltage is necessary to maintain the “E diodes” potential across the L T1085. A1’s inputs are balanced when the L T1085 output is “E diodes” above its input. A1 maintains this condition regardless of line, load or output voltage conditions. Thus, good effi ciency is maintained over the full range of output voltages. The RC network at A1 compensates the loop. Loop start-up is assured by deliberately introduc-ing a positive offset to A1. This is done by grounding A1’s appropriate balance pin (5), resulting in a positive 6mV offset. This increases amplifi er drift, and is normally considered poor practice, but causes no measurable error in this application.As shown, the circuit cannot produce outputs below the L T1085’s 1.2V reference. Applications requiring output adjustability down to 0V will benefi t from option “A” shown on the schematic. This arrangement replaces L1 with L2. L2’s primary performs the same function as L1 and its coupled secondary winding produces a negative bias output (–V). The full-wave bridge rectifi cation is necessitated by widely varying duty cycles. A2 and its at-tendant circuitry replace all components associated withthe L T1085 V ADJ pin. The L T1004 reference terminates the 10k to 250k feedback string at –1.2V with A2 provid-ing buffered drive to the L T1085 V ADJ pin. The negative bias allows regulated L T1085 outputs down to 0V . The –V potential derived from L2’s secondary varies consider-ably with operating conditions. The high feedback string values and A2’s buffering ensure stable circuit operation for “starved” values of –V .Low Quiescent Current RegulatorsMany applications require very wide ranges of power sup-ply output current. Normal conditions require currents in the ampere range, while standby or “sleep” modes draw only microamperes. A typical laptop computer may draw 1 to 2 amperes running while needing only a few hundred microamps for memory when turned off. In theory, any regulator designed for loop stability under no-load condi-tions will work. In practice, a converter’s relatively large quiescent current may cause unacceptable battery drain during low output current intervals. Figure 16’s simple loop effectively reduces circuit quiescent current from 6mA to only 150μA. It does this by utilizing the L T1074’s shutdown pin. When this pin is pulled within 350mV of ground the IC shuts down, pulling only 100μA. Comparator C1 combines with the L T1004 reference and Q1 to form a “bang-bang” control loop around the L T1074. The L T1074’s internal feedback amplifi er and voltage reference are by-passed by this loop’s operation. When the circuit output (T race C, Figure 17) falls slightly below 5V C1’s output (T race A) switches low, turning off Q1 and enabling theL1V IN5V OUTFigure 14. Linear Post-Reglator Improves Noise and T ransient ResponseL1: PULSE ENGINEERING, INC. #PE-51516L2: PULSE ENGINEERING, INC. #PE-6505035V INPUTOUTAN35 F15OPTION “A”(FOR OUTPUT DOWN TO 0V)SEE TEXT FOR DISCUSSIONL112V INPUT5V OUTFigure 15. Adjustable Linear Post-Regulator Maintains Efficiency Over Widely Varying Operating ConditionsFigure 16. A Simple Loop Reduces Quiescent Current to 150μAL T1074. The V SW pin (T race B) pulses at full duty cycle, forcing the output back above 5V . C1 then biases Q1 again, the L T1074 goes into shutdown, and loop action repeats.The frequency of this on-off control action is directly load dependent, with typical repetition rates of 0.2Hz at no load. Short on-times keep duty cycle low, resulting in the small effective quiescent current noted. The on-off operation combines with the LC fi ltering action in the regulator’s V SW line to generate an output hysteresis of about 50mV (again, see Figure 17, T race C).The loop performs well, but has two potential drawbacks. At higher output currents the loop oscillates in the 1kHz to 10kHz range, causing audible noise which may be objec-tionable. This is characteristic of this type of loop, and is the reason that ICs employing gated oscillators invariably produce such noise. Additionally, the control loops opera-tion causes about 50mV of ripple on the output. Ripple frequency ranges from 0.2Hz to 10kHz depending upon input voltage and output current.Figure 18’s more sophisticated circuit eliminates these problems with some increase in complexity. Quiescent current is maintained at 150μA. The technique shown is particularly signifi cant, with broad implication in battery powered systems. It is easily applied to a wide variety of regulator requirements, meeting an acknowledged need across a wide spectrum of applications.Figure 18’s signal fl ow is similar to Figure 16, but ad-ditional circuitry appears between the feedback divider and the L T1074. The L T1074’s internal feedback amplifi er and reference are not used. Figure 19 shows operatingFigure 17. The Low Quiescent Current Loop’s WaveformsV IN–+12VFigure 18. A More Sophisticated Loop Gives Better Regulation While Maintaining 150μA Quiescent CurrentA = 10V/DIVB = 10V/DIV HORIZ = 100μs/DIVAN35 F17C = 0.1V/DIV AC-COUPLED ON 5V DC LEVELwaveforms under no-load conditions. The output (T race A) ramps down over a period of seconds. During this time comparator A1’s output (T race B) is low, as are the 74C04 paralleled inverters. This pulls the V C pin (T race D) low, forcing the regulator to zero duty cycle. Simultaneously, A2 (T race C) is low, putting the L T1074 in its 100μA shutdown mode. The V SW pin (T race E) is off, and no inductor current fl ows. When the output drops about 60mV , A1 triggers and the inverters go high, pulling the V C pin up and biasing the regulator . The Zener diode prevents V C pin overdrive. A2 also rises, taking the IC out of shutdown mode. The V SW pin pulses the inductor at the 100kHz clock rate, causing the output to abruptly rise. This action trips A1 low, forcing the V C pin back low and shutting off V SW pulsing. A2 also goes low, putting the L T1074 into shutdown.This “bang-bang” control loop keeps the 5V output within the 60mV ramp hysteresis window set by the loop. Note that the loop oscillation period of seconds means the R1-C1time constant at V C is not a significant term. Because the L T1074 spends almost all of the time in shutdown, very little quiescent current (150μA) is drawn.Figure 20 shows the same waveforms with the load in-creased to 2mA. Loop oscillation frequency increases to keep up with the load’s sink current demand. Now, the V C pin waveform (T race D) begins to take on a fi ltered ap-pearance. This is due to R1-C1’s 10ms time constant. If the load continues to increase, loop oscillation frequency will also increase. The R1-C1 time constant, however , is fi xed. Beyond some frequency, R1-C1 must average loop oscillations to DC. At 7mA loading (Figure 21) loop fre-quency further increases, and the V C waveform (T race D) appears heavily fi ltered.Figure 22 shows the same circuit points at 2A loading. Note that the V C pin is at DC, as is the shutdown pin. Repetition rate has increased to the L T1074’s 100kHzFigure 19. Low Quiescent Current Regulator’s Waveforms with No Load (T races B, C and E Retouched for Clarity)Figure 20. Low Quiescent Current Regulator’s Waveforms at 2mA LoadingFigure 21. Low Quiescent Current Regulator’s Waveforms at 7mA Loading Figure 22. Low Quiescent Current Regulator’s Waveforms at 2A LoadingA = 0.1V/DIV AC-COUPLEDB = 20V/DIV HORIZ = 0.5 SECOND/DIVAN35 F19C = 20V/DIVD = 2V/DIVE = 10V/DIVA = 0.1V/DIV AC-COUPLEDB = 20V/DIV HORIZ = 20ms/DIVAN35 F20C = 20V/DIVD = 2V/DIVE = 10V/DIVA = 0.1V/DIV AC-COUPLEDB = 20V/DIV HORIZ = 10ms/DIVAN35 F21C = 20V/DIVD = 2V/DIVE = 10V/DIVA = 0.2V/DIV AC-COUPLEDB = 20V/DIV HORIZ—TRACES A AND E = 10μs/DIV TRACES B, C, D = 5ms/DIVAN35 F22C = 20V/DIVD = 2V/DIVE = 20V/DIVclock frequency. Figure 23 plots what is occurring, with a pleasant surprise. As output current rises, loop oscilla-tion frequency also rises until about 23Hz. At this point the R1-C1 time constant fi lters the V C pin to DC and the L T1074 transitions into “normal” PWM operation. With the V C pin at DC it is convenient to think of A1 and the inverters as a linear error amplifi er with a closed-loop gain set by the R2-R3 feedback divider . In fact, A1 is still duty cycle modulating, but at a rate far above R1-C1’s break frequency. The phase error contributed by C2 (which was selected for low loop frequency at low output currents) is dominated by the R1-C1 roll off and the C3 lead into A1. The loop is stable and responds linearly for all loads beyond 10mA. In this high current region the L T1074 is desirably “fooled” into behaving like a conventional step-down regulator .A formal stability analysis for this circuit is quite complex, but some simplifi cations lend insight into loop operation. At 250μA loading (20kΩ) C2 and the load form a decay time constant exceeding 30 seconds. This is orders of magnitude larger than R2-C3, R1-C1, or the L T1074’s 100kHz commutation rate. As a result, C2 dominates the loop. Wideband A1 sees phase shifted feedback, and very low frequency oscillations similar to Figure 19’s occur 5. Although C2’s decay time constant is long, its charge time constant is short because the circuit has low sourc-ing impedance. This accounts for the ramp nature of the oscillations.Increased loading reduces the C2-load decay time con-stant. Figure 23’s plot refl ects this. As loading increases,the loop oscillates at a higher frequency due to C2’s de-creased decay time. When the load impedance becomes low enough C2’s decay time constant ceases to dominate the loop. This point is almost entirely determined by R1 and C1. Once R1 and C1 “take over” as the dominant time constant the loop begins to behave like a linear system. In this region (e.g., above about 10mA, per Figure 23) the L T1074 runs continuously at its 100kHz rate. Now, C3 becomes signifi cant, performing as a simple feedback lead 6 to smooth output response. There is a fundamental trade-off in the selection of the C3 lead value. When the converter is running in its linear region it must dominate the loops time lag generated hysteretic characteristic. As such, it has been chosen for the best compromise between output ripple at high load and loop transient response.Despite the complex dynamics transient response is quite good. Figure 24 shows performance for a step from no load to 1A. When T race A goes high a 1A load appears across the output (T race C). Initially, the output sags al-most 200mV due to slow loop response time (the R1-C1 pair delay V C pin (T race B) response). When the L T1074 comes on response is reasonably quick and surprisingly well behaved considering circuit dynamics. The multi-time constant recovery 7 (“rattling” is perhaps more appropriate) is visible in T race C’s response.Note 5: Some layouts may require substantial trace area to A1’s inputs. In such cases the optional RC network around A1 ensures clean transitions at A1’s output.Note 6: “Zero Compensation” for all you technosnobs out there.Note 7: Once again, “multi-pole settling” for those who adore jargon.OUTPUT (mA)L O O P F R E Q U E N C Y (H z )4812162468AN35 F23101220Figure 23. Figure 18’s Loop Frequency vs Output Current. Note Linear Loop Operation Above 10mAFigure 24. Load T ransient Response for Figure 18A = 10V/DIVB = 2V/DIVHORIZ = 5ms/DIVAN35 F24C = 0.2V/DIV ON 5V DC LEVELF igure 25 plots effi ciency versus output current. High power effi ciency is similar to standard converters. Low power effi ciency is somewhat better , although poor in the lowest ranges. This is not particularly bothersome, as power loss is very small.The loop provides a controlled, conditional instability instead of the usually more desirable (and often elusive) unconditional stability. This deliberately introduced char-acteristic dramatically lowers converter quiescent current without sacrifi cing high power performance.a toroidal DC/DC converter comprised of L1, Q1 and Q2. Q1 and Q2 receive out of phase square wave drive from the 74C74 ÷ 4 fl ip-fl op stage and the L T1010 buffers. The fl ip-fl op is clocked from the L T1074 V SW output via the Q3 level shifter . The L T1086 provides 12V power for A1 and the 74C74. A1 biases the L T1074 regulator to produce the DC input at the DC/DC converter required to balance to loop. The converter has a voltage gain of about 20, resulting in high voltage output. This output is resistively divided down, closing the loop at A1’s negative input. Frequency compensation for this loop must accommodate the signifi -cant phase errors generated by the L T1074 confi guration, the DC/DC converter and the output LC fi lter . The 0.47μF roll-off term at A1 and the 100Ω-0.15μF RC lead network provide the compensation, which is stable for all loads.Figure 27 gives circuit waveforms at 500V output into a 100W load. T race A is the L T1074 V SW pin while T race B is its current. T races C and D are Q1 and Q2’s drain waveforms. The disturbance at the leading edges is due to cross-current conduction, which lasts about 300ns—a small percent-age of the cycle. T ransistor currents during this interval remain within reasonable values, and no overstress or dissipation problems occur . This effect could be eliminated with non-overlapping drive to Q1 and Q28, although there would be no reliability or signifi cant effi ciency gain. The 500kHz ringing on the same waveforms is due to excita-tion of transformer resonances. These phenomena are not deleterious, although L1’s primary RC damper is included to minimize them.All waveforms are synchronous because the fl ip-fl op drive stage is clocked from the L T1074 V SW output. The L T1074’s maximum 95% duty cycle means that the Q1-Q2 switches can never see destructive DC drive. The only condition allowing DC drive occurs when the L T1074 is at zero duty cycle. This case is clearly non-destructive, because L1 receives no power .Figure 28 shows the same circuit points as Figure 27, but at only 5mV output. Here, the loop restricts drive to the DC/DC converter to small levels. Q1 and Q2 chop just 70mV into L1. At this level L1’s output diode drops look large, but loop action forces the desired 0.005V output.OUTPUT CURRENTE F F I C I E N C Y (%)6080100 2.0AN35 F254020507090301000.51.01.52.5Figure 25. Efficiency vs Output Current for Figure 18. Standby Efficiency is Poor , But Power Loss Approaches Battery Self-DischargeWide Range, High Power , High Voltage Regulator BEFORE PROCEEDING ANY FURTHER, THE READER IS WARNED THAT CAUTION MUST BE USED IN THE CONSTRUCTION, TESTING AND USE OF THIS CIRCUIT . HIGH VOL TAGE, LETHAL POTENTIALS ARE PRESENT IN THIS CIRCUIT . EXTREME CAUTION MUST BE USED IN WORKING WITH AND MAKING CONNECTIONS TO THIS CIRCUIT . REPEAT : THIS CIRCUIT CONTAINS DANGER-OUS, HIGH VOL TAGE POTENTIALS. USE CAUTION.Figure 26 is an example of the L T1074 making a complex function practical. This regulator provides outputs from mil-livolts to 500V at 100W with 80% effi ciency. A1 compares a variable reference voltage with a resistively scaled version of the circuit’s output and biases the L T1074 switching regulator confi guration. The switcher’s DC output drivesNote 8: For an example of this technique see L TC Application Note 29, Figure 1.T 28V I N100μS O L I T A N T A L U F i g u r e 26. L T 1074 P e r m i t s H i g h V o l t a g e O u t p u t O v e r 100d B R a n g e w i t h P o w e r a n d E f f i c i e n c y .D A N G E R ! L e t h a l P o t e n t i a l s P r e s e n t —S e e T e x tThe L T1074’s switched mode drive to L1 maintains high effi ciency at high power , despite the circuits wide output range 9.Figure 29 shows output noise at 500V into a 100W load. Q1-Q2 chopping artifacts and transformer related ringing are clearly visible, although limited to about 80mV . The coherent noise characteristic is traceable to the synchro-nous clocking of Q1 and Q2 by the L T1074.A 50V to 500V step command into a 100W load produces the response of Figure 30. Loop response on both edgesis clean, with the falling edge slightly underdamped. This slew asymmetry is typical of switching confi gurations, because the load and output capacitor determine negative slew rate. The wide range of possible loads mandates a compromise when setting frequency compensation. The falling edge could be made critically or even over damped, but response time for other conditions would suffer . The compensation used seems a reasonable compromise.Note 9: A circuit related to the one presented here appears in the L TC Application Note 18 (Figure 13). Its linear drive to the step-up DC/DC converter forces dissipation, limiting output power to about 15W . Similar restrictions apply to Figure 7 in Application Note 6.Figure 27. Figure 26’s Operating Waveforms at 500V Output into a 100W LoadFigure 28. Figure 26’s Operating Waveforms at 0.005V OutputFigure 29. Figure 26’s Output Noise at 500V into a 100W Load. Residue is Composed of Q1-Q2 Chopping Artifacts and T ransformer Related Ringing. DANGER! Lethal Potentials Present—See TextFigure 30. 500V Step Response with 100W Load (Photo Retouched for Clarity). DANGER! Lethal Potentials Present—See TextA = 50V/DIVB = 5A/DIVHORIZ = 10μs/DIVAN35 F27C = 50V/DIVD = 50V/DIVA = 5V/DIVB = 50mA/DIVHORIZ = 10μs/DIVAN35 F28C = 0.1V/DIVD = 0.1V/DIVA = 0.05V/DIV AC-COUPLED ON 500V LEVELHORIZ = 20μs/DIVAN35 F29A = 100V/DIVHORIZ = 50ms/DIVAN35 F30。

DS_BL9110--1A Low Dropout Low Iq High PSRR CMOS LDO(EN,V1.1)

PCMCIA Cards and Wireless LAN Electrical appliances such as cameras, VCRS

DESCRIPTION

The BL9110 is a low-dropout regulator that operates the input voltage from 2.5V to 6V and delivers 1A load current. The BL9110 is available in two types, either fixed or adjustable output voltage. The output voltage of the fixed types is preset at an internally trimmed voltage 1V, 1.2V, 1.3V, 1.5V, 1.8V, 2.5V, 2.7V, 2.8V, 2.85V, 3.0V, 3.2V, 3.3V, 5V or can be made with options of the output range from 1V to 5V in 50mV increments. The output range of adjustable types is from 1V to 5V. The BL9110 consists of a voltage reference, an error amplifier, resistor net for setting output voltage, a current limit circuit for over-current and a thermal-shutdown circuit. A standby mode with ultra low supply current can be realized with the chip enable function. Since the packages for BL9110 are DFN-6, SOT-89-5, SOT-223-5, SOT-223-3, TO-263-3, TO-220-3, SOT-89-3, TO-252-3, TO92-3 and TO-252-5 with high power dissipation, high density mounting of the IC on board is possible.

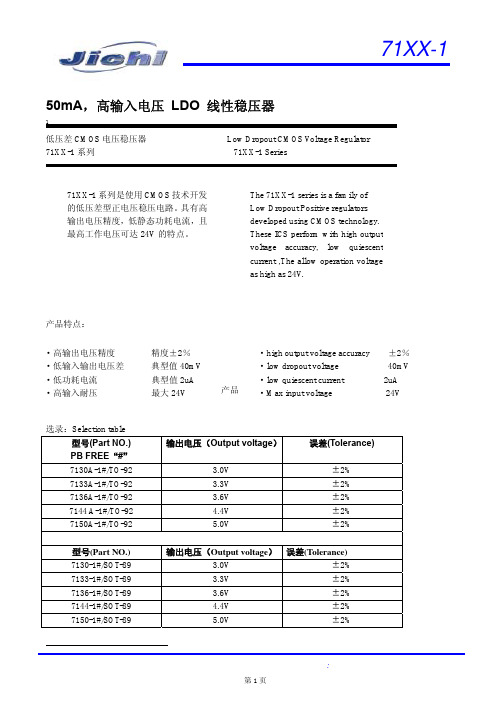

高压降稳压管7133

The 71XX-1 series is a family of Low Dropout Positive regulators developed using CMOS technology. These ICS perform with high output voltage accuracy, low quiescent current ,The allow operation voltage as high as 24V.

典型值 XX

50 50 100 400 2.0

0.2

最大值

XX *102%

24 100 85

4.0

单位 V

mA mV mV Ta μA

%/V

温度调整率

∆VOUT ∆Ta

IOUT =30mA -45℃ ≤Ta≤85℃

+/-0.3

mV/℃

注:

1. VOUT (T)& “XX” :规定的输出电压; XX:X.XV 例如:71(XX)A-1#;XX 为 30 时 :输出:3.0V。 2. VOUT (E) :有效输出电压( 即当 IOUT 保持一定数值,VIN = (VOUT (T)+0.8V)时的输出电压。) 3. Vdif :VIN1 –VOUT (E)’

71XX-1

50mA,高输入电压 LDO 线性稳压器

1

低压差 CMOS 电压稳压器 71XX-1 系列

Low Dropout CMOS Voltage Regulator 71XX-1 Series

71XX-1 系列是使用 CMOS 技术开发 的低压差型正电压稳压电路。具有高 输出电压精度,低静态功耗电流,且 最高工作电压可达 24V 的特点。

VIN1 :逐渐减小输入电压,当输出电压降为 VOUT (E) 的 98%时的输入电压。 VOUT (E)’= VOUT (E)X98%

S-818_1资料

Table 2 Pin No. Symbol Pin description 1 VIN Input voltage pin 2 VSS GND pin 3 ON/OFF Shutdown pin NC*1 No connection 4 5 VOUT Output voltage pin *1. The NC pin is electrically open. The NC pin can be connected to VIN or VSS.

1

2

3

Figure 2

元器件交易网

Rev.2.1_00

LOW DROPOUT CMOS VOLTAGE REGULATOR

S-818 Series

The S-818 Series is a positive voltage regulator developed by CMOS technology and featured by low dropout voltage, high output voltage accuracy and low current consumption. Built-in low on-resistance transistor provides low dropout voltage and large output current. A ceramic capacitor of 2 µF or more can be used as an output capacitor. A shutdown circuit ensures long battery life. The SOT-23-5 miniaturized package and the SOT-89-5 package are recommended for configuring portable devices and large output current applications, respectively.

LP3876-ADJ中文资料

LP3876-ADJ3A Fast Ultra Low Dropout Linear RegulatorGeneral DescriptionThe LP3876-ADJ fast ultra low-dropout linear regulators op-erate from a +2.5V to +7.0V input supply.These ultra low dropout linear regulators respond very quickly to step changes in load,which makes them suitable for low voltage microprocessor applications.The LP3876-ADJ is developed on a CMOS process which allows low quiescent current operation independent of output load current.This CMOS process also allows the LP3876-ADJ to operate under ex-tremely low dropout conditions.Dropout Voltage:Ultra low dropout voltage;typically 80mV at 300mA load current and 800mV at 3A load current.Ground Pin Current:Typically 6mA at 3A load current.Shutdown Mode:Typically 1µA quiescent current when the shutdown pin is pulled low.Adjustable Output Voltage:The output voltage may be programmed via two external resistors.Featuresn Ultra low dropout voltage n Low ground pin current n Load regulation of 0.08%n 1µA quiescent current in shutdown mode n Guaranteed output current of 3A DCn Available in TO-263and TO-220packages n Minimum output capacitor requirements n Overtemperature/overcurrent protectionn−40˚C to +125˚C junction temperature rangeApplicationsn Microprocessor power suppliesn GTL,GTL+,BTL,and SSTL bus terminators n Power supplies for DSPs n SCSI terminator n Post regulatorsn High efficiency linear regulators n Battery chargersnOther battery powered applicationsTypical Application Circuit20074445*See Application HintsSeptember 2003LP3876-ADJ 3A Fast Ultra Low Dropout Linear Regulator©2003National Semiconductor Corporation Connection Diagrams20074405Top View TO220-5Package Bent,Staggered Leads20074406Top View TO263-5PackagePin Description for TO220-5and TO263-5PackagesPin #LP3876-ADJName Function1SD Shutdown 2V IN Input Supply 3GND Ground 4V OUT Output Voltage 5ADJSet Output VoltageOrdering Information20074431Package Type Designator is "T"for TO220package,and "S"for TO263package.TABLE 1.Package Marking and Ordering InformationOutput Voltage Order Number Current DescriptionPackage Type Package Marking Supplied As:ADJ LP3876ES-ADJ 3A TO263-5LP3876ES-ADJ RailADJ LP3876ESX-ADJ 3A TO263-5LP3876ES-ADJ Tape and Reel ADJLP3876ET-ADJ3ATO220-5LP3876ET-ADJRailL P 3876-A D J 2LP3876-ADJ Block Diagram LP3876-ADJ3Absolute Maximum Ratings(Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Storage Temperature Range −65˚C to +150˚CLead Temperature (Soldering,5sec.)260˚C ESD Rating (Note 3)2kVPower Dissipation (Note 2)Internally Limited Input Supply Voltage (Survival)−0.3V to +7.5V Shutdown Input Voltage (Survival)−0.3V to 7.5V Output Voltage (Survival),(Note 6),(Note 7)−0.3V to +6.0V I OUT (Survival)Short Circuit ProtectedOperating RatingsInput Supply Voltage (Operating),(Note 10)2.5V to 7.0V Shutdown Input Voltage (Operating)−0.3V to 7.0VMaximum Operating Current (DC)3AOperating Junction Temp.Range−40˚C to +125˚CElectrical Characteristics LP3876-ADJLimits in standard typeface are for T J =25˚C,and limits in boldface type apply over the full operating temperature range .Unless otherwise specified:V IN =V O(NOM)+1.5V,I L =10mA,C OUT =10µF,V SD =2V.SymbolParameterConditionsTyp (Note 4)LP3876-ADJ (Note 5)UnitsMin Max V ADJ Adjust Pin Voltage V OUT +1.5V ≤V IN ≤7V 10mA ≤I L ≤3A 1.216 1.1981.1801.2341.253V I ADJ Adjust Pin Input Current V OUT +1.5V ≤V IN ≤7V 10mA ≤I L ≤3A 10100nA ∆V OL Output Voltage Line Regulation (Note 8)V OUT +1.5V ≤V IN ≤7.0V 0.020.06%∆V O /∆I OUTOutput Voltage Load Regulation (Note 8)10mA ≤I L ≤3A0.080.14%V IN -V OUT Dropout Voltage (Note 9)I L =300mA 80105125mVI L =3A 80010001200I GNDGround Pin Current In Normal Operation Mode I L =300mA5910mAI L =3A 61415I GND Ground Pin Current In Shutdown Mode V SD ≤0.3V 110µA-40˚C ≤T J ≤85˚C 50I O(PK)Peak Output Current V O ≥V O(NOM)-4%4.5A SHORT CIRCUIT PROTECTIONI SCShort Circuit Current6AL P 3876-A D J 4Electrical CharacteristicsLP3876-ADJ(Continued)Limits in standard typeface are for T J=25˚C,and limits in boldface type apply over the full operating temperature range. Unless otherwise specified:V IN=V O(NOM)+1.5V,I L=10mA,C OUT=10µF,V SD=2V.Symbol Parameter Conditions Typ(Note4)LP3876-ADJ(Note5)Units Min MaxSHUTDOWN INPUTV SDT Shutdown Threshold Output=High V IN2V Output=Low00.3T dOFF Turn-off delay I L=3A20µs T dON Turn-on delay I L=3A25µsI SD SD Input Current V SD=V IN1nA AC PARAMETERSPSRR Ripple Rejection V IN=V OUT+1VC OUT=10uFV OUT=3.3V,f=120Hz73dB V IN=V OUT+0.5VC OUT=10uFV OUT=3.3V,f=120Hz57ρn(l/f Output Noise Density f=120Hz0.8µVe n Output Noise Voltage BW=10Hz–100kHzV OUT=2.5V150µV(rms) BW=300Hz–300kHzV OUT=2.5V100Note1:Absolute maximum ratings indicate limits beyond which damage to the device may occur.Operating ratings indicate conditions for which the device isintended to be functional,but does not guarantee specific performance limits.For guaranteed specifications and test conditions,see Electrical Characteristics.The guaranteed specifications apply only for the test conditions listed.Some performance characteristics may degrade when the device is not operated under the listedtest conditions.Note2:At elevated temperatures,devices must be derated based on package thermal resistance.The devices in TO220package must be derated atθjA=50˚C/W(with0.5in2,1oz.copper area),junction-to-ambient(with no heat sink).The devices in the TO263surface-mount package must be derated atθjA=60˚C/W(with0.5in2,1oz.copper area),junction-to-ambient.See Application Hints.Note3:The human body model is a100pF capacitor discharged through a1.5kΩresistor into each pin.Note4:Typical numbers are at25˚C and represent the most likely parametric norm.Note5:Limits are guaranteed by testing,design,or statistical correlation.Note6:If used in a dual-supply system where the regulator load is returned to a negative supply,the output must be diode-clamped to ground.Note7:The output PMOS structure contains a diode between the V IN and V OUT terminals.This diode is normally reverse biased.This diode will get forward biasedif the voltage at the output terminal is forced to be higher than the voltage at the input terminal.This diode can typically withstand200mA of DC current and1Ampof peak current.Note8:Output voltage line regulation is defined as the change in output voltage from the nominal value due to change in the input line voltage.Output voltage load regulation is defined as the change in output voltage from the nominal value due to change in load current.Note9:Dropout voltage is defined as the minimum input to output differential voltage at which the output drops2%below the nominal value.Dropout voltage specification applies only to output voltages of2.5V and above.For output voltages below2.5V,the drop-out voltage is nothing but the input to output differential,since the minimum input voltage is2.5V.Note10:The minimum operating value for V IN is equal to either[V OUT(NOM)+V DROPOUT]or2.5V,whichever is greater.LP3876-ADJ5Typical Performance CharacteristicsUnless otherwise specified:T J =25˚C,C OUT =10µF,C IN =10µF,S/D pin is tied to V IN ,V OUT =2.5V,V IN=V O(NOM)+1.5V,I L =10mADropout Voltage Vs Output Load CurrentGround Current vs Output Load CurrentV OUT =5V2007446220074453Ground Current vs Output VoltageIL=3AShutdown I Q vs Junction Temperature2007445420074455DC Load Reg.vs Junction Temperature DC Line Regulation vs Temperature2007445820074459L P 3876-A D J 6Typical Performance Characteristics Unless otherwise specified:TJ=25˚C,C OUT=10µF,C IN=10µF,S/D pin is tied to V IN,V OUT=2.5V,V IN=V O(NOM)+1.5V,I L=10mA(Continued)V IN vs V OUT Over Temperature Noise vs Frequency2007446020074461Load Transient Response C IN=C OUT=10µF,OSCONLoad Transient ResponseC IN=C OUT=100µF,OSCON 2007448620074487Load Transient Response C IN=C OUT=100µF,POSCAPLoad Transient ResponseC IN=C OUT=10µF,TANTALUM2007448820074489LP3876-ADJ 7Typical Performance Characteristics Unless otherwise specified:T J =25˚C,C OUT =10µF,C IN =10µF,S/D pin is tied to V IN ,V OUT =2.5V,V IN =V O(NOM)+1.5V,I L =10mA (Continued)Load Transient Response C IN =C OUT =100µF,TANTALUMLoad Transient Response C IN =C OUT =10µF,OSCON2007449020074491Load Transient Response C IN =C OUT =100µF,OSCON Load Transient Response C IN =C OUT =100µF,POSCAP2007449220074493Load Transient Response C IN =C OUT =10µF,TANTALUM Load Transient Response C IN =C OUT =100µF,TANTALUM2007449420074495L P 3876-A D J 8Application HintsV IN RESTRICTIONS FOR PROPER START-UPTo prevent misoperation,ensure that V IN is below50mVbefore start-up is initiated.This scenario can occur in sys-tems with a backup battery using reverse-biased"blocking"diodes which may allow enough leakage current to flow intothe V IN node to raise it’s voltage slightly above ground whenthe main power is ing low leakage diodes or aresistive pull down can prevent the voltage at V IN from risingrge bulk capacitors connected to V IN mayalso cause a start-up problem if they do not discharge fullybefore re-start is initiated(but only if V IN is allowed to fallbelow1V).A resistor connected across the capacitor willallow it to discharge more quickly.It should be noted that theprobability of a"false start"caused by incorrect logic statesis extremely low.SETTING THE OUTPUT VOLTAGEThe output voltage is set using the resistors R1and R2(seeTypical Application Circuit).The output is also dependent onthe reference voltage(typically1.216V)which is measuredat the ADJ pin.The output voltage is given by the equation:V OUT=V ADJ x(1+R1/R2)This equation does not include errors due to the bias currentflowing in the ADJ pin which is typically about10nA.Thiserror term is negligible for most applications.If R1is> 100kΩ,a small error may be introduced by the ADJ biascurrent.The tolerance of the external resistors used contributes asignificant error to the output voltage accuracy,with1%resistors typically adding a total error of approximately1.4%to the output voltage(this error is in addition to the toleranceof the reference voltage at V ADJ).EXTERNAL CAPACITORSLike any low-dropout regulator,external capacitors are re-quired to assure stability.these capacitors must be correctlyselected for proper performance.INPUT CAPACITOR:An input capacitor of at least1µF isrequired.Ceramic or Tantalum may be used,and capaci-tance may be increased without limitOUTPUT CAPACITOR:An output capacitor is required forloop stability.It must be located less than1cm from thedevice and connected directly to the output and ground pinsusing traces which have no other currents flowing throughthem(see PCB Layout section).The minimum value of the output capacitance that can beused for stable full-load operation is10µF,but it may beincreased without limit.The output capacitor must have anESR value as shown in the stable region of the curve(be-low).ESR Curve20074470C FF(Feed Forward Capacitor)The capacitor C FF is required to add phase lead and helpimprove loop compensation.The correct amount of capaci-tance depends on the value selected for R1(see TypicalApplication Circuit).The capacitor should be selected suchthat the zero frequency as given by the equation shownbelow is approximately45kHz:Fz=45,000=1/(2xπx R1x C FF)A good quality ceramic with X5R or X7R dielectric should beused for this capacitor.SELECTING A CAPACITORIt is important to note that capacitance tolerance and varia-tion with temperature must be taken into consideration whenselecting a capacitor so that the minimum required amountof capacitance is provided over the full operating tempera-ture range.In general,a good Tantalum capacitor will showvery little capacitance variation with temperature,but a ce-ramic may not be as good(depending on dielectric type).Aluminum electrolytics also typically have large temperaturevariation of capacitance value.Equally important to consider is a capacitor’s ESR changewith temperature:this is not an issue with ceramics,as theirESR is extremely low.However,it is very important in Tan-talum and aluminum electrolytic capacitors.Both show in-creasing ESR at colder temperatures,but the increase inaluminum electrolytic capacitors is so severe they may notbe feasible for some applications(see Capacitor Character-istics Section).CAPACITOR CHARACTERISTICSCERAMIC:For values of capacitance in the10to100µFrange,ceramics are usually larger and more costly thantantalums but give superior AC performance for bypassinghigh frequency noise because of very low ESR(typically lessthan10mΩ).However,some dielectric types do not havegood capacitance characteristics as a function of voltageand temperature.Z5U and Y5V dielectric ceramics have capacitance thatdrops severely with applied voltage.A typical Z5U or Y5Vcapacitor can lose60%of its rated capacitance with half ofthe rated voltage applied to it.The Z5U and Y5V also exhibitLP3876-ADJ9Application Hints(Continued)a severe temperature effect,losing more than 50%of nomi-nal capacitance at high and low limits of the temperature range.X7R and X5R dielectric ceramic capacitors are strongly rec-ommended if ceramics are used,as they typically maintain a capacitance range within ±20%of nominal over full operat-ing ratings of temperature and voltage.Of course,they are typically larger and more costly than Z5U/Y5U types for a given voltage and capacitance.TANTALUM:Solid Tantalum capacitors are recommended for use on the output because their typical ESR is very close to the ideal value required for loop compensation.They also work well as input capacitors if selected to meet the ESR requirements previously listed.Tantalums also have good temperature stability:a good quality Tantalum will typically show a capacitance value that varies less than 10-15%across the full temperature range of 125˚C to −40˚C.ESR will vary only about 2X going from the high to low temperature limits.The increasing ESR at lower temperatures can cause oscil-lations when marginal quality capacitors are used (if the ESR of the capacitor is near the upper limit of the stability range at room temperature).ALUMINUM:This capacitor type offers the most capaci-tance for the money.The disadvantages are that they are larger in physical size,not widely available in surface mount,and have poor AC performance (especially at higher fre-quencies)due to higher ESR and ESL.Compared by size,the ESR of an aluminum electrolytic is higher than either Tantalum or ceramic,and it also varies greatly with temperature.A typical aluminum electrolytic can exhibit an ESR increase of as much as 50X when going from 25˚C down to −40˚C.It should also be noted that many aluminum electrolytics only specify impedance at a frequency of 120Hz,which indicates they have poor high frequency performance.Only aluminum electrolytics that have an impedance specified at a higher frequency (between 20kHz and 100kHz)should be used for the LP387X.Derating must be applied to the manufacturer’s ESR specification,since it is typically only valid at room temperature.Any applications using aluminum electrolytics should be thoroughly tested at the lowest ambient operating tempera-ture where ESR is maximum.PCB LAYOUTGood PC layout practices must be used or instability can be induced because of ground loops and voltage drops.The input and output capacitors must be directly connected to the input,output,and ground pins of the LP387X using traces which do not have other currents flowing in them (Kelvin connect).The best way to do this is to lay out C IN and C OUT near the device with short traces to the V IN ,V OUT ,and ground pins.The regulator ground pin should be connected to the exter-nal circuit ground so that the regulator and its capacitors have a "single point ground".It should be noted that stability problems have been seen in applications where "vias"to an internal ground plane were used at the ground points of the IC and the input and output capacitors.This was caused by varying ground potentials atthese nodes resulting from current flowing through the ground ing a single point ground technique for the regulator and it’s capacitors fixed the problem.Since high current flows through the traces going into V IN and coming from V OUT ,Kelvin connect the capacitor leads to these pins so there is no voltage drop in series with the input and output capacitors.RFI/EMI SUSCEPTIBILITYRFI (radio frequency interference)and EMI (electromagnetic interference)can degrade any integrated circuit’s perfor-mance because of the small dimensions of the geometries inside the device.In applications where circuit sources are present which generate signals with significant high fre-quency energy content (>1MHz),care must be taken to ensure that this does not affect the IC regulator.If RFI/EMI noise is present on the input side of the regulator (such as applications where the input source comes from the output of a switching regulator),good ceramic bypass ca-pacitors must be used at the input pin of the IC.If a load is connected to the IC output which switches at high speed (such as a clock),the high-frequency current pulses required by the load must be supplied by the capacitors on the IC output.Since the bandwidth of the regulator loop is less than 100kHz,the control circuitry cannot respond to load changes above that frequency.The means the effective output impedance of the IC at frequencies above 100kHz is determined only by the output capacitor(s).In applications where the load is switching at high speed,the output of the IC may need RF isolation from the load.It is recommended that some inductance be placed between the output capacitor and the load,and good RF bypass capaci-tors be placed directly across the load.PCB layout is also critical in high noise environments,since RFI/EMI is easily radiated directly into PC traces.Noisy circuitry should be isolated from "clean"circuits where pos-sible,and grounded through a separate path.At MHz fre-quencies,ground planes begin to look inductive and RFI/EMI can cause ground bounce across the ground plane.In multi-layer PCB applications,care should be taken in layout so that noisy power and ground planes do not radiate directly into adjacent layers which carry analog power and ground.OUTPUT NOISENoise is specified in two ways-Spot Noise or Output noise density is the RMS sum of all noise sources,measured at the regulator output,at a spe-cific frequency (measured with a 1Hz bandwidth).This type of noise is usually plotted on a curve as a function of fre-quency.Total output Noise or Broad-band noise is the RMS sum of spot noise over a specified bandwidth,usually several decades of frequencies.Attention should be paid to the units of measurement.Spot noise is measured in units µV/√Hz or nV/√Hz and total output noise is measured in µV(rms).The primary source of noise in low-dropout regulators is the internal reference.In CMOS regulators,noise has a low frequency component and a high frequency component,which depend strongly on the silicon area and quiescent current.Noise can be reduced in two ways:by increasing the transistor area or by increasing the current drawn by the internal reference.Increasing the area will decrease the chance of fitting the die into a smaller package.IncreasingL P 3876-A D J10Application Hints(Continued)the current drawn by the internal reference increases the total supply current(ground pin current).Using an optimized trade-off of ground pin current and die size,LP387X achieves low noise performance and low quiescent current operation.The total output noise specification for LP387X is presented in the Electrical Characteristics table.The Output noise den-sity at different frequencies is represented by a curve under typical performance characteristics.SHORT-CIRCUIT PROTECTIONThe LP3876-ADJ is short circuit protected and in the event of a peak over-current condition,the short-circuit control loop will rapidly drive the output PMOS pass element off.Once the power pass element shuts down,the control loop will rapidly cycle the output on and off until the average power dissipation causes the thermal shutdown circuit to respond to servo the on/off cycling to a lower frequency.Please refer to the section on thermal information for power dissipation calculations.SHUTDOWN OPERATIONA CMOS Logic level signal at the shutdown(SD)pin will turn-off the regulator.Pin SD must be actively terminated through a10kΩpull-up resistor for a proper operation.If this pin is driven from a source that actively pulls high and low (such as a CMOS rail to rail comparator),the pull-up resistor is not required.This pin must be tied to Vin if not used. DROPOUT VOLTAGEThe dropout voltage of a regulator is defined as the minimum input-to-output differential required to stay within2%of the nominal output voltage.For CMOS LDOs,the dropout volt-age is the product of the load current and the Rds(on)of the internal MOSFET.REVERSE CURRENT PATHThe internal MOSFET in LP3876-ADJ has an inherent para-sitic diode.During normal operation,the input voltage is higher than the output voltage and the parasitic diode is reverse biased.However,if the output is pulled above the input in an application,then current flows from the output to the input as the parasitic diode gets forward biased.The output can be pulled above the input as long as the current in the parasitic diode is limited to200mA continuous and1A peak.POWER DISSIPATION/HEATSINKINGThe LP3876-ADJ can deliver a continuous current of3A over the full operating temperature range.A heatsink may be required depending on the maximum power dissipation and maximum ambient temperature of the application.Under all possible conditions,the junction temperature must be within the range specified under operating conditions.The total power dissipation of the device is given by:P D=(V IN−V OUT)I OUT+(V IN)I GNDwhere I GND is the operating ground current of the device (specified under Electrical Characteristics).The maximum allowable temperature rise(T Rmax)depends on the maximum ambient temperature(T Amax)of the appli-cation,and the maximum allowable junction temperature (T Jmax):T Rmax=T Jmax−T AmaxThe maximum allowable value for junction to ambient Ther-mal Resistance,θJA,can be calculated using the formula:θJA=T Rmax/P DThe LP3876-ADJ is available in TO-220and TO-263pack-ages.The thermal resistance depends on amount of copperarea or heat sink,and on air flow.If the maximum allowablevalue ofθJA calculated above is≥60˚C/W for TO-220package and≥60˚C/W for TO-263package no heatsink isneeded since the package can dissipate enough heat tosatisfy these requirements.If the value for allowableθJA fallsbelow these limits,a heat sink is required.HEATSINKING TO-220PACKAGEThe thermal resistance of a TO220package can be reducedby attaching it to a heat sink or a copper plane on a PCboard.If a copper plane is to be used,the values ofθJA willbe same as shown in next section for TO263package.The heatsink to be used in the application should have aheatsink to ambient thermal resistance,θHA≤θJA−θCH−θJC.In this equation,θCH is the thermal resistance from the caseto the surface of the heat sink andθJC is the thermal resis-tance from the junction to the surface of the case.θJC isabout3˚C/W for a TO220package.The value forθCH de-pends on method of attachment,insulator,etc.θCH variesbetween1.5˚C/W to2.5˚C/W.If the exact value is unknown,2˚C/W can be assumed.HEATSINKING TO-263PACKAGEThe TO-263package uses the copper plane on the PCB asa heatsink.The tab of these packages are soldered to thecopper plane for heat sinking.Figure1shows a curve for theθJA of TO-263package for different copper area sizes,usinga typical PCB with1ounce copper and no solder mask overthe copper area for heat sinking.As shown in the figure,increasing the copper area beyond1square inch produces very little improvement.The minimumvalue forθJA for the TO-263package mounted to a PCB is32˚C/W.Figure2shows the maximum allowable power dissipationfor TO-263packages for different ambient temperatures,assumingθJA is35˚C/W and the maximum junction tempera-ture is125˚C.20074432FIGURE1.θJA vs Copper(1Ounce)Area for TO-263packageLP3876-ADJ11Application Hints(Continued)20074433FIGURE 2.Maximum power dissipation vs ambienttemperature for TO-263packageL P 3876-A D J 12LP3876-ADJ Physical Dimensions inches(millimeters)unless otherwise noted ArrayTO2205-lead,Molded,Stagger Bend Package(TO220-5)NS Package Number T05DFor Order Numbers,refer to the“Ordering Information”section of this document.13Physical Dimensionsinches (millimeters)unless otherwise noted (Continued)TO2635-Lead,Molded,Surface Mount Package (TO263-5)NS Package Number TS5BFor Order Numbers,refer to the “Ordering Information”section of this document.LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Americas Customer Support CenterEmail:new.feedback@ Tel:1-800-272-9959National SemiconductorEurope Customer Support CenterFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National Semiconductor Asia Pacific Customer Support CenterEmail:ap.support@National SemiconductorJapan Customer Support Center Fax:81-3-5639-7507Email:jpn.feedback@ Tel:81-3-5639-7560L P 3876-A D J 3A F a s t U l t r a L o w D r o p o u t L i n e a r R e g u l a t o rNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

SIIS1142 电压稳压器

Features

• Output voltage :

2.0 V to 12.0 V, selectable in 0.1 V step

• Low equivalent series resistance capacitor : Ceramic capacitor of 0.1 μF or more can be used as the I/O capacitor.

S-1142 Series

© Seiko Instruments Inc., 2009-2010

HIGH-WITHSTAND VOLTAGE LOW CURRENT CONSUMPTION LOW DROPOUT CMOS VOLTAGE REGULATOR

Rev.2.0_00

Remark 1. Please contact our sales office for products with an output voltage other than those listed above or type A products.

2. Please select products of environmental code = U for Sn 100%, halogen-free products.

• Output current :

During shutdown: 0.1 μA typ., 1.0 μA max. (Tj = −40°C to +105°C) 200 mA (at VIN ≥ VOUT(S) + 2.0 V)*1

• Built-in overcurrent protector :

HSOP-6 (+85°C supported) S-1142B20I-E6T1U S-1142B25I-E6T1U S-1142B27I-E6T1U S-1142B28I-E6T1U S-1142B2JI-E6T1U S-1142B30I-E6T1U S-1142B32I-E6T1U S-1142B33I-E6T1U S-1142B35I-E6T1U S-1142B37I-E6T1U S-1142B40I-E6T1U S-1142B50I-E6T1U S-1142B80I-E6T1U

美国半导体CM3202-02 DDR VDDQ和VTT终端电压调节器数据手册说明书