DSP2812EV管理器(转)

Dsp2812芯片管脚说明(中文)

XHOLD

E7

159

—

I

ห้องสมุดไป่ตู้

PU

XHOLDA

K10

82

—

O/Z

—

XHOLD 和 XHOLDA 信号同时发出。当

XHOLDA 有效(低)时外部器件只能使

用外部总线

XZCS0AND1

P1

44 88 133

— — —

O/Z O/Z O/Z

— — —

XINTF 区域 0 和区域 1 的片选,当访问 XINTF 区域 0 或 1 时有效(低) XINTF 区域 2 的片选。 当访问 XINTF 区域 2 时有效(低) XINTF 区域 6 和 7 的片选。当访问区域 6 或 7 时有效(低) 写有效。有效时为低电平。写选通信号是 每个区域操作的基础,由 XTIMINGx 寄存 器的前一周期、当前周期和后一周期的值 确定 读有效。低电平读选通。读选通信号是每 个区域操作的基础,由 XTIMINGx 寄存器 的前一周期、当前周期和后一周期的值确 定。注意: XRD 和 XWE 是互斥信号 通常为高电平,当为低电平时表示处于写 周期,当为高电平时表示处于读周期 续表

Dsp2812 芯片管脚说明

图 1-3 176 引脚 LQFP 封装顶视图

图 1-4 128 引脚 PBK 封装顶视图

表 1-2 引脚号 名 字 179 针 GHH 封装 XA[18] XA[17] XA[16] XA[15] XA[14] XA[13] XA[12] XA[11] XA[10] XA[9] XA[8] XA[7] XA[6] XA[5] XA[4] XA[3] XA[2] XA[1] XA[0] XD[15] XD[14] XD[13] XD[12] XD[11] XD[10] XD[9] XD[8] XD[7] XD[6] XD[5] XD[4] XD[3] XD[2] XD[1] XD[0] D7 B7 A8 B9 A10 E10 C11 A14 C12 D14 E12 F12 G14 H13 J12 M11 N10 M2 G5 A9 B11 J10 L14 N9 L9 M8 P7 L5 L3 J5 K3 J3 H5 H3 G3 176 针 PGF 封装 158 156 152 148 144 141 138 132 130 125 121 118 111 108 103 85 80 43 18 147 139 97 96 74 73 68 65 54 39 36 33 30 27 24 21 128 针 PBK 封装 — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — —

“简简单单DSP”系列学习活动——第七期事件管理器——通用定时器

“简简单单DSP”系列学习活动第七期事件管理器——通用定时器事件管理器(EV)强大的功能使它特别适用于运动控制和电机控制领域。

DSP 有两个相同的事件管理器EVA、EVB。

每个事件管理器模块包括通用定时器CP、全比较单元、可编程的死区发生器,PWM波形发生器、捕获单元CAP和和正交编码单元,A/D转换器的外部启动信号,功率驱动保护单元、EV寄存器以及EV中断等多个部分。

每一个EV还包含两路单独的PWM输出。

事件管理器的接口框图下图所示:从图中我们可以看出,每一个事件管理器模块都包含有:两个通用定时器、3个比较单元、三个捕获单元、一个正交编码电路,还可以有外部时钟、外部触发功率保护模块等。

常用的就是通用定时器、全比较PWM单元、和输入捕获单元,下面重点介绍这三个单元。

一、通用定时器CP1、通用定时器有四个中断:A、通用定时器1上溢中断B、通用定时器下溢中断C、通用定时器比较中断D、通用定时器周期中断这四个中断标志位在EVA中断标志寄存器A(EVAIFRA)中,这四个中断的使能位在EVA屏蔽寄存器EVAIMRA中设置。

2、通用定时器有三个16位的和定时比较有关的寄存器:A、通用定时器计数寄存器TXCNTB、通用定时器周期寄存器TxPRC、通用定时器比较寄存器TXCMPR通用定时器计数寄存器TxCNT根据通用定时器的时钟和计数模式开始计数,不停的和周期寄存器和比较寄存器从而产生中断或者各种事件。

当工作在定时器的模式时,TxCNT得值和TxPR中设置的值比较,当比较匹配后的一个时钟后,产生相应的事件当工作在比较的模式时,TxCNT得值和TxCMPR中设置的值比较,当比较匹配后的一个时钟后,产生相应的比较事件TxPR和TxCMPR都是带有影子寄存器的,在一个周期的任何时刻都可以对这两个寄存器进行读写,读写的是他们的影子寄存器。

对于TxCMPR,只有当TxCON 寄存器指定的特定条件满足时,影子寄存器中的值才加载到比较寄存器中;对于周期寄存器,只有当计数寄存器为0时,影子寄存器的值才能重新加载到周期寄存器。

DSP2812

Guangxi University of Science and Technology 课程设计说明书实验课程:DSP原理与应用实验内容:基于TMS320X2812的Led显示控制系统设计院(系):计算机学院专业:通信工程班级:101班学生姓名:刘金龙学号:201000402024指导教师:袁浩浩2013年7 月3 日目录1. 序言 (2)2.设计任务 (2)3.实验目的 (2)4.设计内容 (3)5.实验原理 (2)6.总体设计 (7)7.实验总结 (16)8.参考资料 (17)序言DSP芯片的特点DSP芯片,也称数字信号处理器,是一种具有特殊结构的微处理器。

DSP芯片的内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作,提供特殊的DSP指令,可以用来快速的实现各种数字信号处理算法。

根据数字信号处理的要求,DSP芯片一般具有如下的一些主要特点:⑴在一个指令周期内可完成一次乘法和一次加法。

⑵程序和数据空间分开,可以同时访问指令和数据。

⑶片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问。

⑷具有低开销或无开销循环及跳转的硬件支持。

⑸快速的中断处理和硬件I/O支持。

⑹具有在单周期内操作的多个硬件地址产生器。

⑺可以并行执行多个操作。

⑻支持流水线操作,使取指、译码和执行等操作可以重叠执行。

⑼与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。

1.设计任务:1.1基于TMS320X2812的Led显示控制系统设计要求:(1)绘制系统框图(VISIO);(2)包括复位电路设计、JTAG接口设计、时钟电路设计、电源设计等,并且用Protel 软件绘制原理图;(3)编写程序,实现流水灯;(4)系统理论分析和设计陈述;(5)设计过程、源代码和注释、设计说明书。

2.实验目的:⑴学习并了解DSP开发版的基本原理;⑵学习并了解TMS320X2812芯片的基本结构和原理;⑶熟悉流水灯的软件实现原理和硬件设计;⑷熟悉Emulator方式下的程序调试规程,并最终能够熟练掌握在DSP软硬件环境下的程序开发流程;能够对现有器件进行简单地编程,实现各种简单地显示控制。

DSP 2812中文手册

第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x 系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征TMS320C28x系列DSP的CPU与外设(上)·2·注:‡“S”是温度选择(-40℃~ +125℃)的特征化数据,仅对TMS是适用的。

‡‡产品预览(PP):在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI):在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包括对所有参数的测试。

SR-DSP2812V20开发套件使用手册

SR-DSP2812V20 开发套件使用手册(版本:1.0)长沙赛睿技术有限公司前言感谢您购买本公司的产品,在使用本产品前,请仔细阅读本使用说明书。

本用户指南是TMS320F2812 嵌入式DSP 控制模板硬件使用说明书,详细描述了SR-DSP2812 的硬件构成、原理,以及它的使用方法和编程指导。

如果您有任何意见和建议请发送邮件至:cyrui@。

同时欢迎您访问我们的网站,获取更多产品信息。

在你开始您的DSP学习开发之旅前,请您仔细核对本套件清单,具体如下:1.SR-DSP2812 开发板 1 块;2.9V直流电源 1 只;3.配套串口线 1 根;4.配套光盘 1 张;5.固定铜螺柱 4 只。

目录第1 章入门 (1)1.1 概述 (1)1.2 特点 (1)1.3 技术指标 (2)第2 章 TMS320F2812 基本系统 (3)2.1 TMS320F2812 时钟 (3)2.1.1 CPU 时钟 (3)2.1.2 片上外设时钟 (3)2.2 TMS320F2812 存储空间的配置 (4)2.2.1 ‘F2812 片上SARAM (6)2.2.2 ‘F2812 片上FLASH 和OTP (7)2.2.3 ‘F2812 外部存储器接口 (8)2.3 McBSP (8)2.4 SPI (8)2.5 SCI (9)2.6 CAN (9)2.7 ADC (9)2.8 事件管理器 (9)2.9 定时器 (10)2.10 F2812 的中断 (10)2.11 ‘F2812 的复位 (11)2.11 JTAG (12)2.12 ‘F2812 工作方式的配置 (12)第3 章测试程序 (13)3.1 GPIO 测试 (13)3.2 SCI 测试 (14)3.3 SPI 测试 (15)3.4 CAN 测试 (16)3.5 PWM 测试 (17)3.6 McBSP 测试 (18)3.7 A/D 测试 (19)3.8 TIMER0 测试 (20)3.9 EvTimer 测试 (21)3.10 外部Ram 测试 (21)3.11 外部FLASH 测试 (23)第1章入门1.1 概述SR-DSP2812 开发套件主要包含SR-DSP2812 的硬件系统与相应的测试软件两部分。

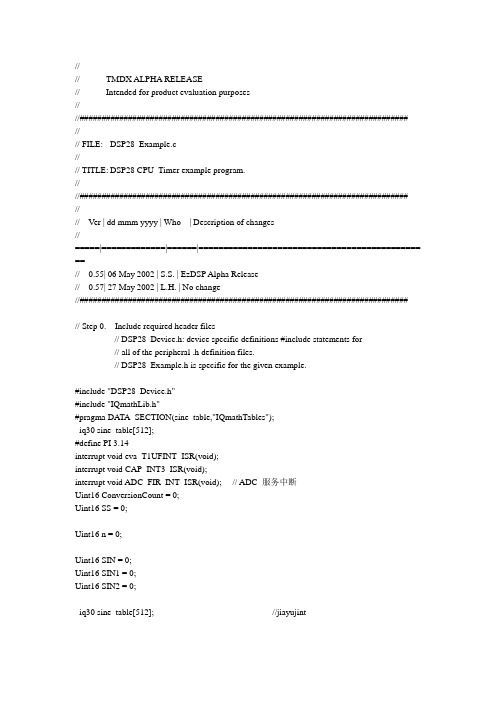

CCS5 DSP2812工程文件构建

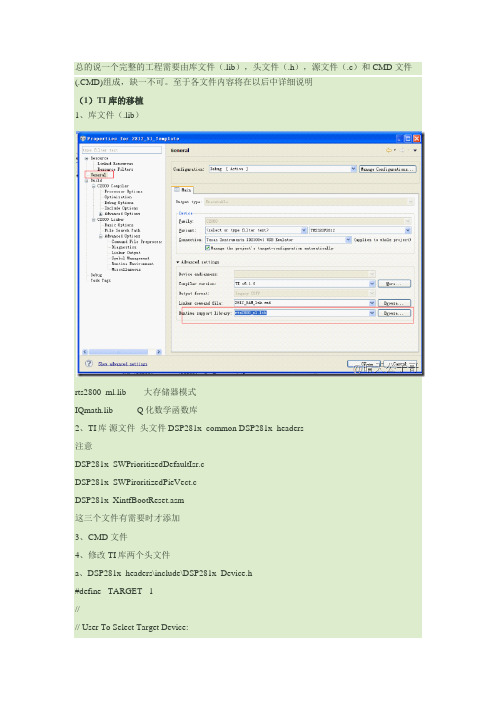

总的说一个完整的工程需要由库文件(.lib),头文件(.h),源文件(.c)和 CMD 文件(.CMD)组成,缺一不可。

至于各文件内容将在以后中详细说明(1)TI 库的移植1、库文件(.lib)rts2800_ml.lib --- 大存储器模式IQmath.lib --- Q化数学函数库2、TI库源文件头文件 DSP281x_common DSP281x_headers注意DSP281x_SWPrioritizedDefaultIsr.cDSP281x_SWPiroritizedPieVect.cDSP281x_XintfBootReset.asm这三个文件有需要时才添加3、CMD 文件4、修改TI库两个头文件a、DSP281x_headers\include\DSP281x_Device.h#define TARGET 1//---------------------------------------------------------------------------// User To Select Target Device:#define DSP28_F2812 TARGET#define DSP28_F2811 0#define DSP28_F2810 0b、DSP281x_common\include\DSP281x_Examples.h#define CPU_RATE 6.667L // for a 150MHz CPU clock speed (SYSCLKOUT) //#define CPU_RATE 7.143L // for a 140MHz CPU clock speed (SYSCLKOUT) 5、编写文件包含头文件#include "DSP281x_Device.h" // DSP281x Headerfile Include File#include "DSP281x_Examples.h" // DSP281x Examples Include File(2)TI库文件解释文件描述DSP281x_GlobalPrototypes.h这个文件包含外设详细的函数原型DSP281x_Adc.cADC具体函数和宏DSP281x_CpuTimers.cCPU-Timer具体函数和宏DSP281x_Ecan.c增强CAN详细函数和宏DSP281x_Ev.cEV详细函数和宏DSP281x_Gpio.cGPIO详细函数和宏DSP281x_Mcbsp.cMcBSP详细函数和宏DSP281x_PieCtrl.cPIE控制详细函数和宏DSP281x_Sci.cSCI详细函数和宏DSP281x_Spi.cSPI详细函数和宏DSP281x_SysCtrl.c系统控制(看门够,时钟,pll等) 详细函数和宏DSP281x_Xintf.cXINTF详细函数和宏DSP281x_Xintrupt.c外部中断详细函数和宏DSP281x_CodeStartBranch.asm当代码导入Flash,OTP或H0 SARAM存储器时,此程序确定代码从哪个分支开始执行。

DSP2812学习笔记-CMD文件编写

DSP2812学习笔记-CMD⽂件编写⾸先我们要知道什么是CMD⽂件,它是⽤来⼲什么的,然后再来看看它有些什么,怎么去编写⼀个CMD⽂件。

CMD即command命令,命令⽂件指定存储区域的分配。

由于 DSP281X 系列的独特性(⽚内存在 SRAM 和 FLASH)所以必须创建⼀个⽤户链接命令⽂件,以便在运⾏程序时,每个块都能对号⼊座。

2812中CMD 采⽤的是分页制,其中PAGE0⽤于存放程序空间,⽽PAGE1⽤于存放数据空间。

我们结合SRAM.cmd(附件1)⽂件来介绍下CMD⽂件的编写。

CMD的伪指令:MEMORY 和 SECTIONS 是命令⽂件中最常⽤的两伪指令。

MEMORY伪指令⽤来表⽰实际存在⽬标系统中的可以使⽤的存储器范围,在这⾥每个存储器都有⾃⼰的名字,起始地址和长度。

SECTIONS伪指令是⽤来描述输⼊端是如何组合到输出端内的。

CMD ⽂件⾥有两个基本的段:初始化段和⾮初始化段。

初始化段包含代码和常数等必须在 DSP 上电之后有效的数。

故初始化块必须保存在如⽚内 FLASH 等⾮遗失性存储器中。

在SRAM.cmd⽂件中已初始化的段:.text,.cinit,.const,.econst,..pinit 和.switch..每个⼩段⾥⾯存储的量说明如下:.text:所有可以执⾏的代码和常量.cinit:全局变量和静态变量的 C 初始化记录.const:包含字符串常量和初始化的全局变量和静态变量(由 const)的初始化和说明.econst:包含字符串常量和初始化的全局变量和静态变量(由 far const)的初始化和说明.pinit:全局构造器( C++)程序列表.switch:包含转换语⽓声明的列表⾮初始化段中含有在程序运⾏过程中才像变量内写数据进去,所以⾮初始化段必须链接到易失性存储器中如 RAM。

⾮初始化的段:.bss,.ebss,.stack,.sysmem,和 esysmem.(更好的理解就是,这些段就是存储空间⽽已)每个⼩段⾥⾯存储的量说明如下:.bss: 为全局变量和局部变量保留的空间,在程序上电时,cinit 空间中的数据复制出来并存储在.bss 空间中。

dsp2812中文介绍

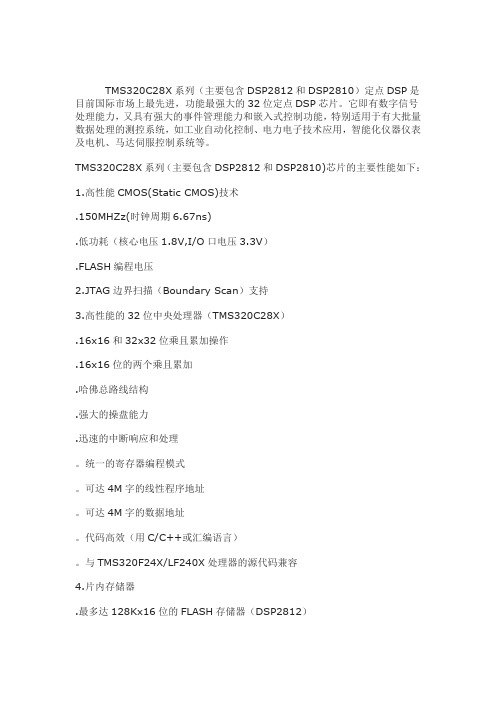

TMS320C28X系列(主要包含DSP2812和DSP2810)定点DSP是目前国际市场上最先进,功能最强大的32位定点DSP芯片。

它即有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控系统,如工业自动化控制、电力电子技术应用,智能化仪器仪表及电机、马达伺服控制系统等。

TMS320C28X系列(主要包含DSP2812和DSP2810)芯片的主要性能如下:1.高性能CMOS(Static CMOS)技术.150MHZz(时钟周期6.67ns).低功耗(核心电压1.8V,I/O口电压3.3V).FLASH编程电压2.JTAG边界扫描(Boundary Scan)支持3.高性能的32位中央处理器(TMS320C28X).16x16和32x32位乘且累加操作.16x16位的两个乘且累加.哈佛总路线结构.强大的操盘能力.迅速的中断响应和处理。

统一的寄存器编程模式。

可达4M字的线性程序地址。

可达4M字的数据地址。

代码高效(用C/C++或汇编语言)。

与TMS320F24X/LF240X处理器的源代码兼容4.片内存储器.最多达128Kx16位的FLASH存储器(DSP2812).最多达128x16位的ROM.1Kx16的OTP型只读存储器.L0和L1:两块4Kx16位的单口随机存储器(SRAM).H0:一块8Kx16位的单口随机存储器.M0和M1:两块1Kx16位的单口随机随机存储器5.根只读存储器(BootROM)4KX16位.带有软件的BOOT模式.标准的数学表6.外部存储器接口(仅DSP2812).有多达1MB的存储器.可编程等待状态数.可编程读/写选通计数器(StrobeTiming).三个独立的片选端7.时钟与系统控制.支持动态的改变锁相环的频率.片内振荡器.看门狗定时器模块8.三个外部中断9.外部中断扩展(PIE)模块.可支持96个外部中断,当前仅用了45个外部中断10.128位的密钥(SECURITYKEY/LOCK).保护FLASH/OTP 和LO/L1 SRAM.防止ROM中的程序被盗11. 3个32位的CPU定时器12.马达控制外围设备.两个事件管理器(EVA、EVB).与C240兼容的器件13.串口外围设备.串行外围接口(SPI).两个串行通信接口(SCIs),标准的UART.改进的局域网络(eCAN).多通道缓冲串行接口(McBSP)和串行外围接口模式14. 12位的ADC,多达16通道.2x8通道的输入多路选择器.两个采样保持器.单个的转换时间:200ns.单路转换时间:60ns15.最多有56个独立的可编程,多用途通用输入/输出(GPIO)引脚16.高级的仿真特性.分析和设置断点的功能.实时的硬件调试17.开发工具.ANSI C/C++编译器/汇编程序/连接器.支持TMS320C24X/240X的指令.代码编辑集成环境.DSP/BIOS.JTAG扫描控制器(TI或第三方的).硬件评估板18.低功耗模式和节能模式.支持空闲模式、等待模式、挂起模式.停止单个外围的时钟19.封装方式.带外部存储器接口的179球形触点BGA封装.带外部存储器接口的176引脚低剖面四芯线扁平LQFP封装.没有外部存储器接口的128引脚贴片正方扁平PBK封装20.温度选择.A: -40C~+85C.S: -40C~+125CTMS320F2812相关资料1.DSP2812开发板开发板参考图:。

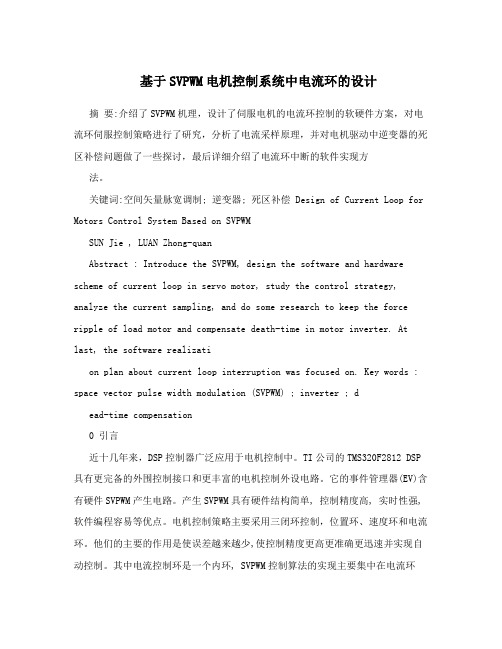

基于SVPWM电机控制系统中电流环的设计

基于SVPWM电机控制系统中电流环的设计摘要:介绍了SVPWM机理,设计了伺服电机的电流环控制的软硬件方案,对电流环伺服控制策略进行了研究,分析了电流采样原理,并对电机驱动中逆变器的死区补偿问题做了一些探讨,最后详细介绍了电流环中断的软件实现方法。

关键词:空间矢量脉宽调制; 逆变器; 死区补偿 Design of Current Loop for Motors Control System Based on SVPWMSUN Jie , LUAN Zhong-quanAbstract : Introduce the SVPWM, design the software and hardware scheme of current loop in servo motor, study the control strategy, analyze the current sampling, and do some research to keep the force ripple of load motor and compensate death-time in motor inverter. At last, the software realization plan about current loop interruption was focused on. Key words : space vector pulse width modulation (SVPWM) ; inverter ; d ead-time compensation0 引言近十几年来,DSP控制器广泛应用于电机控制中。

TI公司的TMS320F2812 DSP 具有更完备的外围控制接口和更丰富的电机控制外设电路。

它的事件管理器(EV)含有硬件SVPWM产生电路。

产生SVPWM具有硬件结构简单, 控制精度高, 实时性强, 软件编程容易等优点。

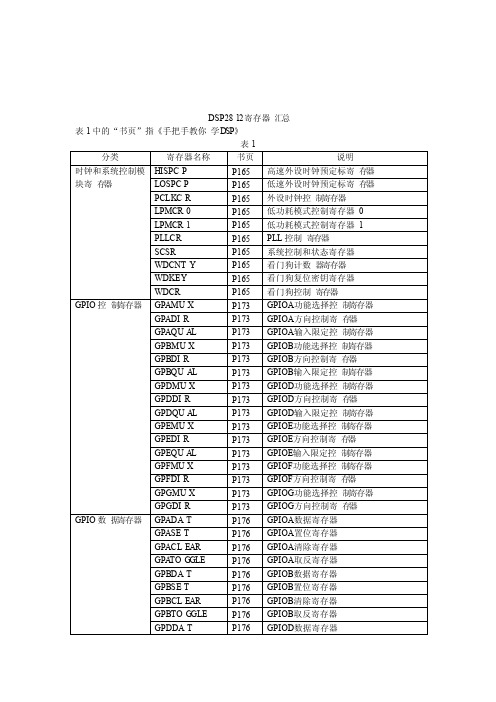

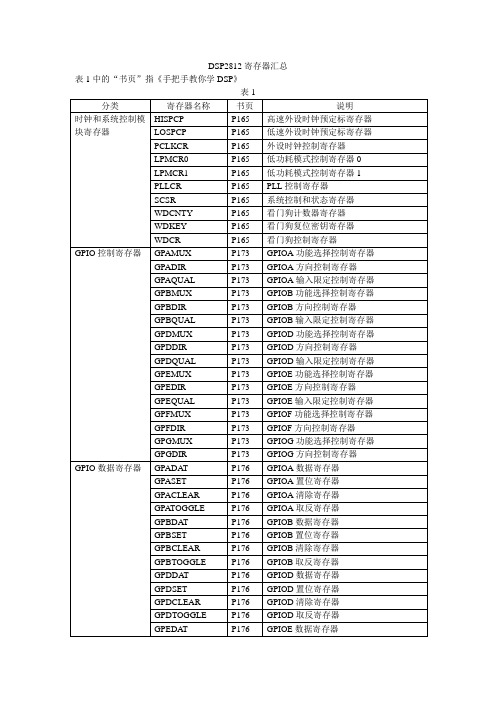

手把手教你学DSP2812-寄存器

比较寄存器 1 比较寄存器 2 比较寄存器 3 比较控制寄 存器 B 比较行为控 制寄存器 B 死区定时器控制寄存器 B 比较寄存器 4 比较寄存器 5 比较寄存器 6 捕获单元控 制寄存器 A 捕获单元 F IFO 状态 寄存器 A CAP1 的 FIFO 堆栈顶层寄存 器 CAP2 的 FIFO 堆栈顶层寄存 器 CAP3 的 FIFO 堆栈顶层寄存 器 CAP1 的 FIFO 堆栈底层寄存 器 CAP2 的 FIFO 堆栈底层寄存 器 CAP3 的 FIFO 堆栈底层寄存 器 捕获单元控 制寄存器 B 捕获单元 F IFO 状态 寄存器 B CAP4 的 FIFO 堆栈顶层寄存 器 CAP5 的 FIFO 堆栈顶层寄存 器 CAP6 的 FIFO 堆栈顶层寄存 器 CAP4 的 FIFO 堆栈底层寄存 器 CAP5 的 FIFO 堆栈底层寄存 器 CAP6 的 FIFO 堆栈底层寄存 器 EVA 中断标志寄存器 A EVA 中断屏蔽寄存器 A EVA 中断标志寄存器 B EVA 中断屏蔽寄存器 B EVA 中断标志寄存器 C EVA 中断屏蔽寄存器 C EVB 中断标志寄存器 A EVB 中断屏蔽寄存器 A EVB 中断标志寄存器 B EVB 中断屏蔽寄存器 B EVB 中断标志寄存器 C EVB 中断屏蔽寄存器 C ADC 控制 寄存器 1 ADC 控制 寄存器 2 ADC 最大转换通道寄 存器 ADC 通道选额控制寄 存器 1 ADC 通道选额控制寄 存器 2 ADC 通道选额控制寄 存器 3

TIMER 2TIMH TIMER 2PRD

dsp2812硬件总结

硬件部分中断硬件,软件中断。

中断分3级:CPU级中断,PIE级中断,外设中断可屏蔽中断:由⽚片内的外设产⽣生,可通过相应寄存器器的中断使能来禁⽌止或使能。

不不可屏蔽中断:软件中断,硬件中断NMI,⾮非法指令陷阱,硬件复位中断。

中断处理理步骤:(先判断该中断是否可屏蔽,再决定是否响应)。

接受中断请求,响应中断,准备执⾏行行中断服务程序并,保存寄存器器值,执⾏行行中断程序。

(结束后恢复断点,继续执⾏行行主程序)中断优先级:复位中断,不不可屏蔽中断,可屏蔽实时操作系统中断,可屏蔽中断,⽤用户⾃自定义陷阱。

优先级可通过硬件,软件控制。

28335⽀支持32个CPU中断,其中CPU⽀支持1个不不可屏蔽硬件中断NMI和16个可屏蔽中断。

CPU需要9个时钟周期获取中断向量量和保存CPU寄存器器(保存断点)。

外设中断扩展PIE模块⽀支持96个独⽴立中断12组*8个。

每个中断都是32位的中断向量量,中断向量量内含中断服务⼦子程序⼊入⼝口地址(地址是22位的)。

CPU定时器器0和1给⽤用户使⽤用,2留留给实时操作系统(DSP/BIOS)CPU定时器器的4个寄存器器:32b定时器器周期寄存器器PRD,32b计数器器寄存器器TIM,16b定时器器分频寄存器器TDDR,16b预定标计数器器寄存器器PSC。

其他地⽅方的寄存器器都是16b,只有定时器器⾥里里有32b的寄存器器存储器器的总线分为两⼤大类:地址总线,数据总线。

28335有3条地址总线和3条数据总线22b程序地址(⾼高⼗十位是空的),32b数据地址,都是4M空间先⽤用地址总线找到地址,再⽤用数据总线传输数据。

地址总线(⽤用来传输存储单元地址):PAB程序地址总线(传输程序空间的读写地址)22b,DRAB数据读地址总线32b,DWAB数据写地址总线32b。

数据总线(⽤用来传输数据):PRDW程序读数据总线32,DRDB数据读数据总线32,DWDB数据写数据总线(向数据空间/程序空间传输数据)32b。

DSP2812寄存器汇总

PIE, INT9组使能寄存器

PIEIFR9

P201

PIE, INT9组标志寄存器

PIEIER10

P201

PIE, INT10组使能寄存器

PIEIFR10

P201

PIE, INT10组标志寄存器

PIEIER11

P201

PIE, INT11组使能寄存器

PIEIFR11

P201

PIE, INT11组标志寄存器

P187

CPU定时器2控制寄存器

TIMER2TPR

P187

CPU定时器2预定标寄存器低位

TIMER2TPRH

P187

CPU定时器2预定标寄存器高位

CPU中断寄存器

IER

P196

CPU中断使能寄存器

IFR

P196

CPU中断标志寄存器

INTM

P196

CPU全局中断标志位

PIE(外设中断控制器)中断寄存器

EVAIFRA

P257

EVA中断标志寄存器A

EVAIMRA

P257

EVA中断屏蔽寄存器A

EVAIFRB

P257

EVA中断标志寄存器B

EVAIMRB

P257

EVA中断屏蔽寄存器B

EVAIFRC

P257

EVA中断标志寄存器C

EVAIMRC

P257

EVA中断屏蔽寄存器C

EVBIFRA

P257

EVB中断标志寄存器A

P293

ADC自动序列状态寄存器

ADCRESULT0

P293

ADC转换结果缓冲寄存器0

ADCRESULT1

P293

ADC转换结果缓冲寄存器1

步进电机恒流驱动电路设计

步进电机恒流驱动电路设计摘要:经济在快速的发展,社会在不断的进步,针对步进电机在恒压驱动控制中,高频条件下容易出现电机失步,造成无法正常运转的情况,设计了基于LMD18200的电流滞环驱动电路;通过对步进电机功率放大器电路的常见形式进行研究,分析恒压与恒流驱动电路设计上的差异,理论上推导恒流驱动稳定电流及波动频率等特性;利用Matlab仿真对比恒流与恒压驱动电路相电流的上升速度,说明两种方式下平均输出力矩以及运行频率情况;以电机驱动集成芯片LMD18200实现两种驱动方式的硬件电路,分别对型号TS3641N1E2的负载电机进行测试;在不同的运行频率下,根据两种驱动电路的相电流以及运行状态,验证步进电机恒流驱动电路设计满足空间光学遥感器机构控制的要求。

关键词:步进电机;LMD18200;恒流驱动引言步进电机是广泛用于计算机控制系统和计算机外部设备的驱动元件.步进电机使用脉冲电流驱动,利用环形脉冲分配器给各绕组分配驱动脉冲,每向环形分配器输入1个脉冲,步进电机绕组的通电状态改变一次,电机的转子转过1个步距角.步进电机的运行性能例如运行频率、输出力矩等,除受电机自身性能的影响外,还直接受驱动器的制约.步进电机伺服系统具有价格低、简单、可靠等交直流伺服系统无法比拟的优点,但由于它的运行速度低、驱动器效率低和发热量大等缺点,使它的使用范围受到限制.随着现代电力电子技术、微电子技术特别是微处理器技术的发展,为步进电机驱动器性能的提高提供了条件,使步进电机驱动器的性能有了很大提高,从而使传统的步进伺服系统得到了广泛的应用.1步进电机的控制系统结构1.1DSP简介DSP即数字信号处理器,是一种专门用来实现各种数字信号处理算法的微处理器。

文中选用TI公司的TMS320F2812作为主控制芯片,片内集成了丰富的外设模块,简化了系统的硬件设计;快速的中断处理能力和硬件I/O支持,保证了系统实时响应的能力;片内具有快速RAM同时采用改进的哈佛总线结构,可以通过独立的总线对多个存储器进行并行访问而且可同时完成获取指令和数据读取操作。

DSP2812EV管理器(转)

第11章 事件管理器(EV)

·277·

EVA/EVB 的启动转换信号(SOC)可以送至外部引脚(EVASOC),该信号为外部 ADC 的接口所用。EVASOC 和 EVBSOC 可以单独由 T2CTRIP和 T4CTRIP多路传输。

9.功率驱动保护中断( PDPINTx,x=A 或 B)

事件管理器(EV)的器件接口如图 11-1 所示。事件管理器 A(EVA)的功能模块图 如图 11-2 所示,事件管理器 B(EVB)的功能模块图与该图类似,只是模块及信号的命名 有所不同。

1.通用目的(GP)定时器 事件管理器各有两组 GP 定时器。GP 定时器 x(x=1 或 2 属于 EVA;x=3 或 4 属于 EVB) 包括: (1)1 个 16 位的定时器 TXCNT,为增/减计数器,TXCNT 可以读/写。 (2)1 个 16 位的定时器比较寄存器 TxCMPR(带阴影的双缓冲寄存器),可以读/写。 (3)1 个 16 位的定时器周期寄存器 TxPR(带阴影的双缓冲寄存器),可以读/写。 (4)1 个 16 位的定时器控制寄存器 TxCON,可以读/写。 (5)可选择的内部或外部输入时钟。 (6)一个对于内部或外部输入时钟可编程的预定标因子。

外部行程输入

PDPINTA*

PDPINTB*

外部 ADC SOC 触发输出

EVASOC

EVBSOC

注:* 在 C240x 的兼容模式下,引脚 T1CTRIP / PDPINTA功能为 PDPINTA,而引脚 T3CTRIP / PDPINTB功能为

PDPINTB

2.全比较单元 每个事件管理器都有 3 个全比较单元。这些比较单元使用定时器 1 为其提供时基,通

第2章TMS320F2812DSP内部结构

内容摘要

TMS320C2000概述 2.1 TMS320F2812中央处理单元 2.2 TMS320F2812存储器配置 2.3 TMS320F2812的引导加载方式 2.4 TMS320F2812的低功耗模式

2

TMS320C2000概述

TMS320C2000是TI公司继第二代定点DSP 处理器TMS320C2X和第三代定点DSP处理器 TMS320C5X之后出现的一种低价格、高性能的 定点DSP芯片。 主要包括: TMS320C24X、TMS320C28X两个子系列。

EVA/EVB

16通道

12位ADC

XRS

X1/XCLKIN X2 XF_XPLLDIS

系统控制 (振荡器、 PPL、外设时 钟、低功耗模 式、看门狗)

RS

CLKIN 存储器总线 外设总线

26

代码保护的模块

2.1.1 TMS320F2812CPU内部结构

TMS320F2812中包含一个高性能低功耗的32位 定点CPU内核,它主要负责DSP内部指令的控制和 数据的处理,主要由CPU内部寄存器、总线及相应 控制逻辑组成: 1.32位中央算术逻辑单元(CALU) 2.32位累加器(ACC) 3.能进行16bit×16bit或32bit×32bit定点乘法运 算的硬件乘法器(MUL) 4.桶形移位器 5.辅助寄存器算术单元(ARAU)及地址产生逻辑 6. 程序地址产生器及控制逻辑

Register Bus / Result Bus Data/Program-write Data Bus (32) Data-write Address Bus (32)

乘法器

Program Bus Data Bus

32 16 32

操作数1

DSP 2812中文手册

第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x 系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征TMS320C28x系列DSP的CPU与外设(上)·2·注:‡“S”是温度选择(-40℃~ +125℃)的特征化数据,仅对TMS是适用的。

‡‡产品预览(PP):在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI):在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包括对所有参数的测试。

[整理]DSP2812寄存器详解.

![[整理]DSP2812寄存器详解.](https://img.taocdn.com/s3/m/79e26c0f376baf1ffc4fad63.png)

T1CTRIPE

T1CTRIP使能位,使能或禁止定时器1的比较输出。

当EXTCON (0)=1时该位激活;当EXTCON=0时该位保留。

0禁止T1CTRIP,T1CTPIR不影响定时器1的比较输出、GPTCDN(4)或PDPINTA(EVIFRA(0))标

志。1使能T1CTRIP,定时器1变为高阻状态,GPTCON ( 4 )变为0, PDPINTA(EVIFRA(0))标志置1。

EXTCON(0)=1时激活该位,EXTCON(0)=0时该位保留。如果T1CMPOE有效,T1CTRIP为低电平且被使能,则T1CMPOE变为0

0定时器2比较输出T1PWM_T1CMP为高阻。

1定时器2比较输出T1PWM_T1CMP由定时器1比较逻辑驱动

3~2

T2PIN

定时器2比较输出极性。00强制低01低有效01高有效11强制高

TENABLE

TCLKS1

TCLKS0

TCLD1

TCLD0

TECMPR

SELT1PR

位(Bit)

名称

功能描述

15~14

FREE ,SOFT

仿真控制位; 00一旦仿真挂起,立即停止01一旦仿真挂起,在当前周期结束后停止

(五)规划环境影响评价的跟踪评价10操作受仿真挂起的影响11操作不受仿真挂起的影响

(四)规划环境影响评价的审查13

比较控制寄存器(COMCONA)

15

14

13

12

11

10

9

8

CENABLE

CLD1

CLD0

SVENABLE

ACTRLD1

ACTRLD0

FCOMPOE

PDPINTA

7

基于DSP2812控制的单相光伏逆变器程序代码

AdcBuf1[ibuf] = _IQmpy(AdcFsVoltage, _IQ16toIQ( (_iq)AdcRegs.RESULT1));

xDelay[0] = AdcBuf[ibuf];

AdcBufFiltered[ibuf] = IQssfir(xDelay, coeffs, N);

xDelay1[0] = AdcBuf1[ibuf];

AdcBufFiltered1[ibuf] = IQssfir(xDelay1, coeffs, N);

vf[ibuf] =AdcBufFiltered[ibuf]; //采样电压值

if (ibuf==0)

{

Ig[ibuf]=kp*ev[ibuf]+ki*ev[ibuf] ;

if (Ig[ibuf]>=Imax) //电压环限幅考虑输出Ig正负

Ig[ibuf]=Imax;

else if (Ig[ibuf]<=-Imax)

Ig[ibuf]=-Imax;

Ig[0]=Ig[ibuf];

//计算得出新的正弦表

SIN = _IQsat(_IQ30mpy(sine_table[SS]+_IQ30(0.9999),EvaRegs.T1PR/2),EvaRegs.T1PR,0);

SIN2 = _IQsat(_IQ30mpy(-sine_table[SS]+_IQ30(0.9999),EvaRegs.T1PR/2),EvaRegs.T1PR,0);

SS++;

if(SS == 512)

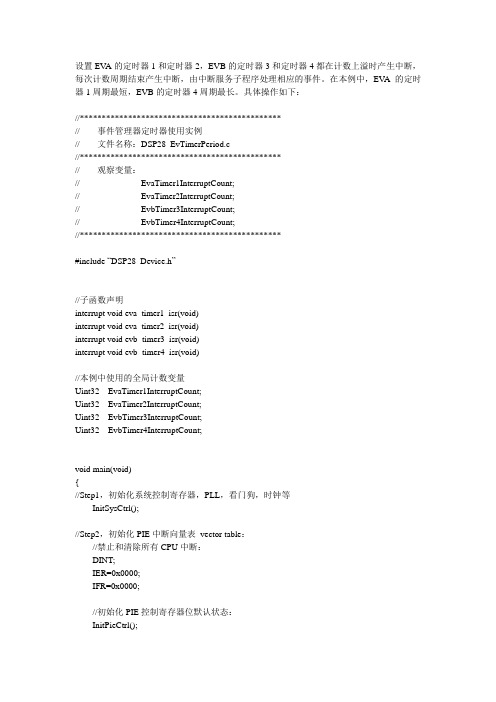

EV的定时器实例

Uint32 EvaTimer2InterruptCount;

Uint32 EvbTimer3InterruptCount;

Uint32 EvbTimer4InterruptCount;

voidmain(void)

{

//Step1,初始化系统控制寄存器,PLL,看门狗,时钟等

}

interruptvoid eva_timer3_isr(void)

{

EvaTimer3InterruptCount++;

EvbRegs.EVBIFRA.all=BIT7;

PieCtrlRegs.PIEACK.all=PIEACK_GROUP4;

}

interruptvoid eva_timer4_isr(void)

PieCtrlRegs.PIEIER3.all=M_INT1;

//为T3PINT中断使能PIE组4的中断4

PieCtrlRegs.PIEIER4.all=M_INT4;

//为T4PINT中断使能PIE组5的中断1

PieCtrlRegs.PIEIER5.all=M_INT1;

//使能CPU中断2、3、4和5

//向上计数、预定标x128、内部时钟、使能比较、使用自己的周期值

EvaRegs.EVAIMRB.bit.T2PINT=1;

EvaRegs.EVAIFRB.bit.T2PINT=1;

//清除通用目的定时器2的计数器值

EvaRegs.T2CNT=0x0000;

EvaRegs.T2CON.all=0x1742;

//使能通用目的定时器3的周期中断

//向上计数、预定标x128、内部时钟、使能比较、使用自己的周期值

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

定时器-方向 外部时钟

QEP11 TDIRA TCLKINA

定时器-方向 外部时钟

QEP12 TDIRB TCLKINB

C1T RIP

C4T RIP

外部比较-输出行程输入

比较

C2T RIP

C5T RIP

C3T RIP

C6T RIP

外部定时器-比较行程输入

T1CTRIP / T2CT RIP

T3CT RIP T4CTRIP /

事件管理器 EVA 和 EVB 拥有功能相同的外围寄存器组。EVA 的寄存器组地址开始于 7400h,EVB 的寄存器组地址开始于 7500h。本章中讲述了采用 EVA 命名方式的 GP 定时 器、比较单元、捕捉单元和正交编码脉冲电路(QEPs)的功能。这些段落对于与 EVB 相 关的器件功能同样是适用的,只是模块及信号的命名不同而已。

表 11-1 EVA 和 EVB 的模块及信号的命名

事件管理器模块

EVA

模块

信号

EVB

模块

信号

GP 定时器 比较单元 捕捉单元

GP 定时器 1 GP 定时器 2 比较器 1 比较器 2 比较器 3 捕捉器 1 捕捉器 2 捕捉器 3

T1PWM/T1CMP T2PWM/T2CMP PWM1/2 PWM3/4 PWM5/6 CAP1 CAP2 CAP3

外部行程输入

PDPINTA*

PDPINTB*

外部 ADC SOC 触发输出

EVASOC

EVBSOC

注:* 在 C240x 的兼容模式下,引脚 T1CTRIP / PDPINTA功能为 PDPINTA,而引脚 T3CTRIP / PDPINTB功能为

PDPINTB

2.全比较单元 每个事件管理器都有 3 个全比较单元。这些比较单元使用定时器 1 为其提供时基,通

图 11-1 事件管理器(EV)器件接口

3.可编程的死区发生器 死区发生器电路包括 3 个 8 位计数器和 8 位比较寄存器。可将需要的死区幅值通过编 程写入比较寄存器,以便用于 3 个比较单元的输出。通过每个比较单元的输出可以单独使 能或禁止死区的产生。死区发生器电路可以为每个比较寄存器的输出信号产生两个输出(带 有或不带有死区地带)。通过双缓冲 ACTRx 寄存器,可以根据需要设置或更改死区发生 器的输出状态。

捕捉单元具有以下的特点: (1)1 个 16 位的捕捉控制寄存器 CAPCONx(读/写)。 (2)1 个 16 位的捕捉 FIFO 状态寄存器 CAPFIFOx。 (3)可以选择 GP 定时器 1、2(为 EVA)或 GP 定时器 3、4(为 EVB)作为时基。 (4)3 个 16 位的两级深度 FIFO 堆栈,每个捕捉单元配备 1 个。 (5)6 个捕捉输入引脚(CAP1/2/3 为 EVA 所用,CAP4/5/6 为 EVB 所用),每个捕 捉单元有 1 个捕捉引脚。所有捕捉引脚的输入都与器件的 CPU 时钟同步。为了能正确地捕 捉到引脚上的变化,输入引脚的信号电平必须保持两个时钟的上升沿。输入引脚 CAP1/2 和 CAP4/5 也可以作为正交编码脉冲电路的输入引脚。 (6)用户可指定诊测变化的方式(上升沿、下降沿或两个边沿)。 (7)3 个可屏蔽中断标志,每个捕捉单元具有 1 个。

第11章 事件管理器(EV)

·275·

注:EVB 模块与 EVA 模块相似

图 11-2 事件管理器 A 的功能模块图

4.PWM 波形的产生 每个事件管理器在同一时刻可产生多达 8 个 PWM 的波形输出;通过带有可编程死区 的 3 个全比较单元可单独产生 3 对(6 个)输出;通过 GP 定时器的比较功能可产生两个单

(3)PIE 请求。如果同时有两个中断标志位和中断屏蔽位被置为 1,那么外围设备向 PIE 模块发出一个中断请求。PIE 模块将会收到来自外围设备的一个以上的中断。PIE 逻辑 记录所有的中断请求并产生各自的 CPU 中断。INT1、2、3、4 或 5 是建立在所收到中断的 预先分配的中断优先级。

当类似的事件发生时与 PDPINTx相关的中断也会发生;然而,它必须等到 PDPINTx引 脚上的变化被确认后才被允许而且必须与内部时钟同步。确认和同步将会引起 2 个时钟周 期的延迟。标志位是否置位不依赖于 PDPINTx中断是否被屏蔽:只要确认了 PDPINTx引 脚上的变化它就置位。复位将会使能中断。如果 PDPINTx中断被禁止,驱动 PWM 输出变 为高阻状态动作也同样会被禁止。

·274·

TMS320C28x系列DSP的CPU与外设(下)

过使用可编程的死区电路可产生 6 个比较输出或 PWM 波形输出,6 个输出中的任何一个 输出状态都可以单独设置。比较单元中的比较寄存器是双缓冲的,允许可编程的变换比 较/PWM 脉冲宽度。

注:EXTCONA 是一个附加控制寄存器,它是用来使能或禁止添加/修改特点的。它要求与 240x 的 EV 兼 容。EXTCONA 可使能或禁止在特性中进行添加或修改。所有的添加和修改都被默认设置为禁止,以 保证与 240x 的 EV 兼容。详情可见 5.6 节关于 EXTCON 寄存器的内容

GP 定时器 3 GP 定时器 4 比较器 4 比较器 5 比较器 6 捕捉器 4 捕捉器 5 捕捉器 6

T3PWM/T3CMP T4PWM/T4CMP PWM7/8 PWM9/10 PWM11/12 CAP4 CAP5 CAP6

QEP 通道

QEP1

QEP

QEP2

QEP3QEPFra bibliotekQEP4

外部定时器输入

6.捕捉单元

捕捉单元为用户提供了对不同事件和变化进行记录的功能。当捕捉输入引脚 CAPx (x=1、2 或 3 属于 EVA;x=4、5 或 6 属于 EVB)检测到变化时,它将捕捉所选择的 GP 定时器的当前计数值,并把该计数值存储在两级深度的 FIFO 堆栈中。捕捉单元由 3 个捕 捉电路组成。

事件管理器(EV)的器件接口如图 11-1 所示。事件管理器 A(EVA)的功能模块图 如图 11-2 所示,事件管理器 B(EVB)的功能模块图与该图类似,只是模块及信号的命名 有所不同。

1.通用目的(GP)定时器 事件管理器各有两组 GP 定时器。GP 定时器 x(x=1 或 2 属于 EVA;x=3 或 4 属于 EVB) 包括: (1)1 个 16 位的定时器 TXCNT,为增/减计数器,TXCNT 可以读/写。 (2)1 个 16 位的定时器比较寄存器 TxCMPR(带阴影的双缓冲寄存器),可以读/写。 (3)1 个 16 位的定时器周期寄存器 TxPR(带阴影的双缓冲寄存器),可以读/写。 (4)1 个 16 位的定时器控制寄存器 TxCON,可以读/写。 (5)可选择的内部或外部输入时钟。 (6)一个对于内部或外部输入时钟可编程的预定标因子。

PDPINTx为系统的操作(例如功率转化器和马达驱动)提供了安全。 PDPINTx可以 向监测马达驱动异常的监视程序报告信息,例如:过压、过流和温度的急剧上升。如果 PDPINTx的中断未被屏蔽,当 PDPINTx引脚变为低电平时,所有的 PWM 输出引脚都将 立刻变为高阻状态,同时也将会产生 1 个中断。详情可见 EXTCON 寄存器关于单个 PWM 对、功率保护或行程功能(trip functions)每个位的定义。

8.外部启动转换的模/数转换器(ADC)

第11章 事件管理器(EV)

·277·

EVA/EVB 的启动转换信号(SOC)可以送至外部引脚(EVASOC),该信号为外部 ADC 的接口所用。EVASOC 和 EVBSOC 可以单独由 T2CTRIP和 T4CTRIP多路传输。

9.功率驱动保护中断( PDPINTx,x=A 或 B)

第 11 章 事件管理器(EV)

事件管理器模块为用户提供了众多的功能和特点,它们在运动控制和马达控制的应用 中是特别有用的。事件管理器模块包括通用目的(GP)定时器、全比较/PWM 单元、捕捉 单元和正交编码脉冲电路等。EVA 和 EVB 两个 EV 模块都是特定的外围设备,它们是为多 轴运动控制应用而设计的。

(1)中断源。如果产生外围中断,寄存器 EVxIFRA、EVxIFRB 或 EVxIFRC(x=A 或 B)中各自的标志位将会被置位。一旦置位,这些标志位将会保持直到软件清 0。当标志位 被软件清 0 后,随后的中断将不会被响应。

(2)使能中断事件管理器中断可以由中断屏蔽寄存器 EVxIMRA、EVxIMRB 和 EVxIMRC(x=A 或 B)单独的使能或禁止。寄存器中的每个位置 1 使能中断,清 0 禁止中断。

10.EV 的寄存器

事件管理器的寄存器占用两块 64 个字的地址空间。事件管理器模块对地址的低 6 位进 行译码,而外围地址译码逻辑对地址的高 10 位进行译码,该逻辑提供一个模块用来选择事 件管理器,此时外围地址总线携带一个地址,该地址将会指定器件上的 EV。

在 28x 芯片中(正如 C240 芯片一样),EVA 的寄存器位于 7400h~7431h 地址范围, EVB 寄存器位于 7500h~7531h 地址范围。

当用户通过软件读取保留的寄存器和寄存器中的保留位时返回值均为 0,写没有影响。 详情见 11.1.3 节“事件管理器的寄存器地址”。

11.EV 中断

每个 EV 中断组都有多个中断源,CPU 的中断请求由外设中断扩展(PIE)模块来处理。 详情见外设中断扩展的外围应用参考指南(文件号 SPRU045)。相应的过程如下。

第11章 事件管理器(EV)

·273·

(7)控制和中断逻辑,用于 4 种可屏蔽中断:下溢中断、上溢中断、定时器比较中断 和定时器周期中断。

(8)1 个输入方向选择引脚(TDIRx)(当选择为单增/减计数模式后,进行增计数或 减计数)。

GP 定时器可以进行单独操作,也可与其他定时器同步操作。每个 GP 定时器所具有的 比较寄存器可以用作比较功能和 PWM 波形的产生。对于每一个 GP 定时器在增或增/减计 数模式下都有 3 种连续操作模式。通过预定标因子,每个 GP 定时器可以使用内部或外部 时钟。GP 定时器可以为事件管理器的其他子模块提供时基:GP 定时器 1 可以为所有的比 较和 PWM 电路提供时基,GP 定时器 1 和 GP 定时器 2 可以为捕捉电路和正交脉冲计数操 作提供时基。双缓冲的周期和比较寄存器允许可编程的变化定时器(PWM)的周期,从而 得到比较/PWM 脉冲的所需宽度。