cankao高清晰AD9854中文资料附带51程序

AD9854中文数据手册

AD9854特征·300M内部时钟频率·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作·正交的双通道12位D/A转换器·超高速比较器,3皮秒有效抖动偏差·外部动态特性:80 dB无杂散动态范围(SFDR)@ 100 MHz (±1 MHz) A OUT·4倍到20倍可编程基准时钟乘法器·两个48位可编程频率寄存器·两个14位可编程相位补偿寄存器·12位振幅调制和可编程的通断整形键控功能·单引脚FSK和BPSK数据输入接口·PSK功能可由I/O接口实现·具有线性和非线性的脉冲调频(FM CHIRP)功能,带有引脚可控暂停功能·具有过渡FSK功能·在时钟发生器模式下,有小于25 ps RMS抖动偏差·可自动进行双向频率扫描·能够对信号进行sin(x)/x校正·简易的控制接口:可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ 8位并行可编程接口·3.3V单电源供电·具有多路低功耗功能·单输入或差分输入时钟·小型80脚LQFP 封装应用·便携式频率特性分析仪·可编程时钟发生器·应用于雷达和扫频系统的脉冲调频信号源·测试和测量设备·商业和业余的射频(RF)发射机概述AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号。

在高稳定度时钟的驱动下,AD9854将产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本振用于通信,雷达等方面。

AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1uHZ)。

AD9850介绍AD9850中文资料

第13章DDS芯片AD9850/AD9851的设计13.1 硬件设计信号源作为现代电子产品设计和生产中的重要工具,必须满足高精度、高速度、高分辨率等要求。

本章基于DDS ( Direct Digital Synthesis ,直接数字频率合成)技术,采用AD9850 DDS芯片,采用F169单片机作为控制芯片,实现一种了简易信号发生器的设计,该信号发生器具有输出频率范围宽,可以输出正弦和方波两种波形,与键盘结合易于实现全数字化的设计。

13.1.1 AD9850 DDS芯片简介随着数字技术的飞速发展,用数字控制方法从一个参考频率源产生多种频率的技术,即直接数字频率合成(DDS)技术异军突起。

美国AD公司推出的高集成度频率合成器AD9850便是采用DDS技术的典型产品之一。

AD9850采用CMOS工艺,其功耗在3.3V左右。

供电时仅为155mW,扩展工业级温度范围为-40~80℃,采用28脚SSOP表面封装形式。

AD9850的引脚排列如图13-1所示:LSB D0FQ-UD CLKIN AGND AVDDRSET QOUT QOUTBD4D5D6D7 MSBDGNDDVDORESETIOUTIOUTBAGNDAVDODACBL(NC)VINPVINN图13-1 AD9850的引脚图图13-2中层虚线内是一个完整的可编程DDS系统,外层虚线内包含了AD9850的主要组成部分。

图13-3为其组成框图。

图13-2 AD9850组成原理AD9850内含可编程DDS 系统和高速比较器,能实现全数字编程控制的频率合成[22]。

可编程DDS 系统的核心是相位累加器,它由一个加法器和一个N 位相位寄存器组成,N 一般为24~32。

每来一个外部参考时钟,相位寄存器便以步长M 递加。

相位寄存器的输出与相位控制字相加后可输入到正弦查询表地址上。

正弦查询表包含一个正弦波周期的数字幅度信息,每一个地址对应正弦波中0°~360°范围的一个相位点。

高清晰AD9854中文资料附带51程序

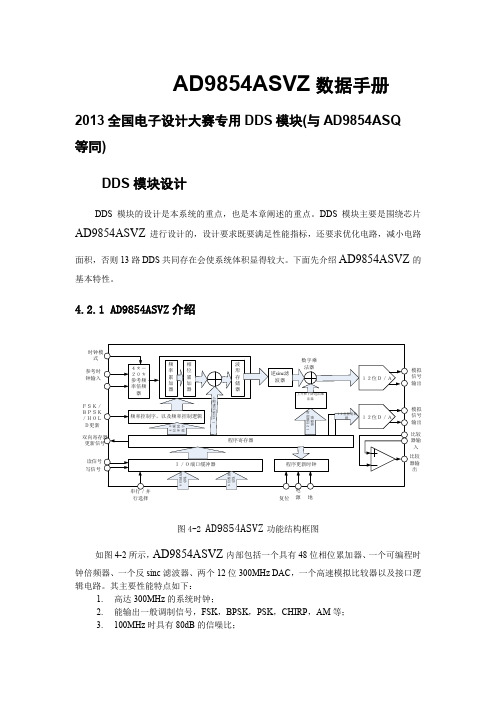

DDS模块设计DDS模块的设计是本系统的重点,也是本章阐述的重点。

DDS模块主要是围绕芯片AD9854进行设计的,设计要求既要满足性能指标,还要求优化电路,减小电路面积,否则13路DDS共同存在会使系统体积显得较大。

下面先介绍AD9854的基本特性。

4.2.1 AD9854介绍式参考时钟输入D更新读信号写信号行选择复位源地比较器输入模拟信号输出模拟信号输出比较器输出图4-2 AD9854功能结构框图chart4-2 AD9854 function and structure如图4-2所示,AD9854内部包括一个具有48位相位累加器、一个可编程时钟倍频器、一个反sinc滤波器、两个12位300MHz DAC,一个高速模拟比较器以及接口逻辑电路。

其主要性能特点如下:1.高达300MHz的系统时钟;2.能输出一般调制信号,FSK,BPSK,PSK,CHIRP,AM等;3.100MHz时具有80dB的信噪比;4.内部有4*到20*的可编程时钟倍频器;5.两个48位频率控制字寄存器,能够实现很高的频率分辨率。

6.两个14位相位偏置寄存器,提供初始相位设置。

7.带有100MHz的8位并行数据传输口或10MHz的串行数据传输口。

AD9854的芯片封装图如下:图4-3 AD9854芯片封装图chart4-3 AD9854 chip encapsulationAD9854有40个程序寄存器,对AD9854的控制就是对这些程序寄存器写数据实现的。

表4-1 AD9854并行接口寄存器功能并行地址寄存器功能默认值0x00 0x01 相位寄存器#1<13:8>(15,14位无效)相位寄存器#1<7:0>0x000x000x02 0x03 相位寄存器#2<13:8>(15,14位无效)相位寄存器#2<7:0>0x000x000x04 0x05 0x06 0x07 0x08 0x09 频率转换字#1<47:40>频率转换字#1<39:32>频率转换字#1<31:24>频率转换字#1<23:16>频率转换字#1<15:8>频率转换字#1<7:0>0x000x000x000x000x000x000x0A 频率转换字#1<47:40> 0x00表4-2 AD9854控制寄存器功能通过并行总线将数据写入程序寄存器时,实际上只是暂存在I/O缓冲区中,只有提供更新信号,这些数据才会更新到程序寄存器。

AD9854中文数据手册要点

AD9854特征·300M内部时钟频率·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作·正交的双通道12位D/A转换器·超高速比较器,3皮秒有效抖动偏差·外部动态特性:80 dB无杂散动态范围(SFDR)@ 100 MHz (±1 MHz) A OUT·4倍到20倍可编程基准时钟乘法器·两个48位可编程频率寄存器·两个14位可编程相位补偿寄存器·12位振幅调制和可编程的通断整形键控功能·单引脚FSK和BPSK数据输入接口·PSK功能可由I/O接口实现·具有线性和非线性的脉冲调频(FM CHIRP)功能,带有引脚可控暂停功能·具有过渡FSK功能·在时钟发生器模式下,有小于25 ps RMS抖动偏差·可自动进行双向频率扫描·能够对信号进行sin(x)/x校正·简易的控制接口:可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ 8位并行可编程接口·3.3V单电源供电·具有多路低功耗功能·单输入或差分输入时钟·小型80脚LQFP 封装应用·便携式频率特性分析仪·可编程时钟发生器·应用于雷达和扫频系统的脉冲调频信号源·测试和测量设备·商业和业余的射频(RF)发射机概述AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号。

在高稳定度时钟的驱动下,AD9854将产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本振用于通信,雷达等方面。

AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1uHZ)。

AD9854对照翻译

FEATURES300 MHz internal clock rateFSK, BPSK, PSK, chirp, AM operationDual integrated 12-bit digital-to-analog converters (DACs) Ultrahigh speed comparator, 3 ps rms jitterExcellent dynamic performance80 dB SFDR at 100 MHz (±1 MHz) AOUT4× to 20× programmable reference clock multiplierDual 48-bit programmable frequency registersDual 14-bit programmable phase offset registers12-bit programmable amplitude modulation andon/off output shaped keying functionSingle-pin FSK and BPSK data interfacesPSK capability via input/output interfaceLinear or nonlinear FM chirp functions with single-pin frequency hold functionFrequency-ramped FSK<25 ps rms total jitter in clock generator mode特征300 MHz内部时钟速率支持FSK, BPSK, PSK, chirp, AM调制集成双路12位数/模转换器(DAC)超高速比较器,3个PS RMS抖动出色的动态性能80dB的SFDR在100 MHz(±1 MHz)的AOUT4 ×20×可编程参考时钟倍频器双48位可编程频率寄存器双通道,14位可编程相位偏移寄存器12位可编程振幅调制ON / OFF输出形键控功能单引脚FSK和BPSK的数据接口通过输入/输出接口实现PSK功能单线实现线性或非线性的调频功能频率暂停功能频率ramped的FSK<25 ps的均方根时钟发生器模式的总抖动Automatic bidirectional frequency sweepingSin(x)/x correctionSimplified control interfaces10 MHz serial 2- or 3-wire SPI compatible100 MHz parallel 8-bit programming3.3 V single supplyMultiple power-down functionsSingle-ended or differential input reference clockSmall, 80-lead LQFP or TQFP with exposed padAPPLICATIONSAgile, quadrature LO frequency synthesisProgrammable clock generatorsFM chirp source for radar and scanning systemsTest and measurement equipmentCommercial and amateur RF exciters双向自动扫频sin(x)/ x修正简化的控制接口兼容10 MHz串行2 或3线SPI总线100兆赫并行8位总线3.3 V单电源供电多重省电功能参考时钟可单端或差分输入小型,80引脚LQFP或带有散热焊盘的TQFP封装应用正交LO频率合成可编程时钟发生器调频雷达和扫描系统的线性调频源测试与测量设备商业及业余射频发射器目录特点................................................. .............................................一应用................................................. ......................................一功能框图............................................... ...............一修订历史................................................ ...............................三一般描述................................................ . (4)规格................................................. (5)绝对最大额定值............................................... . (8)热阻................................................ . (8)测验等级说明.............................................. . (8)防静电提示................................................ . (8)引脚配置和功能说明 (9)典型性能特征 (12)典型应用................................................ .. (16)操作原理............................................... .. (19)操作模式............................................... .. (19)使用AD9854 ............................................... (29)内部和外部更新时钟 (29)ON / OFF输出形键控(侨丰) (29)I和Q数模转换器.............................................. .. (30)控制DAC ................................................ . (30)逆Sinc函数............................................... .. (31)REFCLK乘法器 (31)编程AD9854 ............................................... . (32)主复位................................................ (32)并行I / O操作............................................. (34)串行端口I / O操作............................................ .. (34)一般操作的串行接口 (36)指令字节................................................ .. (37)串行接口引脚说明 (37)串口操作的注意事项............................................. (37)的MSB / LSB的转移.............................................. (38)控制寄存器的说明............................................... .. (38)功耗和散热考虑 (40)热阻抗................................................ . (40)结温事项 (40)评价工作条件 (41)热增强型封装安装指南 (41)评估板................................................ . (42)评估板说明............................................... (42)一般操作说明 (42)使用提供的软件.............................................. (44)支持................................................. (44)外形尺寸................................................ .. (52)订购指南................................................ .. (52)GENERAL DESCRIPTIONThe AD9854 digital synthesizer is a highly integrated device that uses advanced DDS technology, coupled with two internal high speed, high performance quadrature DACs to form a digitally programmable I and Q synthesizer function. When referenced to an accurate clock source, the AD9854 generates highly stable, frequency-phase, amplitude-programmable sine and cosine outputs that can be used as an agile LO in communications, radar, and many other applications. The innovative high speed DDS core of the AD9854 provides 48-bit frequency resolution (1 μHz tuning resolution with 300 MHz SYSCLK). Maintaining 17 bits ensures excellent SFDR.概述在AD9854数字频率合成器是一种高度集成的器件,采用先进的DDS技术,具有两个内部耦合高速,高性能正交数模转换器以实现数字可编程的I/Q合成功能。

AD9854的信号发生器设计

designed by MCU controlled AD9854, has virtues of generating multiple sorts of signals, high precision and programming of output

signals. Its system structure, the design of software and hardware and the way to realize the circuitry is analyzed in detail. Keywor d: Signal Gener ator ; DDS; AD9854

本 文 设 计 中 还 采 用 了 通 信 接 口 ( RS232) 与 PC 机 相联, PC 机的控制命令可以通 过 TXD( Pin10) 和 RXD ( Pin11) 与 W78E58 进行交互, 控制信号源的输出。

3.2 信号的处理 根据 DDS 合成的频谱分析, 由于存在相位截断和 D/A 转换, 输出信号含有高次谐波分量干扰。尤其是输 出信号频率越高, 谐波畸变越大, 本文设计的信号发 生器输出频率最高达 100MHz, 故需进行更有 效的滤 波处理。本设计中采用的小波分析能同时利用信号与 噪声在时域和频域内的差别, 实现更为有效的信噪分 离, 从而获得较为理想的除噪效果。滤除高次谐波时, 利用 3σ准则确定每层小波分解系数的阈值。3σ准则 通常用于测量误差的处理, 主要功能是挑出测量误差 中 的 粗 大 误 差 。基 本 思 想 是:由 于 随 机 误 差 是 服 从 于 正 态分布, 则误差的绝对值主要集中在均值(0)附近。凡 所测数据大于 3σ的则认为是粗大误差,予以剔除。具 体算法为: 1)计算各层细节系数的均方值 σ; 2)将 相应 层的小波变换系数中绝对值大于 3σ的系数置为 0,其 他保持 不变; 3)返回 1)重 新计算 σ的值,继 续比较,如 果小波变换系数中仍然有大于 3σ的值存在,则循环执 行 1)、2),直到该层所有小波变换系数都小 于该次求得 的 3σ。此时的 3σ就是 该层小波分 解系数去噪 阈值。 处理后的系数再进行小波反变换, 即得到预期的波 形 。 把 滤 波 后 的 I 和 Q 通 过 VINP ( Pin42) 、VINN ( Pin43) 脚输入, 经过高速比较器, 即可得到方波信号, 方波信号经过简单的变换, 可得到三角波、锯齿波等。

ad9854单片机程序详细说明(ad9854结构框图及电路)

ad9854单片机程序详细说明(ad9854结构框图及电路)

ad9854结构框图如图4-2所示,AD9854内部包括一个具有48位相位累加器、一个可编程时钟倍频器、一个反sinc滤波器、两个12位300MHzDAC,一个高速模拟比较器以及接口逻辑电路。

其主要性能特点如下:

1.高达300MHz的系统时钟;

2.能输出一般调制信号,FSK,BPSK,PSK,CHIRP,AM等:

3.100MHz时具有80dB的信噪比:

4.内部有4*到20*的可编程时钟倍频器:

5.两个48位频率控制字寄存器,能够实现很高的频率分辨率。

6.两个14位相位偏置寄存器,提供初始相位设置。

7.带有100MHz的8位并行数据传输口或10MHz的串行数据传输口。

两款ad9854应用电路电路一:

下面给出一种用AD9854开发高精度频率信号发生器的简易方法,开发者只需要熟悉MCS-51单片机编程即可。

该系统具有开发周期短,开发成本低的特点,也可以作为探索AD9854功能的一种方法,它的电路原理图见图2。

系统主要由DDS芯片AD9854、单片机AT89C51、看门狗定时器X25045和LED显示驱动芯片MAX7219组成。

在这个系统中提供了8位七段LED显示器,其中前五位为输出频率值,显示范围为00.000~99.999MHz,后三位为幅度显示位,显示范围为0~999,表示幅值从零幅度到满幅度的变化。

电路二:

正交信号源选择了DDS芯片AD9854,具体实现电路见下图。

对AD9854进行编程控制,使之输出两路幅度相同并且正交的信号,然后对输出信号进行滤波,使得正弦波变得更加平滑,滤波之后再把输出峰值为512mV的信号放大2倍到1.24V。

AD9854ASVZ中文数据手册

相位寄存器#2<13:8>(15,14 位无效) 相位寄存器#2<7:0> 频率转换字#1<47:40> 频率转换字#1<39:32> 频率转换字#1<31:24> 频率转换字#1<23:16> 频率转换字#1<15:8> 频率转换字#1<7:0> 频率转换字#1<47:40> 频率转换字#1<39:32> 频率转换字#1<31:24> 频率转换字#1<23:16> 频率转换字#1<15:8> 频率转换字#1<7:0> 三角频率字<47:40> 三角频率字<39:32> 三角频率字<31:24> 三角频率字<23:16> 三角频率字<15:8> 三角频率字<7:0> 更新时钟计数器<31:24> 更新时钟计数器<23:16> 更新时钟计数器<15:8> 更新时钟计数器<7:0> 边沿速率计数器<19:16>(23,22,21,20 不起作用) 边沿速率计数器<15:8> 边沿速率计数器<7:0> 节电控制 时钟倍频控制器 DDS 模式控制与累加器清零控制 传输模式,和 OSK 控制 输出幅度乘法器 I<11:8>(15,14,13,12 不起作用) 输出幅度乘法器 I<7:0> 输出幅度乘法器 Q<11:8>(15,14,13,12 不起作用) 输出幅度乘法器 Q<7:0> 输出边沿变化率控制器<7:0> QDAC,Q 通道 D/A 输入<11:8> QDAC,Q 通道 D/A 输入<7:0>

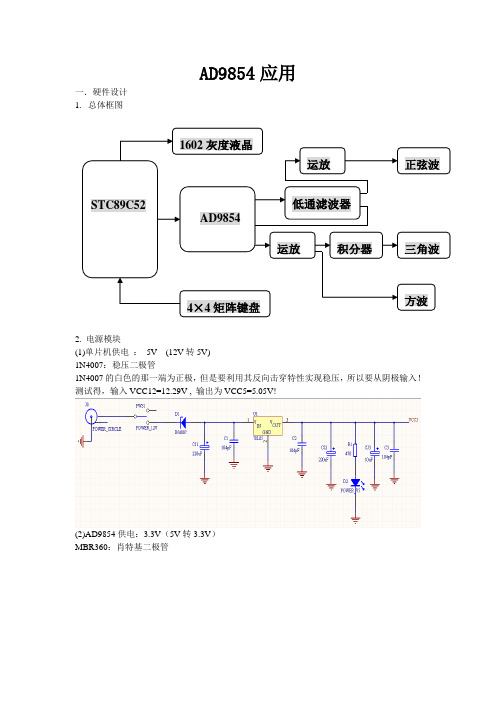

AD9854应用

AD9854应用一.硬件设计 1. 总体框图2. 电源模块(1)单片机供电 : 5V (12V 转5V) 1N4007:稳压二极管1N4007的白色的那一端为正极,但是要利用其反向击穿特性实现稳压,所以要从阴极输入! 测试得,输入VCC12=12.29V , 输出为VCC5=5.05V!(2)AD9854供电:3.3V (5V 转3.3V ) MBR360:肖特基二极管3. 单片机(1)复位(2)晶振(11.0592M )(3)矩阵键盘(4)1602液晶(5)串行下载(6)单片机稳压供电问题参考AD9854的技术文档中的评估板的设计,在VCC5端口并联一个10uF极性电容和8个0.1uF的非极性电容!4. AD9854首先,先仔细阅读AD9854的每个管脚的具体作用的介绍,如下:引脚名称引脚及配置D7-D0 8 位双向并行编程数据输入。

只用于并行编程模式。

DVDD 连接到数字电路的供应电压。

通常为3.3V。

DGND 连接到数字电路的地。

功能同AGND。

NC 无内部连接。

A5-A0 编程寄存器的6位并行地址输入。

只用于并行编程模式。

当使用串行编程模式时A0,A1,A2使用它们各自的另一个功能,如下介绍:A2/IO RESET 串行通讯总线的I/O复位信号。

由于不合适的编程协议而造成无应答就会产生此复位信号。

用这种方式复位串行总线不会影响之前编好的程序,也不会唤醒“默认”编程值。

此脚工作状态为高。

A1/SDO 当使用3线串行通讯模式时的单向串行数据输出。

A0/SDIO 当使用2线串行通讯模式时的双向串行数据输入/输出。

在设计中只用其并型模式。

设计中将其与MSP430F149的P4口相连。

I/O UD CLK 双向I/O刷新时钟。

用作控制寄存器选择方向。

若选择作为输入,则会在上升沿时把I/O端口缓冲器的内容传送到程序寄存器。

若作为输出(默认),则在8个系统时钟周期期间的输出脉冲(低到高)就表明一个内部频率刷新已经发生了。

AD9854的DDS实用外围电路设计和程序

AD9854想必大家都在为AD9854没有电路图,没有资料而头疼吧。

我这里有一份AD9854ASQ的资料,里面有可以用的程序原理图PCB 码原希望对大家有帮助。

现在把我的设计法出来供大家使用参考。

原理图和PCB图为AD9854外围电路!以下是AD9854的控制程序!//#include <reg51f.h>#include "sst89x5xxrd2.h"#include <intrins.h>#define USE_KEY 0#define uchar unsigned char#define uint unsigned int#define schar signed char#define sint signed int#define ulong unsigned long int//须主程序定义的参数/sbit ADDR0 =P2^0; //sbit ADDR1 =P2^1; //sbit ADDR2 =P2^2; //sbit ADDR3 =P2^3; //sbit ADDR4 =P2^4; //sbit ADDR5 =P2^5; ///sbit AD_FUD =P3^7; //UP_DATA sbit RUN =P3^2;sbit WR_LOW =P3^5; // WRsbit MASTER_RESET=P3^3;bit bdata F_Flag,OneSec_Flag,Re_Flag,P_Flag;//uchar SecOne;uchar Time_count;uchar AD_Addr;uchar dats;uchar TAB_Data[40];////初始化串口。

配置定时器// voidinitial_system(){EA = 0;TMOD=0x21; //初始化定时器0PCON=0x00;SCON=0x50;TH0 = 0xdc; //10毫秒定时, 采用晶体11.0592 定时器0,方式1 TL0 = 0x00;TH1 = 0xfd; //波特率9600 采用晶体11.0592 定时器1,方式1 TL1 = 0xfd;TR0 =1; //开启定时器0TR1 =1; //开启定时器0ET0 =1; //时钟0ES =0; //开串口中断EA = 1 ; // 使能所有中断}void Timer0() interrupt 1 using 3{TH0 = 0xdc; //10毫秒采用晶体11.0592 定时器0,方式1TL0 = 0x00;SecOne++;if(SecOne>200) //计时1秒钟{SecOne=0x00;OneSec_Flag=1;RUN=~RUN;}}//void AD9854_delay(int time){int i;for(i = 0; i < time; i++){_nop_();_nop_();_nop_();_nop_();}}void TAB_DataWord(){TAB_Data[0]=0x00; //00H Phase Adjust Register #1 <13:8> (Bits 15, 14 don't care) Phase #1 相位为0TAB_Data[1]=0x00; //01H Phase Adjust Register #1 <7:0> 01HTAB_Data[2]=0x00; //02H Phase Adjust Register #2 <13:8> (Bits 15, 14 don't care) Phase #2 相位为0TAB_Data[3]=0x00; //03H Phase Adjust Register #1 <7:0> 03H//100MTAB_Data[4]=0X31; //Frequency Tuning Word 1 <47:40>//623795E0184ATAB_Data[5]=0X1B; //Frequency Tuning Word 1 <39:32>TAB_Data[6]=0xE6; //Frequency Tuning Word 1 <31:24>TAB_Data[7]=0xE6; //Frequency Tuning Word 1 <23:16>TAB_Data[8]=0x53; //Frequency Tuning Word 1 <15:8>TAB_Data[9]=0x86; //Frequency Tuning Word 1 <7:0>//FTW2TAB_Data[10]=0x31; //Frequency Tuning Word 2 <47:40TAB_Data[11]=0x1B; //Frequency Tuning Word 2 <39:32>TAB_Data[12]=0xE6; //Frequency Tuning Word 2 <31:24>TAB_Data[13]=0xE6; //Frequency Tuning Word 2 <23:16>TAB_Data[14]=0x53; //Frequency Tuning Word 2 <15:8>TAB_Data[15]=0x86; //Frequency Tuning Word 2 <7:0> //500KHZ//FTWTAB_Data[16]=0x01; //Delta Frequency Word <47:40>TAB_Data[17]=0x47; //Delta Frequency Word <39:32>TAB_Data[18]=0xAE; //Delta Frequency Word <31:24>TAB_Data[19]=0x14; //Delta Frequency Word <23:16>TAB_Data[20]=0x7A; //Delta Frequency Word <15:8>TAB_Data[21]=0xE1; //Delta Frequency Word <7:0> 三角波 //频率为0//UpclokTAB_Data[22]=0x00; //Update Clock <31:24>TAB_Data[23]=0x00; //Update Clock <23:16>TAB_Data[24]=0x00; //Update Clock <15:8>TAB_Data[25]=0xF0; //Update Clock <7:0> //系统出现寄存器更新信号reg. Int UpdateClk.=0;外部更新TAB_Data[26]=0x00; //Ramp Rate Clock <19:16> (Bits 23, 22, 21, 20 don't care)TAB_Data[27]=0x00; //Ramp Rate Clock <15:8>TAB_Data[28]=0x00; //Ramp Rate Clock <7:0>TAB_Data[29]=0x10; //Don't Care(0),Don't Care(0),Don't Care(0),Comp PD(1),Reserved_Always Low(0),QDAC PD(0),DAC PD(0),DIG PD(0).TAB_Data[30]=0x20; //Don't Care(0),PLL Range(1),Bypass PLL(1),Ref Mult 4(0),RefMult 3(0),Ref Mult 2(0),Ref Mult 1(0),Ref Mult 0(0).TAB_Data[31]=0x10; //CLR ACC1(0),CLR ACC2(0),Triangle(0)(三角波),SRC QDAC(0),Mode2(0),Mode 1(0),Mode 0(0),Int Update Clk(0). 注意TAB_Data[32]=0x50; //Don't Care(0),Bypass_Inv_Sinc(0),OSK EN(0),OSK INT(0),Don't Care(0),Don't Care(0),LSB First(0),SDO_Active(0).TAB_Data[33]=0x00; //Output Shape Key I Mult <11:8> (Bits 15, 14, 13, 12 don't care)TAB_Data[34]=0x0F; //Output Shape Key I Mult <7:0>TAB_Data[35]=0x00; //Output Shape Key Q Mult <11:8> (Bits 15, 14, 13, 12 don't care)TAB_Data[36]=0x0F; //Output Shape Key Q Mult <7:0>TAB_Data[37]=0xFF; //Output Shape Key Ramp Rate <7:0>TAB_Data[38]=0x00; //QDAC <11:8> (Bits 15, 14, 13, 12 don't care)TAB_Data[39]=0x0F; //QDAC <7:0> (Data is required to be in twos complement format) }void AD9854_ParallelSendByte(uchar addr,uchar data1){// WR_LOW=0; //lhyaddr WR_LOW=WRB_nop_();P2=addr&0x3F;_nop_();P1=data1;WR_LOW=0; //lhyaddr WR_LOW=WRB_nop_();WR_LOW=1;_nop_();_nop_();WR_LOW=0; //lhyaddr WR_LOW=WRB}data0=*(SWord+i);AD9854_ParallelSendByte(Special_addr,data0); AD9854_delay(5);}}void Init9854(void){WR_LOW=0;AD_FUD=0;MASTER_RESET=0;}//void main(void){ uchar i;MASTER_RESET=0;initial_system(); //系统初始化Init9854();TAB_DataWord();MASTER_RESET=0;_nop_();_nop_();_nop_();_nop_();MASTER_RESET=1;AD9854_delay(30);_nop_();_nop_();_nop_();_nop_();_nop_();MASTER_RESET=0;_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();AD9854_delay(500);AD9854_delay(500);AD9854_delay(500);for (i=0;i<40;i++){dats=TAB_Data[i];AD_Addr=i;AD9854_ParallelSendByte(AD_Addr,dats); }_nop_();AD_FUD=0;_nop_();_nop_();_nop_();AD_FUD=1;AD9854_delay(80);_nop_();_nop_();AD_FUD=0;while(1){if(OneSec_Flag==1){_nop_();_nop_();_nop_();AD9854_delay(80);_nop_();_nop_();_nop_();AD9854_delay(80);_nop_();for (i=0;i<40;i++){dats=TAB_Data[i];AD_Addr=i;AD9854_ParallelSendByte(AD_Addr,dats); }_nop_();AD_FUD=0;_nop_();_nop_();AD9854_delay(80);AD_FUD=1;_nop_();AD9854_delay(80); _nop_();_nop_();AD_FUD=0;OneSec_Flag=0; }_nop_();_nop_();}}。

AD9854-DDS模块板

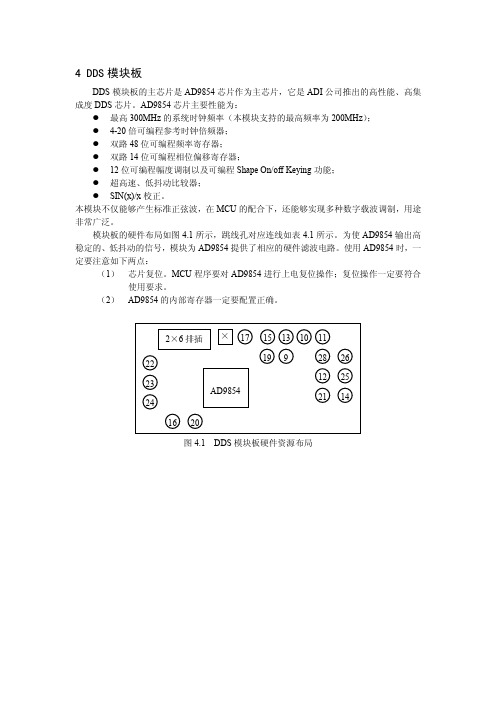

4 DDS模块板DDS模块板的主芯片是AD9854芯片作为主芯片,它是ADI公司推出的高性能、高集成度DDS芯片。

AD9854芯片主要性能为:●最高300MHz的系统时钟频率(本模块支持的最高频率为200MHz);●4-20倍可编程参考时钟倍频器;●双路48位可编程频率寄存器;●双路14位可编程相位偏移寄存器;●12位可编程幅度调制以及可编程Shape On/off Keying功能;●超高速、低抖动比较器;●SIN(x)/x校正。

本模块不仅能够产生标准正弦波,在MCU的配合下,还能够实现多种数字载波调制,用途非常广泛。

模块板的硬件布局如图4.1所示,跳线孔对应连线如表4.1所示。

为使AD9854输出高稳定的、低抖动的信号,模块为AD9854提供了相应的硬件滤波电路。

使用AD9854时,一定要注意如下两点:(1)芯片复位。

MCU程序要对AD9854进行上电复位操作;复位操作一定要符合使用要求。

(2)AD9854的内部寄存器一定要配置正确。

图4.1 DDS模块板硬件资源布局附带的参考文档提供了电路原理图、AD8954的Datasheet和中文使用说明。

Demo程序说明如下:●位置:fpga/ demo_project/ test_parallel_dds。

●功能说明:提供了DDS模块板的演示程序。

该程序能够使模块输出频率为156.25KHz的正弦波。

程序的顶层文件提供了更为详细的工程说明,ucf文件提供了模块的连线方法。

●连线方法:(1)跳线连接底板跳线孔模块板跳线孔TP140 TP17TP136 TP9TP139 TP11TP200 TP22TP207 TP23TP206 TP24TP214 TP15TP208 TP13TP212 TP10TP213 TP19TP216 TP16TP222 TP20(2)排线连接底板排插J4 模块板排插J3J4.1 J3.1J4.2 J3.2J4.3 J3.3J4.4 J3.4J4.5 J3.5J4.6 J3.6J4.7 J3.7J4.8 J3.8J4.9 J3.9J4.10 J3.10J4.11 J3.11J4.12 J3.12。

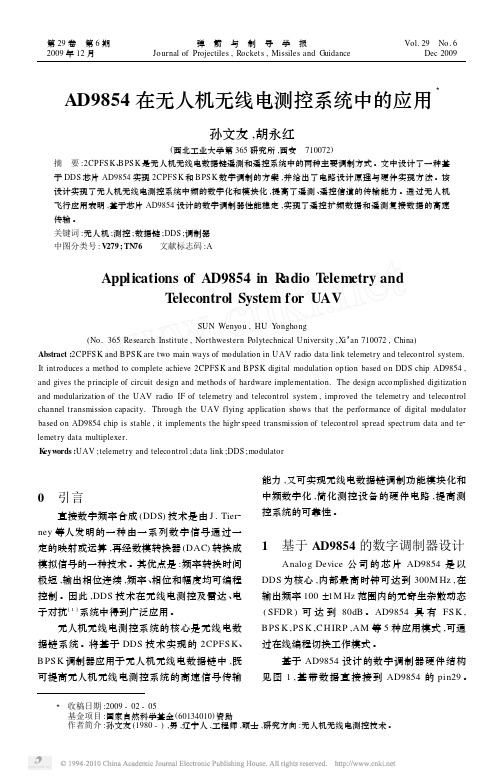

AD9854在无人机无线电测控系统中的应用

φ 2P 0 × 360°

( 4)

式中 :φ 0 为相位调整寄存器的初始相位 ; P 为相 位调整寄存器位数 14 。 当 BPSK 载波 的两个相位分别为

90° 和 270° 时 , 由式 (4 ) 得到相位调整

程序中的 Send_ dds_ byte 是按位发送数据 的子程序 ,因为是 8 位单片机 ,所以每个字节为 8 位二进制 ,子程序代码如下 。

可提高无人机无线电测控系统的高速信号传输

3

收稿日期 :2009 - 02 - 05 基金项目 : 国家自然科学基金 (60134010) 资助 作者简介 : 孙文友 ( 1980 - ) ,男 ,辽宁人 ,工程师 ,硕士 ,研究方向 : 无人机无线电测控技术 。

・236 ・ 犚 犛 2 3 2协议格式 的控制指令 , 经电 平 转 换 成 CMOS 电平后给单片机 , 单片 机 根 据 控 制 指令改变 AD9854

Send_dds_byte : clr mov mov rlc mov set b nop clr djnz ret dds_sclk R1 ,Send_dds_bit dds_sclk R1 , # 008 H A ,R0 A dds_data ,C dds_sclk

孙文友 ,胡永红

( 西北工业大学第 365 研究所 ,西安 710072)

3

摘 要 :2CPFS K、 B PS K 是无人机无线电数据链遥测和遥控系统中的两种主要调制方式 。文中设计了一种基 于 DDS 芯片 AD9854 实现 2CPFS K 和 B PS K 数字调制的方案 , 并给出了电路设计原理与硬件实现方法 。该 设计实现了无人机无线电测控系统中频的数字化和模块化 ,提高了遥测 、 遥控信道的传输能力 。通过无人机 飞行应用表明 ,基于芯片 AD9854 设计的数字调制器性能稳定 ,实现了遥控扩频数据和遥测复接数据的高速 传输 。 关键词 : 无人机 ; 测控 ; 数据链 ;DDS ; 调制器 中图分类号 : V279 ; TN76 文献标志码 :A

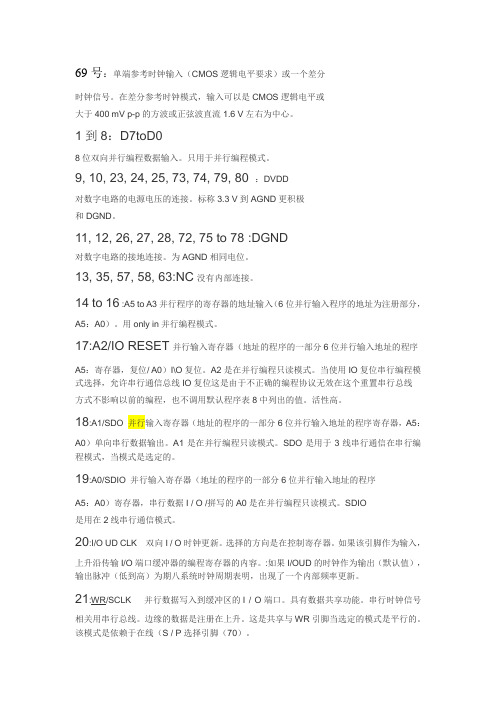

AD9854管脚信息中文

69号:单端参考时钟输入(CMOS逻辑电平要求)或一个差分时钟信号。

在差分参考时钟模式,输入可以是CMOS逻辑电平或大于400 mV p-p的方波或正弦波直流1.6 V左右为中心。

1到8:D7toD08位双向并行编程数据输入。

只用于并行编程模式。

9, 10, 23, 24, 25, 73, 74, 79, 80 :DVDD对数字电路的电源电压的连接。

标称3.3 V到AGND更积极和DGND。

11, 12, 26, 27, 28, 72, 75 to 78 :DGND对数字电路的接地连接。

为AGND相同电位。

13, 35, 57, 58, 63:NC没有内部连接。

14 to 16 :A5 to A3并行程序的寄存器的地址输入(6位并行输入程序的地址为注册部分,A5:A0)。

用only in并行编程模式。

17:A2/IO RESET并行输入寄存器(地址的程序的一部分6位并行输入地址的程序A5:寄存器,复位/ A0)I\O复位。

A2是在并行编程只读模式。

当使用IO复位串行编程模式选择,允许串行通信总线IO复位这是由于不正确的编程协议无效在这个重置串行总线方式不影响以前的编程,也不调用默认程序表8中列出的值。

活性高。

18:A1/SDO 并行输入寄存器(地址的程序的一部分6位并行输入地址的程序寄存器,A5:A0)单向串行数据输出。

A1是在并行编程只读模式。

SDO是用于3线串行通信在串行编程模式,当模式是选定的。

19:A0/SDIO 并行输入寄存器(地址的程序的一部分6位并行输入地址的程序A5:A0)寄存器,串行数据I / O /拼写的A0是在并行编程只读模式。

SDIO是用在2线串行通信模式。

20:I/O UD CLK 双向I / O时钟更新。

选择的方向是在控制寄存器。

如果该引脚作为输入,上升沿传输I/O端口缓冲器的编程寄存器的内容。

:如果I/OUD的时钟作为输出(默认值),输出脉冲(低到高)为期八系统时钟周期表明,出现了一个内部频率更新。

c51单片机驱动AD9954的程序及调试笔记

c51单片机驱动AD9954的程序及调试笔记2009年寒假前几天,第一次用51单片机写AD9954程序,仔细读了一遍datasheet、并参考前面同学的示例程序之后,只简单的实现了单频输出(Single-tone Mode)。

一开始调试,先要正确控制SYNC_CLK,因为这个输出引脚就是内部DDS时钟的4分频(假设DDS时钟最高为400MHz,那么SYNC_CLK此时应当输出100MHz;反之,通常用SYNC_CLK来推测DDS系统时钟)。

前提是必须复位Control Function Register No.1(CFR1:0x00)中的bit1(SYNC_CLK Disable)。

然后根据输入时钟的频率正确设置CFR2中的倍频系数REFCLK Multiplier和VCO Range(0:100~250MHz;1:250~400MHz)。

只要外部电路没什么错的地方,SYNC_CLK 一般都OK了。

用了才发现,AD9954真的还不错,400MHz的系统时钟就先不说了,居然可以用控制字Amplitude Scale Factor (ASF:0x02)调节输出信号的幅度,前提是打开CFR1中的OSK Enable。

并且14bit的长度也能够达到足够高的幅度控制精度了。

当时作信号源的时候,还用外接AD835+TLV5638控制幅度,现在想来真是憨啊。

还有就是,输出信号的相位可调。

控制字Phase Offset Word(POW0 0x05)中含有14bit的相位偏移控制字,因此相位调节的精度也是相当高的,可达360°/16384 = 0.022°,在大多数情况下肯定够用,比AD9851的5bit控制字(360°/32 = 11.25°)强多了。

具体见程序1。

然后想尝试一下线性扫频功能(Linear-sweeping Mode),调了一整天都没出来,然后就放假回家了。

AD9954芯片资料中文版

AD9954- Direct Digital Synthesizer400 MSPS 14-Bit, 1.8 V CMOS功能: (2)应用 (2)概述 (2)AD9954电气特性 (3)最大操作范围 (4)Table 2. (4)管脚定义 (4)管脚功能描述 (4)典型的性能特性 (6)原理 (7)器件块 (7)控制寄存器位描述 (10)Other Register Descriptions 其他寄存器描述 (14)Programming AD9954 Features-- AD9954编程特性 (18)SERIAL PORT OPERATION串口操作 (19)INSTRUCTION BYTE指令字节 (20)SERIAL INTERFACE PORT PIN DESCRIPTION串行接口管脚描述 (20)MSB/LSB TRANSFERS (20)RAM I/O VIA SERIAL PORT (21)Power-Down Functions of the AD9954 AD9954省电功能 (21)功能:400MSPS 内部时钟 集成14位DAC可编程相位/幅度抖动 32位控制字相位噪声小于等于-120dbc/Hz@1kHz(DAC 输出)出色的动态性能>80db SFDR@160MHz (偏离100KHz ) 串行I/O 口控制 超高速模拟比较器 自动线性和非线性扫频能力 4种频率/相位偏移坡面 1.8v 电压供电软件或者硬件控制休眠内部集成1024字节*32位RAM 大多数输入口支持5v 电平PLL REFCLK 乘法器(4倍-20倍) 单晶振驱动内部时钟 相位调制能力 多芯片同步 应用敏捷LO 频率输出 可编程的时钟发生器雷达和扫频系统中的FM 啁啾源自动雷达测试和测量设备 声光设备驱动概述AD9954具有一个14位DAC 最高达400 MSPS 的DDS 。

AD9954使用了先进的DDS 技术,内部集成高速,高性能的DAC 形成数字可编程,完整的高频合成器,能产生高达200MHz 模拟正弦波的能力。

基于AD9854的高精度高频信号发生器的设计

Biography:Ma Lu,male,was born in November 1981,Han nation-

triggering

to

ensure

Call

quick responses

event

the

output wave frequency

stable。It is

designed

for

Cooling Storage Ring

of

Cyclotron System in Lanshou.It is used Key words:ACEXlKS0,AD9854,Signal Generator

conversion pulse pl=>ADC_aut=p2;

———-start

p2=>ADC_aut=p3;

IF IF; nBusyADC

WHEN p3=>RC_ADC—j沁.r=vcc;

ADC_aut=p4;ELSE ————waiting Busy

THEN

ADC_ant=p3;END

End

WHEN p4=>SerEn.S=VCC;ADC_aut。p5; 一一Enable serializafion WHEN

Heavy Ion

as

signal process and control unit in RF cavity of CSRm.

1引言.

在现代科研、通信、电子产业中,信号发生器的精确性和稳 定性往往决定了整个系统的性能与稳定与否,所以如何设计制 造高品质的信号发生器成为一个很重要的课题。随着微电子技

基于AD9854的多功能高精度DDS信号源设计

基于AD9854的多功能高精度DDS信号源设计

张铮;胡婷

【期刊名称】《电子科技》

【年(卷),期】2017(030)003

【摘要】为得到性能更好、价格更加低廉的高精度信号源,文中提出了通过采用AD9854芯片实现多功能高精密DDS信号源设计.在系统设计过程中不仅通过程控技术实现对波形的控制,而且应用单片机程序对数字信号进行处理.将AT89 C51单片机与AD9854芯片相结合,实现了信号从数字量到模拟量之间的转换,通过模拟仿真和实际测试,测试结果表明,所设计的DDS信号源完成了高精度多功能DDS信号源的设计和模拟实现.

【总页数】3页(P182-184)

【作者】张铮;胡婷

【作者单位】兰州交通大学电子与信息工程学院,甘肃兰州730070;兰州交通大学电子与信息工程学院,甘肃兰州730070

【正文语种】中文

【中图分类】TN942

【相关文献】

1.基于DDS的高精度信号源的设计与实现 [J], 宗接华;

2.基于AD9854的多功能信号源设计 [J], 王成华;叶佳

3.基于DDS技术的可调高精度信号源设计 [J], 罗嗣乔;何春晖

4.基于FPGA的DDS高精度信号源设计分析 [J], 贾亮;孙伟;马兴;孙军

5.基于DDS技术的高精度数控信号源设计 [J], 周遐;金瑞;曹云川

因版权原因,仅展示原文概要,查看原文内容请购买。

基于AD9854的信号发生器设计

自然科学科技进展2016年2月 第5期·265·ꢀ基于AD9854的信号发生器设计肖昂弘 谢鸿钧 苏伟康 林 立 黄昌诚华南师范大学物理与电信工程学院,广东 广州 510006摘要:介绍了用数字方式实现频率合成技术的基本原理和DDS芯片AD9854的内部结构及工作模式。

设计了一种采用STM32单片机控制AD9854为核心的信号发生器,它具有输出信号精度高、可程控等特点。

文中详细分析了该信号发生器的系统结构、软硬件设计和具体实现电路。

关键词:信号发生器;DDS;AD9854;STM32中图分类号:TN741 文献标识码:A 文章编号:1671-5578(2016)5-0265-02引言在现代科研、通信系统、电子对抗及各种电子测量技术中,一个高精度、频率可调的信号源是很多电子设备和系统实现高性能的关键。

随着数字集成电路和微电子技术的发展,直接数字合成技术(DDS)将先进的数字处理技术与方法引入信号合成领域,优越的性能和突出的特点使其成为现代频率合成技术中的佼佼者。

DDS器件采用了高速数字电路和高速D/A转换技术,具备了频率转换时间短、相对带宽宽、频率分辨率高、输出相位连续和相位可快速程控切换等优点,可以实现对信号的全数字式调制。

而且,由于DDS是数字化高密度集成电路产品,芯片体积小、功耗低,因此可以用DDS构成高性能频率合成信号源来取代传统频率信号源产品。

1 方案论证1.1 单片机选型方案一:采用现在比较通用的51系列单片机。

51系列单片机的发展已经有比较长的时间,应用比较广泛,各种技术都比较成熟,但此系列单片机是8位机,处理速度不是很快,资源不够充足,而且其最小系统的外围电路都要自己设计和制作,使用起来不是很方便,故不采用。

方案二:选用意法半导体公司的STM32F103VET6单片机。

STM32F103VET6单片机是16位的处理器,主频可以达到72MHz,速度足够快,再加上其具有FSMC接口驱动TFT显示屏,和方便的ADC接口,可以完成对信号的采集,实现幅频特性曲线分析。

单片机控制AD9850的信号发生器C51程序可直接用

单片机控制AD9850的数字信号发生器C51程序单片机控制AD9850的数字信号发生器C51程序//-----------------------函数声明,变量定义------------------------------#include <reg51.h>#include <intrins.h>#include<ABSACC.H>//-----------------------定义管脚----------------------------------------#define data_OUT P1sbit FQ_UD=P3^0; //AD9850信号更新申请sbit W_CLK=P3^1; //写控制字时钟unsigned char CON_word[5];//Word data[7] data[6] data[5] data[4] data[3] data [2] data[1] data[0]//W0 Phase b Phase b3 Phase b2 Phase b1 Phase b0 Power Down Control Control//W1 Freq-b31 Freq-b30 Freq-b29 Freq-b28 Freq-b27 F req-b26 Freq-b25 Freq-b24//W2 Freq-b23 Freq-b22 Freq-b21 Freq-b20 Freq-b19 F req-b18 Freq-b17 Freq-b16//W3 Freq-b15 Freq-b14 Freq-b13 Freq-b12 Freq-b11 F req-b10 Freq-b9 Freq-b8//W4 Freq-b7 Freq-b6 Freq-b5 Freq-b4 F req-b3 Freq-b2//--------------------------------------------------------------------------------------------------// 函数名称: delay// 入口参数: N// 函数功能:延时子程序,实现(16*N+24)us的延时// 系统采用11.0592MHz的时钟时,延时满足要求,其它情况需要改动//--------------------------------------------------------------------------------------------------void delay(unsigned int N){int i;for(i=0;i<N;i++);}//--------------------------------------------------------------------------------------------------// 函数名称: WRITE_AD9850// 函数功能:将控制字写入AD9850//--------------------------------------------------------------------------------------------------void WRITE_AD9850(void){unsigned char i;FQ_UD=0;W_CLK=0;delay(0);CON_word[0]=CON_word[0]&0xFC; //置工作方式选择位为00for(i=0;i<5;i++){data_OUT=CON_word[i]; //送控制字W_CLK=0;delay(0);W_CLK=1; //上升延delay(0);}FQ_UD=1; //上升延要求AD9850改变输出}//--------------------------------------------------------------------------------------------------// 函数名称:main// 用户主函数// 函数功能:主函数//--------------------------------------------------------------------------------------------------void main(){FQ_UD=0;WRITE_AD9850();} <下面是总结的一些设计中应注意的问题,和单片机硬件设计原则,希望大家能看完(1)在元器件的布局方面,应该把相互有关的元件尽量放得靠近一些,例如,时钟发生器、晶振、CPU的时钟输入端都易产生噪声,在放置的时候应把它们靠近些。