Encoding Temporal Logics in Executable Z A Case Study for the ZETA System

模型检验

• Fφ: “Sometime in the future it will be the case thatφ” • Gφ;“Always in the future it will be the case thatφ ” • Pφ: “Sometime in the past φ was the case” • Hφ: “Always in the past φ was the case” • Also: sometime Eφ / always Aφ

推导: at(B!m0)←→at(b!ack0)←→after(a?ack0)←→success(m0) 得出:P1:at(B!m0)←→success(m0) P1表示接收端向其用户递交报文m0等价亍报文m0已经成功

• 同理,我们可以根据CH2,AS4,AR4得出P2: at(B!m1)←→success(m1); • 其他的推导: • 由AR1和AR3得到X1:◇at(B!m0)→□◇after(b?m0) • 由X1和CH3得到P3:◇at(B!m0)→□◇at(a!m0) • 同理,可得到P4: ◇at(B!m1)→□◇at(a!m1) • P3表示接收方向用户B递交报文m0说明収送方多次向通道 収送报文m0; • 由CH1和AR3得到X2:after(a?ack0)←→at(B!m0) • 由X2和AS1得到X3: • (seq=0)∧after(A?any)→◇□◇at(a!m0) at(B!m0)

形式化验证的基本概念

• • • • 例:组合电路的形式化验证 输入:a,b,c,d 输出:x x=f(a,b,c,d) 电路行为是:

• F=c ∧d ∨a∧b ∧d∨ ┐ a∧ ┐ b∧d∨ ┐ a∧ ┐ c∧d a 。 b 。 c 。 d 。

线性时态逻辑LTL的一个公理系统及其可靠性证明

LTL的一个公理系统及其可靠性证明题目:LTL的一个公理系统及其可靠性证明@binzhengLTL的一个公理系统及其可靠性证明题目(列出相应的参考文献):提高题1. 给出LTL的一个可靠的公理系统并证明其可靠性。

1) 以写出的独立的公理数目作为评分标准。

2) 不必证明写出公理的独立性。

答:一、根据课程讲义的语义规定:⏹Let σ be a sequence s0 s1 s2… in a Kripke Model M⏹Let σi be a suffix of σ: s i s i+1 s i+2… (σ0 =σ )⏹σi |= p, where p a proposition, if p is in L(s i).⏹σi |= Φ/\ψ if σi |= Φ and σi |= ψ.⏹σi |= Φ\/ψ if σi |= Φ or σi |= ψ.⏹σi|= ¬Φ if it is not the case that σi |= Φ.⏹σi |= OΦ if σi+1 |= Φ⏹σi |= <>Φ if for some j≥i, σj |= Φ.⏹σi |= []Φ if for each j≥i, σj |= Φ.⏹σi |= ΦU ψ if for some j≥i, σj|=ψ.and for each i≤k<j, σk |=Φ.⏹σi |= ΦR ψ if either for every j≥i, σj |= ψ or for some j≥i, σj|= Φ and,for every i≤k≤j, σk |= ψ.⏹Intuitively, ΦR ψ means ψ holds forever or holds until some pointswhere both Φ and ψ hold.二、以下是LTL的一个可靠的公理系统(共19个公理)及其证明记Φ,ψ,ρ为LTL语法定义中的公式公理1)O (Φ∨ψ) ≡(O Φ) ∨(O ψ)左边到右边:由语义定义,σi+1 |= (Φ∨ψ),即或者σi+1 |= Φ,或者σi+1 |=ψ,即(O Φ) ∨(O ψ)。

UnconstrainedPaths解决办法

UnconstrainedPaths解决办法⽤TimeQuest对DAC7512控制器进⾏时序分析在对某个对象下时序约束的时候,⾸先要能正确识别它,TimeQuest 会对设计中各组成部分根据属性进⾏归类,我们在下时序约束的时候,可以通过命令查找对应类别的某个对象。

TimeQuest对设计中各组成部分的归类主要有cells,pins,nets和ports ⼏种。

寄存器,门电路等为cells;设计的输⼊输出端⼝为ports;寄存器,门电路等的输⼊输出引脚为pins;ports和pins之间的连线为nets。

具体可以参照下图(此图出⾃Altera Time Quest的使⽤说明)。

下⾯我们按照本⽂第⼆部分⽤TimeQuest做时序分析的基本操作流程所描述的流程对DAC7512控制器进⾏时序分析。

建⽴和预编译项⽬的部分相对简单,涉及到的也只是QuartusII的⼀些基本操作,这⾥我们就不再做具体的叙述。

主要介绍如何向项⽬中添加时序约束和如何进⾏时序验证。

⾸先建⽴⼀个名称与项⽬top层名字⼀致的sdc⽂件,然后按照下⾯的步骤添加时序约束。

1. 创建时钟添加时序约束的第⼀步就是创建时钟。

为了确保STA结果的准确性,必须定义设计中所有的时钟,并指定时钟所有相关参数。

TimeQuest⽀持下⾯的时钟类型:a) 基准时钟(Base clocks)b) 虚拟时钟(Virtual clocks)c) 多频率时钟(Multifrequency clocks)d) ⽣成时钟(Generated clocks)我们在添加时序约束的时候,⾸先创建时钟的原因是后⾯其它的时序约束都要参考相关的时钟的。

基准时钟:基准时钟是输⼊到FPGA中的原始输⼊时钟。

与PLLs输出的时钟不同,基准时钟⼀般是由⽚外晶振产⽣的。

定义基准时钟的原因是其他⽣成时钟和时序约束通常都以基准时钟为参照。

很明显,在DAC7512控制器中,CLK_IN是基准时钟。

3. temporal logic_687102912

时序逻辑时序辑线性时序逻辑(LTL)线性时序逻辑线性时序逻辑,简称LTL(Linear Temporal Logic)。

系统状态变化的可能性被表示为系统所有可能执行路径的集合。

条路径代表系统的次可能执行情况一条路径代表系统的一次可能执行情况。

在每条路径上,只存在一个后续状态。

LTL语法LTL公式由以下规则递归定义:任意原子命题都是LTL公式;如果p和q 是LTL公式,则¬p, p ∧q, X p, F p, G p和p U q也都是LTL公式。

FG p GFp¬ q U (¬ p例如:FG p, GFp, ¬ q U (¬ p ∧¬ q)LTL 语义设中的一条路M 是Kripke 结构,π: s 0→s 1→s 2→…是M 中的条路径,f 和g 为LTL 公式,根据以下规则定义M , π|= f :M, π|= piff p ∈L(s 0), 其中p 是原子公式M, π|= f ∧g iff (M, π|= f )且(M, π|= g )M (M 1M, π|= ¬f iff (M, π|= f )不成立M | Gf iff j (M | f )M, π|= Ffiff ∃j. (M, πj |= f )M, π|= Xf iff (M, π|= f )M, π|= f U g iff ∃k. (M, πk |= g ) 且∀j < k (M, πj |= f)M, π|= Gf iff ∀j. (M, πj |= f )LTL 语义的直观解释解释Fp Gp pp p p p pXppUqppppq基本的时序模态词F 沿当前路径 F p :沿当前路径,p 终将成立G p :沿当前路径,p 总是成立X p :沿当前路径,p 在下一个状态成立p U q :沿当前路径,p 一直成立直到q 成立LTL语义语法中不包括路径量其语义观点要求考虑所有路 LTL语法中不包括路径量词,其语义观点要求考虑所有路径。

C++常见编译的英语提示的翻译

批判性推理基础学习CriticalReasoningforbeginners全记录文本

Critical Reasoning for beginnersby Marianne Talbot OxfordLess on 1 How to recog nize argume nts and Whatis the n ature of argume ntsArguments are a set of senten ces such that one of them (the con clusi on) is being said to be true, and the other(s) (the premises) are being offered as reasons for believ ing the truth of the one.An argume nt isn't a set of con tradicti ons.Part of the point of an argument is to move us on from where we are to somewhere a bit further. Argume nts lead to deeper thoughts. (from where we are to where we want)An Argume nt:(one or more) Premises i Con clusi on (Fun cti on) [to prove---reas ons] [suppose true]relati on ship among senten cese.g. It's Friday.Maria nne always wears jea ns on Friday.Therefore Maria nne will wear jea ns today.Play atte nti on to suppressed premises (隐藏前提)con text ----- all senten ces may be argume nt.implicatio n (实质蕴涵)en tailme nt (逻辑蕴涵)Disti nguish argume nts from(a)sets of senten ces not related as argume nts(1)aren't related at alle.g. The sea is salt.Sydney is in Australia.(2)related but not an argume nte.g. Towards lun chtime clouds formed and the sky blacke ned. The n the storm broke.(b)senten ces (asserti ons) 'if...the n...'e.g. If it is snowing, the mail will be late.(implicatio n not en tailme nt)An argument is a set of sentences, one of which is being asserted.An assert ion is a sin gle sentence (possibly complex) ,that is being expressed in assertive mode.'because' may be causal or rati on al.reas on and causecausal relati ons (因果关系) and rati onal relatio ns (推理关系)A andB en tailC does n't mea n A and B cause C.e.g. It's Friday. (A)Maria nne always wears jea ns on Friday. (B)Therefore Maria nne will wear jea ns today. (C)expla natio n:(1) causal expla nation (因果性解释):e.g. Pawl fell dow n because he wan ted to amuse childre n.⑵ ratio nal expla nation (推理性解释):e.g. Pawl fell dow n because Jelly pushed him.Facts are what makes sentences true or false. They are not true or false, they just exist or don't exist.Only beliefs or sentences that express beliefs are true or false.Belief (e.g. concept) ............ t he con cept 'chair'Language ......................... t he Ian guage 'c-h-a-i-r'Reality .......................... t he object 'chair'Argume nts can only be good or bad ,they can only be valid or in valid ,they can't be true or false because the only thing that can be true or false is beliefs or the senten ces that express beliefs.A good argume nt is one in which:(1)the conclusion must follow the premises(2)the premises must all be true .The conclusion must be true. (truth preserving)逻辑学并不关心前提正确与否,而只关心前提与结论的关系。

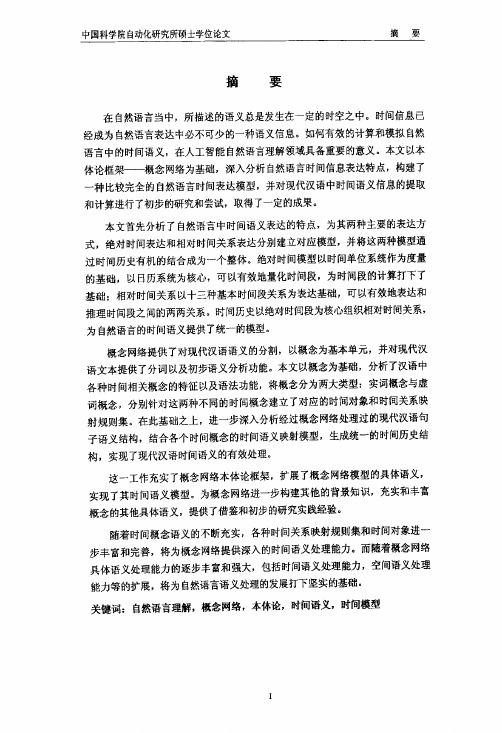

自然语言时间语义信息处理

第三章时间信息表达与推理模型

行为描述是指对于概念的行为进行形式化的描述,概念网络目前采用的是脚本描述方法,这种方法简单方便,而且推理链可以清晰呈现,虽然描述的灵活性不够,效率需要进一步提高,但已经可以基本实现对于现代汉语中虚词行为规则的有效分析和描述。

基于此,对于自然语言中实词和虚词两大词类,都有了相应的语义处理方法,并可以实现对于句子的统一分析:分词之后,首先确定词汇对应的概念,然后通过概念复合规则对相关概念进行语义复合,接着进一步分析概念类脚本的执行和成员脚本的执行,达到对语义的初步分析处理。

概念网络不仅仅是一种知识表示方法,而且已经搭建起了概念网络平台。

概念平台将概念按照领域区分存放,加载了特定领域的概念库之后,便可以对相应的领域概念的属性、行为等特征进行编辑,添加概念之间的语义状态、语义约束等相关语义联系。

由于目前概念网络平台的概念语义知识有限,还无法达到自动分析获取语义的阶段,因此初期为了确保准确性,采用手工添加概念语义特征的方法。

在此实验平台之上,当构建了比较丰富的语义之后,可以进一步添加自动学习的方法,分析语料的语义关联,以自动获取概念语义定义。

概念平台中除了概念的定义和浏览模块,还增加了中文文本分词,文本理解接口,初步实现了对已定义概念的语义复合功能,参见图3—2。

3—2概念网络语义处理平台。

欧洲高校计算机专业的形式化方法课程教学

99文章编号:1672-5913(2008)10-0099-05欧洲高校计算机专业的形式化方法课程教学古天龙,董荣胜(桂林电子科技大学,广西 桂林 541004)摘 要:本文对欧洲高等院校的计算机相关专业形式化方法教育进行了介绍,主要包括形式化方法课程的知识体系、形式化方法教育的课程及其内容。

关键词:计算机学科;形式化方法;知识体系;欧洲高校 中图分类号:G642 文献标识码:B形式化方法是基于严密的、数学上的形式机制的计算机系统研究方法。

从20世纪90年代开始,计算机学科相关专业的形式化方法的教育引起了欧美教育界的高度重视和关注。

欧洲的英国、德国、法国、意大利、荷兰、西班牙等国家的高校相继为研究生开设了形式化方法方面的课程,并推广至本科生教育。

从20世纪90年代中期开始,美国高校也开展了形式化方法教育研究,并在美国顶尖的35所大学的计算机学科实施了研究生和本科生的教育实践。

IEEE-CS 和ACM 联合任务组于2005年9月提交了计算教程CC2005(Computing Curricula 2005)最终报告,该报告的软件工程分册CCSE(Computing Curriculum- Software Engineering 2004)将“软件工程的形式化方法(Formal Methods in Software Engineering)”列为一门核心课程。

CC2005最终报告的推出对计算机学科相关专业的形式化方法教育产生了重要的影响。

欧洲形式化方法协会于2001年成立了专门的形式化方法教育研究分会FME-SoE(Formal Methods Europe Association - Subgroup on Education),目的在于研究并提出高等院校本科生形式化方法教育的知识体系及课程内容。

该组织于2004年11月发布了对欧洲11个国家、58所高等院校中的117门形式化方法教育相关课程的调研报告。

CTL3. temporal logic_960301659

软件形式化验证第三章 时序逻辑贺 飞 清华大学软件学院 2010年3月2011年3月14日星期一1属性规约为验证系统满足某条性质:1. 2. 3. 3对系统进行建模,得到系统模型 对属性进行说明,得到属性公式 执行模型检测算法如何以一种形式化语言无歧义的描述系统属性?2011年3月14日星期一2时序逻辑Temporal logic provides a formal system p g p y qualitatively describing and reasoning about how the truth values of assertions change over time g It is appropriate for describing the time-varying behavior of systems (or programs). y ( p g ) Example: System can always run into working status after being started AG (Started → AF Working)March 14, 20113常用的时序逻辑1. 1 2. 3.计算树逻辑( CTL) 线性时序逻辑( LTL) 扩展的计算树逻辑 (CTL*)2011年3月14日星期一4时序 辑 时序逻辑计算树逻辑(CTL)2011年3月14日星期一5计算树逻辑计算树逻辑,简称 CTL (Computation Tree Logic)。

是一种分枝时序逻辑 系统状态变化的可能性被表示成树状结构 从 个系统状态出发,存在多个可能的后续状态 从一个系统状态出发,存在多个可能的后续状态2011年3月14日星期一6本节内容CTL语法 CTL语义 CTL等价关系 CTL最小联结词集合 CTL属性范例2011年3月14日星期一7Computation Tree Logic (CTL)CTL = Classical propositional logic + temporal operatorsPropositional LogicTemporal operatorsMarch 14, 20118命题逻辑——语法P, Q, R, ... : ¬P: P∧Q : P∨Q : Q P→Q: P↔Q: Propositional symbols Negation of P Conjunction: P and Q Disjunction: P or Q j Implication: if P then Q Equivalence: P if and only if QMarch 14, 20119命题逻辑——语义P 0 0 1 1Q 0 1 0 1¬P 1 1 0 0P∧Q 0 0 0 1P∨Q 0 1 1 1P→Q 1 1 0 1P↔Q 1 0 0 1March 14, 201110CTL的时序联结词CTL以命题逻辑为基础,扩展了新的语法元素 路径量词A:对所有路径(All)E:存在一条路径(Exist)时序模态词X:下一个状态(neXt)未来某个状态(F tF:未来某个状态(Future)G:所有未来状态(Global)直到lU:直到(Until)CTL语法CTL公式由以下规则递归定义每一个原子命题都是CTL公式;如果f和g是CTL公式,则¬f, f∧g, AF g, EF g , AG f, EG f, AX f, EX f, A(f U g), E(f U g) 也都是CTL公式。

python中logic用法

python中logic用法Python中logic用法1. if语句•使用if语句可以根据条件来执行不同的代码块。

•格式:if condition : (若condition为真,则执行以下代码)•示例:x = 10if x > 5:print("x大于5")# 输出结果:x大于52. else语句•在if语句之后,可以使用else语句来执行在条件为假时执行特定的代码块。

•格式:else: (如果上一个条件为假,则执行以下代码)•示例:x = 3if x > 5:print("x大于5")else:print("x小于等于5")# 输出结果:x小于等于53. elif语句•elif语句用于在多个条件之间进行判断,类似于多个if语句的组合,但更简洁。

•格式:elif condition : (如果上一个条件为假且当前条件为真,则执行以下代码)•示例:x = 7if x > 10:print("x大于10")elif x > 5:print("x大于5,小于等于10")else:print("x小于等于5")# 输出结果:x大于5,小于等于104. 布尔逻辑运算符•Python提供了三个布尔逻辑运算符:and、or和not,用于在条件判断中组合多个条件。

•and: 如果两个条件都为真,则结果为真;否则为假。

•or: 如果两个条件中至少有一个为真,则结果为真;否则为假。

•not: 对给定的条件取反。

•示例:x = 5y = 7if x > 0 and y > 0:print("x和y都大于0")if x > 10 or y > 10:print("x或y至少有一个大于10")else:print("x和y都小于等于10")if not x > 0:print("x小于等于0")# 输出结果:# x和y都大于0# x和y都小于等于10# x小于等于05. in运算符•in运算符用于检查某个值是否存在于一个列表、元组、字符串等可迭代对象中。

Guardmaster 440C-CR30 Safety Relay 版本11 目录号440C-CR

Release NotesOriginal InstructionsGuardmaster 440C-CR30 Safety Relay, Revision 11Catalog Number 440C-CR30-22BBBSummary of ChangesThis publication contains the following new or updated information. This list includes substantive updates only and is not intended to reflect all changes.About This PublicationThese release notes supplement the existing documentation supplied with your product. Read this document before using Guardmaster® 440C-CR30 safety relays.Firmware Revision HistoryAvailability of Enhancements and Anomaly FixesEnhancements are available in the safety relay only if it is at the required firmware revision or higher and the Connected Components Workbench™ or Studio 5000 Logix Designer® project contains a safety relay that is configured with the required firmware revision or higher. If the project contains a safety relay revision that is lower than the required revision for an enhancement, then the project is still valid but the enhancement will not be available until the project is upgraded to the minimum supported revision.Fixes for firmware anomalies are available as long as the safety relay firmware revision is at the minimum revision or higher. The configured safety relay revision must be of the same major revision.The following tables provide a list of enhancements, known anomalies, and corrected anomalies for the CR30 safety relay firmware revisions.EnhancementsTopicPage Updated Firmware Revision History 1Updated Table 22Updated image in step 23Revision Description6.004First revision release [safety firmware 0A.01]6.006Minor revision release [safety firmware 0A.02]7.006Major revision release [safety firmware 0A.02]8.013Major revision release [safety firmware 0A.02]9.004Major revision release [safety firmware 0A.02]10.004Major revision release [safety firmware 0A.03]10.009Minor revision release [safety firmware 0A.03]10.010Minor revision release [safety firmware 0A.03]10.011Minor revision release [safety firmware 0A.03]Table 1 - EnhancementsEnhancement (1)DescriptionAvailable From Firmware RevisionLock control function support New Lock Control function is now supported forissuing an unlock request to a safety gate withguard locking.10.004Mode selection function support New Mode Selection Safety Monitoring Function is now supported.10.004Mute function enhancements New Muting function block has been enhanced to support a mute enable input, a mute fault manual monitored reset and now offers a secondary output based on the override status.10.004Status function supportNew Status functions for monitoring andannunciating function block faults or ‘waiting for reset’ conditions.10.004Reusable feedback supportNew ability to apply feedback inputs to multiple Safety Output Functions.10.004Single input And withRestartenhancement New ability for the And with Restart logic function to support one input.10.004PanelView Plus Tag browsing support With release 8.00 of FactoryTalk® View Studio, PanelView™ Plus can communicate to CR30 safety relays using EDS parameter browsing over EtherNet/IP™.9.004Nesting of Logic Level Function blocksNew ability to use the output state of a logic block immediately above another logic block as an input condition.9.004Inverting of Logic Level Inputs/Outputs New ability to invert (logical NOT) of inputs and outputs of Logic Level function blocks.9.004Output Loop Safety Monitoring Function support New Output Loop Safety Monitoring Function that allows the logical state of a Safety Output Function to be used as an input condition.9.004RS Flip-Flop Logic Function support New RS Flip-Flop Logic function is now supported in the Logic level columns of the Logic Editor.9.004440C-ENET plug-in supportThe EtherNet/IP plug-in provides both I/O messaging and explicit messaging. The safety relay can now be configured over EtherNet/IP using either Connected Component Workbench or an Add-on Profile (AOP) in Studio 5000 Logix Designer application.8.013Standard Signal Safety Monitoring Function support New Standard Signal Safety Monitoring Function that allows the use of standard control signals from digital plug-ins or communication ports to be used in the logic of the safety relay.8.013Project Upgrade featureProjects developed for earlier versions of firmware can be automatically converted into the latest version of firmware supported.8.0132080-MEMBAK-RTC plug-in support Project backup and restore are supported on CR30 safety relays through the 2080-MEMBAK-RTC module.7.0062080-IQ4 plug-in supportThe 2080-IQ4 digital input plug-in provides 4-pt standard rated 12/24V DC digital input expansion. It can be used in slot 1 and/or slot 2 module bays.7.0062Rockwell Automation Publication 440C-RN001H-EN-P - December 2020Guardmaster 440C-CR30 Safety Relay, Revision 11 Release NotesAnomalies2080-OB4 plug-in support The 2080-OB4 digital output plug-in provides 4-pt standard rated 12/24V DC sourcing output expansion. It can be used in slot 1 and/or slot 2 module bays.7.0062080-OW4I plug-in supportThe 2080-OW4I relay output plug-in provides 4-pt standard rated relay output, individually isolated, 2A expansion. It can be used in slot 1 and/or slot 2 module bays.7.006Unique function block name supportUnique names can be assigned to the Safety Monitoring Function blocks and the Safety Output Function blocks. These names are stored in the project that is loaded to the safety relay and can be recovered by an upload.7.006Password protection Software connections including Upload, Download,and Connect can be restricted through passwordprotection.7.006(1)For more information, see publication 440C-UM001.Table 2 - Known and Corrected AnomaliesAnomalyDescriptionAffected Firmware Revisions Corrected Firmware Revision Discrepancy Fault on Power-upDevices with pulse testing outputs would sometimes cause a discrepancy fault in the CR30 safety relay upon power-up. On power-up, the Channel Test during the first logic scan when transitioning from self-test to run mode has been removed to help prevent the discrepancy fault.See publication 440C-UM001 for details.6.0046.0067.0068.0139.00410.00410.00910.01010.011Memory Module Incompatibility Safety relay fails to recognize 2080-MEMBAK-RTC memory modules that are manufactured on or after 2016/02/11.APBC000280011 6.0046.0067.0068.0139.00410.00410.00910.010Memory Module Update When updating a safety relay from a previous firmware revision to firmware 10 using thememory module the restore operation must be performed twice (the first process updates thefirmware, the second process restores the user configuration). 6.004 6.0067.0068.0139.004Configuration loss on power cycleDuring specific power down conditions, the safety relay could be interrupted while writing a fault condition to its nonvolatile memory. On power up, the memory is evaluated as corrupted and the user configuration is discarded.APBC00026898 6.0046.0067.0068.0139.00410.00410.009Connection failure with Add-on Profile (AOP) major revision 1The safety relay rejects an I/O connection that originates from the safety relay AOP (versions 1.013 and versions 1.014) when Compatible Keying and Major Revision 8 or later is configured.APBC000271569.00410.004Download faultA download could result in a major fault on the safety relay, Type 06, Code 20 – Configuration Fault.APBC000251087.0068.0139.00410.004Download over Ethernet faultA download over Ethernet to the safety relay could result in a Type 05, Code 00 – Internal Safety Synch Fault.APBC000236608.0139.00410.004Unexpected disconnect from safety relay Occasionally Connected ComponentsWorkbench software would unexpectedly disconnect while connected to a password protected safety relay.APBC000248668.0139.004Table 1 - Enhancements (Continued)Enhancement (1)DescriptionAvailable From Firmware RevisionLocked by another connection error Attempts to connect to the safety relay arerejected and erroneously reports “CR30 has been locked by another, new connection is not allowed.”APBC000248678.0139.004No reconfiguration after EEPROM fault After the safety relay experiences a memory fault (Type 5 Code 00), the safety relay does not accept a new download.APBC00024866 6.0046.0067.0068.0139.004Muting L-Type reports incorrect fault description Under specific configuration conditions, the Muting T Type function block incorrectly reports a mute sensor timing fault when actually a sequence fault occurred.APBC000237318.0139.004Network address changes require power cycle Changes to the 440C-ENET Ethernet portsettings, duplicate IP address detection, and DHCP vs. static IP address settings may require a power cycle to take effect.APBC000241338.0139.004Power-up faultVariations in 24V DC supply power to the CR30 safety relay during power-up could lead to power fault: Type 04, Code 01.APBC000244266.0046.0067.0068.013Discrepancy fault after power-upVariations in 24V DC supply power to the CR30 safety relay during power-up could lead to adiscrepancy fault on any dual channel Safety Monitoring Function: “One channel open after reset” 6.0046.0067.0068.013Empty fault logModbus reporting of the fault log always returns 0, indicating no fault, even if faults are present in the log.APBC00025011 6.0046.0067.0068.013Incorrect Mode The safety relay will return to Run Mode after downloading a valid configuration to a unit that has experienced a nonrecoverable fault.APBC000257716.0046.0067.0068.013Modbus fault state cleared in Program Mode The safety relay does not report faultinformation over Modbus once the safety relay is placed in Program Mode.6.0046.0067.0068.013Memory module firmware update failure The memory module is unable to upgrade a firmware revision 7 safety relay to version 8 or later 7.006L-Type muting override conditionOverride for L-Type muting cannot be initiated when only the light curtain is interrupted (no mute sensors).6.0046.0067.006Two Hand Control at power up Two Hand Control does not fault at power up if buttons are pressed. 6.0046.0067.006Override conditionsFor muting applications, mute sensor interrupted or timing faults should be only conditions that allow override to be initiated.6.0046.0067.006Serial port doesnot shutdownWhen the serial port is configured as shutdown,it still responds to Modbus messages.APBC00020590 6.0046.0067.006Input filters greater than 200 ms create nonrecoverable fault When an input filter of greater than 200 ms is configured on any Safety Monitoring function, a nonrecoverable fault is generated when the configuration is downloaded to the safety relay.APBC00020589 6.0046.0067.006Missing plug-in slot 1 without fault log entry A missing plug-in module configured in slot 1 and not actually present results in a fault but no fault log entry is created.APBC00018493 6.0046.0067.006Plug-inmismatch with duplicate fault log entriesA mismatch between the plug-in present on slot 1 and the actual plug-in present results in duplicate entries in the fault log.APBC000205086.0046.0067.006Plug-in outputs fail to configure When Plug-in outputs terminals are selected asoutputs for Safety Output Functions, they fail toturn on when the corresponding Safety OutputFunction turns on.APBC000201036.004 6.006Table 2 - Known and Corrected Anomalies (Continued)AnomalyDescriptionAffected Firmware Revisions Corrected Firmware RevisionRockwell Automation Publication 440C-RN001H-EN-P - December 20203Guardmaster 440C-CR30 Safety Relay, Revision 11 Release NotesUse DMK FilesFirmware for the CR30 safety relay beginning with firmware revision 10.009 uses a new file format called *.DMK. These files are named for easy identification, for example: 440C-CR30-22BBB_10.009.dmk.ControlFLASH™ software, version 13 or later, supports the format. ControlFLASH software is automatically installed as part of Studio 5000 Logix Designer application installation, version 28 or later. You can download ControlFLASH software from the Rockwell Automation Product Compatibility and Download Center (PCDC - rok.auto/pcdc ) separately, if necessary.You are not required to install the new firmware file format. When you download *.DMK files from the Rockwell Automation PCDC, ControlFLASH softwareautomatically saves the folder location where the *.DMK files were downloaded. As a result, ControlFLASH software can easily locate *.DMK files.You can use the Browse option to access and configure the folders that ControlFLASH software monitors as shown:Upgrade Safety Relay FirmwareThis procedure shows you how to update the firmware in a CR30 safety relay using ControlFLASH. To download the latest CR30 safety relay firmware revision, go to the PCDC (PCDC - rok.auto/pcdc ) and select your desired revision.On CR30 safety relays, you can upgrade your safety relays through the Ethernet port on the 440C-ENET plug-in module and the USB.Through USB1.Verify successful RSLinx® Classic communications with you CR30 safety relay by USB using RSWho. The CR30 safety relay uses the AB_VBP-x driver.2.Start ControlFLASH (Start > All Programs > FLASH Programming Tools > ControlFlash) and click Next >.3.Select the catalog number of the CR30 safety relay (440C-CR30-22BBB) that you are updating and click Next >.4.Select the safety relay in the browse window and click OK.Communication fault without fault log entryIf the host microprocessor within the CR30safety relay loses communication with the safety processors a fault is generated but no fault log entry is createdAPBC00020302 6.0046.006Fault log index changes after power cycleAfter a power cycle of the safety relay,previously detected faults index by one within the fault log.APBC000186376.004 6.006Inverted image of downloadprogram notcompared After performing a download, the inverted datais sent back from the safety relay to Connected Components Workbench software but not compared as an additional diagnostic check.APBC00020430 6.004 6.006Download through virtual image failsDownload of a program to the safety relay occasionally fails due to connection timeout when downloading through a virtual image.6.004 6.006ATTENTION: All Ethernet settings are reverted to factory default after a ControlFLASH firmware update.Table 2 - Known and Corrected Anomalies (Continued)AnomalyDescriptionAffected Firmware Revisions Corrected Firmware Revision IMPORTANTTo update your safety relay successfully, it must be in Program Mode or BOOT Loader mode. The safety relay can be placed into Program Mode from the Graphic Overview screen in Connected Component Workbench software, the Logic Configuration tab in the Logix Designer module profile or placed in BOOT Loader mode by holding the MEM/ID button located below the USB port on the safety relay during power-up.Publication 440C-RN001H-EN-P - December 2020 | Supersedes Publication 440C-RN001G-EN-P - April 2016Copyright © 2020 Rockwell Automation, Inc. All rights reserved. Printed in the U.S.A.Rockwell Otomasyon Ticaret A.Ş. Kar Plaza İş Merkezi E Blok Kat:6 34752 İçerenköy, İstanbul, Tel: +90 (216) 5698400 EEE Yönetmeliğine UygundurAllen-Bradley, Connected Components Workbench, ControlFLASH, expanding human possibility, FactoryTalk, Guardmaster, PanelView,Rockwell Automation, RSLinx, and Studio 5000 Logix Designer are trademarks of Rockwell Automation, Inc.EtherNet/IP is a trademark of ODVA, Inc.Trademarks not belonging to Rockwell Automation are property of their respective companies.Your comments help us serve your documentation needs better. If you have any suggestions on how to improve our content, complete the form at rok.auto/docfeedback .For technical support, visit rok.auto/support.Waste Electrical and Electronic Equipment (WEEE)Rockwell Automation maintains current product environmental compliance information on its website at rok.auto/pec .At the end of life, this equipment should be collected separately from any unsorted municipal waste.5.Verify the revision, and click Next > to continue.6.Click Finish.7.Click Yes to initiate the update.The next screen shows the download progress.If you see the following error message, verify that the safety relay is in Run mode. If so, change to Program or BOOT Loader mode by pressing theMEM/ID switch during power-up of the CR30 safety relay, click OK, and try again.When the update is complete, you see a screen similar to the following.Click OK to complete the update.。

encoding.getencoding用法 -回复

encoding.getencoding用法-回复关于encoding模块中的getencoding方法的使用,不仅限于一步一步解释,而是会从基本概念开始,逐步深入探讨该方法的用法和作用。

第一部分:基本概念在编程中,数据的编码和解码是一个非常关键的问题。

当我们需要在不同的数据源之间进行传递时,比如从文件中读取文本,从网络接收数据,或是发送数据至网络等等,都需要对数据进行编码和解码的操作。

而编码方式则决定着数据的存储形式。

Python的encoding模块提供了一系列的方法和函数来处理不同的编码和解码方式。

其中之一便是getencoding方法。

第二部分:getencoding方法的基本功能getencoding方法用于获取给定文件的编码类型,它接受一个文件名作为参数,并返回对应的编码类型。

这个方法通常在读取文件时被调用,以确保正确地解码文件中的文本。

第三部分:使用getencoding方法在使用getencoding方法之前,我们需要先了解一下Python中文本编码的常见问题。

在Python中,文本是以Unicode来表示的,而不同的文件格式(如UTF-8、GBK、ASCII等)则按照不同的编码方式将Unicode转换为字节序列。

因此,在读取文件时,我们需要明确文件的编码类型,以便正确地解码文本内容。

下面是一个使用getencoding方法的示例代码:pythonimport encodingdef read_file(file_name):with open(file_name, 'r') as f:encoding_type = encoding.getencoding()content = f.read().decode(encoding_type)return contentfile_name = 'example.txt'content = read_file(file_name)print(content)在上述代码中,我们首先导入了encoding模块,然后定义了一个read_file 函数,该函数用于读取指定文件的内容。

run length encoding 填充空洞算法

run length encoding 填充空洞算法Run Length Encoding(RLE)是一种用于压缩数据的简单算法,它能够有效地减少数据的存储空间。

在RLE中,连续重复出现的字符会被替换为该字符和其连续出现的次数。

然而,RLE算法在处理包含空洞(即重复的字符之间有缺失)的数据时可能会面临一些挑战。

因此,我们可以使用“填充空洞”算法来进一步改进RLE算法,以更好地处理这种情况。

填充空洞算法的基本思想是,在进行RLE编码之前,先对数据进行预处理,将空洞处插入一个特殊字符作为标记。

然后,RLE算法可以识别这些标记,并正确地编码包含空洞的数据。

在解码过程中,我们则需要将编码后的数据还原为原始数据。

下面我们将详细介绍填充空洞算法的步骤。

步骤1:插入标记字符对于要进行RLE编码的数据,我们需要遍历整个数据,当检测到空洞时,在空洞的位置插入一个特殊字符(例如“*”),以标记该位置是一个空洞。

这样,数据中的所有空洞都会被标记出来。

步骤2:RLE编码经过了标记处理后的数据将进入RLE编码的步骤。

对于连续重复的字符,我们仍然使用RLE算法进行编码,表示为<char><count>,其中<char>是重复的字符,<count>是该字符连续重复出现的次数。

由于数据中已经插入了标记字符,RLE算法将能够正确地对包含空洞的数据进行编码。

步骤3:RLE解码在对编码后的数据进行解码时,我们需要识别和处理标记字符。

我们首先找到所有标记字符的位置,并记录下来。

然后,根据标记字符的位置将编码后的数据拆分成多个部分。

每个部分都是一个连续重复的字符和其次数,除了标记字符所在的部分,其他部分可以按照正常的RLE解码方式进行解码。

步骤4:还原空洞在解码得到连续的字符后,我们需要根据标记字符的位置,还原数据中的空洞。

根据标记字符的位置,我们可以确定空洞的范围,并将其填充为原始数据中的空洞。

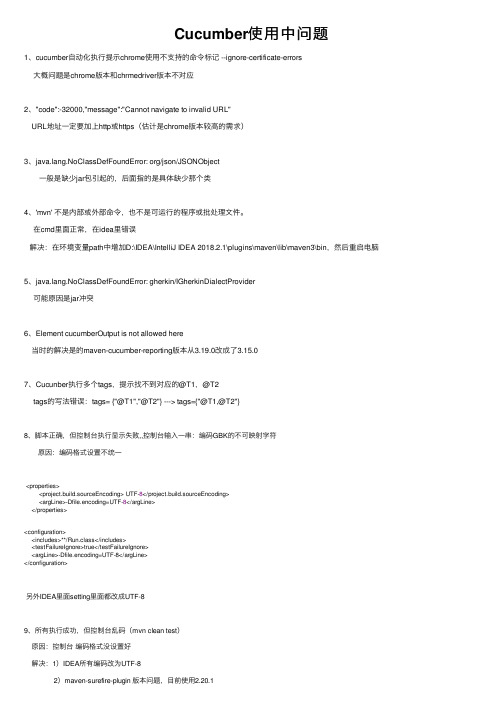

Cucumber使用中问题

Cucumber使⽤中问题1、cucumber⾃动化执⾏提⽰chrome使⽤不⽀持的命令标记 --ignore-certificate-errors⼤概问题是chrome版本和chrmedriver版本不对应2、"code":-32000,"message":"Cannot navigate to invalid URL"URL地址⼀定要加上http或https(估计是chrome版本较⾼的需求)3、ng.NoClassDefFoundError: org/json/JSONObject ⼀般是缺少jar包引起的,后⾯指的是具体缺少那个类4、'mvn' 不是内部或外部命令,也不是可运⾏的程序或批处理⽂件。

在cmd⾥⾯正常,在idea⾥错误解决:在环境变量path中增加D:\IDEA\IntelliJ IDEA 2018.2.1\plugins\maven\lib\maven3\bin,然后重启电脑5、ng.NoClassDefFoundError: gherkin/IGherkinDialectProvider可能原因是jar冲突6、Element cucumberOutput is not allowed here当时的解决是的maven-cucumber-reporting版本从3.19.0改成了3.15.07、Cucunber执⾏多个tags,提⽰找不到对应的@T1,@T2tags的写法错误:tags= {"@T1","@T2"} ---> tags={"@T1,@T2"}8、脚本正确,但控制台执⾏显⽰失败,,控制台输⼊⼀串:编码GBK的不可映射字符 原因:编码格式设置不统⼀<properties><project.build.sourceEncoding> UTF-8</project.build.sourceEncoding><argLine>-Dfile.encoding=UTF-8</argLine></properties><configuration><includes>**/Run.class</includes><testFailureIgnore>true</testFailureIgnore><argLine>-Dfile.encoding=UTF-8</argLine></configuration>另外IDEA⾥⾯setting⾥⾯都改成UTF-89、所有执⾏成功,但控制台乱码(mvn clean test)原因:控制台编码格式没设置好解决:1)IDEA所有编码改为UTF-8 2)maven-surefire-plugin 版本问题,⽬前使⽤2.20.13)Setting->maven->runner--> VMoptions: -Dfile.encoding=GB231210、定位信息获取到,但是执⾏始终不对,提⽰ element not visible解决:加上浏览器窗⼝最⼤化,有时候可能要加上等待时间。

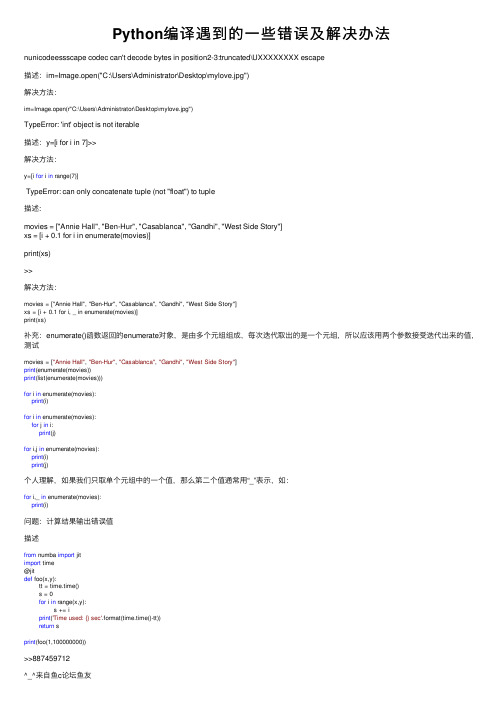

Python编译遇到的一些错误及解决办法

Python编译遇到的⼀些错误及解决办法nunicodeessscape codec can't decode bytes in position2-3:truncated\UXXXXXXXX escape描述:im=Image.open("C:\Users\Administrator\Desktop\mylove.jpg")解决⽅法:im=Image.open(r"C:\Users\Administrator\Desktop\mylove.jpg")TypeError: 'int' object is not iterable描述:y=[i for i in 7]>>解决⽅法:y=[i for i in range(7)]TypeError: can only concatenate tuple (not "float") to tuple描述:movies = ["Annie Hall", "Ben-Hur", "Casablanca", "Gandhi", "West Side Story"]xs = [i + 0.1 for i in enumerate(movies)]print(xs)>>解决⽅法:movies = ["Annie Hall", "Ben-Hur", "Casablanca", "Gandhi", "West Side Story"]xs = [i + 0.1 for i, _ in enumerate(movies)]print(xs)补充:enumerate()函数返回的enumerate对象,是由多个元组组成,每次迭代取出的是⼀个元组,所以应该⽤两个参数接受迭代出来的值,测试movies = ["Annie Hall", "Ben-Hur", "Casablanca", "Gandhi", "West Side Story"]print(enumerate(movies))print(list(enumerate(movies)))for i in enumerate(movies):print(i)for i in enumerate(movies):for j in i:print(j)for i,j in enumerate(movies):print(i)print(j)个⼈理解,如果我们只取单个元组中的⼀个值,那么第⼆个值通常⽤“_”表⽰,如:for i,_ in enumerate(movies):print(i)问题:计算结果输出错误值描述from numba import jitimport time@jitdef foo(x,y):tt = time.time()s = 0for i in range(x,y):s += iprint('Time used: {} sec'.format(time.time()-tt))return sprint(foo(1,100000000))>>887459712^_^来⾃鱼c论坛鱼友原因分析:int整型溢出⽤c代码测试如下int main(){//std::cout << sizeof(int);//std::cout << sizeof(int) * 8;int a = 4999999950000000;std::cout <<"a初始化值为4999999950000000,输出"<<a <<"\n" ;//warning C4305: “初始化”: 从“__int64”到“int”截断//a初始化值为4999999950000000,输出887459712int b = 2147483647;std::cout << "b初始化值为2147483647,即4字节int类型,能表⽰的最⼤值" << b << "\n";//2147483647std::cout << b+1 << "\n";//-2147483648std::cout << b + 2 << "\n";//最⼤值-2147483647std::cout << b + 3 << "\n";//-2147483646std::cout << b + 3 + 2147483647<< "\n";std::cout << b + 3 + 2147483647*2 << "\n";//-2147483646}总结:·int占4个字节,⽤32位表⽰,第⼀位表⽰正负号,1表⽰负数,0表⽰正,所以最⼤正数为01111111111111111111111111111111(⾸位为0,后31位为1)所以能表⽰的最⼤值就是2147483647·⼀旦超出这个值,它把第⼀位表⽰符号的设置为1(或者它⾃动进⼀位),此时,它代表⼀个负数,那么为什么是-2147483648呢,⽤⼯具转换⼀下,-2147483648值为-10000000000000000000000000000000,那它就是把第⼀位为1的时候,其他所有位为0了·每次到了存储位不够⽤的时候,它⼜循环以上的操作(正转负,负转正,第⼀位的0-1不断切换)·所以最后,⼤概可以推算出为什么4999999950000000输出的是887459712TypeError: Cannot handle this data type~这个问题有待研究,应该是matplitlib库中画图的“轴”plt或axes⽆法理解传⼊的数据~_tkinter.TclError: image "pyimage1" doesn't exist可能是你建了两个root窗⼝,可以将wlcm_scrn = ()改为wlcm_scrn = tkinter.Toplevel()。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Encoding Temporal Logics in Executable Z:A Case Study for the ZETA SystemWolfgang Grieskamp and Markus LepperTechnische Universit¨a t Berlin,FB13,Institut f¨u r Kommunikations-und Softwaretechnik, Sekr.5–13,Franklinstr.28/29,D–10587Berlin,E-mail:wg,lepper@cs.tu-berlin.de Abstract.The ZETA system is a Z-based tool environment for developing for-mal specifications.It contains a component for executing the Z language basedon the implementation technique of concurrent constraint resolution.In this pa-per,we present a case-study for the environment,by providing an executableencoding of temporal interval logics in the Z language.As an application of thissetting,test-case evaluation of trace-producing systems on the base of a formalrequirements specifications is envisaged.1IntroductionThe ZETA system[2]is a tool environment for developing formal specifications based on the Z notation[10].It contains a component for executing the Z language,using a computation model of concurrent constraint resolution,described in[5].A wide range of Z’s logic can be executed within this approach,integrating the power of higher-order functional and logic computation.In this paper,we present a case study of the system.We develop an executable en-coding of discrete temporal interval logics(in the style of Moszkowski’s logic,[8]),and illustrate it by animation in the ZETA system.The example demonstrates the interplay of logical search and of higher-orderness,the last one allowing us to build abstractions by passing predicates(generally represented as sets in Z)to functions and storing them in data values.As an application of our encoding of temporal logics we briefly look at test-case evaluation for safety-critical embedded systems.Given a formal requirements speci-fication which uses temporal logics,some input data describing a test case,and the output data from a run of the system’s implementation on the given input,we check by executing the specification whether the implementation meets its requirements.This application stems from the context of a research project funded by Daimler-Chrysler.This paper is organized as follows.In Sec.2,we introduce the basic features of executing Z in the ZETA system.In Sec.3we develop the encoding of temporal logics, and describe the application to test-case evaluation,where we use the example of an elevator controller.In Sec.4we give a conclusion,discussing the results and related work.2Executing Z under ZETAIn[4,5]a computation model based on concurrent constraint resolution has been de-veloped for Z.A high-performance virtual machine has been derived,which is im-three S S S Zadd N N Nx y N t N x S t y addA few remarks on the syntax.With a free type is introduced in Z.The declaration form n E declares and defines a(non-recursive)name simultaneously.The form x y is just an alternative notation for x y.A set-comprehension in Z,x T P E,describes the values E such that P holds for the possible assignments of x;if the is omitted(as in the definition for less,where the actually belongs to the existential quantor),the set of tuples of the assignments to the variables in the declaration part is denoted(thus x y T P x y T P x y).We may now execute under ZETA queries such as the following,where we ask for the pair of sets less and greater than three:x N x less three x N three less x({Z,S(Z),S(S(Z))},{S(S(S(S(t˜))))})The query as it is entered into the ZETA GUI is visualized in Fig.1.In the sequel, however,we will use a conceptual notation as above.As the result of the query,we get the pair of the numbers less than and greater than three,where the second value of the resulting pair is a singleton set containing the free variable t˜(the˜results from internal variable renaming).These capabilities are obviously similar to logic programming.In fact,we can give a translation from any clause-based system to a system of recursive set-equations in the style given for add,where we collect all clauses for the same relational symbol into a union of set-comprehensions,and map literals R e e n to membership tests e e n R.The functional paradigm comes into play as follows.A binary relation R can be applied,written as R e,which is syntactic sugar for the expression y X e y R.This expression is defined iff their exists a unique y such that the con-straint is satisfied;it then delivers this y.The set add is a binary relation(since it is member of the set N N N),and therefore we can for example evaluate add three three.Note the semantic difference of e y R and y R e:thefirst is not satisfied if R is not defined at e,or produces several solutions for y if R is not unique at e,whereas the second is undefined in these cases.This difference is resembled in the implementation: application,-expressions,and related forms are realized by encapsulated search.Dur-ing encapsulated search,free variables from the enclosing context are not allowed to be bound.A constraint requiring a value for such variables residuates until the context binds the variable.As a consequence,if we had defined the recursive path of add as x y z N z add x y S x y S z(instead of using x y z add), backwards computation is not be possible:x N x less threeunresolved constraints:LTX:cpinz(48.24-48.31)waiting for variable x Here,the encapsulated search for add x y,solving z N x y z add,cannot continue,since it is not allowed to produce bindings for the context variables x and y.The elegance of the functional paradigm comes from the fact that functions arefirst-class citizens.In our implementation of execution for Z,sets arefirst-class citizens as well.For example,we define a function describing relational image as follows:R X Y S X x X y Y x S x y R yA query for the relational image of the add function over the cartesian product of the numbers less then three yields in:ns x N x three less add ns ns{Z,S(Z),S(S(Z)),S(S(S(Z))),S(S(S(S(Z))))}Universal quantification is executable if it deals withfinite ranges.For example,we can define the operator denoting the set of partial functions in Z,A B,as follows:R X Y x X x R y Y x y R Universal and unique existential quantification are resolved by enumeration.Thus,if we try to check whether add is a partial function,we get in a few seconds:add N N Nstill searching after200000stepsgc#1reclaimed28674k of32770k...In enumerating the domain of add our computation diverges.However,if we restrict add to afinite domain it works:ns x N x three less ns ns add N N N*true*Above,A R restricts the domain of R to the set A;the existential quantor is used to introduce a local name in the predicate.3Encoding of Temporal Interval LogicsTemporal interval logics[8,3]is a powerful tool for describing requirements on traces of the behavior of real-time systems.For a discrete version of this logic,related to Moszkowski’s version of ITL,an embedding into Z has been described in[1].Here, we develop an executable shallow encoding for the positive subset of this kind of ITL. The encoding supports resolution for timing and observation constraints(going behind Moszkowski’s Tempura implementation),demonstrating some of the capabilities of Ex-ecutable Z in the ZETA system.3.1The EncodingWe define temporal formulas generic over a state type,such that the behaviors we look at have type(1We use the powerset-constructor which models a computable powerset ing the general power,,our free type definition of ARC would be inconsistent in Z,since a free type’s constructor cannot have a general powerset of the type in its domain.where p is the guard for this transition and w a followup formula,or the special arc eot which indicates that an interval which satisfies this formula may end at this point:TF ARC ARC eot tr SP TF xs T w is the satisfaction relation of this encoding of temporal formulas,and defined as follows:TFT]]]ws TF ws Beware that the generalized disjunction operator can be used for introducing“localvariables”,as on x T TF x.Conjunction,w w,constructs new arcs by pairwise combination of all arcs of w and w–the conjunction is recursively“pushed”through these combinations:TF TF TF]w w TFeot w wp SP w TF tr p w w tr p w ww is the repetition of w for zero or more times,w for one or more times.In the definition of in a set-comprehension, since our implementation of Z imposes a strict(eager)evaluation order.The formula holds for arbitrary singleton intervals.Temporal truthness,satisfied by any interval, is the repetition of.Temporal falsity is described by the empty set of arcs:]w TF w w]]Using the satisfaction relation t T w,we can now test whether a trace t fulfills a formula w and–provided the state predicates arefinite–also generate the set of traces which satisfy a formula.Here are some examplesT x x*false*T x x*true*t t T<1>,<2>,<1,1>,<1,2>,... In thefirst two examples above,the formula states that the interval must be partitionable into zero or more sub-interval such that in each sub-interval,from some point only numbers greater or equal two appear.This is not satisfied by thefirst trace,but by the second,choosing the right partitioning.The third example shows the generation of traces.Our encoding allows the use of free variables in state predicates.For example,we can define a formula which is satisfied by all traces which contain adjacent values. The variable can be existential quantified,or as in the example below,bound by a set comprehension to enumerate its possible bindings:x T x x1,2We will use this feature in the next section in order to introduce timing constraints. 3.2Timing ConstraintsDue to the higher-orderness of Z and our implementation,it is easily possible to add new temporal operators.Suppose that our state type contains a duration stamp describing the time distance to the next observation2,and that this stamp is selected by the function getd.We then can define a duration operator DUR getd d which holds for those intervals whose duration is d3:DUR TF2Currently,in our implementation of Z only integral numbers are supported–hence we define time as integral numbers.3Beware that we do not support an“overlapping chop”;therefore intervals which limits fall between two data samples of the given behavior are never considered.delaySTATEdur pos POS open request FLOORgetd STATE durSafety STATE f FLOOR f open pos fServe f FLOORSTATE f requestSTATE f request f posd d delay STATE f pos DUR getd dSTATE f openLiveness Serve Serve Serve Serve Serve Reqs Safety Livenessanywhere else.But as soon as it reaches thefloor,it must stop there and open the door at least after delay seconds.(The specification does not handle error situations, where the elevator does not work for some reason.)–Liveness:is simply the conjunction of all service requirements for allfloors. Such a specification can now be used for test-evaluation,feeding it with the concrete traces produced by an implementation of the controller.For example,let some test traces (parameterized over a duration stamp)be defined as follows:t d dur d pos open requestdur d pos open requestdur d pos open requestt d dur d pos open requestdur d pos open requestdur d pos open requestHere are some evaluation results:t T Reqs*true*t T Reqs*false*t T Reqs*false* In the second case,the elevator stopped at the requestedfloor but did not opened the door in time.In the third case,the elevator passed a requestedfloor without stopping.The performance of test-evaluation highly depends on the kind of specification.For the above specification we check traces of around thousand elements in approx. seconds.However,it is possible to formulate specifications which are intractable to execution since deep backtracking is required to recognize traces.These specifications involve constructs such as decision decision.4Conclusion and Related WorkWe have presented a case study of the ZETA system,a practical,working setting for developing specifications based on the Z language,which allows for executing a sub-set of Z based on concurrent constraint resolution.The example of encoding temporal interval logics showed that higher-orderness is a key feature for an environment where we can add new abstractions and notations in a convenient and consistent way:in that temporal formulas arefirst-class citizens,we could define the operators of the logic as functions over formulas.Below,we discuss some further aspects.Animating Z.Animation of the“imperative”part of Z is provided by the ZANS tool [7],imperative meaning Z’s specification style for sequential systems using state tran-sition schemas.This approach is highly restricted.An elaborated functional approach for executing Z has been described in[11],though no implementation exists today,and logic resolution is not employed.Other approaches are based on a mapping to Prolog (e.g.[12,13]),but do not support higher-orderness.The approach presented in this pa-per goes beyond all the others,since it allows the combination of the functional and logic aspects of Z in a higher-order setting.Functional and Logic Programming Languages.There is a close relationship of our setting to functional logic languages such as Curry[6]or Oz[9]:in these languages it is possible to write functions which return constraints,enabling abstractions as have been used in this paper.However,our setting provides a tighter integration and has a richer predicate language as f.i.Curry,including negation and universal quantification which are treated by encapsulated search.The role of a function as a special kind of relation as a special kind of set,and of application e e just as an abbreviation for y e y e, makes this tight integration possible.Integrating Specific Resolution Techniques.Currently,our implementation is not very ambitious regarding the basic employed resolution techniques.Central to the computa-tion model is not the basic solver technology(which is currently mere term unification) but the management of abstractions of constraints via sets.However,the integration of specialized solvers for arithmetic,interval and temporal constraints is required for our application to test-evaluation.The extension of the model to an architecture of cooper-ating basic solvers is therefore subject of future work.References1.R.B¨u ssow and binig Z and temporal interval logics for the formalizationof properties and behaviors of embedded systems.In R.K.Shyamasundar and K.Ueda, editors,Advances in Computing Science–Asian’97,volume1345of LNCS,pages46–56.Springer-Verlag,1997.2.R.B¨u ssow and W.Grieskamp.A Modular Framework for the Integration of HeterogenousNotations and Tools.In K.Araki,A.Galloway,and K.Taguchi,editors,Proc.of the1st Intl.Conference on Integrated Formal Methods–IFM’99.Springer-Verlag,London,June1999.3.Z.Chaochen,C.A.R.Hoare,and A.Ravn.A calculus of rmation ProcessingLetters,40(5),1991.4.W.Grieskamp.A Set-Based Calculus and its Implementation.PhD thesis,Technische Uni-versit¨a t Berlin,1999.5.W.Grieskamp.A Computation Model for Z based on Concurrent Constraint Resolution.Toappear in ZB2000–International Conference of Z and B Users,September2000.6.M.Hanus.Curry–an integrated functional logic language.Technical report,Internet,1999.Language report version0.5.7.X.Jia.An approach to animating Z specifications.Internet:http://saturn.cs./˜fm/zans.html,1996.8. B.Moszkowski.Executing Temporal Logic Programs.Cambridge University Press,1986.updated version from the authors home page.9.G.Smolka.Concurrent constraint programming based on functional programming.InC.Hankin,editor,Programming Languages and Systems,Lecture Notes in Computer Sci-ence,vol.1381,pages1–11,Lisbon,Portugal,1998.Springer-Verlag.10.J.M.Spivey.The Z Notation:A Reference Manual.Prentice Hall International Series inComputer Science,2nd edition,1992.11.S.Valentine.The programming language rmation and Software Technology,37(5–6):293–301,May–June1995.12.M.M.West and B.M.Eaglestone.Software development:Two approaches to animation ofZ specifications using Prolog.IEE/BCS Software Engineering Journal,7(4):264–276,July 1992.13.M.Winikoff,P.Dart,and E.Kazmierczak.Rapid prototyping using formal specifications.In Proceedings of the Australasian Computer Science Conference,1998.14.Drafts for the Z ISO standard.Ian Toyn(editor).URL:/˜ian/zstan,1999.。