STM32_MX25Lxx05D_C

STM32 LL 库使用指南说明书

STM32 LL库使用指南---By Fengzi熟悉STM32的都知道ST官方提供了非常方便好用的库函数供用户使用,多数人都使用过STM32标准外设库,STM32Cube库(即HAL库),这个LL库是什么鬼,却从来没听说过。

好吧,我承认这个名字是我自己XJB取的。

目录一、初识LL 库 (1)二、怎么使用LL库 (3)三、新建STM32LL库工程模板 (5)四、第一个程序——点亮LED (8)五、添加其他程序功能 (10)………………………………………………………………………………………………………………………………………………….一、初识LL 库最近论坛发的STM32L476RG Nucleo开发板到手了,准备学习玩耍,当然第一步就是下载资料,于是我下载STM32L4Cube 1.1.0版本,打开逐个查看,好像和以前一样的,没什么特别嘛,于是准备开始开发。

等等,好像还真发现了有点不一样:熟悉HAL库的都知道,该库的文件几乎都是以stm32xxx_hal_xxx.h/.c命名的,为了和以前的标准库有个区分,上图中那些是什么鬼前辈说,遇到问题赶紧查手册,于是我果断打开STM32L4Cube库的说明手册(UM1884):原来这个东西叫做Low Layer APIs,作为英文渣渣表示实在不习惯洋里洋气的高大上名字,于是擅自把他叫做【STM32LL库】了(不服的你咬我啊)。

从这里看好像是说这个东东比HAL库更接近硬件,到底什么鬼,还不清楚。

但是以前好像没见过这个东西啊,就算是STM32L4Cube的1.0.0版本中都没有。

看看Cube发行历史:原来LL库是在1.1.0版本才加上的,大概意思就是:1.LL APIs是寄存器级的编程,嗯,也就是说我们常说的直接操作寄存器吧。

2.LL APIs适用于xxx等一大堆外设3.LL APIs函数全部定义为static inline函数,放在对应的头文件中,用户使用需要包含相关头文件4.参考这两个文档看看LL库文件在Cube库中的位置,有20多个文件,全部以stm32l4xx_ll_xxx.h命名:STM32Cube_FW_L4_V1.1.0\Drivers\STM32L4xx_HAL_Driver\IncSTM32L4是面向低功耗市场的,同时不失高性能,功耗和性能往往是两个矛盾的东西,ST在硬件设计上想了各种办法来实现兼顾低功耗高性能(例如各种低功耗模式,LP外设等),而在软件层面,程序也讲求效率,LL库全是直接操作寄存器,直接操作寄存器往往效率较高,而且函数定义为内联函数,调用函数时不是堆栈调用,而是直接把函数的代码嵌入到调用的地方,利于提高代码相率,我想这也是ST在STM32L4系列中推出这个直接操作寄存器的LL库的原因之一吧。

STM32应用基础

STM32F101R4 36

16

4

2(8/8/8)

STM32F101R6 36

32

6

2(8/8/8)

STM32F101R8 36

64

10

3(12/12/12)

64 STM32F101RB 36

128

16

3(12/12/12)

STM32F101RC 36

256

32

4(16/16/16)

2

STM32F101RD 36

512

48

有 4(16/16/16)

2

STM32F102C4 48

16

4

2(8/8/8)

STM32F102C6 48

32

6

48

STM32F102C8 48

64

10

2(8/8/8) 3(12/12/12)

STM32F102CB 48

128

16

3(12/12/12)

STM32应用基础

STM32F101V8 36

2

3+2

1

1

STM32F103VE 3

2

3+2

1

1

STM32F103ZC 3

2

3+2

1

1

STM32F103ZD 3

2

3+2

1

1

STM32F103ZE 3

2

3+2

1

1

STM32F105R8 3

2

3+2

OTG

2

STM32F105RB 3

2

3+2

OTG

2

STM32F105RC 3

STM32学习笔记及勘误手册

/******************************************************************* 文件名:书写程序中一些特别需要留意的地方文件编辑人:张恒编辑日期:15/11/23功能:快速查阅巩固知识点*******************************************************************/ 版本说明:v1.0版本:1.开始编辑书写整个文档,开始用的为TXT文档的形式,整理了部分学习到的东西和一些在书写常用程序中容易出错的地方,以及经常忽视细节而导致程序运行失败,是巩固知识点,提醒值得注意地方的工具文档。

2.添加的功能上基本涵盖了所有的模块,除了串口通信中的SPI和I2C、I2S等,应用是比较简单后续可能会添加。

3.对一些特定的功能综合应用并未加入进去,这是一个不好的地方,后续应该会随着学习总结更新,每次更新记录为一个版本。

// 2015/11/24;v1.1版本:1.将所有的TXT版本的文档全部转换为DOC模式,并且更新的加入了目录显示,显示为1级目录,方便查阅相关内容。

2.更新了SysTick书写中值得注意的地方3.更新了FSMC的一些细微操作,后续继续追捕更新书写细节。

V1.2版本:1.更新了FSMC部分功能显示,详细了FSMC的使用注意事项2.添加了RTC实时时钟的一些注意事项。

//2015/12/1;V1.3版本:1.更新RTC部分注意事项。

//2015/12/11V1.4版本:1.更新ADC校准标志部分注意事项。

2.更新了TIM1和TIM8的高级定时器特殊功能说明。

//2015/12/13V1.5版本:1.优化了部分注意事项,SysTick的写法上重新的定制写法。

2.优化了ADC在使用过程的一些细节注意地方。

3.面对最近出现的浮点数运算错误,配合AD数据进行总结。

4.RTC细节的把握-配置正确顺序的错误。

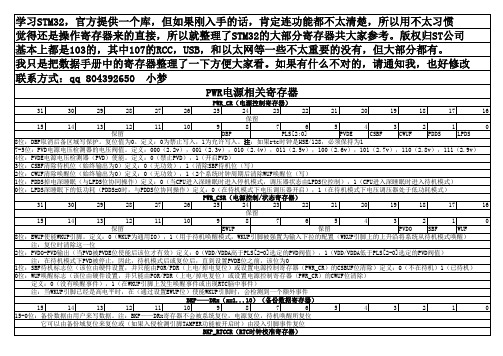

Stm32之寄存器列表

16 0

0

13 12 11 10 9 8 7 6 5 4 3 2 1 0 保留 ASOS ASOE CCO CAL[6:0] 9位:ASOS闹钟或秒输出(当设置ASOE位,ASOS位可用于选择在TAMPER引脚上输出的是RTC秒脉冲还是闹钟脉冲信号)定义:0(输出RTC闹钟脉冲),1(输出秒脉冲)注:后备 8位:ASOE允许输出闹钟或秒脉冲(根据ASOS位的置位,该位允许RTC闹钟或秒脉冲输出到TAMPER引脚。脉冲宽度为1个RTC时钟周期。置位时不能开启TAMPER功能) 7位:CCO校准时钟输出。定义:0(无影响),1(此位置1可在侵入检引脚输出经64分频后的RTC时钟。当CCO位置1时,必须关闭侵入检测)注:vdd断电,该位清除

PWR_CR(电源控制寄存器) 25 24 23 22 21 20 19 18 17 保留 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 保留 DBP PLS[2:0] PVDE CSBF CWUF PDDS LPDS 8位:DBP取消后备区域写保护。复位值为0。定义:0为禁止写入,1为允许写入。注:如果rtc时钟是HSE/128,必须保持为1 7-5位:PVD电源电压检测器的电压阀值。定义:000(2.2v),001(2.3v),010(2.4v),011(2.5v),100(2.6v),101(2.7v),110(2.8v),111(2.9v) 4位:PVDE电源电压检测器(PVD)使能。定义:0(禁止PVD),1(开启PVD) 3位:CSBF清除待机位(始终输出为0)定义:0(无功效),1(清除SBF待机位(写) 2位:CWUF清除唤醒位(始终输出为0)定义:0(无功效),1(2个系统时钟周期后清除WUF唤醒位(写) 1位:PDDS掉电深睡眠(与LPDS位协同操作)定义:0(当CPU进入深睡眠时进入停机模式,调压器状态由LPDS位控制),1(CPU进入深睡眠时进入待机模式) 0位:LPDS深睡眠下的低功耗(PDDS=0时,与PDDS位协同操作)定义:0(在待机模式下电压调压器开启),1(在待机模式下电压调压器处于低功耗模式) PWR_CSR(电源控制/状态寄存器) 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 保留 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 保留 EWUP 保留 PVDO SBF WUF 8位:EWUP使能WKUP引脚。定义:0(WKUP为通用IO),1(用于待机唤醒模式,WKUP引脚被强置为输入下拉的配置(WKUP引脚上的上升沿将系统从待机模式唤醒) 注:复位时清除这一位 2位:PVDO-PVD输出(当PVD被PVDE位使能后该位才有效)定义:0(VDD/VDDA高于PLS[2-0]选定的PVD阀值),1(VDD/VDDA低于PLS[2-0]选定的PVD阀值) 注:在待机模式下PVD被停止,因此,待机模式后或复位后,直到设置PVDE位之前,该位为0 1位:SBF待机标志位(该位由硬件设置,并只能由POR/PDR(上电/掉电复位)或设置电源控制寄存器(PWR_CR)的CSBUF位清除)定义:0(不在待机)1(已待机) 0位:WUF唤醒标志(该位由硬件设置,并只能由POR/PDR(上电/掉电复位)或设置电源控制寄存器(PWR_CR)的CWUF位清除) 定义:0(没有唤醒事件),1(在WKUP引脚上发生唤醒事件或出现RTC脑中事件) 注:当WKUP引脚已经是高电平时,在(通过设置EWUP位)使能WKUP引脚时,会检测到一个额外事件 BKP——DRx(x=1...10)(备份数据寄存器) 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 15-0位:备份数据由用户来写数据。注:BKP——DRx寄存器不会被系统复位,电源复位,待机唤醒所复位 它可以由备份域复位来复位或(如果入侵检测引脚TAMPER功能被开启时)由浸入引脚事件复位 BKP_RTCCR(RTC时钟校准寄存器) 31 30 29 28 27 26 16 0

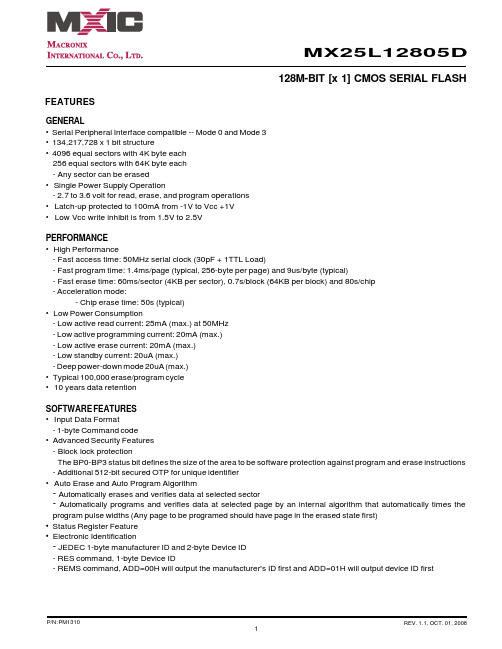

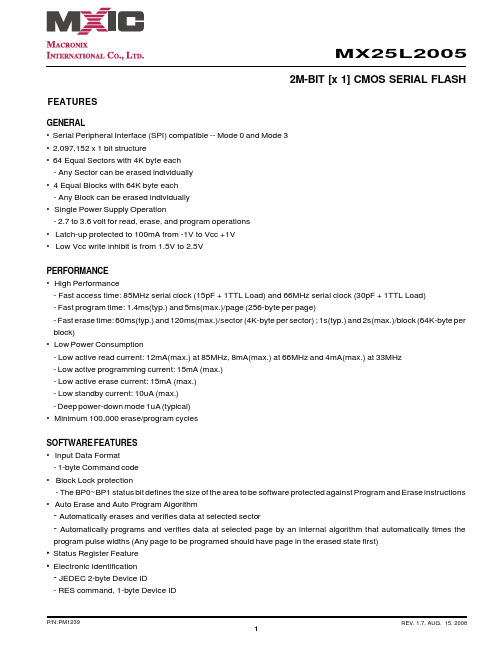

MX25L12805D中文资料

MX25L12805D128M-BIT [x 1] CMOS SERIAL FLASH FEATURESGENERAL• Serial Peripheral Interface compatible -- Mode 0 and Mode 3• 134,217,728 x 1 bit structure• 4096 equal sectors with 4K byte each256 equal sectors with 64K byte each- Any sector can be erased• Single Power Supply Operation- 2.7 to 3.6 volt for read, erase, and program operations• Latch-up protected to 100mA from -1V to Vcc +1V• Low Vcc write inhibit is from 1.5V to 2.5VPERFORMANCE• High Performance- Fast access time: 50MHz serial clock (30pF + 1TTL Load)- Fast program time: 1.4ms/page (typical, 256-byte per page) and 9us/byte (typical)- Fast erase time: 60ms/sector (4KB per sector), 0.7s/block (64KB per block) and 80s/chip- Acceleration mode:- Chip erase time: 50s (typical)• Low Power Consumption- Low active read current: 25mA (max.) at 50MHz- Low active programming current: 20mA (max.)- Low active erase current: 20mA (max.)- Low standby current: 20uA (max.)- Deep power-down mode 20uA (max.)•Typical 100,000 erase/program cycle• 10 years data retentionSOFTWARE FEATURES• Input Data Format- 1-byte Command code•Advanced Security Features- Block lock protectionThe BP0-BP3 status bit defines the size of the area to be software protection against program and erase instructions - Additional 512-bit secured OTP for unique identifier• Auto Erase and Auto Program Algorithm- Automatically erases and verifies data at selected sector- Automatically programs and verifies data at selected page by an internal algorithm that automatically times the program pulse widths (Any page to be programed should have page in the erased state first)•Status Register Feature•Electronic Identification- JEDEC 1-byte manufacturer ID and 2-byte Device ID- RES command, 1-byte Device ID- REMS command, ADD=00H will output the manufacturer's ID first and ADD=01H will output device ID firstHARDWARE FEATURES• SCLK Input- Serial clock input• SI Input- Serial Data Input•SO- Serial Data Output• WP#/ACC Pin- Hardware write protection and Program/erase acceleration• HOLD# pin- pause the chip without diselecting the chip• PACKAGE- 16-pin SOP (300mil)- All Pb-free devices are RoHS CompliantGENERAL DESCRIPTIONThe MX25L12805D is a CMOS 134,217,728 bit serial Flash Memory, which is configured as 16,777,216 x 8 internally. The MX25L12805D features a serial peripheral interface and software protocol allowing operation on a simple 3- wire bus. The three bus signals are a clock input (SCLK), a serial data input (SI), and a serial data output (SO). Serial access to the device is enabled by CS# input.The MX25L12805D provides sequential read operation on whole chip. User may start to read from any byte of the array. While the end of the array is reached, the device will wrap around to the beginning of the array and continuously outputs data until CS# goes high.After program/erase command is issued, auto program/erase algorithms which program/erase and verify the specified page locations will be executed. Program command is executed on byte basis, or page (256 bytes) basis, and erase command is executed on sector (4K-byte), or block(64K-byte), or whole chip basis.To provide user with ease of interface, a status register is included to indicate the status of the chip. The status read command can be issued to detect completion status of a program or erase operation via WIP bit.Advanced security features enhance the protection and security functions, please see security features section for more details.When the device is not in operation and CS# is high, it is put in standby mode and draws less than 20uA DC current. The MX25L12805D utilizes MXIC's proprietary memory cell which reliably stores memory contents even after 100,000 program and erase cycles.PIN CONFIGURATIONSSYMBOL DESCRIPTION CS#Chip SelectSI Serial Data Input SO Serial Data Output SCLK Clock InputHOLD#Hold, to pause the serial communication WP#/ACCWrite Protection: connect to GND;11V for program/erase acceleration:connect to 11VVCC + 3.3V Power Supply GND GroundNCNo Internal ConnectionPIN DESCRIPTION16-PIN SOP (300 mil)HOLD#VCC NC NC NC NC CS#SOSCLK SI NC NC NC NC GND WP#/ACCBLOCK DIAGRAMDATA PROTECTIONThe MX25L12805D are designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exist during power transition. During power up the device automatically resets the state machine in the Read mode. In addition, with its control register architecture, alteration of the memory contents only occurs after successful completion of specific command sequences. The device also incorporates several features to prevent inadvertent write cycles resulting from VCC power-up and power-down transition or system noise.•Power-on reset and tPUW: to avoid sudden power switch by system power supply transition, the power-on reset and tPUW (internal timer) may protect the Flash.• Valid command length checking: The command length will be checked whether it is at byte base and completed on byte boundary.• Write Enable (WREN) command: WREN command is required to set the Write Enable Latch bit (WEL) before other command to change data. The WEL bit will return to reset stage under following situation:- Power-up- Write Disable (WRDI) command completion- Write Status Register (WRSR) command completion- Page Program (PP) command completion- Sector Erase (SE) command completion- Block Erase (BE) command completion- Chip Erase (CE) command completion•Software Protection Mode (SPM): by using BP0-BP3 bits to set the part of Flash protected from data change.•Hardware Protection Mode (HPM): by using WP# going low to protect the BP0-BP3 bits and SRWD bit from data change.•Deep Power Down Mode: By entering deep power down mode, the flash device also is under protected from writing all commands except Release from deep power down mode command (RDP) and Read Electronic Signature command (RES).•Advanced Security Features: there are some protection and securuity features which protect content from inadvertent write and hostile access.I. Block lock protection- The Software Protected Mode (SPM) use (BP3, BP2, BP1, BP0) bits to allow part of memory to be protected as read only. The proected area definition is shown as table of "Protected Area Sizes", the protected areas are more flexible which may protect various area by setting value of BP0-BP3 bits.Please refer to table of "protected area sizes".- The Hardware Proteced Mode (HPM) use WP#/ACC to protect the (BP3, BP2, BP1, BP0) bits and SRWD bit.II. Additional 512-bit secured OTP for unique identifier: to provide 512-bit one-time program area for setting device unique serial number - Which may be set by factory or system customer. Please refer to table 3. 512-bit secured OTP definition.- Security register bit 0 indicates whether the chip is locked by factory or not.- To program the 512-bit secured OTP by entering 512-bit secured OTP mode (with ENSO command), and going through normal program procedure, and then exiting 512-bit secured OTP mode by writing EXSO command.- Customer may lock-down the customer lockable secured OTP by writing WRSCUR(write security register) commandto set customer lock-down bit1 as "1". Please refer to table of "security register definition" for security register bit definition and table of "512-bit secured OTP definition" for address range definition.- Note: Once lock-down whatever by factory or customer, it cannot be changed any more. While in 512-bit secured OTP mode, array access is not allowed.512-bit Secured OTP DefinitionAddress range Size Standard Customer LockFactory Lockxxxx00~xxxx0F128-bit ESN (electrical serial number)Determined by customer xxxx10~xxxx3F384-bit N/ATable 1. Protected Area SizesStatus bit Protection AreaBP3BP2BP1BP0128Mb1111All1110All1101All1100All1011All1010All1001All1000Upper half (hundrend and twenty-eight sectors: 128 to 255)0111Upper quarter (sixty-four sectors: 192 to 255)0110Upper eighth (thirty-two sectors: 224 to 255)0101Upper sixteenth (sixteen sectors: 240 to 255)0100Upper 32nd (eight sectors: 248 to 255)0011Upper 64th (four sectors: 252 to 255)0010Upper 128th (two sectors: 254 and 255)0001Upper 256th (one sector: 255)0000NoneNote:1.The device is ready to accept a Chip Erase instruction if, and only if, all Block Protect (BP3, BP2, BP1, BP0) are 0.HOLD FEATUREHOLD# pin signal goes low to hold any serial communications with the device. The HOLD feature will not stop the operation of write status register, programming, or erasing in progress.The operation of HOLD requires Chip Select(CS#) keeping low and starts on falling edge of HOLD# pin signal while Serial Clock (SCLK) signal is being low (if Serial Clock signal is not being low, HOLD operation will not start until Serial Clock signal being low). The HOLD condition ends on the rising edge of HOLD# pin signal while Serial Clock(SCLK) signal is being low( if Serial Clock signal is not being low, HOLD operation will not end until Serial Clock being low), see Figure 1. Figure 1. Hold Condition OperationThe Serial Data Output (SO) is high impedance, both Serial Data Input (SI) and Serial Clock (SCLK) are don't care during the HOLD operation. If Chip Select (CS#) drives high during HOLD operation, it will reset the internal logic of the device. To re-start communication with chip, the HOLD# must be at high and CS# must be at low.PROGRAM/ERASE ACCELERATIONTo activate the program/erase acceleration function requires ACC pin connecting to 11V voltage (see Figure 2), and then to be followed by the normal program/erase process. By utilizing the program/erase acceleration operation, the performances are improved as shown on table of "ERASE AND PROGRAM PERFORMACE".Figure 2. ACCELERATED PROGRAM TIMING DIAGRAMNote: tVHH (VHH Rise and Fall Time) min. 250nsTable 2. COMMAND DEFINITIONTable 3. Memory OrganizationBlock Sector4095FFF000h FFFFFFh …4080FF0000hFF0FFFh4079FEF000h FEFFFFh …4064FE0000h FE0FFFh 4063FDF000h FDFFFFh…4048FD0000h FD0FFFh 4047FCF000h FCFFFFh …4032FC0000h FC0FFFh 4031FBF000h FBFFFFh …4016FB0000h FB0FFFh 4015FAF000h FAFFFFh (4000)FA0000h FA0FFFh9505F000h 05FFFFh …80050000h 050FFFh 7904F000h 04FFFFh …64040000h 040FFFh 6303F000h 03FFFFh …48030000h 030FFFh 4702F000h 02FFFFh …32020000h 020FFFh 3101F000h 01FFFFh …16010000h 010FFFh 1500F000h 00FFFFh 0000000h000FFFh252251250Address Range 25525425354321Figure 3. Serial Modes SupportedNote:CPOL indicates clock polarity of Serial master, CPOL=1 for SCLK high while idle, CPOL=0 for SCLK low while not transmitting. CPHA indicates clock phase. The combination of CPOL bit and CPHA bit decides which Serial mode is supported.DEVICE OPERATION1.Before a command is issued, status register should be checked to ensure device is ready for the intended operation.2.When incorrect command is inputted to this LSI, this LSI becomes standby mode and keeps the standby mode untilnext CS# falling edge. In standby mode, SO pin of this LSI should be High-Z.3.When correct command is inputted to this LSI, this LSI becomes active mode and keeps the active mode until nextCS# rising edge.4.Input data is latched on the rising edge of Serial Clock(SCLK) and data shifts out on the falling edge of SCLK. Thedifference of Serial mode 0 and mode 3 is shown as Figure 3.5.For the following instructions: RDID, RDSR, RDSCUR, READ, FAST_READ, RES and REMS the shifted-in instructionsequence is followed by a data-out sequence. After any bit of data being shifted out, the CS# can be high. For the following instructions: WREN, WRDI, WRSR, SE, BE, CE, PP, RDP, DP, ENSO, EXSO,and WRSCUR, the CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed.6.During the progress of Write Status Register, Program, Erase operation, to access the memory array is neglected andnot affect the current operation of Write Status Register, Program, Erase.SCLK MSBCPHASI 01CPOL 0(Serial mode 0)(Serial mode 3)1SO SCLKMSBCOMMAND DESCRIPTION(1) Write Enable (WREN)The Write Enable (WREN) instruction is for setting Write Enable Latch (WEL) bit. For those instructions like PP, SE, BE, CE, and WRSR, which are intended to change the device content, should be set every time after the WREN instruction setting the WEL bit.The sequence of issuing WREN instruction is: CS# goes low-> sending WREN instruction code-> CS# goes high. (see Figure 12)(2) Write Disable (WRDI)The Write Disable (WRDI) instruction is for re-setting Write Enable Latch (WEL) bit.The sequence of issuing WRDI instruction is: CS# goes low-> sending WRDI instruction code-> CS# goes high. (see Figure 13)The WEL bit is reset by following situations:- Power-up- Write Disable (WRDI) instruction completion- Write Status Register (WRSR) instruction completion- Page Program (PP) instruction completion- Sector Erase (SE) instruction completion- Block Erase (BE) instruction completion- Chip Erase (CE) instruction completion(3) Read Identification (RDID)The RDID instruction is for reading the manufacturer ID of 1-byte and followed by Device ID of 2-byte. The MXIC Manufacturer ID is C2(hex), the memory type ID is 20(hex) as the first-byte device ID, and the individual device ID of second-byte ID is as followings: 18(hex).The sequence of issuing RDID instruction is: CS# goes low-> sending RDID instruction code -> 24-bits ID data out on SO -> to end RDID operation can use CS# to high at any time during data out. (see Figure. 14)While Program/Erase operation is in progress, it will not decode the RDID instruction, so there's no effect on the cycle of program/erase operation which is currently in progress. When CS# goes high, the device is at standby stage.(4) Read Status Register (RDSR)The RDSR instruction is for reading Status Register Bits. The Read Status Register can be read at any time (even in program/erase/write status register condition) and continuously. It is recommended to check the Write in Progress (WIP) bit before sending a new instruction when a program, erase, or write status register operation is in progress.The sequence of issuing RDSR instruction is: CS# goes low-> sending RDSR instruction code-> Status Register data out on SO (see Figure. 15)The definition of the status register bits is as below:WIP bit. The Write in Progress (WIP) bit, a volatile bit, indicates whether the device is busy in program/erase/write status register progress. When WIP bit sets to 1, which means the device is busy in program/erase/write status register progress. When WIP bit sets to 0, which means the device is not in progress of program/erase/write status register cycle.WEL bit. The Write Enable Latch (WEL) bit, a volatile bit, indicates whether the device is set to internal write enable latch. When WEL bit sets to 1, which means the internal write enable latch is set, the device can accept program/erase/write status register instruction. When WEL bit sets to 0, which means no internal write enable latch; the device will not accept program/erase/write status register instruction. The program/erase command will be ignored and not affect value of WEL bit if it is applied to a protected memory area.BP3, BP2, BP1, BP0 bits. The Block Protect (BP3, BP2, BP1, BP0) bits, non-volatile bits, indicate the protected area(as defined in table 1) of the device to against the program/erase instruction without hardware protection mode being set. To write the Block Protect (BP3, BP2, BP1, BP0) bits requires the Write Status Register (WRSR) instruction to be executed. Those bits define the protected area of the memory to against Page Program (PP), Sector Erase (SE), Block Erase (BE) and Chip Erase(CE) instructions (only if all Block Protect bits set to 0, the CE instruction can be executed).SRWD bit. The Status Register Write Disable (SRWD) bit, non-volatile bit, is operated together with Write Protection (WP#) pin for providing hardware protection mode. The hardware protection mode requires SRWD sets to 1 and WP# pin signal is low stage. In the hardware protection mode, the Write Status Register (WRSR) instruction is no longer accepted for execution and the SRWD bit and Block Protect bits (BP3, BP2, BP1, BP0) are read only.bit 7bit 6bit 5bit 4bit 3bit 2bit 1bit 0SRWD BP3BP2BP1BP0WEL WIPStatus reserved the level of the level of the level of the level of(write enable(write in progress Register Write protected protected protected protected latch)bit) Protect block block block block1= status1=write enable1=write operation register write(note 1)(note 1)(note 1)(note 1)0=not write0=not in write disable enable operationNote:1. see the table "Protected Area Sizes".(5) Write Status Register (WRSR)The WRSR instruction is for changing the values of Status Register Bits. Before sending WRSR instruction, the Write Enable (WREN) instruction must be decoded and executed to set the Write Enable Latch (WEL) bit in advance. The WRSR instruction can change the value of Block Protect (BP3, BP2, BP1, BP0) bits to define the protected area of memory (as shown in table 1). The WRSR also can set or reset the Status Register Write Disable (SRWD) bit in accordance with Write Protection (WP#) pin signal. The WRSR instruction cannot be executed once the Hardware Protected Mode (HPM) is entered.The sequence of issuing WRSR instruction is: CS# goes low-> sending WRSR instruction code-> Status Register data on SI-> CS# goes high. (see Figure 16)The WRSR instruction has no effect on b6, b1, b0 of the status register.The CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed. The self-timed Write Status Register cycle time (tW) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Write Status Register cycle is in progress. The WIP sets 1 during the tW timing,and sets 0 when Write Status Register Cycle is completed, and the Write Enable Latch (WEL) bit is reset.Table 4. Protection ModesNote:1. As defined by the values in the Block Protect (BP3, BP2, BP1, BP0) bits of the Status Register, as shown in Table 1.As the above table showing, the summary of the Software Protected Mode (SPM) and Hardware Protected Mode (HPM).Software Protected Mode (SPM):-When SRWD bit=0, no matter WP# is low or high, the WREN instruction may set the WEL bit and can change the valuesof SRWD, BP3, BP2, BP1, BP0. The protected area, which is defined by BP3, BP2, BP1, BP0, is at software protected mode (SPM).-When SRWD bit=1 and WP# is high, the WREN instruction may set the WEL bit can change the values of SRWD, BP3,BP2, BP1, BP0. The protected area, which is defined by BP3, BP2, BP1, BP0, is at software protected mode (SPM)ModeStatus register condition Software protectionmode(SPM)Status register can be written in (WEL bit is set to "1") andthe SRWD, BP0-BP3bits can be changed WP# and SRWD bit status Memory WP#=1 and SRWD bit=0, or WP#=0 and SRWD bit=0, or WP#=1 and SRWD=1The protected area cannot be program or erase.The protected area cannot be program or erase.WP#=0, SRWD bit=1The SRWD, BP0-BP3 of status register bits cannot bechanged Hardware protectionmode (HPM)Note: If SRWD bit=1 but WP# is low, it is impossible to write the Status Register even if the WEL bit has previously been set. It is rejected to write the Status Register and not be executed.Hardware Protected Mode (HPM):-When SRWD bit=1, and then WP# is low (or WP# is low before SRWD bit=1), it enters the hardware protected mode (HPM). The data of the protected area is protected by software protected mode by BP3, BP2, BP1, BP0 and hardware protected mode by the WP# to against data modification.Note: to exit the hardware protected mode requires WP# driving high once the hardware protected mode is entered. If the WP# pin is permanently connected to high, the hardware protected mode can never be entered; only can use software protected mode via BP3, BP2, BP1, BP0.(6) Read Data Bytes (READ)The read instruction is for reading data out. The address is latched on rising edge of SCLK, and data shifts out on the falling edge of SCLK at a maximum frequency fR. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single READ instruction. The address counter rolls over to 0 when the highest address has been reached.The sequence of issuing READ instruction is: CS# goes low-> sending READ instruction code-> 3-byte address on SI -> data out on SO-> to end READ operation can use CS# to high at any time during data out. (see Figure. 17)(7) Read Data Bytes at Higher Speed (FAST_READ)The FAST_READ instruction is for quickly reading data out. The address is latched on rising edge of SCLK, and data of each bit shifts out on the falling edge of SCLK at a maximum frequency fC. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single FAST_READ instruction. The address counter rolls over to 0 when the highest address has been reached.The sequence of issuing FAST_READ instruction is: CS# goes low-> sending FAST_READ instruction code-> 3-byte address on SI-> 1-dummy byte address on SI->data out on SO-> to end FAST_READ operation can use CS# to high at any time during data out. (see Figure. 18)While Program/Erase/Write Status Register cycle is in progress, FAST_READ instruction is rejected without any impact on the Program/Erase/Write Status Register current cycle.(8) Sector Erase (SE)The Sector Erase (SE) instruction is for erasing the data of the chosen sector to be "1". The instruction is used for any 4K-byte sector and 1K-byte parameter sector while parameter sectors are enable. A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Sector Erase (SE). Any address of the sector (see table 3) is a valid address for Sector Erase (SE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.Address bits [Am-A12] (Am is the most significant address) select the sector address.The sequence of issuing SE instruction is: CS# goes low -> sending SE instruction code-> 3-byte address on SI -> CS# goes high. (see Figure 20)The self-timed Sector Erase Cycle time (tSE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tSE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP3, BP2, BP1, BP0 bits, the Sector Erase (SE) instruction will not be executed on the page.(9) Block Erase (BE)The Block Erase (BE) instruction is for erasing the data of the chosen block to be "1". The instruction is used for 64K-byte sector erase operation. A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Block Erase (BE). Any address of the block (see table 3) is a valid address for Block Erase (BE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.The sequence of issuing BE instruction is: CS# goes low -> sending BE instruction code-> 3-byte address on SI -> CS# goes high. (see Figure 21)The self-timed Block Erase Cycle time (tBE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tBE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP3, BP2, BP1, BP0 bits, the Block Erase (BE) instruction will not be executed on the page.(10) Chip Erase (CE)The Chip Erase (CE) instruction is for erasing the data of the whole chip to be "1". A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Chip Erase (CE). Any address of the sector (see table 3) is a valid address for Chip Erase (CE) instruction. The CS# must go high exactly at the byte boundary( the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.The sequence of issuing CE instruction is: CS# goes low-> sending CE instruction code-> CS# goes high. (see Figure 22)The self-timed Chip Erase Cycle time (tCE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Chip Erase cycle is in progress. The WIP sets 1 during the tBE timing, and sets 0 when Chip Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the chip is protected by BP3, BP2, BP1, BP0 bits, the Chip Erase (CE) instruction will not be executed. It will be only executed when BP3, BP2, BP1, BP0 all set to "0".(11) Page Program (PP)The Page Program (PP) instruction is for programming the memory to be "0". A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Page Program (PP). If the eight least significant address bits (A7-A0) are not all 0, all transmitted data which goes beyond the end of the current page are programmed from the start address if the same page (from the address whose 8 least significant address bits (A7-A0) are all 0). The CS# must keep during the whole Page Program cycle. The CS# must go high exactly at the byte boundary( the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed. If more than 256 bytes are sent to the device, the data of the last 256-byte is programmed at the request page and previous data will be disregarded. If less than 256 bytes are sent to the device, the data is programmed at the request address of the page without effect on other address of the same page.The sequence of issuing PP instruction is: CS# goes low-> sending PP instruction code-> 3-byte address on SI-> at least1-byte on data on SI-> CS# goes high. (see Figure 19)The self-timed Page Program Cycle time (tPP) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Page Program cycle is in progress. The WIP sets 1 during the tPP timing, and sets 0 when Page Program Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP3, BP2, BP1, BP0 bits, the Page Program (PP) instruction will not be executed.(12) Deep Power-down (DP)The Deep Power-down (DP) instruction is for setting the device on the minimizing the power consumption (to entering the Deep Power-down mode), the standby current is reduced from ISB1 to ISB2). The Deep Power-down mode requires the Deep Power-down (DP) instruction to enter, during the Deep Power-down mode, the device is not active and all Write/ Program/Erase instruction are ignored. When CS# goes high, it's only in standby mode not deep power-down mode. It's different from Standby mode.The sequence of issuing DP instruction is: CS# goes low-> sending DP instruction code-> CS# goes high. (see Figure 23)Once the DP instruction is set, all instruction will be ignored except the Release from Deep Power-down mode (RDP) and Read Electronic Signature (RES) instruction. (RES instruction to allow the ID been read out). When Power-down, the deep power-down mode automatically stops, and when power-up, the device automatically is in standby mode. For RDP instruction the CS# must go high exactly at the byte boundary (the latest eighth bit of instruction code been latched-in); otherwise, the instruction will not executed. As soon as Chip Select (CS#) goes high, a delay of tDP is required before entering the Deep Power-down mode and reducing the current to ISB2.(13) Release from Deep Power-down (RDP), Read Electronic Signature (RES)The Release from Deep Power-down (RDP) instruction is terminated by driving Chip Select (CS#) High. When Chip Select (CS#) is driven High, the device is put in the Stand-by Power mode. If the device was not previously in the Deep Power-down mode, the transition to the Stand-by Power mode is immediate. If the device was previously in the Deep Power-down mode, though, the transition to the Stand-by Power mode is delayed by tRES2, and Chip Se-lect (CS#) must remain High for at least tRES2(max), as specified in Table 6. Once in the Stand-by Power mode, the device waits to be selected, so that it can receive, decode and execute instructions.RES instruction is for reading out the old style of 8-bit Electronic Signature, whose values are shown as table of ID Definitions. This is not the same as RDID instruction. It is not recommended to use for new design. For new design, please use RDID instruction. Even in Deep power-down mode, the RDP, RES, and REMS are also allowed to be executed, only except the device is in progress of program/erase/write cycle; there's no effect on the current program/erase/write cycle in progress.The sequence is shown as Figure 24,25.The RES instruction is ended by CS# goes high after the ID been read out at least once. The ID outputs repeatedly if continuously send the additional clock cycles on SCLK while CS# is at low. If the device was not previously in Deep Power-down mode, the device transition to standby mode is immediate. If the device was previously in Deep Power-down mode, there's a delay of tRES2 to transit to standby mode, and CS# must remain to high at least tRES2(max). Once in the standby mode, the device waits to be selected, so it can be receive, decode, and execute instruction.The RDP instruction is for releasing from Deep Power Down Mode.。

stm32标准库函数手册

stm32标准库函数手册STM32标准库函数是一种由ST公司推出的一套用于STM32微控制器编程的开发工具,它能够帮助开发者快速地进行芯片的开发、调试和测试。

本文将对STM32标准库函数进行详细的介绍,并提供中文手册,帮助开发者更好地掌握这个工具。

一、STM32标准库函数概述STM32标准库函数是一套由ST公司提供的软件库,包括了一系列用于STM32微控制器的常用功能函数,例如GPIO、USART、SPI、I2C等,这些函数可以用于快速实现各种应用。

同时,ST公司也提供了一些示例代码,可以方便开发者进行学习和参考。

STM32标准库函数可以与各种不同的开发环境集成,例如Keil、IAR、STM32Cube等,方便开发者进行开发。

在使用STM32标准库函数时,可以通过库函数的方式来调用硬件资源,比如设置GPIO口的状态、使用USART进行通信、配置外部中断等。

1. 系统初始化函数:这些函数包括了芯片系统时钟的初始化、中断优先级的设置、时钟输出的配置等,必须在主函数前进行调用。

2. GPIO和外部中断函数:这些函数用于对GPIO口状态的配置和读取,以及对外部中断的控制。

3. USART函数:这些函数用于对串口进行配置和读写操作。

8. DAC函数:这些函数用于对模拟量进行输出。

以下是STM32标准库函数的中文手册,包含了常用函数的介绍和使用方法。

1. 系统初始化函数1.1. RCC配置函数函数原型:void RCC_Configuration(void)函数功能:配置STM32的时钟源和时钟分频系数。

函数说明:在函数内部,首先对PLL时钟源进行配置,然后根据系统时钟的需要选择PLL时钟的分频系数,然后对AHB、APB1、APB2的分频系数进行配置。

最后,开启相应时钟使能位。

函数功能:对STM32的中断向量表进行重定位,并设置各个中断的优先级。

函数说明:中断向量表的地址是由SCB_VTOR寄存器来控制的。

MX25L3205D中文资料

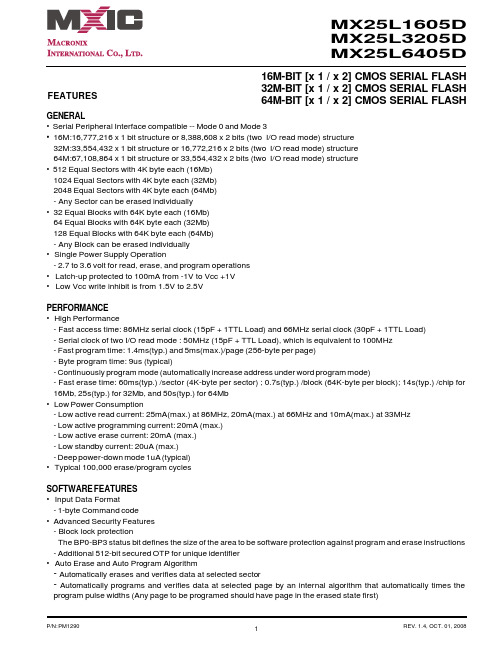

16M-BIT [x 1 / x 2] CMOS SERIAL FLASH 32M-BIT [x 1 / x 2] CMOS SERIAL FLASH 64M-BIT [x 1 / x 2] CMOS SERIAL FLASHFEATURESGENERAL• Serial Peripheral Interface compatible -- Mode 0 and Mode 3• 16M:16,777,216 x 1 bit structure or 8,388,608 x 2 bits (two I/O read mode) structure 32M:33,554,432 x 1 bit structure or 16,772,216 x 2 bits (two I/O read mode) structure 64M:67,108,864 x 1 bit structure or 33,554,432 x 2 bits (two I/O read mode) structure • 512 Equal Sectors with 4K byte each (16Mb)1024 Equal Sectors with 4K byte each (32Mb)2048 Equal Sectors with 4K byte each (64Mb)- Any Sector can be erased individually•32 Equal Blocks with 64K byte each (16Mb)64 Equal Blocks with 64K byte each (32Mb)128 Equal Blocks with 64K byte each (64Mb)- Any Block can be erased individually • Single Power Supply Operation- 2.7 to 3.6 volt for read, erase, and program operations • Latch-up protected to 100mA from -1V to Vcc +1V • Low Vcc write inhibit is from 1.5V to 2.5VPERFORMANCE • High Performance- Fast access time: 86MHz serial clock (15pF + 1TTL Load) and 66MHz serial clock (30pF + 1TTL Load)- Serial clock of two I/O read mode : 50MHz (15pF + TTL Load), which is equivalent to 100MHz - Fast program time: 1.4ms(typ.) and 5ms(max.)/page (256-byte per page)- Byte program time: 9us (typical)- Continuously program mode (automatically increase address under word program mode)- Fast erase time: 60ms(typ.) /sector (4K-byte per sector) ; 0.7s(typ.) /block (64K-byte per block); 14s(typ.) /chip for 16Mb, 25s(typ.) for 32Mb, and 50s(typ.) for 64Mb • Low Power Consumption- Low active read current: 25mA(max.) at 86MHz, 20mA(max.) at 66MHz and 10mA(max.) at 33MHz - Low active programming current: 20mA (max.)- Low active erase current: 20mA (max.)- Low standby current: 20uA (max.)- Deep power-down mode 1uA (typical)• Typical 100,000 erase/program cyclesSOFTWARE FEATURES • Input Data Format- 1-byte Command code •Advanced Security Features - Block lock protectionThe BP0-BP3 status bit defines the size of the area to be software protection against program and erase instructions - Additional 512-bit secured OTP for unique identifier • Auto Erase and Auto Program Algorithm- Automatically erases and verifies data at selected sector- Automatically programs and verifies data at selected page by an internal algorithm that automatically times the program pulse widths (Any page to be programed should have page in the erased state first)MX25L1605D MX25L3205D MX25L6405D元器件交易网•Status Register Feature•Electronic Identification- JEDEC 1-byte manufacturer ID and 2-byte device ID- RES command for 1-byte Device ID- Both REMS and REMS2 commands for 1-byte manufacturer ID and 1-byte device IDHARDWARE FEATURES• SCLK Input- Serial clock input• SI Input- Serial Data Input• SO Output- Serial Data Output• WP#/ACC pin- Hardware write protection and program/erase acceleration• HOLD# pin- pause the chip without diselecting the chip• PACKAGE- 16-pin SOP (300mil)- 8-land WSON (8x6mm or 6x5mm)- 8-pin SOP (200mil, 150mil)- 8-pin PDIP (300mil)- 8-land USON (4x4mm)- All Pb-free devices are RoHS CompliantALTERNATIVE• Security Serial Flash (MX25L1615D/MX25L3215D/MX25L6415D) may provides additional protection features for op-tion. The datasheet is provided under NDA.GENERAL DESCRIPTIONThe MX25L1605D are 16,777,216 bit serial Flash memory, which is configured as 2,097,152 x 8 internally. When it is in two I/O read mode, the structure becomes 8,388,608 bits x 2. The MX25L3205D are 33,554,432 bit serial Flash memory, which is configured as 4,194,304 x 8 internally. When it is in two I/O read mode, the structure becomes 16,772,216 bits x 2. The MX25L6405D are 67,108,864 bit serial Flash memory, which is configured as 8,388,608 x 8 internally. When it is in two I/O read mode, the structure becomes 33,554,432 bits x 2. (please refer to the "Two I/O Read mode" section). The MX25L1605D/3205D/6405D feature a serial peripheral interface and software protocol allowing operation on a simple 3-wire bus. The three bus signals are a clock input (SCLK), a serial data input (SI), and a serial data output (SO). Serial access to the device is enabled by CS# input.When it is in two I/O read mode, the SI pin and SO pin become SIO0 pin and SIO1 pin for address/dummy bits input and data output.The MX25L1605D/3205D/6405D provides sequential read operation on whole chip.After program/erase command is issued, auto program/ erase algorithms which program/ erase and verify the specified page or sector/block locations will be executed. Program command is executed on byte basis, or page (256 bytes) basis, or word basis for Continuously program mode, and erase command is executes on sector (4K-byte), or block (64K-byte), or whole chip basis.To provide user with ease of interface, a status register is included to indicate the status of the chip. The status read command can be issued to detect completion status of a program or erase operation via WIP bit.Advanced security features enhance the protection and security functions, please see security features section for more details.When the device is not in operation and CS# is high, it is put in standby mode and draws less than 20uA DC current. The MX25L1605D/3205D/6405D utilizes MXIC's proprietary memory cell, which reliably stores memory contents even after typical 100,000 program and erase cycles.Table 1. Additional Feature ComparisonPIN CONFIGURATIONSSYMBOL DESCRIPTION CS#Chip SelectSI/SIO0Serial Data Input (for 1 x I/O)/ Serial Data Input & Output (for 2xI/O read mode)SO/SIO1Serial Data Output (for 1 x I/O)/ Serial Data Input & Output (for 2xI/O read mode)SCLK Clock InputWP#/ACCWrite protection: connect to GND ;9.5~10.5V for program/eraseacceleration: connect to 9.5~10.5V HOLD#Hold, to pause the device without deselecting the device VCC + 3.3V Power Supply GNDGroundPIN DESCRIPTION16-PIN SOP (300mil)8-LAND WSON (8x6mm, 6x5mm), USON (4x4mm)8-PIN SOP (200mil, 150mil)PACKAGE OPTIONS16M 32M 64M150mil 8-SOP V 200mil 8-SOP V V 300mil 16-SOP V V V300mil 8-PDIP V V 6x5mm WSON V V 8x6mm WSON V4x4mm USONVV12345678HOLD#VCC NC NC NC NC CS#SO/SIO1161514131211109SCLK SI/SIO0NC NC NC NC GND WP#/ACCCS#SO/SIO1WP#/ACCGND VCC HOLD#SCLK SI/SIO0CS#SO/SIO1WP#/ACC GND VCC HOLD#SCLK SI/SIO01234CS#SO/SIO1WP#/ACC GND 8765VCC HOLD#SCLK SI/SIO08-PIN PDIP (300mil)BLOCK DIAGRAMDATA PROTECTIONThe MX25L1605D/3205D/6405D is designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exist during power transition. During power up the device automatically resets the state machine in the Read mode. In addition, with its control register architecture, alteration of the memory contents only occurs after successful completion of specific command sequences. The device also incorporates several features to prevent inadvertent write cycles resulting from VCC power-up and power-down transition or system noise.•Power-on reset and tPUW: to avoid sudden power switch by system power supply transition, the power-on reset and tPUW (internal timer) may protect the Flash.• Valid command length checking: The command length will be checked whether it is at byte base and completed on byte boundary.• Write Enable (WREN) command: WREN command is required to set the Write Enable Latch bit (WEL) before other command to change data. The WEL bit will return to reset stage under following situation:- Power-up- Write Disable (WRDI) command completion- Write Status Register (WRSR) command completion- Page Program (PP) command completion- Continuously Program mode (CP) instruction completion- Sector Erase (SE) command completion- Block Erase (BE) command completion- Chip Erase (CE) command completion- Write Read-lock Bit (WRLB) instruction completion•Deep Power Down Mode: By entering deep power down mode, the flash device also is under protected from writing all commands except Release from deep power down mode command (RDP) and Read Electronic Signature command (RES).•Advanced Security Features: there are some protection and securuity features which protect content from inadvertent write and hostile access.I. Block lock protection- The Software Protected Mode (SPM) use (BP3, BP2, BP1, BP0) bits to allow part of memory to be protected as read only. The proected area definition is shown as table of "Protected Area Sizes", the protected areas are more flexible which may protect various area by setting value of BP0-BP3 bits.Please refer to table of "protected area sizes".- The Hardware Proteced Mode (HPM) use WP#/ACC to protect the (BP3, BP2, BP1, BP0) bits and SRWD bit.Table 2. Protected Area SizesII. Additional 512-bit secured OTP for unique identifier: to provide 512-bit one-time program area for setting device unique serial number - Which may be set by factory or system customer. Please refer to table 3. 512-bit secured OTP definition.- Security register bit 0 indicates whether the chip is locked by factory or not.- To program the 512-bit secured OTP by entering 512-bit secured OTP mode (with ENSO command), and going through normal program procedure, and then exiting 512-bit secured OTP mode by writing EXSO command.- Customer may lock-down the customer lockable secured OTP by writing WRSCUR(write security register) command to set customer lock-down bit1 as "1". Please refer to table of "security register definition" for security register bit definition and table of "512-bit secured OTP definition" for address range definition.- Note: Once lock-down whatever by factory or customer, it cannot be changed any more. While in 512-bit secured OTP mode, array access is not allowed.Table 3. 512-bit Secured OTP DefinitionAddress range Size Standard Customer LockFactory Lockxxxx00~xxxx0F128-bit ESN (electrical serial number)Determined by customer xxxx10~xxxx3F384-bit N/AHOLD FEATURESHOLD# pin signal goes low to hold any serial communications with the device. The HOLD feature will not stop the operation of write status register, programming, or erasing in progress.The operation of HOLD requires Chip Select(CS#) keeping low and starts on falling edge of HOLD# pin signal while Serial Clock (SCLK) signal is being low (if Serial Clock signal is not being low, HOLD operation will not start until Serial Clock signal being low). The HOLD condition ends on the rising edge of HOLD# pin signal while Serial Clock(SCLK) signal is being low( if Serial Clock signal is not being low, HOLD operation will not end until Serial Clock being low), see Figure 1. Figure 1. Hold Condition OperationThe Serial Data Output (SO) is high impedance, both Serial Data Input (SI) and Serial Clock (SCLK) are don't care during the HOLD operation. If Chip Select (CS#) drives high during HOLD operation, it will reset the internal logic of the device. To re-start communication with chip, the HOLD# must be at high and CS# must be at low.PROGRAM/ERASE ACCELERATIONTo activate the program/erase acceleration function requires ACC pin connecting to 9.5~10.5V voltage (see Figure 2), and then to be followed by the normal program/erase process. By utilizing the program/erase acceleration operation, the performances are improved as shown on table of "ERASE AND PROGRAM PERFORMACE".After power-up ready, it should wait 10ms at least to apply VHH(9.5~10.5V) on the WP#/ACC pin.Figure 2. ACCELERATED PROGRAM TIMING DIAGRAMNote: tVHH (VHH Rise and Fall Time) min. 250nsTable 4. COMMAND DEFINITIONCOMMAND (byte)WREN (writeenable)WRDI (write disable)RDID (read identification )RDSR (read statusregister)WRSR(write status register)READ (read data)FAST READ(fast read data)2READ (2x I/O read command)note1SE (sector erase)1st byte 06 (hex)04 (hex)9F (hex)05 (hex)01 (hex)03 (hex)0B (hex)BB (hex)20 (hex)2nd byte AD1AD1ADD(2)AD13rd byte AD2AD2ADD(2) &Dummy(2)AD24th byte AD3AD3AD35th byte Actionsets the (WEL)write enable latch bit resets the (WEL)write enable latch bitoutputs JEDEC ID:1-byte manufactur er ID & 2-byte device IDto read out the values of the status register to writenew values to the statusregister n bytes read out until CS#goes high n bytes read out until CS#goes high n bytes read out by 2 x I/O until CS#goes high to erase the selectedsector Note 1: The count base is 4-bit for ADD(2) and Dummy(2) because of 2 x I/O. And the MSB is on SI/SIO0 which is different from 1 x I/O conditionCOMMAND (byte)BE (block erase)CE (chip erase)PP (Page program)CP (Continuo-usly program mode)DP (Deep powerdown)RDP (Release from deep power down)RES (read electronic ID)REMS(read electronic manufactu-rer &device ID)REMS2(read ID for 2x I/O mode)1st byte D8 (hex)60 or C7(hex)02 (hex)AD (hex)B9 (hex)AB (hex)AB (hex)90 (hex)EF (hex)2nd byte AD1AD1AD1x x x 3rd byte AD2AD2AD2x x x 4th byte AD3AD3AD3x ADD(note 2)ADD(note2)5th byteAction to erase theselected block to erase whole chip to program the selected page continously program wholechip, theaddress is automatica lly increaseentersdeep power down moderelease from deep power down mode to read out 1-byte device ID outout the manufactu-rer ID &device ID output the manufactu-rer ID &device ID Note 2: ADD=00H will output the manufacturer ID first and ADD=01H will output device ID first Note 3: It is not recommoded to adopt any other code not in the command definition table, which will potentially enter the hidden mode.COMMAND (byte)ENSO (enter secured OTP)EXSO (exit secured OTP)RDSCUR (read security register)WRSCUR (write security register)ESRY (enable SO to output RY/BY#)DSRY (disable SO to output RY/BY#)1st byte B1 (hex)C1 (hex)2B (hex)2F (hex)70 (hex)80 (hex)2nd byte 3rd byte 4th byte 5th byte Actionto enter the 512-bit secured OTP mode to exit the 512-bit secured OTP mode to read value of security registerto set the lock-down bit as "1"(once lock-down,cannot be updated)to enable SO to output RY/BY#during CP mode to disable SO to output RY/BY#during CP modeDummyTable 5-1. Memory Organization (16Mb)Table 5-2. Memory Organization (32Mb)Table 5-3. Memory Organization (64Mb)DEVICE OPERATION1.Before a command is issued, status register should be checked to ensure device is ready for the intended operation.2.When incorrect command is inputted to this LSI, this LSI becomes standby mode and keeps the standby mode until next CS# falling edge. In standby mode, SO pin of this LSI should be High-Z.3.When correct command is inputted to this LSI, this LSI becomes active mode and keeps the active mode until next CS# rising edge.4.Input data is latched on the rising edge of Serial Clock(SCLK) and data shifts out on the falling edge of SCLK. The difference of Serial mode 0 and mode 3 is shown as Figure 3.Figure 3. Serial Modes Supported5.For the following instructions: RDID, RDSR, RDSCUR, READ, FAST_READ, 2READ, RES, REMS and REMS2 the shifted-in instruction sequence is followed by a data-out sequence. After any bit of data being shifted out, the CS# can be high. For the following instructions: WREN, WRDI, WRSR, SE, BE, CE, PP, CP, RDP, DP, ENSO, EXSO,and WRSCUR, the CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed.6.During the progress of Write Status Register, Program, Erase operation, to access the memory array is neglected and not affect the current operation of Write Status Register, Program, Erase.Note:CPOL indicates clock polarity of Serial master, CPOL=1 for SCLK high while idle, CPOL=0 for SCLK low while not transmitting. CPHA indicates clock phase. The combination of CPOL bit and CPHA bit decides which Serial mode is supported.SCLKMSBCPHASI 01CPOL 0(Serial mode 0)(Serial mode 3)1SO SCLKMSBCOMMAND DESCRIPTION(1) Write Enable (WREN)The Write Enable (WREN) instruction is for setting Write Enable Latch (WEL) bit. For those instructions like PP, CP, SE, BE, CE, and WRSR, which are intended to change the device content, should be set every time after the WREN instruction setting the WEL bit.The sequence of issuing WREN instruction is: CS# goes low-> sending WREN instruction code-> CS# goes high. (see Figure 12)(2) Write Disable (WRDI)The Write Disable (WRDI) instruction is for resetting Write Enable Latch (WEL) bit.The sequence of issuing WRDI instruction is: CS# goes low-> sending WRDI instruction code-> CS# goes high. (see Figure 13)The WEL bit is reset by following situations:- Power-up- Write Disable (WRDI) instruction completion- Write Status Register (WRSR) instruction completion- Page Program (PP) instruction completion- Sector Erase (SE) instruction completion- Block Erase (BE) instruction completion- Chip Erase (CE) instruction completion- Continuously program mode (CP) instruction completion(3) Read Identification (RDID)The RDID instruction is for reading the manufacturer ID of 1-byte and followed by Device ID of 2-byte. The MXIC Manufacturer ID is C2(hex), the memory type ID is 20(hex) as the first-byte device ID, and the individual device ID of second-byte ID are listed as table of "ID Definitions".The sequence of issuing RDID instruction is: CS# goes low-> sending RDID instruction code -> 24-bits ID data out on SO -> to end RDID operation can use CS# to high at any time during data out. (see Figure. 14)While Program/Erase operation is in progress, it will not decode the RDID instruction, so there's no effect on the cycle of program/erase operation which is currently in progress. When CS# goes high, the device is at standby stage.(4) Read Status Register (RDSR)The RDSR instruction is for reading Status Register Bits. The Read Status Register can be read at any time (even in program/erase/write status register condition) and continuously. It is recommended to check the Write in Progress (WIP) bit before sending a new instruction when a program, erase, or write status register operation is in progress.The sequence of issuing RDSR instruction is: CS# goes low-> sending RDSR instruction code-> Status Register data out on SO (see Figure. 15)The definition of the status register bits is as below:WIP bit. The Write in Progress (WIP) bit, a volatile bit, indicates whether the device is busy in program/erase/write status register progress. When WIP bit sets to 1, which means the device is busy in program/erase/write status register progress. When WIP bit sets to 0, which means the device is not in progress of program/erase/write status register cycle.WEL bit. The Write Enable Latch (WEL) bit, a volatile bit, indicates whether the device is set to internal write enable latch. When WEL bit sets to 1, which means the internal write enable latch is set, the device can accept program/erase/write status register instruction. When WEL bit sets to 0, which means no internal write enable latch; the device will not accept program/erase/write status register instruction. The program/erase command will be ignored and not affect value of WEL bit if it is applied to a protected memory area.BP3, BP2, BP1, BP0 bits. The Block Protect (BP3, BP2, BP1, BP0) bits, non-volatile bits, indicate the protected area(as defined in table 1) of the device to against the program/erase instruction without hardware protection mode being set. To write the Block Protect (BP3, BP2, BP1, BP0) bits requires the Write Status Register (WRSR) instruction to be executed. Those bits define the protected area of the memory to against Page Program (PP), Sector Erase (SE), Block Erase (BE) and Chip Erase(CE) instructions (only if all Block Protect bits set to 0, the CE instruction can be executed).Continuously Program Mode( CP mode) bit. The Continuously Program Mode bit indicates the status of CP mode, "0" indicates not in CP mode; "1" indicates in CP mode.SRWD bit. The Status Register Write Disable (SRWD) bit, non-volatile bit, is operated together with Write Protection (WP#/ ACC) pin for providing hardware protection mode. The hardware protection mode requires SRWD sets to 1 and WP#/ACC pin signal is low stage. In the hardware protection mode, the Write Status Register (WRSR) instruction is no longer accepted for execution and the SRWD bit and Block Protect bits (BP3, BP2, BP1, BP0) are read only.Status Registernote1: see the table "Protected Area Sizes"(5) Write Status Register (WRSR)The WRSR instruction is for changing the values of Status Register Bits. Before sending WRSR instruction, the Write Enable (WREN) instruction must be decoded and executed to set the Write Enable Latch (WEL) bit in advance. The WRSR instruction can change the value of Block Protect (BP3, BP2, BP1, BP0) bits to define the protected area of memory (as shown in table 1). The WRSR also can set or reset the Status Register Write Disable (SRWD) bit in accordance with Write Protection (WP#/ACC) pin signal. The WRSR instruction cannot be executed once the Hardware Protected Mode (HPM)is entered.The sequence of issuing WRSR instruction is: CS# goes low-> sending WRSR instruction code-> Status Register data on SI-> CS# goes high. (see Figure 16)The WRSR instruction has no effect on b6, b1, b0 of the status register.The CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed. The self-timed Write Status Register cycle time (tW) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Write Status Register cycle is in progress. The WIP sets 1 during the tW timing,and sets 0 when Write Status Register Cycle is completed, and the Write Enable Latch (WEL) bit is reset.Table 6. Protection ModesNote:1. As defined by the values in the Block Protect (BP3, BP2, BP1, BP0) bits of the Status Register, as shown in Table 1.As the above table showing, the summary of the Software Protected Mode (SPM) and Hardware Protected Mode (HPM).Software Protected Mode (SPM):-When SRWD bit=0, no matter WP#/ACC is low or high, the WREN instruction may set the WEL bit and can changethe values of SRWD, BP3, BP2, BP1, BP0. The protected area, which is defined by BP3, BP2, BP1, BP0, is at software protected mode (SPM).-When SRWD bit=1 and WP#/ACC is high, the WREN instruction may set the WEL bit can change the values of SRWD,BP3, BP2, BP1, BP0. The protected area, which is defined by BP3, BP2, BP1, BP0, is at software protected mode (SPM)ModeStatus register condition Software protection mode(SPM)Status register can be written in (WEL bit is set to "1") and the SRWD, BP0-BP3bits can be changedWP# and SRWD bit status MemoryWP#=1 and SRWD bit=0, or WP#=0 and SRWD bit=0, or WP#=1 and SRWD=1The protected area cannot be program or erase.The protected area cannot be program or erase.WP#=0, SRWD bit=1The SRWD, BP0-BP3 ofstatus register bits cannot be changedHardware protection mode (HPM)Note: If SRWD bit=1 but WP#/ACC is low, it is impossible to write the Status Register even if the WEL bit has previously been set. It is rejected to write the Status Register and not be executed.Hardware Protected Mode (HPM):-When SRWD bit=1, and then WP#/ACC is low (or WP#/ACC is low before SRWD bit=1), it enters the hardware protected mode (HPM). The data of the protected area is protected by software protected mode by BP3, BP2, BP1, BP0 and hardware protected mode by the WP#/ACC to against data modification.Note: to exit the hardware protected mode requires WP#/ACC driving high once the hardware protected mode is entered. If the WP#/ACC pin is permanently connected to high, the hardware protected mode can never be entered; only can use software protected mode via BP3, BP2, BP1, BP0.(6) Read Data Bytes (READ)The read instruction is for reading data out. The address is latched on rising edge of SCLK, and data shifts out on the falling edge of SCLK at a maximum frequency fR. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single READ instruction. The address counter rolls over to 0 when the highest address has been reached.The sequence of issuing READ instruction is: CS# goes low-> sending READ instruction code-> 3-byte address on SI -> data out on SO-> to end READ operation can use CS# to high at any time during data out. (see Figure. 17)(7) Read Data Bytes at Higher Speed (FAST_READ)The FAST_READ instruction is for quickly reading data out. The address is latched on rising edge of SCLK, and data of each bit shifts out on the falling edge of SCLK at a maximum frequency fC. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single FAST_READ instruction. The address counter rolls over to 0 when the highest address has been reached.The sequence of issuing FAST_READ instruction is: CS# goes low-> sending FAST_READ instruction code-> 3-byte address on SI-> 1-dummy byte address on SI->data out on SO-> to end FAST_READ operation can use CS# to high at any time during data out. (see Figure. 18)While Program/Erase/Write Status Register cycle is in progress, FAST_READ instruction is rejected without any impact on the Program/Erase/Write Status Register current cycle.(8) 2 x I/O Read Mode (2READ)The 2READ instruction enable double throughput of Serial Flash in read mode. The address is latched on rising edge of SCLK, and data of every two bits(interleave on 2 I/O pins) shift out on the falling edge of SCLK at a maximum frequency fT. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single 2READ instruction. The address counter rolls over to 0 when the highest address has been reached. Once writing 2READ instruction, the following address/dummy/ data out will perform as 2-bit instead of previous 1-bit.The sequence of issuing 2READ instruction is: CS# goes low→ sending 2READ instruction→ 24-bit address interleave on SIO1 & SIO0→ 8-bit dummy interleave on SIO1 & SIO0→ data out interleave on SIO1 & SIO0→ to end 2READ operation can use CS# to high at any time during data out (see Figure of 2 x I/O Read Mode Timing Waveform)While Program/Erase/Write Status Register cycle is in progress, 2READ instruction is rejected without any impact on the Program/Erase/Write Status Register current cycle.The 2 I/O only perform read operation. Program/Erase /Read ID/Read status/Read ID....operation do not support 2 I/O throughputs.(9) Sector Erase (SE)The Sector Erase (SE) instruction is for erasing the data of the chosen sector to be "1". The instruction is used for any 4K-byte sector. A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Sector Erase (SE). Any address of the sector (see table 3) is a valid address for Sector Erase (SE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.Address bits [Am-A12] (Am is the most significant address) select the sector address.The sequence of issuing SE instruction is: CS# goes low -> sending SE instruction code-> 3-byte address on SI -> CS# goes high. (see Figure 22)The self-timed Sector Erase Cycle time (tSE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tSE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP3, BP2, BP1, BP0 bits, the Sector Erase (SE) instruction will not be executed on the page.(10) Block Erase (BE)The Block Erase (BE) instruction is for erasing the data of the chosen block to be "1". The instruction is used for 64K-byte sector erase operation. A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Block Erase (BE). Any address of the block (see table 3) is a valid address for Block Erase (BE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.The sequence of issuing BE instruction is: CS# goes low -> sending BE instruction code-> 3-byte address on SI -> CS# goes high. (see Figure 23)The self-timed Block Erase Cycle time (tBE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tBE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP3, BP2, BP1, BP0 bits, the Block Erase (BE) instruction will not be executed on the page.(11) Chip Erase (CE)The Chip Erase (CE) instruction is for erasing the data of the whole chip to be "1". A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Chip Erase (CE). Any address of the sector (see table 3) is a valid address for Chip Erase (CE) instruction. The CS# must go high exactly at the byte boundary( the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.The sequence of issuing CE instruction is: CS# goes low-> sending CE instruction code-> CS# goes high. (see Figure 24)。

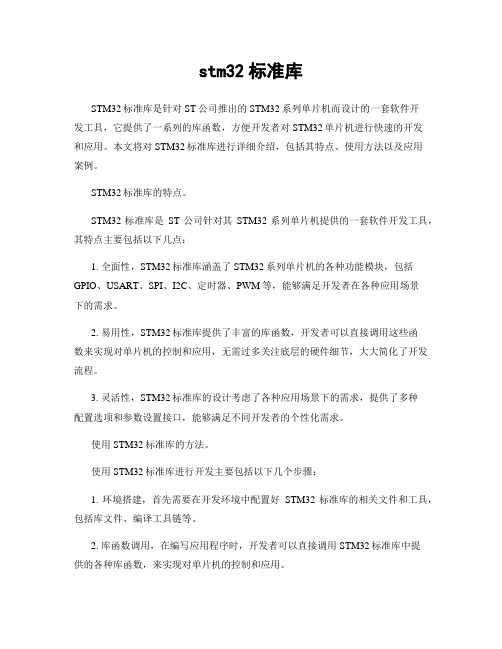

stm32标准库

stm32标准库STM32标准库是针对ST公司推出的STM32系列单片机而设计的一套软件开发工具,它提供了一系列的库函数,方便开发者对STM32单片机进行快速的开发和应用。

本文将对STM32标准库进行详细介绍,包括其特点、使用方法以及应用案例。

STM32标准库的特点。

STM32标准库是ST公司针对其STM32系列单片机提供的一套软件开发工具,其特点主要包括以下几点:1. 全面性,STM32标准库涵盖了STM32系列单片机的各种功能模块,包括GPIO、USART、SPI、I2C、定时器、PWM等,能够满足开发者在各种应用场景下的需求。

2. 易用性,STM32标准库提供了丰富的库函数,开发者可以直接调用这些函数来实现对单片机的控制和应用,无需过多关注底层的硬件细节,大大简化了开发流程。

3. 灵活性,STM32标准库的设计考虑了各种应用场景下的需求,提供了多种配置选项和参数设置接口,能够满足不同开发者的个性化需求。

使用STM32标准库的方法。

使用STM32标准库进行开发主要包括以下几个步骤:1. 环境搭建,首先需要在开发环境中配置好STM32标准库的相关文件和工具,包括库文件、编译工具链等。

2. 库函数调用,在编写应用程序时,开发者可以直接调用STM32标准库中提供的各种库函数,来实现对单片机的控制和应用。

3. 参数配置,在调用库函数时,开发者可以根据具体的应用需求进行参数的配置和设置,以实现个性化的功能实现。

4. 编译下载,在完成应用程序的编写后,需要将程序编译生成可执行文件,并下载到目标单片机中进行调试和运行。

STM32标准库的应用案例。

STM32标准库广泛应用于各种领域的嵌入式系统开发中,例如工业控制、智能家居、汽车电子、医疗设备等。

下面以一个简单的LED闪烁程序为例,介绍STM32标准库的应用方法:```c。

#include "stm32f10x.h"void Delay(__IO uint32_t nCount) {。

微机原理STM32实验指导书

微机原理与接口技术STM32实验指导书V2.0龙岩学院物理与机电工程学院电子工程系2016.3实验一GPIO 模块实验一、实验目的1、学习S TM32 模块的G PIO 模块的配置2、学习S TM32 模块的输入输出功能的实验二、实验原理1 、S TM32 的 IO 口相比 51 而言要复杂得多,所以使用起来也困难很多。

首先S TM32 的IO 口可以由软件配置成如下8种模式:输入浮空、输入上拉、输入下拉、模拟输入、开漏输出、推挽输出、推挽式复用功能、开漏复用功能。

STM32 的每个 IO 端口都有 7 个寄存器来控制。

他们分别是:配置模式的 2 个 32 位的端口配置寄存器C RL 和C RH;2 个32 位的数据寄存器I DR 和O DR;1 个32 位的置位/复位寄存器 BSRR;一个16 位的复位寄存器B RR;1个32 位的锁存寄存器L CKR。

刚复位后,复用功能未开启,I/O 端口被配置成浮空输入模式STM32 的CRL 控制着每组 IO 端口(A~G )的低8 位的模式。

每个 IO 端口的位占用C RL 的4个位,高两位为C NF,低两位为M ODE。

这里我们可以记住几个常用的配置,比如0X0 表示模拟输入模式(ADC 用)、0X3 表示推挽输出模式(做输出口用,50M 速率)、 0X8 表示上/下拉输入模式(做输入口用)、0XB 表示复用输出(使用I O 口的第二功能,50M 速率)。

CRH 的作用和C RL 完全一样在固件库开发中,操作寄存器C RH 和C RL 来配置I O 口的模式和速度是通过G PIO 初始化函数完成:void GPIO_Init(GPIO_TypeDef* GPIOx, GPIO_InitTypeDef* GPIO_InitStruct);第一个参数是用来指定G PIO,取值范围为G PIOA~GPIOG。

第二个参数为初始化参数结构体指针,结构体类型为G PIO_InitTypeDef。

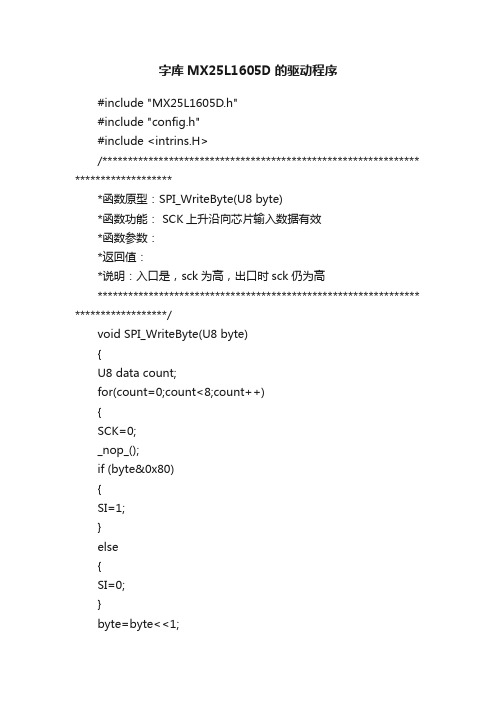

关于MX25L系列8脚存储器的读写方法

关于MX25L系列8脚存储器的读写方法

MX25L系列8脚存储器,是Macronix旺宏半导体公司生产的SPI总线FLASH,广泛应用于液晶显示器和液晶电视驱动板、电脑主板、DVD、卫星接收机等电子产品,用于存储MCU固件程序或产品数据,常用型号有MX25L1005,MX25L4005,MX25L8005等,容量分别为1M bit、4Mbit、8Mbit,对应文件大小为128KB、512KB、1MB,此芯片如果拆下来用通用编程器读写,往往会出现以下问题:能读取、能擦除、查空正常,校验时出错,我们用MX25L1005和MX25L4005的同一芯片,在多款通用编程器上进行了测试,结果如下:

校验出错的型号:北京鑫润飞的RF1800,欧洲ELNEC的SEEPRO及国内仿制产品;

正常读写的型号:南京西尔特的SP3000U,天津威磊的VP480;

RT806编程器用来读写MX系列25芯片,不要选择菜单里的MXIC子菜单下面的型号,只要选择Winbond相应容量的型号,即可正常读写。

例如读写MX25L1005的芯片,选择Winbond的W25X10,即可正常识别芯片、读取、擦除和写入;同理,MX25L4005的芯片选择W25X40,MX25L8005的芯片选择W25X80。

依次类推,如果遇到编程器菜单里没有相同型号的25芯片,可以从Winbond菜单下选取容量相同的型号再读写。

嵌入式单片机STM32应用技术(课本)

嵌⼊式单⽚机STM32应⽤技术(课本)⽬录SAIU R20 1 6 第1页第1 章. 初识STM32 (1)1.1. 课前预习 (1)1.2. 概述 (1)1.3. 什么是STM32 (1)1.4. STM32 能做什么 (2)1.5. STM32 怎么选型 (3)1.5.1. STM32 分类 (3)1.5.2. STM32 命名⽅法 (4)1.5.3. 选择合适的MCU (4)1.5.4. PCB 哪⾥打样 (6)1.6. 总结 (7)1.7. 课后练习 (7)第2 章. STM32 的结构和组成 (8)2.1. 课前预习 (8)2.2. 概述 (8)2.3. 什么是寄存器 (8)2.4. STM 32 长啥样 (8)2.5. 芯⽚⾥⾯有什么 (10)2.5.1. ICode 总线 (10)2.5.2. 驱动单元 (10)2.5.3. 被动单元 (11)2.6. 存储器映射 (13)2.7. 寄存器映射 (14)2.7.1. STM32 的外设地址映射 (15)2.7.2. 总线基地址 (15)2.7.3. 外设基地址 (15)2.7.4. 外设寄存器 (16)2.8. C 语⾔对寄存器的封装 (16)2.8.1. 封装总线和外设基地址 (16)2.8.2. 封装寄存器列表 (17)2.9. 课后练习 (20)第3 章. 初识STM32 标准库 (21)3.1. 课前预习 (21)3.2. 概述 (21)3.3. 库⽬录、⽂件简介 (21)3.4. STM32F10x_StdPeriph_Driver ⽂件夹 (24)3.5. 库各⽂件间的关系 (26)3.6. 初识库函数 (28)⽬录第2 页SAIUR201 6陈德⾦⽼师编著3.7. 课后练习 (29)第4 章. GPIO 的使⽤ (30)4.1. 课前预习 (30)4.2. 概述 (30)4.3. GPIO 简介 (30)4.4. GPIO 框图剖析 (31)4.4.1. 保护⼆极管及上、下拉电阻 (31)4.4.2. P-MOS 管和N-MOS 管 (31)4.4.3. 输出数据寄存器 (33)4.4.4. 复⽤功能输出 (34)4.4.5. 输⼊数据寄存器 (34)4.4.6. 复⽤功能输⼊ (34)4.4.7. 模拟输⼊输出 (34)4.5. GPIO ⼯作模式 (35)4.5.1. 输⼊模式(模拟/浮空/上拉/下拉) (35)4.5.2. 输出模式(推挽/开漏) (35)4.5.3. 复⽤功能(推挽/开漏) (35)4.6. 点亮LED-硬件设计 (37)第5 章. STM32 RCC 时钟系统 (43)5.1. 课前预习 (43)5.2. 概述 (43)5.3. RCC 主要作⽤—时钟部分 (43)5.4. RCC 框图剖析—时钟部分 (43)5.5. 系统时钟 (44)5.5.1. HSE ⾼速外部时钟信号 (44)5.5.2. PLL 时钟源 (45)5.5.3. PLL 时钟PLLCLK (45)5.5.4. 系统时钟SYSCLK (45)5.5.5. AHB 总线时钟HCLK (45)5.5.6. APB2 总线时钟HCLK2 (45)⽬录SAIU R20 1 6 第3页5.5.7. 总线时钟HCLK1 (46)5.6. 设置系统时钟库函数 (46)5.7. 其他时钟 (47)5.7.1. USB 时钟 (47)5.7.2. Cortex 系统时钟 (47)5.7.3. ADC 时钟 (48)5.7.4. RTC 时钟、独⽴看门狗时钟 (48)5.7.5. MCO 时钟输出 (48)5.8. 配置系统时钟实验 (48)5.8.1. 使⽤HSE (48)5.8.2. 使⽤HSI (48)5.8.3. 硬件设计 (49)5.8.4. 软件设计 (49)5.8.5. 编程要点 (49)5.8.6. 代码分析 (49)5.8.7. 下载验证 (54)第6 章. STM32 中断应⽤概览 (55)6.1. 课前预习 (55)6.2. 概述 (55)6.3. 异常类型 (55)6.4. NVIC 简介 (56)6.5. NVIC 寄存器简介 (56)6.6. NVIC 中断配置固件库 (57)6.7. 优先级的定义 (58)6.7.1. 优先级定义 (58)6.7.2. 优先级分组 (58)6.8. 中断编程 (59)6.9. 课后练习 (60)第7 章. EXTI—外部中断/事件控制器 (61)7.1. 课前预习 (61)7.2. 概述 (61)7.3. EXTI 简介 (61)7.4. EXTI 功能框图 (61)7.5. 中断/事件线 (63)7.6. EXTI 初始化结构体详解 (64)7.7. 外部中断控制实验 (65)7.7.1. 硬件设计 (65)7.7.2. 软件设计 (65)⽬录第4 页SAIUR201 6陈德⾦⽼师编著7.7.3. 编程要点 (65)7.7.4. 代码分析 (65)7.7.5. 下载验证 (69)7.8. 课后练习 (69)第8 章. SysTick 系统定时器 (70)8.5.4. 代码分析 (73)8.6. 课后练习 (79)第9 章. USART—串⼝通讯 (80)9.1. 课前预习 (80)9.2. 概述 (80)9.3. 串⼝通讯协议简介 (80)9.3.1. 物理层 (80)9.3.2. 协议层 (84)9.4. STM32 的USART 简介 (85)9.5. USART 功能框图 (85)9.6. USART 初始化结构体详解 (90)9.7. USART1 接发通信实验 (91)9.7.1. 硬件设计 (92)9.7.2. 软件设计 (92)9.7.3. 编程要点 (92)9.7.4. 代码分析 (93)9.7.5. 下载验证 (97)9.8. 课后练习 (97)第10 章. DMA 直接存储区访问 (98)10.1. 课前预习 (98)10.2. 概述 (98)10.3. DMA 简介 (98)10.4. DMA 功能框图 (98)10.5. DMA 数据配置 (100)10.6. DMA 初始化结构体详解 (101)⽬录SAIU R20 1 6 第5页10.7. DMA 存储器到存储器模式实验 (103)10.7.1. 硬件设计 (103)10.7.2. 软件设计 (103)10.7.3. 编程要点 (103)10.7.4. 代码分析 (104)10.7.5. 下载验证 (107)10.8. 课后练习 (107)第11 章. TIM 基本定时器 (108)11.1. 课前预习 (108)11.2. 概述 (108)11.3. 定时器分类 (108)11.4. 基本定时器功能框图讲解 (109)11.5. 定时器初始化结构体详解 (110)11.6. 基本定时器定时实验 (111)11.6.1. 硬件设计 (111)11.6.2. 软件设计 (111)11.6.3. 编程要点 (111)11.6.4. 软件分析 (111)11.6.5. 下载验证 (114)11.7. 课后练习 (114)第12 章. TIM ⾼级定时器 (115)12.1. 课前预习 (115)12.2. 概述 (115)12.3. ⾼级控制定时器 (115)12.4. ⾼级控制定时器功能框图 (116)12.4.1. 时钟源 (117)12.4.2. 外部时钟模式1 (117)12.4.3. 外部时钟模式2 (118)12.4.4. 内部触发输⼊ (119)12.4.5. 输⼊捕获 (121)12.4.6. 输出⽐较 (122)12.4.7. 断路功能 (125)12.5. 输⼊捕获应⽤ (125)⽬录第6 页SAIUR201 6陈德⾦⽼师编著12.7.2. PWM 边沿对齐模式 (128)12.7.3. PWM 中⼼对齐模式 (129)12.8. 定时器初始化结构体详解 (129)12.8.1. TIM_TimeBaseInitTypeDef (130)12.8.2. TIM_OCInitTypeDef (130)12.8.3. TIM_ICInitTypeDef (131)12.8.4. TIM_BDTRInitTypeDef (132)12.9. PWM 互补输出实验 (133)12.9.1. 硬件设计 (133)12.9.2. 软件设计 (133)12.9.3. 编程要点 (133)12.9.4. 软件分析 (134)12.9.5. 下载验证 (136)第13 章. I2C 通讯 (138)13.1. 课前预习 (138)13.2. 概述 (138)13.3. I2C 协议简介 (138)13.3.1. I2C 物理层 (139)13.3.2. 协议层 (140)13.3.3. 通讯的起始和停⽌信号 (141)13.4. STM32 的I2C 特性及架构 (144)13.4.1. STM32 的I2C 外设简介 (144)13.4.2. STM32 的I2C 架构剖析 (145)13.4.3. 通讯过程 (147)13.5. I2C 初始化结构体详解 (149)13.6. I2C—读写EEPROM 实验 (150)13.6.1. 硬件设计 (150)13.6.2. 软件设计 (151)13.6.3. 编程要点 (151)13.6.4. 代码分析 (152)13.6.5. 下载验证 (167)13.7. 课后练习 (168)第14 章. SPI 通讯 (169)14.1. 课前预习 (169)14.2. 概述 (169)14.3. SPI 协议简介 (169)14.3.1. SPI 物理层 (169)14.3.2. 协议层 (171)⽬录SAIU R20 1 6 第7页14.4. STM32 的SPI 特性及架构 (173)14.4.1. STM32 的SPI 外设简介 (173)14.4.2. TM32 的SPI 架构剖析 (174)14.4.3. 通讯过程 (175)14.5. SPI 初始化结构体详解 (177)14.6. SPI—读写串⾏FLASH 实验 (178)14.6.1. 硬件设计 (179)14.6.2. 软件设计 (179)14.6.3. 编程要点 (180)14.6.4. 代码分析 (180)14.6.5. 下载验证 (198)14.7. 课后练习 (198)第15 章. 陀螺仪姿态检测 (199)15.1. 课前预习 (199)15.2. 概述 (199)15.3. 姿态检测 (199)15.3.1. 基本认识 (199)15.3.2. 坐标系 (200)15.4. 利⽤陀螺仪检测⾓度 (201)15.5. 利⽤加速度计检测⾓度 (202)15.9.2. MPU6050 模块的引脚功能说明 (205)15.9.3. MPU6050 模块的硬件原理图 (205)15.10. MPU6050 模块的特性参数 (206)15.11. MPU6050—获取原始数据实验 (207)15.11.1. 硬件设计 (207)15.11.2. 配套程序简介 (208)15.11.3. 软件设计 (209)15.11.4. 程序设计要点 (209)15.11.5. 代码分析 (209)15.11.6. 下载验证 (215)15.12. MPU6050—利⽤DMP 进⾏姿态解算 (216)15.12.1. 硬件设计 (216)15.12.2. 软件设计 (216)15.12.3. 程序设计要点 (216)⽬录第8 页SAIUR201 6陈德⾦⽼师编著15.12.4. 代码分析 (216)15.12.5. 下载验证 (226)15.13. MPU6050—使⽤第三⽅上位机 (227)15.13.1. 硬件设计 (227)15.13.2. 软件设计 (227)15.13.3. 程序设计要点 (227)15.13.4. 代码分析 (227)15.13.5. 下载验证 (231)第1 章.初识STM32SAIU R20 1 6 第1页第1 章. 初识STM321.1. 课前预习在书上找到答案。

电子设计常用芯片清单

H

I

IGET驱动...............EXB841(开关器件..BUP304)

J 集成稳压芯片............LM337 检波器..................MX636 键盘/显示器控制芯片.....8279 接收器.................M3486 K 开关...................CD4051(多路)

MAX4051 /4052 /4053

第1页

新建 文本文档

Q

R

S SPWM波产生.............AD9851 3端可调分流基准源.......TL431 三极管.................2N3906 3端稳压器..............LM317 输出显示...............MAX136 锁相环.................CD4046

E 二极管..................MV209(变容) 2AP30

F 分频器..................MC12022(前置) 集成放大器..............AD603(可控增益宽带) 发送器..................MC3487 F/V变换..................LM331 FSK解调器...............XR2211

D 单相电源滤波器..........SH160-6 达林顿管................TIP122 TIP127 TIP132 DDS芯片.................AD9852(正旋信号发生器) AD9835 电压源..................MC1403(带隙基准) 定时器.................555系列

MX25L6405D中文资料