面向FPGA的稀疏傅里叶并行算法实现

基于FPGA的并行实序列FFT算法研究与实现

基于FPGA的并行实序列FFT算法研究与实现随着科技的发展,要求越来越高的数据处理速度对计算技术提出了更高的要求。

离散傅立叶变换(Discrete Fourier Transform,简称DFT)是一种重要的信号处理技术,广泛应用于通信、图像处理等领域。

FFT (Fast Fourier Transform)是一种快速计算DFT的算法,大大提高了DFT的计算效率。

现在,越来越多的应用需要实时处理海量的数据,这对FFT算法提出了更高的要求。

然而,传统基于CPU的FFT算法在处理大规模数据时效率低下。

为了加速FFT算法,可以利用FPGA并行计算的特性。

FPGA(Field Programmable Gate Array)是一种集成电路,可以通过配置逻辑门来实现特定的功能。

相较于通用处理器,FPGA具有可编程性强、并行计算能力强等优点。

因此,利用FPGA进行并行实序列FFT算法的设计与实现,可以大大提高计算效率。

首先,需要了解并行实序列FFT算法的原理。

实序列FFT算法可以将输入序列分为偶数部分和奇数部分,然后通过FFT算法分别计算这两部分的DFT,最后将结果进行合并即可得到整个序列的DFT。

并行算法的设计思路是将这些计算任务分配给多个处理单元,并行计算。

在FPGA上实现并行实序列FFT算法,可以通过以下步骤:1.设计FPGA的结构:将输入序列分为偶数部分和奇数部分,并为每个处理单元分配计算任务。

2.对每个处理单元进行FFT计算:在每个处理单元内部,实现FFT算法,计算偶数部分和奇数部分的DFT。

3.合并计算结果:将各个处理单元计算得到的DFT结果进行合并,得到整个序列的DFT。

在设计并行实序列FFT算法时1.处理单元之间的通信:处理单元之间需要进行数据的传输和同步。

可以使用FPGA内部的通信接口来实现高速数据传输,保证各个处理单元的计算结果能够及时传输和合并。

2.数据存储:在FPGA上进行大规模数据的计算,需要合理设计数据存储结构,以提高计算效率。

用FPGA实现FFT算法

用FPGA实现FFT算法引言DFT(Discrete Fourier Transformation)是数字信号分析与处理如图形、语音及图像等领域的重要变换工具,直接计算DFT的计算量与变换区间长度N的平方成正比。

当N较大时,因计算量太大,直接用DFT算法进行谱分析和信号的实时处理是不切实际的。

快速傅立叶变换(Fast Fourier Transformation,简称FFT)使DFT运算效率提高1~2个数量级。

其原因是当N较大时,对DFT进行了基4和基2分解运算。

FFT算法除了必需的数据存储器ram和旋转因子rom外,仍需较复杂的运算和控制电路单元,即使现在,实现长点数的FFT仍然是很困难。

本文提出的FFT 实现算法是基于FPGA之上的,算法完成对一个序列的FFT计算,完全由脉冲触发,外部只输入一脉冲头和输入数据,便可以得到该脉冲头作为起始标志的N点FFT输出结果。

由于使用了双ram,该算法是流型(Pipelined)的,可以连续计算N点复数输入FFT,即输入可以是分段N点连续复数数据流。

采用DIF(Decimation In Frequency)-FFT和DIT(Decimation In Time)-FFT对于算法本身来说是无关紧要的,因为两种情况下只是存储器的读写地址有所变动而已,不影响算法的结构和流程,也不会对算法复杂度有何影响。

算法实现的可以是基2/4混合基FFT,也可以是纯基4FFT和纯基2FFT运算。

傅立叶变换和逆变换对于变换长度为N的序列x(n)其傅立叶变换可以表示如下:N nkX(k)=DFT[x(n)] =Σ x(n)Wn=0式(1)其中,W=exp(-2π/N)。

当点数N较大时,必须对式(1)进行基4/基2分解,以短点数实现长点数的变换。

而IDFT的实现在DFT的基础上就显得较为简单了:式(2)由式(2)可以看出,在FFT运算模块的基础上,只需将输入序列进行取共轭后再进行FFT运算,输出结果再取一次共轭便实现了对输入序列的IDFT运算,因子1/N对于不同的数据表示格式具体实现时的处理方式是不一样的。

fpga 快速傅里叶变换实现卷积

标题:FPGA实现快速傅里叶变换加速卷积的原理与应用在当今信息时代,数字信号处理和数据处理已经成为许多领域中不可或缺的部分。

而在处理这些信号和数据时,快速傅里叶变换(FFT)和卷积运算是常用的数学工具。

在很多实际应用中,由于其高复杂度,这两个运算往往需要花费大量的时间和资源。

然而,通过利用现代的FPGA技术,我们可以实现这些运算的高效加速,本文将探讨如何利用FPGA来加速实现快速傅里叶变换卷积。

1. 背景介绍快速傅里叶变换(FFT)是一种离散傅里叶变换(DFT)的快速算法。

它不仅可以用于频域分析和信号处理,还被广泛应用于图像处理、通信、雷达和生物医学领域等。

而卷积运算则是数字信号处理和图像处理中常见的运算之一,用于实现信号的滤波、特征提取和模式识别等。

然而,这两种运算都具有较高的计算复杂度,特别是在涉及大规模数据时,传统的处理方法往往效率低下。

2. FPGA加速计算的优势FPGA(Field-Programmable Gate Array)是一种灵活可编程的数字集成电路,它通过可编程的逻辑单元和可编程的连接网络,可以实现大规模的并行计算和高速数据处理。

这使得FPGA在加速计算领域具有独特的优势。

与传统的CPU和GPU相比,FPGA可以根据具体的应用需求进行快速定制和优化,提供更高的计算密度和更低的功耗。

利用FPGA来加速实现FFT和卷积运算,可以大幅提高运算速度和效率。

3. FPGA实现快速傅里叶变换在实现FFT时,FPGA可以充分利用其并行计算的特性,通过设计合适的硬件结构和算法,实现FFT运算的高效加速。

可以采用基于蝶形运算单元(Butterfly)的并行计算结构,利用FPGA的片上资源进行数据流控制和计算单元的并行化。

通过巧妙的数据流设计和数据重用策略,还可以有效地减少时序延迟和资源消耗,进一步提高FFT算法的运行速度。

在实际应用中,基于FPGA的FFT加速器已经被广泛应用于通信系统、无线电频谱监测和图像处理等领域。

fpga做快速傅里叶变换

fpga做快速傅里叶变换(最新版)目录1.引言2.FPGA 与快速傅里叶变换概述3.FPGA 实现快速傅里叶变换的方法4.FPGA 实现快速傅里叶变换的性能分析5.总结正文1.引言随着数字信号处理的广泛应用,快速傅里叶变换(FFT)算法在信号处理领域具有重要的地位。

FPGA(现场可编程门阵列)作为一款可编程硬件,可以实现快速傅里叶变换算法,从而在信号处理领域发挥重要作用。

本文将探讨 FPGA 实现快速傅里叶变换的方法及其性能分析。

2.FPGA 与快速傅里叶变换概述FPGA 是一种集成电路,可以由用户编程配置,从而实现特定的功能。

FPGA 具有高速、可重构和灵活性等优点,在数字信号处理领域有着广泛的应用。

快速傅里叶变换是一种高效的算法,用于计算离散傅里叶变换。

它可以将一个信号从时域转换到频域,从而分析信号的频率成分。

快速傅里叶变换算法有很多种实现方法,如时域抽取法、频域抽取法等。

3.FPGA 实现快速傅里叶变换的方法FPGA 实现快速傅里叶变换的方法有很多种,其中一种常见的方法是基于蝶形单元的实现。

蝶形单元是一种基本的运算单元,可以实现基的傅里叶变换。

通过将多个蝶形单元组合起来,可以实现更高级的傅里叶变换,如点的傅里叶变换。

另一种常见的实现方法是基于流水线的方法。

这种方法将快速傅里叶变换算法分解成多个阶段,每个阶段由一个专用的硬件模块完成。

通过将这些模块连接成流水线,可以实现快速傅里叶变换。

4.FPGA 实现快速傅里叶变换的性能分析FPGA 实现快速傅里叶变换的性能取决于多个因素,如硬件资源、算法优化程度等。

一般情况下,FPGA 实现的快速傅里叶变换具有较高的性能,因为它可以充分利用硬件资源,降低算法复杂度。

然而,FPGA 实现快速傅里叶变换也存在一定的局限性。

由于 FPGA 的硬件资源有限,实现大规模的快速傅里叶变换可能会受到性能和资源的限制。

此外,FPGA 的编程和调试过程相对复杂,可能需要较长的开发周期。

基于FPGA的FFT算法的实现

基于FPGA的FFT算法的实现摘要:信号处理在电力系统工作中应用广泛,其中快速傅里叶变换(FFT)在信号处理中是一种采用较多的方式。

现提出一种基于FPGA的快速傅里叶变化算法的实现方式,同时给出基于Modelsim的仿真结果与Matlab的计算结果进行对比。

关键词:FFT;FPGA;信号处理0 引言FFT是DFT的一种快速计算方式,能够将DFT运算的计算效率提高1~2个数量级[1]。

传统的快速傅里叶变化多采用单片机或者DSP进行实现,而单片机都采用循环的串行计算,当碰到高频信号需要较高的采样频率时,其计算结果的实时性无法得到保证。

FPGA(现场可编程门阵列)其并行运算的特性,能够进一步提高FFT计算的速度,拥有较高的实时性。

本文提出了一种基于FPGA的256点的FFT算法的实现。

1 FFT算法的原理对于一个N点有限长度的序列的,其DFT计算方式为:完成一次N点序列的DFT计算需要N2次复数乘法即N(N-1)次复数加法[2],最终需要经历4N2次实数乘法,2N(2N-1)次实数加法才能得到其计算结果,其计算量十分庞大。

考虑到旋转因子的对称性和周期性,有:若N=2M,M为整数,则可将N点序列按照N的奇偶性分为N/2长度的两个序列:根据旋转因子的特性,将上式改写为:如图1-1所示的蝶形运算形式:图1-12 256点基2DIT的FPGA实现2.1 FFT运算模块的结构FFT的设计采用并行迭代的结构,计算完上一级的蝶形运算后将计算结储存在RAM中,作为下一级蝶形运算的输入,继续调用蝶形运算模块,最总完成FFT的计算。

对于256点FFT需要进行8级蝶形运算,每级需要进行128次蝶形运算。

这里采用32位的定点数运算,在节约逻辑门资源的同时也保证了计算的精度。

FFT模块分为数据储存模块,蝶形运算模块,时钟模块,旋转因子储存模块,其整体结构如图2-1所示:图2-1蝶形运算模块的结构图如2-2:图2-22.2 FFT模块的工作过程1)当复位信rst_n(低电平有效)为高电平,发出一个启动信号FFT_START后,FFT模块开始工作,将输入的数据转存到RAM中去。

基于FPGA的并行计算技术

基于FPGA的并行计算技术基于FPGA的并行计算技术是利用现场可编程门阵列(FPGA)进行高性能并行计算的技术。

FPGA是一种自定义硬件的形式,它可以通过重新配置门电路来实现特定的计算任务。

相比于传统的通用处理器,FPGA具有可并行化、低功耗和高密度等优势,因此在并行计算领域具有广泛的应用。

首先,基于FPGA的并行计算技术能够充分利用FPGA的并行处理能力。

FPGA由大量的基本逻辑单元(Logic Slice)组成,每个逻辑单元都可以独立地进行计算操作。

这使得FPGA能够同时执行多个计算任务,实现真正的并行计算。

与传统的多核处理器相比,FPGA可以根据任务的要求灵活配置计算资源,从而有效提高计算效率。

其次,基于FPGA的并行计算技术可以通过数据流架构实现高效的数据并行处理。

数据流架构是一种基于数据依赖的并行计算模型,它将计算任务划分为多个具有数据依赖关系的子任务,并利用并行处理器同时执行这些子任务。

在FPGA上实现数据流架构,可以通过数据流图描述任务之间的数据依赖关系,并利用FPGA的高可编程性将数据流图映射到硬件逻辑上。

这种方式可以充分利用FPGA的并行计算能力,并通过数据流调度算法实现任务之间的流水线执行,从而提高计算效率。

另外,基于FPGA的并行计算技术还可以通过向量化计算实现高效的数据并行处理。

向量化计算是利用向量寄存器对数据进行并行处理的技术,在FPGA上可以采用SIMD(单指令多数据流)架构实现。

FPGA的可编程性可以使得向量寄存器的宽度和数量得以灵活配置,从而满足不同应用的需求。

通过向量化计算,可以充分发挥FPGA的并行计算能力,并实现高效的数据处理。

此外,基于FPGA的并行计算技术还可以通过硬件加速实现高性能的并行计算。

FPGA具有高度可编程性的特点,可以通过定制的硬件逻辑实现特定的计算任务。

对于一些计算密集型的应用,FPGA可以通过编写硬件描述语言(HDL)代码实现硬件加速,从而显著提高计算性能。

基于FPGA的快速傅立叶变换算法实现

本文 中基 于 F P G A的 F F T实现 对 电力 系

统谐 波检 测 , 需要 采集 3路 电压 电流 的谐波 ,

并对 其 进 行 检 测 , 要 保 证 采 集 和 检 测 的六 路 信

系统 谐 波检 测具 有运 算 大、精度 高、 高速度 的特 点,从 而 实现 了 对谐 波信 号的实时监 测处理。

电流频率域系统频率保 持一致 ,因此电流 产生 了畸变 波形,从而导致系统中产生谐波 【 1 ] 。

1 . 1 频 谱 泄 漏

则逻辑 阵列组合而成 的满 足复杂设计方案的一 种 自适应体 系结构 。F P G A优 点在于计算 速度

快,F F T的 运 算 时 间 为 微 秒 级 别 , 甚 至 纳 秒 级

感 器 单 元 接 收 到 6路 信 号 , 利 用 F P G A控 制 AD采样 单 元 实时 采 样 6路 数据 ,再 通 过 F P GA 的线性插值 ,获得 的高点数 ( 2 N)中间 数据 提 供给 F F T单 元计 算 ,最终将 6路计 算

形成 的电流不 是成正比例关系,从而形成波形 较长,均为毫秒级别 。 畸变 。对 于伏 安特性保持正 比例关系的用 电负

P o we r E l e c t r o n i c s ・ 电力 电子

基于 F P G A的快速傅立叶变换算法实现

文 家 九

1 . 2 电力系统 中的谐 波测量

次乘法运算 ,3 2 0次加减 法运算,可见 F F T算 法相 较于 DF T算法 , 当 N越大 时,运算量 将 明显较小 。F F T的此特点有利于 F P GA平台的

档嵌 入 系统 来进 行谐波 检测 ,要满 足 F F T运

算量 ,必须要求配备 的嵌入 式系 统带有 相当数 量的硬件浮点数 ,且利用先进 的编程算来来实 现F F T运算 。 以上两种 方案 的实 时 响应 时间

基于FPGA的FFT算法实现

基于FPGA的FFT算法实现摘要随着数字电子技术的发展,数字信号处理技术具有极其广泛的应用,比如视频压缩、数字机顶盒、有线调制解调器、数字多用盘、多媒体与无线通信、语音处理、传输系统、雷达成像、全球定位系统等等。

同时,信息技术领域是依赖于数字信号处理及其相应的专用集成电路的,所以对数字信号处理的要求越来越高。

因此对数字信号处理中涉及到的有关算法的改进也提出了更高的要求,其中快速傅立叶变换是数字信号处理的一种重要的算法研究。

现场可编程门阵列是近年来出现的一种新的可编程逻辑器件,它具有运行速度快、存储容量大、管脚多等特点。

本文研究的是利用现场可编程门阵列来实现快速傅立叶变换算法,快速傅立叶变换算法的实现,大大缩短了运算所需的时间,降低了因计算复杂而导致的计算误差。

随着超大规模集成电路技术的不断提高,现场可编程门阵列的规模和集成度越来越大,在电子系统的设计中发挥了更大的作用。

主要的设计内容包括现场可编程门阵列的结构与功能、VHDL语言的介绍、算法的实现过程等。

本文通过离散傅立叶变换引出快速傅立叶变换算法,提出了快速傅立叶变换的两种抽取方法,重点介绍了基2按时间抽取的快速傅立叶算法,对算法进行了MAX+PLUSⅡ的仿真,再利用现场可编程门阵列来实现,并对仿真结果进行了分析。

结果表明快速傅立叶变换的算法结果已达到了一定的精度,运算速度能够满足一般实时信号处理的要求。

关键词:现场可编程门阵列,VHDL,快速傅立叶变换,MAX+PLUSⅡAbstractWith the development of digital electronic technology , digital signal processing technology have an extremely wide range of applications ,such as video compression,digital set-top boxes ,cable modems ,digital multi-purpose tray ,multimedia and wireless communications ,voice processing ,transmission systems ,radar imaging ,global positioning systems and so on .Meanwhile ,information technology depend on the digital signal processing and its corresponding application specific integrated circuit ,so the demand of digital signal processing have become more and more .Therefore, the digital signal processing involved in the algorithm is also put forward higher requirements ,and fast Fourier transform digital signal processing is an important algorithm . Field programmable gate array emerged in recent years, and it is a new programmable logic devices .It has the operational speed, storage capacity, much more pins and so on.This paper studies the implementation of FFT based FPGA .The realization of Fast Fourier Transform algorithm greatly reduce the computation time which required to and decrease the computational complexity caused by calculation errors .As VLSI technology continues to improve , its size and growing integration play a bigger role on the design of electronic systems .And the main design elements include the structure and function of FPGA ,the description of VHDL language ,algorithm implementation processes and so on .According to the description of Fourier transform fast Fourier transform algorithm, leading to fast Fourier transform of the two extraction methods .And the paper especially studies the time taken by the base 2 Fast Fourier algorithm and uses MAX+PLUSⅡsimulate it ,meanwhile adopts FPGA to achieve ,and the simulation results are analyzed .The results show that the results of fast Fourier transform algorithm has reached a certain degree ,and its accuracy, computation speed can meet the general requirements of real-time signal processing .Keywords :FPGA,VHDL,FFT,MAX+PLUSⅡ目录第1章绪论 (1)1.1 FFT算法的研究现状及应用 (1)1.2 课题的提出 (1)1.3 FPGA实现FFT的优势 (2)1.4 本文的研究工作 (2)第2章可编程门阵列与VHDL (3)2.1 可编程门阵列 (3)2.1.1 FPGA的基本结构 (3)2.1.2 FPGA的基本特点 (3)2.1.3 FPGA的配置模式与功能 (4)2.2 VHDL的出现 (4)2.2.1 VHDL硬件描述语言 (4)2.2.2 VHDL的基本结构 (5)第3章 FFT算法研究 (6)3.1 傅立叶变换 (6)3.2 离散傅立叶变换 (6)3.3 FFT的基本思想 (6)3.4 快速傅立叶变换 (7)3.4.1 基于时选的快速傅立叶变换 (7)3.4.2 基于频选的快速傅立叶变换 (11)3.5 FFT算法的类型 (13)第4章FFT算法的软件设计与仿真 (15)4.1 FFT算法模块设计的层次划分 (15)4.2旋转因子 (15)4.2.1旋转因子模块 (15)4.2.2旋转因子复数乘法器算法研究 (15)4.3加/减法器 (16)4.3.1端口命名 (16)4.3.2加/减法器设计 (17)4.4乘法器 (18)4.4.1端口命名 (18)4.4.2乘法器设计 (18)4.5 基-2蝶形处理器 (19)小结 (20)致谢 (21)参考文献 (22)附录 (23)第1章绪论1.1 FFT算法的研究现状及应用数字信号处理是起源于十七和十八世纪数学的一个学科,当时加文(Garwin)在他的研究中极需要一个计算傅立叶变换的快速方法。

稀疏编码的并行计算方法与技巧

稀疏编码的并行计算方法与技巧稀疏编码是一种重要的信号处理技术,广泛应用于图像处理、语音识别、模式识别等领域。

在大规模数据处理和高效计算的需求下,如何提高稀疏编码的计算效率成为一个关键问题。

本文将介绍稀疏编码的并行计算方法与技巧。

一、稀疏编码简介稀疏编码是一种基于稀疏表示的信号处理方法,其核心思想是通过选择少量的基向量来表示信号,从而实现信号的压缩和降维。

在稀疏编码中,通常使用L1范数来衡量信号的稀疏性,即最小化信号的L1范数,使得信号的大部分系数为零。

二、串行计算方法的局限性传统的串行计算方法在处理大规模数据时存在一定的局限性。

首先,串行计算无法充分利用多核处理器的并行计算能力,导致计算效率低下。

其次,串行计算方法在计算过程中需要依次处理每个样本,导致计算时间随着样本数量的增加而线性增长。

最后,串行计算方法无法处理实时数据流,对于需要实时处理的应用场景存在较大的困难。

三、并行计算方法的优势为了克服串行计算方法的局限性,研究者们提出了一系列的并行计算方法与技巧。

并行计算方法可以充分利用多核处理器的并行计算能力,提高计算效率。

同时,并行计算方法可以同时处理多个样本,大大减少计算时间。

此外,并行计算方法还可以实现实时处理,满足对实时性要求较高的应用场景。

四、并行计算方法的具体实现在稀疏编码的并行计算中,可以采用多种并行计算方法。

一种常见的方法是将数据划分为多个子集,然后分配给不同的处理器进行并行计算。

每个处理器计算得到的稀疏编码结果可以合并得到最终的结果。

另一种方法是采用图像处理中常用的并行计算技术,如并行投影、并行反投影等。

这些方法可以有效地提高稀疏编码的计算效率。

五、并行计算方法的技巧除了基本的并行计算方法外,还有一些技巧可以进一步提高稀疏编码的计算效率。

首先,可以采用稀疏编码的近似算法,如OMP算法、LARS算法等,以减少计算量。

其次,可以采用稀疏编码的快速算法,如快速哈达玛变换、快速傅里叶变换等,以加快计算速度。

fpga 快速傅里叶变换实现卷积延迟

在FPGA中实现快速傅里叶变换(FFT)以及卷积延迟是一项复杂但极具挑战性的任务。

通过对这一主题的深入探讨,我们可以更好地理解FPGA在信号处理和数字系统方面的应用,以及如何最大限度地减少卷积的延迟。

1. 快速傅里叶变换(FFT)的基本概念FFT是一种用于将时域信号转换为频域信号的算法。

通过使用FFT,我们可以有效地分析信号的频谱特性,从而在很多领域中得到应用,比如通信系统和图像处理。

在FPGA中实现FFT需要考虑算法的复杂度和数据流的处理,以及如何利用硬件加速来提高计算效率。

2. FPGA中的FFT实现在FPGA中实现FFT需要充分利用硬件资源和并行计算的优势。

通过合理的数据流架构和硬件优化,我们可以在FPGA上实现高效的FFT 算法。

考虑到FFT的复杂性,我们还需要充分利用FPGA的硬件并行性和流水线功能,以实现快速和准确的FFT计算。

3. FPGA中卷积延迟的挑战卷积是数字信号处理中常用的运算,但在FPGA中实现卷积时会面临延迟和复杂度的问题。

通过对卷积运算的分析,我们可以深入了解在FPGA中如何通过优化算法和硬件架构来降低卷积的延迟,从而提高系统的性能和效率。

4. 解决方案和思考为了在FPGA中实现FFT和降低卷积延迟,我们可以采取一系列方法和策略。

通过使用并行计算和流水线技术来提高FFT和卷积的计算速度;同时利用FPGA的硬件资源来减少算法复杂度和提高运算效率;我们还可以借助现有的开发工具和IP核来快速实现FFT和卷积,从而降低开发成本和时间。

5. 总结通过本文的探讨,我们对FPGA中实现FFT和降低卷积延迟有了更加深入的了解。

通过合理的算法设计、硬件优化和并行计算,我们可以充分利用FPGA的性能和资源,从而实现高效的FFT和快速的卷积运算。

对于未来的研究和应用,我们还需深入探讨如何进一步改进FFT算法和降低卷积的延迟,以满足对实时信号处理和高性能计算的需求。

个人观点:作为一名FPGA开发工程师,我深知在实现FFT和降低卷积延迟时所面临的挑战和困难。

fpga做快速傅里叶变换

fpga做快速傅里叶变换【原创实用版】目录1.引言2.FPGA 与快速傅里叶变换3.FPGA 实现快速傅里叶变换的方法4.整体结构及蝶形单元5.性能分析6.结论正文1.引言傅立叶变换是一种数字处理中的基本操作,被广泛应用于表述和分析离散时域信号领域。

然而,随着信号点数的增加,其运算量与变换点数的平方成正比关系,使得直接应用算法进行谱变换在较大时变得不切实际。

为了解决这一问题,快速傅里叶变换技术应运而生。

本文将介绍基于 FPGA 实现快速傅里叶变换的方法。

2.FPGA 与快速傅里叶变换FPGA(现场可编程门阵列)是一种集成电路,可以实现数字信号的处理和控制。

与传统的 CPU 和 GPU 相比,FPGA 具有更高的计算效率和更低的功耗。

这使得 FPGA 在需要大量计算的领域,如信号处理、图像处理和深度学习等领域具有很大的优势。

而快速傅里叶变换正是 FPGA 应用的一个重要领域。

3.FPGA 实现快速傅里叶变换的方法FPGA 实现快速傅里叶变换有很多种方法,如时域抽取法、频域抽取法和等。

本文主要以算法为对象来讨论。

该算法的基本思想是将高点数的傅立叶变换通过多重低点数傅立叶变换来实现。

虽然与有差别,但由于它们在本质上都是一种基于标号分解的算法,故在运算量和算法复杂性等方面完全一样,而没有性能上的优劣之分。

4.整体结构及蝶形单元基于 FPGA 的快速傅里叶变换的基本结构主要包括基模块、复数乘法器、存储单元和存储器控制模块。

其整体结构如图所示。

其中,用来存储输入数据、运算过程中的中间结果以及运算完成后的数据,用来存储旋转因子表。

蝶形运算单元即为基模块,控制模块可用于产生控制时序及地址信号,以控制中间运算过程及最后输出结果。

5.性能分析基于 FPGA 的快速傅里叶变换具有较高的计算效率和较低的功耗。

其运算速度和资源占用与 FPGA 的硬件性能和算法优化程度密切相关。

一般来说,随着 FPGA 硬件性能的提高和算法优化的深入,基于 FPGA 的快速傅里叶变换的性能将得到进一步提升。

fpga做快速傅里叶变换

fpga做快速傅里叶变换FPGA(Field Programmable Gate Array,现场可编程门阵列)作为一种可编程逻辑器件,具有高度灵活性和并行处理能力,已广泛应用于信号处理领域。

在信号处理中,傅里叶变换(Fourier Transform,FFT)常用于将信号从时域转换为频域,以实现频谱分析、滤波、信号识别等功能。

因此,将FFT算法实现在FPGA 上,能够充分发挥FPGA的并行计算能力,提高傅里叶变换的计算速度。

实现FFT算法的关键在于将信号分解为不同频率的正弦和余弦波,然后对这些波进行频谱分析。

FFT算法利用了对称性和乘法约简等技术,将傅里叶变换的计算复杂度从O(N^2)降低到O(NlogN),大大提高了计算效率。

在FPGA上实现FFT算法,可以通过并行计算和高速存储器的配合,进一步加快计算速度。

具体实现FFT算法的FPGA系统,可以分为以下几个模块:1. 输入/输出模块:负责将待处理的信号输入到FPGA中,并将计算结果输出。

FPGA具有高速IO接口,可以方便地与外部系统进行数据交互。

2. 数据处理模块:对输入的信号进行预处理,例如加窗处理、零填充等。

然后,将处理后的信号分成不同频率的子信号,交给并行计算单元进行处理。

3. 并行计算单元:包括多个计算核心,每个核心负责计算一个频率分量的傅里叶变换。

这些计算核心之间可以通过数据流方式进行数据交换,提高计算效率。

4. 存储器模块:FPGA内部包含大量的高速存储器,用于存储FFT算法的中间结果和输入/输出数据。

通过充分利用存储器的带宽和并行访问能力,可以提高计算效率。

5. 控制模块:负责控制整个系统的运行流程,包括时钟、时序控制和状态机控制等。

控制模块可以根据输入数据的特点,动态调整计算资源的分配和工作频率,以获得更高的计算性能。

实现FFT算法的FPGA系统需要综合考虑计算精度、资源利用率和功耗等因素。

对于不同的应用场景,可以选择不同的FPGA 型号和算法优化策略,以达到最佳性能和成本的平衡。

一种基于FPGA 并行加速的稀疏矩阵求解方法

第49卷第11期电力系统保护与控制Vol.49 No.11 2021年6月1日 Power System Protection and Control June 1, 2021 DOI: 10.19783/ki.pspc.200948一种基于FPGA并行加速的稀疏矩阵求解方法吴志勇1,王晞阳1,陈继林2(1.国家超级计算无锡中心,江苏 无锡 214072;2.中国电力科学研究院有限公司,北京 100085)摘要:研究了电力系统电磁暂态仿真中最耗时的稀疏矩阵快速求解问题。

采用了算法定义架构的设计思想,提出了一种DAG静态并行调度算法,并设计了与之相适配的硬件并行加速阵列架构。

在设计实现中,针对电磁暂态仿真运算中稀疏矩阵求解的特性,采用了精确的节拍级硬件资源调度,实现了高度融合的软硬件协同加速。

在此基础上,进行了该设计的测试及性能分析。

实验结果表明,该结构和方法在电力系统稀疏矩阵运算中的性能优于通用CPU和GPU。

关键词:稀疏矩阵;DAG;数据流机;静态调度;并行算法;现场可编程门阵列(FPGA)A method for solving a sparse matrix based on FPGA parallel accelerationWU Zhiyong1, WANG Xiyang1, CHEN Jilin2(1. National Supercomputing Center in Wuxi, Wuxi 214072, China;2. China Electric Power Research Institute Co., Ltd., Beijing 100085, China)Abstract: This paper studies the most time-consuming sparse matrix fast solving problem in the electromagnetic transient simulation of a power system. It adopts the design idea of algorithm definition architecture, proposes a DAG static parallel scheduling algorithm, and designs a suitable hardware parallel to accelerate the array architecture. In the design and implementation, in order to solve the sparse matrix in the electromagnetic transient simulation operation, the precise beat-level hardware resource scheduling is adopted to realize the highly integrated software and hardware coordination acceleration. A design test and performance analysis is carried out. The results show that the structure and method performance is better than general-purpose CPU and GPU in the sparse matrix operation of a power system.This work is supported by the Science and Technology Project of State Grid Corporation of China “Research and Development of High-performance Computing Technology Suitable for Power System Applications” (No.XTB17201900305).Key words: sparse matrix; DAG; data-flow computer; static scheduling; parallel algorithm; field programmable gate array (FPGA)0 引言在电力系统仿真中,电磁暂态仿真是主要的系统仿真应用之一,也是电力系统安全分析和运行的关键组件[1-4]。

fpga 傅里叶变换的速度

fpga 傅里叶变换的速度

(原创版)

目录

1.FPGA 与傅里叶变换

2.FPGA 实现傅里叶变换的优势

3.FPGA 实现傅里叶变换的方法

4.FPGA 在实时光谱探测中的应用

5.总结

正文

FPGA(现场可编程门阵列)是一种集成电路,可以实现数字电路的快速配置和重新配置。

近年来,FPGA 在信号处理领域得到了广泛应用,尤其是快速傅里叶变换(FFT)。

傅里叶变换是一种在信号处理中常用的算法,它可以将一个信号从时域转换到频域。

这种转换在许多应用中都很重要,比如音频处理、图像处理和通信等。

快速傅里叶变换(FFT)是傅里叶变换的一种高效算法,可以大大减少计算时间。

FPGA 实现傅里叶变换的优势在于其并行计算能力。

FPGA 可以通过与或非电路实现 FFT 硬件的算法,在 ns 时钟的时钟节拍下可以并行做计算。

相比之下,CPU 上的软件 FFT 算法实现,即使有多级流水线,也很难做到硬件算法的速度。

FPGA 实现傅里叶变换的方法有多种。

首先,可以自己编写 Verilog 代码实现 FFT 算法。

其次,可以从开源社区下载已经实现好的 FPGA 版FFT 算法,并进行调试和仿真。

最后,可以直接使用 Xilinx 等公司的 IP (知识产权)库中的预设 FFT 模块。

在实时光谱探测中,FPGA 可以实现快速傅里叶变换,从而快速地获

取光谱信息。

例如,优化基 2-FFT 算法,并利用 Xilinx 公司的 FPGA 实现,可以大大提高光谱探测的效率和精度。

总的来说,FPGA 在实现傅里叶变换方面具有速度优势,并且有多种实现方法。

基于FPGA的并行实序列FFT算法研究与实现

基于FPGA的并行实序列FFT算法研究与实现钟强;刘云学;刘鹏飞;秦绪栋;王娟娟;张红【期刊名称】《烟台大学学报(自然科学与工程版)》【年(卷),期】2016(029)004【摘要】快速傅里叶变换( FFT)算法的优劣直接影响信道化接收机的性能。

文章围绕信道化接收机中的FFT模块进行研究,提出了一种可以对数据进行并行处理的FFT算法。

并根据实际工程应用要求,将目前普遍采用的复序列运算改为实序列运算。

文章以MATLAB软件进行理论运算,在现场可编程逻辑门阵列( FPGA )芯片环境下用ModelSim软件进行逻辑功能仿真,两者结果进行比较后表明,文中设计的算法结果正确,逻辑资源利用率高,完全符合要求。

%The advantages and disadvantages of fast fourier transform( FFT) algorithm directly affect the perform-ance of the channelized receiver. In this paper, a FFT algorithm for parallel processing of data is proposed based on the research of the FFT module in the channelized receiver, and the real sequence operation is adopted instead of the commonly used complex sequence operation according to the practical engineering application requirements. The MATLAB software is used for theoretical calculation, and the logic function simulation is carried out in the field-programmable gate array( FPGA) chip environment with ModelSim software. The comprison of the two results shows that the result of the algorithm is correct, the logic resource utilization is high, and the result is in full compliance with the requirements.【总页数】5页(P294-298)【作者】钟强;刘云学;刘鹏飞;秦绪栋;王娟娟;张红【作者单位】烟台大学光电信息科学技术学院,山东烟台264005;烟台大学光电信息科学技术学院,山东烟台264005;烟台大学光电信息科学技术学院,山东烟台264005;烟台大学光电信息科学技术学院,山东烟台264005;烟台大学光电信息科学技术学院,山东烟台264005;烟台大学光电信息科学技术学院,山东烟台264005【正文语种】中文【中图分类】TN957.51【相关文献】1.基于TMS320C80的FFT算法的并行实现 [J], 胡辉;丁士圻2.基于FPGA的新型高速FFT算法研究与实现 [J], 顾艳丽;周洪敏3.基于时间序列的并行实时渲染系统研究与实现 [J], 付金华;徐洁;常化文;4.基于多核架构适用于LTE标准的FFT算法研究与实现 [J], 徐虎雄;盛嘉奕;陈赟;虞志益5.基于轻核阵列机的FFT算法并行化研究与实现 [J], 常立博;王时雨因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的数字信号处理算法实现-机械工程论文-工程论文

基于FPGA的数字信号处理算法实现-机械工程论文-工程论文——文章均为WORD文档,下载后可直接编辑使用亦可打印——摘要:数字信号处理技术的应用必须依赖于一定的算法, 并且在复杂应用场合中往往会采用较复杂的算法, 这对数字信号处理芯片的性能和资源提出了越来越高的要求。

笔者首先介绍了数字信息处理的基本理论, FPGA的基本原理、技术特点及应用思路, 并以数字信号处理领域中广泛应用的FFT算法为例, 对FPGA在数字信号处理中的应用进行了详细的分析, 为相关领域的研究提供有价值的参考。

关键词:DSP; FPGA; VHDL; FFT;Abstract:The application of digital signal processing technology must rely on a certain algorithm, and in complex applications often use more complex algorithms, which put higher and higher requirements on the performance and resources of digital signal processing chips. The author first introduces the basic theory of digital information processing, the basic principle, technical features and application ideas of FPGA, and takes the FFT algorithm widely used in the digital signal processing field as an example, and analyzes the application of FPGA in the digital signal processing in detail, and provides valuable reference for the research of the related domain.Keyword:DSP; FPGA; VHDL; FFT;1、前言数字信号处理是20世纪60年发展起来的, 在信息技术的发展背景下迅速成为了一门新兴的学科。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

面向FP G A的稀疏傅里叶并行算法实现杨超,钱慧(福州大学物理与信息工程学院,福建福州350108)摘要:提出了一种基于最优搜索的稀疏傅里叶变换(SFT)的并行实现设计。

首先将输入信号分为并行Q组,分别进行快速傅 里叶变换(FFT),实现信号频率分量的取模处理,然后通过排序搜索获得。

经验证,相较于FFTW,当信号长度大于524 288时,执行时间会有更好的表现;相较于正交匹配算法及其他SFT的FP G A实现,其系统的复杂度降低了。

关键词:稀疏傅里叶变换;并行框架;现场可编程门阵列中图分类号:TN911.7 文献标识码:A D0I: 10. 19358/j.issn.1674-7720.2017. 10.020引用格式:杨超,钱慧.面向FPG A的稀疏傅里叶并行算法实现[J].微型机与应用,2017,36(10):70-73.The parallel frameworlt of sparse Fourier transform on FPGAY a ng Ch a o,Q ia n H ui(C olle ge of Ph ysic s a nd In formatio n En gi n eeri ng,Fu z h o u Un iversit y,Fu z h o u350108,China)Abstract:This paper proposed the parallel framework of sparse Fourier transform and implemented all the design on FPGA.The input signal is divided into Q groups to search for the optimal solution.It is proved that the design compared to the fast Fourier transform in the West!FF-TW),the execution time has a better performance when the signal length is greater than implementation of orthogonal m atching pursuit algorithm and other implementation of sparse Fourier transform algorithm,this design reduces the complexity of the system.Key w ords:sparse Fourier transform;parallel frameworls;FPGA〇引言稀疏傅里叶变换(Sparse Fourier Transform,SFT)是一-种新的算法框架,也是快速傅里叶变换(F a t Fourier T ra n s o m,FFT)在处理稀疏频谱信号上的延伸。

2003年 AYDINER A A等人提出了针对频域稀疏信号的傅里叶变 换基本思想[1]。

对于频域稀疏信号来说,其频谱可以通过 其多级子集频谱获得。

之后,IWEN M A等人从压缩感知 得到启发,将采样和频率估计整合到快速傅里叶变换并提 出了经典S FT框架[2]。

之后S F T广泛运用于稀疏频谱信号(诸如音频信号、医学图像信号)的处理以及频谱感知 领域[3]。

大量的S FT算法被提出,它们多利用经典的频率 估计算法通过亚奈奎斯特采样点的子集的傅立叶变换重构稀疏频点[4]。

但由于经典S F T的亚奈奎斯特率样本是通过多次采样获得的,因此,经典S F T不可能代替F F T来 处理实时信号,比如雷达信号等。

2010年以来,一种并行结构的S F T算法受到了广泛的关注[5]。

并行S FT首先通过并行下采样,采集计算所 需的所有时域数据,然后再通过F F T,通过亚线性频谱估计方法获得信号的稀疏频率及其幅值。

由于该类方法以 并行取代迭代获得频谱估计所需的所有信息,因此可以实 时处理各种频域稀疏信号,使得经典S FT得到了改善。

基于此,参考文献[6] _ [8]探讨了稀疏傅里叶变换在GPU以及多核C PU上的实现方式。

这些研究显示,基于GPU加速的实现方案运行速度要显著高于基于C P U的实现方 案。

然而,基于G P U的实现方案都存在主存储区与GPU存储区的连接交互问题,因此数据间的正常流动不能得到更好的促进。

为解决G P U的数据并行处理的局限性,本文研究S F T的并行算法并在F P G A上对其进行实现,同时应用中国余数定理(CRT)的基本原理对信号进行重构。

相较于传统的SF T,本文的方法可以极大地降低系统的复杂度,减少了硬件的开销。

本文,首先介绍S F T的并行框架,然后讨论S F T的F P G A实现架构,最后从仿真结果以及硬件实现两方面对系统进行评估。

1S F T并行算法S F T并行算法主要由下采样、频率估计、幅度估计个部分组成。

在下采样过程中,将输信号划分为Q个组,每个组的采样因子分别为/,/,…,/q。

利用中国余数定理(Chinese Residue Theorem,CRT)进行频率以及幅度的估计,设定各组的采样因子两两互质。

并行S FT算法从)个采样样点中重构2 O算个参数,其中包括O个时延参数以及O个幅度参数。

重构法的具体计算步骤如下:首先,设采样通道数为Q ,每个通道的采 样点数分别为-,. =1,2,…,计算X 0 M !X ,其中6为下采样矩阵,X 为采样样本。

之后,对X 进行D F T 变换,得到X = @F T (X )。

按幅度从大到小对X 向量中的值 进行排序,计算:0 B Y M AX I X 7,B $ [0,〇](1)其中O 为指定的重构信号的参数。

得到Y b 之后则可通过 求余运算获取余数信息的位置mod —。

通过并行 查询的方式搜索余数的最优解:数!、排序位置信息等都在存储单元中保存,控制单元产 生地址值来执行读写存储器的操作,并输出必要的控制信 号来初始化运算模块。

在本设计中,设定信号长度Q 0 223,参数个数〇,采 样通道数(=3,其中,各个通道的采样点分别为—,—, —# —,—,—两两互质且乘积大于信号长度Q ,因此,通过中国余数定理可由—+ — + —个采样点数获取原始信号 所有的信息,降低了幅度以及频率估计时所需的采样点 数。

下面介绍各个主要功能模块的设计。

2.1频率估计!;/m inf $[0,—]丨 YB - —+8B 1,•/ $ [2,Q ](2)8 = 8,b +!;! —m 〇d —"• $ [2,Q ](3)利用C R T 通过8a ,…,8 A 重构时延参数-,幅度估计参数可由公式(F )和(5)得出:{# = re a l ! YB ) I t"=imag ( Y b )丨-= I # + . IS F T 主要部分的F P G A 实现本文考虑使用M A T LA B -S im ulink 工具构建S F T 采样 算法的F P G A 实现架构。

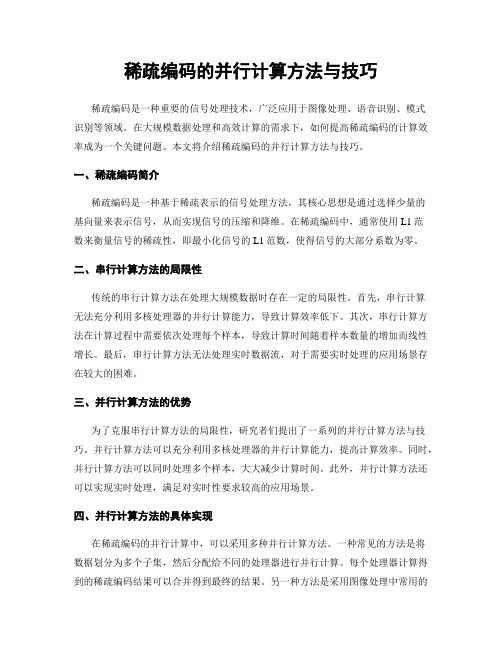

图1展示了当采样通道数Q = 3 时的S FT 并行结构,其主要包括下采样、频率估计、幅度估 计三个部分。

⑷(5)2.1.1最优解模块实现架构频率估计模块的核心部分在于最优解的获得,最优解 实现架构如图2所示。

图中X ! — +8B可由采样样本经过多 路选择器M U X 获得,根据£的取值不同,可以得到多个定 点采样的样点值。

当排序网络为三输入结构时,8b 代表2图1 SFT 的并行架构如图1所示,频率估计与幅度估计共用部分相同的硬 件结构,信号在经过下采样之后,通过F F T 运算得到复数 的输出信号,为了对该复数信号进行排序,将该复数信号 取模后送入排序网络,由于每个通道送入排序网络的点数 不同,排序网络的结构会稍有差异。

在利用C R T 估计信 号的幅度和频率之前,需要对信号进行求余、求最优解等 运算。

其中,最优解运算的核心是排序网络,利用排序网 络的思想求取输入信号的最大值以及获取排序后的信号 在原输入信号中的位置;C R T 模块由一些加法器和乘法器 组成。

输入信号经过多路选择器获得下采样信号,所以该部 分主要研究下采样信号的频率估计以及幅度估计,频率估 计包括最优解模块以及C R T 重构模块。

另外,硬件构成 部门还包含了存储和控制单元,各通道采样因子数—、参置信息数据对—取余 所得的值。

£的取值范 围为0〜—,y = 2,3,其 中当y = 2时,—=4,同样地,有—=5;两种图2最优解模块架构情况下只有£值的变化 导致定点采样的样点值 的变化,而其对应的模 块架构是相同的,所以 这里仅对y = 2时的情 况加以分析。

根据排序网络结 构,需要的输入数据有 两组,一组为需要排序的数据,以便求得最小 值,另外一组则为数据对应的位置信息!。

这样在排序网络求取完最小值后可以直接获取相应的£值 而不需要进行其他的运算处理。

为此,将需要排序的数据 并行导入排序网络的数据输入接口,将对应的位置信息! 值也并行导入排序网络的位置信息接口。

如图3所示,原有输入的3路信号序号为1,2,3。

该 模块实现对这3路信号进行从大到小的排序,并获得排序 后的信号在原序列中的序号,即取位。

图3显示了 3输入 结构的排序图,4输入乃至更多输入结构图原理相同,图 中比较器的输出作为多路选择器的s e l 选择端输入,利用 比较器以及多路选择器的硬件电路连接实现逻辑上的比较选择排序。

B ,1,B 2,B 3为3输入信号经过排序网络的 输出信号,有 B ,1 > B 1,2 > B 1,3。

^1,1_19,、2_19,、3_19分别记录了 ,B# %在原序列中的位置。

同时将位置信息存储到位置信息存储器中。

2.2幅度估计幅度估计中,利用C R T重构模块中获取的频率集合@#,@!分别与)#,)!作求余运算,以此为基础求得Y b,利用前面式(4)和式(5)可求得原始信号的幅度估计。

其中频率集合@#,@!由C R T模块获得,图5中求余的作用为频率集合@#,@分别对采样点数)#,)2作求余运算。

输入序列#、稀疏度值、采样通道数、每个通道的采样点数存储在寄存器中供乘法器调用。

利用排序网络分别求得输入信号实部与虚部的最大值,再对其进行取模则可得到幅度值的估计。

幅度估计的模型如图5所示,其中,排序网络为 4输入结构。

图3排序网络结构(3输入结构)2.1.2 C R T模块架构最优解模块输出一组余数信息的集合,利用中国余数 定理可以轻易地通过一组累加求和运算获取频率集合,进 一步便可获取时延参数-。