数字后端流程二【Astro】

数字后端流程(初学必看)

基本后端流程(漂流&雪拧)----- 2010/7/3---2010/7/8本教程将通过一个8*8的乘法器来进行一个从verilog代码到版图的整个流程(当然只是基本流程,因为真正一个大型的设计不是那么简单就完成的),此教程的目的就是为了让大家尽快了解数字IC设计的大概流程,为以后学习建立一个基础。

此教程只是本人探索实验的结果,并不代表内容都是正确的,只是为了说明大概的流程,里面一定还有很多未完善并且有错误的地方,我在今后的学习当中会对其逐一完善和修正。

此后端流程大致包括一下内容:1.逻辑综合(逻辑综合是干吗的就不用解释了把?)2.设计的形式验证(工具formality)形式验证就是功能验证,主要验证流程中的各个阶段的代码功能是否一致,包括综合前RTL 代码和综合后网表的验证,因为如今IC设计的规模越来越大,如果对门级网表进行动态仿真的话,会花费较长的时间(规模大的话甚至要数星期),这对于一个对时间要求严格(设计周期短)的asic设计来说是不可容忍的,而形式验证只用几小时即可完成一个大型的验证。

另外,因为版图后做了时钟树综合,时钟树的插入意味着进入布图工具的原来的网表已经被修改了,所以有必要验证与原来的网表是逻辑等价的。

3.静态时序分析(STA),某种程度上来说,STA是ASIC设计中最重要的步骤,使用primetime对整个设计布图前的静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。

(PR后也需作signoff的时序分析)4.使用cadence公司的SOCencounter对综合后的网表进行自动布局布线(APR)5.自动布局以后得到具体的延时信息(sdf文件,由寄生RC和互联RC所组成)反标注到网表,再做静态时序分析,与综合类似,静态时序分析是一个迭代的过程,它与芯片布局布线的联系非常紧密,这个操作通常是需要执行许多次才能满足时序需求,如果没违规,则进入下一步。

6.APR后的门级功能仿真(如果需要)7.进行DRC和LVS,如果通过,则进入下一步。

数字后端设计

dbSetGlobalPowerNet "VDD“ dbSetGlobalGroundNet "VSS“ (定义电源环和地环端口,包括VDD,VSS,AVDD,AVSS,DVDD,DVSS)

数字后端有哪些步骤?

1 Setup

auVerilogToCellsetFormField “Verilog To Cell” “Library Name“ $libname

atTimingSetup

(设置时序的要求 由于没有做时钟树插入,仍用理想时钟 ideal clock 优化的方案 寄生参数 单元延迟和线网延迟模型 串扰模型)

数字后端有哪些步骤?

3 Timing 3 执行结束后版图的效果?

只设置了 参数,对 cell的布局 没有影响

ቤተ መጻሕፍቲ ባይዱ 数字后端有哪些步骤?

4 Place 1 这一步主要做什么?

(定义cell中的三组全局电源/地)

axgLoadTDF(加载tdf文件,自己定义,指导pad摆放) astMarkHierAsPreserved(保留层次化信息)

数字后端有哪些步骤?

1 Setup 3 执行结束后版图的效果?

由于只进行了系统的设置, 加载一些文件,setup后在 单元中只能看到一个模拟 的marco

数字后端设计

Reporter: Zizhu.Feng: Date: 2013.06.08

• 三 数 字 和 模 拟 电 路 怎 样 连 接 ?

• 二 数 字 后 端 有 哪 些 步 骤 ?

• 一 什 么 是 数 字 后 端 ?

三 个 问 题

什么是数字后端?

编写 HDL 代码 布局规划

功能仿真 布局

(建库存放单元的数据,导入网表文件,建立版图单元,加载一个.tf文件定义布线的规则)

Astro使用说明(希望对新手有帮助)

Astro使用说明Astro是Synopsys®公司推出的,针对数字电路设计的平台,主要用于对设计进行Floorplan、加Timing Tree、加Power Grid等总体布局上的工作。

其中的大部分软件由被Synopsys®收购的Avanti®开发。

在龙芯组中,Astro主要被用于做Floorplan,通常来说,每个模块的面积、形状、端口及Powergrid等子模块外部信息由一人总体完成,并制成db文件。

各小组成员调用已经生成好的子模块外部信息,在此信息约束下,在子模块内对模块内部进行Floorplan。

对子模块中cell进行布局的一般原则为:对于存储器,一般都制成单独的macro-cell进行布局;对于其他cell是否要单独布局,则由DC中推时钟的结果判断,对于关键路径上的关键器件,根据需要将其fix在一个相对优化的位置。

以下将对龙芯组使用Astro的基本操作做一说明:一、新建library1、新建librarylibrary > Create… ( cmCreateLib )??Technology File Name:/…/csm13_8lm.tf(工艺文件,扩展名为.tf)??Set Case Sensitive 选中(大小写敏感)2、加入reference libraryLibrary > Add Ref…(cmRefLib)??Library Name:test(也可自己取名)??Ref Library Name:依次输入zhaojy/godson2/lib/Astro/logic,zhaojy/godson2/lib/ Astro/pll,zhaojy/godson2/lib/Astro/ram,zhaojy/godson2/lib/Astro/regfile,zhaojy/ godson2/lib/Astro/ict_cells_t。

数字后端流程

数字后端流程1. 数据准备。

对于CDN 的Silicon Ensemble而言后端设计所需的数据主要有是Foundry厂提供的标准单元、宏单元和I/O Pad的库文件,它包括物理库、时序库及网表库,分别以.lef、.tlf和.v的形式给出。

前端的芯片设计经过综合后生成的门级网表,具有时序约束和时钟定义的脚本文件和由此产生的.gcf约束文件以及定义电源Pad的DEF(Desi gn Exchange Format)文件。

(对synopsys 的Astro 而言,经过综合后生成的门级网表,时序约束文件SDC 是一样的,Pad的定义文件--tdf ,.tf 文件--technology file,Foundry厂提供的标准单元、宏单元和I/O Pad的库文件就与FRAM, CELL view, LM view 形式给出(Milkway 参考库and DB, LIB file)2. 布局规划。

主要是标准单元、I/O Pad和宏单元的布局。

I/O Pad预先给出了位置,而宏单元则根据时序要求进行摆放,标准单元则是给出了一定的区域由工具自动摆放。

布局规划后,芯片的大小,Core的面积,Row的形式、电源及地线的Ring和Strip都确定下来了。

如果必要在自动放置标准单元和宏单元之后,你可以先做一次PNA(power netw ork analysis)--IR drop and EM .3. Placement -自动放置标准单元。

布局规划后,宏单元、I/O Pad的位置和放置标准单元的区域都已确定,这些信息SE(Silicon Ensemble)会通过DEF文件传递给PC(Ph ysical Compiler),PC根据由综合给出的.DB文件获得网表和时序约束信息进行自动放置标准单元,同时进行时序检查和单元放置优化。

如果你用的是PC +Astro那你可用write_milkway, read_milkway 传递数据。

数字后端流程二..

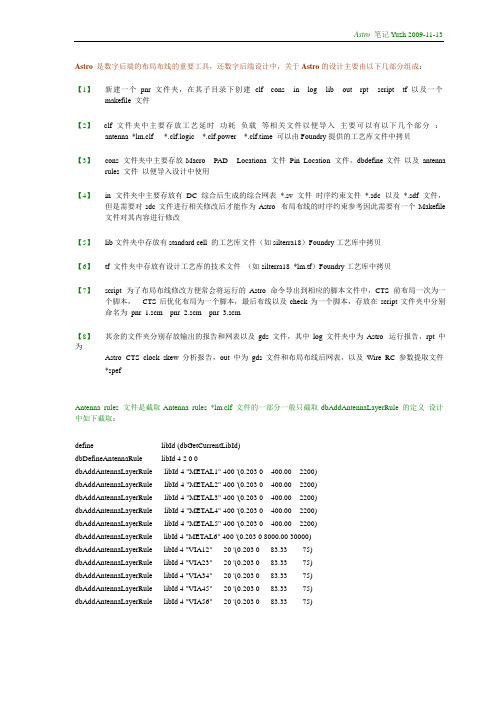

dbAddAntennaLayerRule_libId 4 "VIA12"20 '(0.203 083.3375) dbAddAntennaLayerRule_libId 4 "VIA23"20 '(0.203 083.3375) dbAddAntennaLayerRule_libId 4 "VIA34"20 '(0.203 083.3375) dbAddAntennaLayerRule_libId 4 "VIA45"20 '(0.203 083.3375) dbAddAntennaLayerRule_libId 4 "VIA56"20 '(0.203 083.3375)Astro 笔记Y uzh 2009-11-13Astro 是数字后端的布局布线的重要工具,还数字后端设计中,关于Astro 的设计主要由以下几部分组成:【1】新建一个pnr 文件夹,在其子目录下创建clf cons in log lib out rpt script tf 以及一个makefile 文件【2】clf 文件夹中主要存放工艺延时功耗负载等相关文件以便导入主要可以有以下几个部分:antenna_*lm.clf *.clf.logic *.clf.power *.clf.time 可以由Foundry 提供的工艺库文件中拷贝【3】cons 文件夹中主要存放Macro PAD Locationa 文件Pin Location 文件,dbdefine 文件以及antenna rules 文件以便导入设计中使用【4】in 文件夹中主要存放有DC 综合后生成的综合网表*.sv 文件时序约束文件*.sdc 以及*.sdf 文件,但是需要对sdc 文件进行相关修改后才能作为Astro 布局布线的时序约束参考因此需要有一个Makefile 文件对其内容进行修改【5】lib 文件夹中存放有standard cell 的工艺库文件(如silterra18)Foundry 工艺库中拷贝【6】tf 文件夹中存放有设计工艺库的技术文件(如silterra18_*lm.tf)Foundry 工艺库中拷贝【7】script 为了布局布线修改方便常会将运行的Astro 命令导出到相应的脚本文件中,CTS 前布局一次为一个脚本,CTS 后优化布局为一个脚本,最后布线以及check 为一个脚本,存放在script 文件夹中分别命名为pnr_1.scm pnr_2.scm pnr_3.scm【8】其余的文件夹分别存放输出的报告和网表以及gds 文件,其中log 文件夹中为Astro 运行报告,rpt 中为Astro CTS clock skew 分析报告,out 中为gds 文件和布局布线后网表,以及Wire RC 参数提取文件*spefAntenna_rules 文件是截取Antenna_rules_*lm.clf 文件的一部分一般只截取dbAddAntennaLayerRule 的定义设计中如下截取:define _libId (dbGetCurrentLibId)dbDefineAntennaRule _libId 4 2 0 0dbAddAntennaLayerRule _libId 4 "METAL1" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL2" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL3" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL4" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL5" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL6" 400 '(0.203 0 8000.00 30000)Astro 笔记Y uzh 2009-11-13dbDefine 文件是为了Astro 做时钟树综合优化时作准备的,在CTS 之前需调用该文件,Astro 做时钟树时只对它默认的DFF 的时钟管脚做相关处理一般是定义了clock 但我们设计需要对一些多扇出的复位信号scan 链信号做处理就需要专门声明下这也是时钟树需要处理的信号,就在dbDefine 做这样的声明,一般有同步复位、异步复位、scan_enable 以及宏单元的clk 信号,异步复位最常用需要做scan 链才定义SE,有Memory 时才定义clk,具体设置如下:(let* ((selectedlist (geGetSelectedSet (getEditWindow))))(for-each (lambda (x)(let* ((instName (dbFetchObjectField (geGetEditCell) x "name")))(dbDefineSyncPin (geGetEditCell) instName '( ("RN" "nonInvertRise" 0) ("RN" "invertRise" 0)) )(dbDefineSyncPin (geGetEditCell) instName '( ("SN" "nonInvertRise" 0) ("SN" "invertRise" 0)) );; (dbDefineSyncPin (geGetEditCell) instName '( ("SE" "nonInvertRise" 0) ("SE" "invertRise" 0)) );; (dbDefineSyncPin (geGetEditCell) instName '( ("CLK" "nonInvertRise" 0) ("CLK" "invertRise" 0)) )))selectedlist))tdf 文件定义相关的PAD 或者是PIN 的位置信息,坐标描述方法基本一致设计中根据实际的需要略有不同如下:tdfPurgePadConstrdefine step15define offset50define off0pin "clk"39 0 0"right"0(set! offset(+ step1 offset))pin "rstn"39 0 0"right"0(set! offset(+ step1 offset))pin "scan_mode"39 0 0"right"0(set! offset(+ step1 offset))pin "mic_fm_sel" 39 0 0 "right" 0 (set! offset(+ step1 offset))在Astro 布局布线时需要根据DC 综合时设置生成的时序约束文件对相关cel(l standard cell)进行布局优化,通常在Place 设置时考虑congestion 和time 因素,通常考虑关键性的时序路径,满足设计的时序约束条件,而对于非关键路径的cell 可以放置的远离些,增加延时,如果将非关键路径的cell 布局在关键时序路径布局区域就会对其产生影响,使其布线拥塞增加布线难度。

后端流程整理

后端流程整理目录1。

综合2。

综合后仿真3。

布局布线4。

布线后仿真5。

规则检查6。

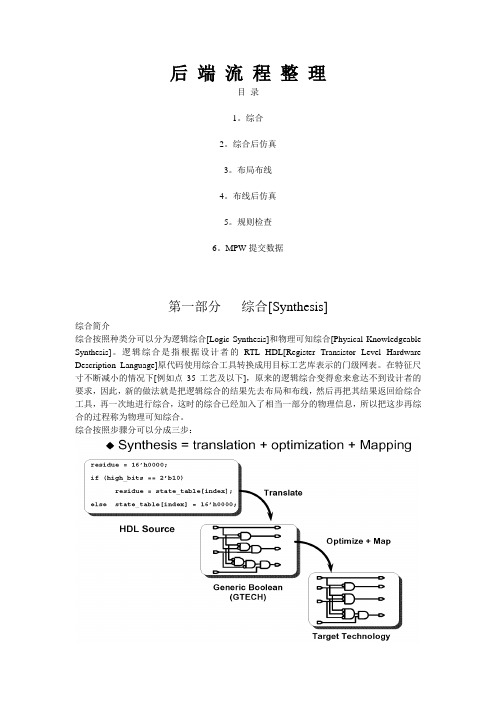

MPW提交数据第一部分综合[Synthesis]综合简介综合按照种类分可以分为逻辑综合[Logic Synthesis]和物理可知综合[Physical Knowledgeable Synthesis]。

逻辑综合是指根据设计者的RTL HDL[Register Transistor Level Hardware Description Language]原代码使用综合工具转换成用目标工艺库表示的门级网表。

在特征尺寸不断减小的情况下[例如点35工艺及以下],原来的逻辑综合变得愈来愈达不到设计者的要求,因此,新的做法就是把逻辑综合的结果先去布局和布线,然后再把其结果返回给综合工具,再一次地进行综合,这时的综合已经加入了相当一部分的物理信息,所以把这步再综合的过程称为物理可知综合。

综合按照步骤分可以分成三步:综合的特点:以时序路径为基础,以约束为准绳的转换过程。

[Timing-path-Based and Constraint-Driven]下面介绍一下综合部分的工作流程以及工具介绍ASIC[Application-Specific Integrated Circuit]领域里面综合工具主要有:Cadence公司的Ambit和新思[Synopsys]公司的Design Compiler,这里主要介绍后者。

使用DC做Verilog 设计的综合工作流程1。

文件和目录准备文件准备:RTL设计描述文件[V erilog HDL]CMOS标准单元库[CSMC06_ver5]在这里顺便介绍一下CMOS标准单元库:CSMC CMOS 06um Standard Cell Library[Version 5.0 复旦大学ASIC国家实验室开发,上海集成电路设计与研究中心版权所有]构成简介CTLF --- Compiled Timing Librarycontains the timing library of all the core and pad cells*.tlf ---text format file*.ctlf ---binary format fileDEF --- Design Exchange Formatcontains the def of power and ground nets*.def --- text formatEXTRACTED_NETcontains SPICE[CDL] netlist of all the core and pad cellsGCF --- General Constraints Formatcontains the location of CTLF filesLEF --- Library Exchange Formatcontains library information for a class of designs.LIB --- Standard core and pad cells database library for DCcontains the function and timing information of cells and its symbol.MAP --- Mapping filescontains the information for matching of layout layer from varies design systems.SE_INI --- Silicon Ensemble Initialization filescontains the setup of some environmental variables in Silicon EnsembleTECHFILE --- Technology Specific Information filescontains the files used to initialize new library in ICFB.VERILOG --- Verilog description of all the core and pad cellsVITAL --- VHDL description of all the core and pad cells工作目录准备2.启动DC启动DC一般有三种方式:图形界面:按回车键,然后跳出主界面:关于界面:然后选择要执行的脚本文件:选择完成以后,DC就自动执行所设定的脚本,完成后显示如下图:选择查看顶层模块:查看其下层电路图:下图是完全去除了层次:随后退出即可。

数字后端版图设计

数字后端设计流程-9 布线

第二步 布线通道分配

在global route 时已经将信号线分配到每个GRC,而track assignment旳 功能就是将这些信号线在分配到每个track上,决定每条线要走旳途径。 Track assignment是以整个芯片为处理单位来作规划,尽量绕出又长又 直且via数目至少旳绕线。

Formal Verification (ECO Netlist vs

CT Inserted Netlist)

Post-layout STA

Power check

Timing OK? Yes

Tape Out

DC MODELSIM MBISTARCHITECT FORMALITY

PT

Astro AstroRail FORMALITY

数字后端设计流程-5 布局

一般来说cell面积旳拥有率控制在70%左右, 布线旳时候不会引起拥塞。

数字后端设计流程-5 时钟树和复位树综合

时钟树综合旳目旳: 低skew 低clock latency

数字后端设计流程-5 时钟树和复位树综合

芯片中旳时钟网络要驱动电路中全部旳时序单元,所以 时钟源端门单元带载诸多,其负载延时很大而且不平衡, 需要插入缓冲器减小负载和平衡延时。时钟网络及其上 旳缓冲器构成了时钟树。一般要反复几次才能够做出一 种比较理想旳时钟树。

布线工具会自动进行布线拥塞消除、优化时序、减 小耦合效应、消除串扰、降低功耗、确保信号完整性等 问题。

数字后端流程(初学必看)

基本后端流程(漂流&雪拧)----- 2010/7/3---2010/7/8本教程将通过一个8*8的乘法器来进行一个从verilog代码到版图的整个流程(当然只是基本流程,因为真正一个大型的设计不是那么简单就完成的),此教程的目的就是为了让大家尽快了解数字IC设计的大概流程,为以后学习建立一个基础。

此教程只是本人探索实验的结果,并不代表内容都是正确的,只是为了说明大概的流程,里面一定还有很多未完善并且有错误的地方,我在今后的学习当中会对其逐一完善和修正。

此后端流程大致包括一下内容:1.逻辑综合(逻辑综合是干吗的就不用解释了把?)2.设计的形式验证(工具formality)形式验证就是功能验证,主要验证流程中的各个阶段的代码功能是否一致,包括综合前RTL 代码和综合后网表的验证,因为如今IC设计的规模越来越大,如果对门级网表进行动态仿真的话,会花费较长的时间(规模大的话甚至要数星期),这对于一个对时间要求严格(设计周期短)的asic设计来说是不可容忍的,而形式验证只用几小时即可完成一个大型的验证。

另外,因为版图后做了时钟树综合,时钟树的插入意味着进入布图工具的原来的网表已经被修改了,所以有必要验证与原来的网表是逻辑等价的。

3.静态时序分析(STA),某种程度上来说,STA是ASIC设计中最重要的步骤,使用primetime对整个设计布图前的静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。

(PR后也需作signoff的时序分析)4.使用cadence公司的SOCencounter对综合后的网表进行自动布局布线(APR)5.自动布局以后得到具体的延时信息(sdf文件,由寄生RC和互联RC所组成)反标注到网表,再做静态时序分析,与综合类似,静态时序分析是一个迭代的过程,它与芯片布局布线的联系非常紧密,这个操作通常是需要执行许多次才能满足时序需求,如果没违规,则进入下一步。

6.APR后的门级功能仿真(如果需要)7.进行DRC和LVS,如果通过,则进入下一步。

数字后端流程二【astro】[精华]

![数字后端流程二【astro】[精华]](https://img.taocdn.com/s3/m/cc2e23d9a0c7aa00b52acfc789eb172ded639939.png)

Astro 笔记Y uzh 2009-11-13Astro 是数字后端的布局布线的重要工具,还数字后端设计中,关于Astro 的设计主要由以下几部分组成:【1】新建一个pnr 文件夹,在其子目录下创建clf cons in log lib out rpt script tf 以及一个makefile 文件【2】clf 文件夹中主要存放工艺延时功耗负载等相关文件以便导入主要可以有以下几个部分:antenna_*lm.clf *.clf.logic *.clf.power *.clf.time 可以由Foundry 提供的工艺库文件中拷贝【3】cons 文件夹中主要存放Macro PAD Locationa 文件Pin Location 文件,dbdefine 文件以及antenna rules 文件以便导入设计中使用【4】in 文件夹中主要存放有DC 综合后生成的综合网表*.sv 文件时序约束文件*.sdc 以及*.sdf 文件,但是需要对sdc 文件进行相关修改后才能作为Astro 布局布线的时序约束参考因此需要有一个Makefile 文件对其内容进行修改【5】lib 文件夹中存放有standard cell 的工艺库文件(如silterra18)Foundry 工艺库中拷贝【6】tf 文件夹中存放有设计工艺库的技术文件(如silterra18_*lm.tf)Foundry 工艺库中拷贝【7】script 为了布局布线修改方便常会将运行的Astro 命令导出到相应的脚本文件中,CTS 前布局一次为一个脚本,CTS 后优化布局为一个脚本,最后布线以及check 为一个脚本,存放在script 文件夹中分别命名为pnr_1.scm pnr_2.scm pnr_3.scm【8】其余的文件夹分别存放输出的报告和网表以及gds 文件,其中log 文件夹中为Astro 运行报告,rpt 中为Astro CTS clock skew 分析报告,out 中为gds 文件和布局布线后网表,以及Wire RC 参数提取文件*spefAntenna_rules 文件是截取Antenna_rules_*lm.clf 文件的一部分一般只截取dbAddAntennaLayerRule 的定义设计中如下截取:define _libId (dbGetCurrentLibId)dbDefineAntennaRule _libId 4 2 0 0dbAddAntennaLayerRule _libId 4 "METAL1" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL2" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL3" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL4" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL5" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL6" 400 '(0.203 0 8000.00 30000)dbAddAntennaLayerRule_libId 4 "VIA12"20 '(0.203 083.3375)dbAddAntennaLayerRule_libId 4 "VIA23"20 '(0.203 083.3375)dbAddAntennaLayerRule_libId 4 "VIA34"20 '(0.203 083.3375)dbAddAntennaLayerRule_libId 4 "VIA45"20 '(0.203 083.3375)dbAddAntennaLayerRule_libId 4 "VIA56"20 '(0.203 083.3375)dbDefine 文件是为了Astro 做时钟树综合优化时作准备的,在CTS 之前需调用该文件,Astro 做时钟树时只对它默认的DFF 的时钟管脚做相关处理一般是定义了clock 但我们设计需要对一些多扇出的复位信号scan 链信号做处理就需要专门声明下这也是时钟树需要处理的信号,就在dbDefine 做这样的声明,一般有同步复位、异步复位、scan_enable 以及宏单元的clk 信号,异步复位最常用需要做scan 链才定义SE,有Memory 时才定义clk,具体设置如下:(let* ((selectedlist (geGetSelectedSet (getEditWindow))))(for-each (lambda (x)(let* ((instName (dbFetchObjectField (geGetEditCell) x "name")))(dbDefineSyncPin (geGetEditCell) instName '( ("RN" "nonInvertRise" 0) ("RN" "invertRise" 0)) )(dbDefineSyncPin (geGetEditCell) instName '( ("SN" "nonInvertRise" 0) ("SN" "invertRise" 0)) );; (dbDefineSyncPin (geGetEditCell) instName '( ("SE" "nonInvertRise" 0) ("SE" "invertRise" 0)) );; (dbDefineSyncPin (geGetEditCell) instName '( ("CLK" "nonInvertRise" 0) ("CLK" "invertRise" 0)) )))selectedlist))tdf 文件定义相关的PAD 或者是PIN 的位置信息,坐标描述方法基本一致设计中根据实际的需要略有不同如下:tdfPurgePadConstrdefine step15define offset50define off0pin "clk"39 0 0"right"0(set! offset(+ step1 offset))pin "rstn"39 0 0"right"0(set! offset(+ step1 offset))pin "scan_mode"39 0 0"right"0(set! offset(+ step1 offset))pin "mic_fm_sel" 39 0 0 "right" 0 (set! offset(+ step1 offset))在Astro 布局布线时需要根据DC 综合时设置生成的时序约束文件对相关cel(l standard cell)进行布局优化,通常在Place 设置时考虑congestion 和time 因素,通常考虑关键性的时序路径,满足设计的时序约束条件,而对于非关键路径的cell 可以放置的远离些,增加延时,如果将非关键路径的cell 布局在关键时序路径布局区域就会对其产生影响,使其布线拥塞增加布线难度。

数字后端中解fanout的方法-概述说明以及解释

数字后端中解fanout的方法-概述说明以及解释1.引言1.1 概述数字后端中解fanout的方法是一篇关于解决fanout问题的长文。

fanout是一种常见的技术需求,在数字后端应用中广泛存在。

本文将探讨不同的解决方法,以帮助读者更好地理解并解决fanout问题。

在本文中,我们将分析fanout问题的定义和背景,并提出四种解决方法。

这四种方法分别是使用消息队列、使用分布式计算框架、使用缓存和使用并行处理。

每种方法都有其独特的优点和缺点,我们将在正文中详细讨论它们。

通过本文的阅读,读者将了解到不同解决方法的原理和适用场景,并能够根据具体业务需求选择最合适的解决方案。

我们还将对这些方法的优缺点进行总结,并探讨未来的发展方向。

本文旨在帮助读者更全面地了解数字后端中解决fanout问题的方法,为他们在实际应用中提供指导和帮助。

无论是对于正在面临fanout问题的工程师,还是对于对数字后端技术感兴趣的读者,本文都有着重要的参考价值。

接下来,我们将详细介绍fanout问题的定义和背景,以便读者能够更好地理解该问题的重要性和实际需求。

1.2 文章结构文章结构部分的内容主要是对整篇文章的结构进行介绍和概括,可以包括以下几个方面的内容:文章结构是指文章的整体框架和组成部分,在本篇论文中,主要分为引言、正文和结论三个部分。

引言部分(Introduction)主要包括概述、文章结构和目的。

概述部分介绍了数字后端中解fanout的问题和背景,引起读者对该问题的兴趣。

接着,在文章结构部分,概括性地介绍了文章的整体框架和各个部分的内容,为读者提供了整体的导读。

最后,明确了本文的目的,即从几个不同的角度探讨解决fanout问题的方法。

正文部分(Main Body)是文章的核心内容,包括了解fanout的定义和背景以及具体的解决方法。

在这一部分,将会阐述几种解决fanout 问题的方法,包括使用消息队列、使用分布式计算框架、使用缓存和使用并行处理。

数字后端流程简述

HDL代码

逻辑综合

形式验证

布局布线

形式验证

综合的定义

逻辑综合:决定设计电路逻辑门之间的相互连接。 逻辑综合的目的:决定电路门级结构,寻求时序、面积和功耗的平衡, 增强电路的测试性。 逻辑综合的过程(constraint_driven) : Synthesis = Translation + Logic Optimization + Mapping 首先,DC分析HDL代码,用一种模型(GTECH) ,对HDL进行映 射,这个模型是与技术库无关的,也不包含Timing和Load信息; 然后,在设计者的控制下,对这个模型进行逻辑优化; 最后一步,进行逻辑映射和门级优化,将逻辑根据约束条件,映射 为专门的技术目标单元库(target cell library)中的单元,形成了综合后 的网表。

DC时钟约束命令: create_clock:用于定义时钟的周期和波形(占空比及起始沿) 例如: create_clock -period 40 -waveform{0 20} 对于仅包含组合逻辑的模块,为了定义该模块的延时约束,可以创造一个虚 拟时钟定义。 例如: create_clock -period 20 -name V_clk

对于以下两个约束最好在时序做不下去时再用,平时尽量少用。 set_max_delay: 1、对于仅包含组合逻辑的模块,用此命令约束所有输入到输出 的总延时。 例如: set_max_delay 5 -from all_inputs() -to all_outputs 2、对于含有多个时钟的模块,可用通常的方法定义一个时钟, 用此命令进行约束定义时钟和其他时钟之间的关系。 例如:set_max_delay 0 –from CLK2 \ –to all_register(clock_pin) set_min_delay: 1、对于仅包含组合逻辑的模块,定义指定路径的最小延时。 例如:set_min_delay 3 -from all_inputs() 2、和set_fix_hold一起使用,只是DC添加一定的延迟,满足最 小延迟需求。

astro集成电路后端设计流程

导入SDC文件

• Timing--Constraints: Load SDC

(ataLoadSDC) • SDC (Synopsys Design Constraints)设计约束条件

Timing Setup(1)[选择寄生模型]

• Timing--AstroTime: Timing Setup • 选择TLU+寄生模型

门级网表是从哪来的?

• 门级网表通常是

Design Conpiler 这类综合工具产 生的。 • 这类逻辑综合工 具“综合”了 RTL (register transfer level) code,使它转换 成门级网表,并 在设计约束下使 其速度和尺寸最 优化。

前端提供的文件

• 综合后的门级的verilog文件 • 时序文件(SDC) • PAD放置信息文件(TDF) • 库转换文件(DEF)

连接电源地的macro端口和pad到环上

• PreRoute Macros/Pads • 这个步骤可以把macro的电源 地端口和电源地pad连到最近的 电源地环上

ASTRO流程[Placement]

Placemet Stag

•

Placemeng的目的就是以容易饶线为目标将元件摆放至core area,并达到时 序上的需求. 解决时序问题的方法有两种:一种是timing driven placement,利用cell moving方式尽量将关键途径上的元件摆放在一起以降低元件与元件之间相 互连接的延迟;另一种为placement optimization,包括cell bypassing cell resizing,buffer/inverter insertion等 如果电路中包括scan chain(扫描链),建议在进行placement之前,打断其 连接,在clock tree synthesis(CTS)之后再重新连接,这样饶线会比较容易。 Scan chain将所有的连续的一个个pin脚按顺序串起来,假设在placement 时没有按照其顺序摆放,那么饶线是非常困难的。但是在placement时就 最佳化摆放位置,会浪费非常多的执行时间,并且有可能无法对时序做最 佳化。因此,在placement之前必须将scan chain拿掉,等到CTS后再重新 连接起来,并且其连接的顺序会和打断前不同。

数字集成电路 后端设计 APR流程 之Astro

Astro布局布线流程随着深亚微米工艺的应用,逻辑门间的连线主导了电路的时序性能。

在实际设计时,设计者不再只是完成简单的逻辑门摆放和连线工作,更重要的是要降低实际的连线延迟,使最后的物理设计时序性能满足设计要求。

Astro是由Synopsys公司开发的物理设计软件,适用于现在的主流设计。

Astro提供了一套完整的物理设计流程,布局布线同时还具有时序优化功能,可以在一次流程中使设计电路达到预设指标。

但Astro步骤繁多、设定复杂,本章将针对Astro的设计流程借助一个简单的设计实例,对Astro一次流程中的主要步骤进行简单说明,使读者短时间内可以了解Astro。

一.数据准备本流程中需要的输入数据包括:网表文件(Netlist File)、时序约束SDC文件(Timing Constraint File)、参考库(Reference Library)、定义PAD TDF文件(Top Design File)、工艺tf文件(Technology File)。

其中工艺文件和部分参考库文件由Foundry提供。

1.网表:网表文件由前端工程师提供,格式一般采用verilog(.v)格式。

布局布线用网表文件一般由Design Compiler(DC)综合得到。

从DC中输出网表时,需要在脚本中如下命令,以满足Astro的要求。

2.时序约束文件:时序约束文件由前端工程师提供,格式一般采用SDC(.sdc)格式,SDC文件也由DC中输出。

时序约束文件中所加的约束只能针对顶层端口,文件中时钟定义可能需要加以修改。

因为从DC中输出的时钟定义一般不指定具体的单元及其端口,Astro通常很难根据这样的时钟定义找到真正的时钟源,因此需要先在网表中找到真正的时钟端口,并据此在SDC文件中加以修改。

例如,原来的SDC文件中时钟的定义片段为:原来的时序约束文件是给予综合的DC用,而不是用来布局布线的。

所以综合用的SDC文件中只给出了一个“产生时钟(create clock)”的命令,根据上面这段时序约束文件中的片段,Astro一般无法找到clk_div/clk,因此需要将“get_pin”的目标修改替换为在网表中的一个实际的时钟产生的单元:clk_div/CK01D1/Z.。

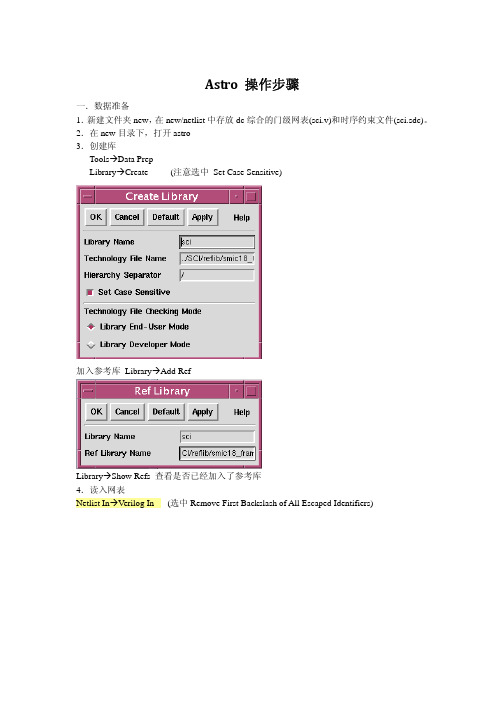

Astro 操作步骤

Astro 操作步骤一.数据准备1.新建文件夹new,在new/netlist中存放dc综合的门级网表(sci.v)和时序约束文件(sci.sdc)。

2.在new目录下,打开astro3.创建库ToolsÆData PrepLibraryÆCreate (注意选中Set Case Sensitive)加入参考库 LibraryÆAdd RefLibraryÆShow Refs 查看是否已经加入了参考库4.读入网表Netlist InÆVerilog In (选中Remove First Backslash of All Escaped Identifiers)扩展顶层 Netlist InÆExpand (注意Unexpanded Cell Name要与sci/NETL文件夹中的顶层文件名相同)选中右上方的Global Net Options (填完后点Apply)绑定网表先打开库 LibraryÆOpenCellÆCreateDesign SetupÆBind Netlist将单元另存为 CellÆSave As5.全局电源/地的连接先回到Astro环境 ToolsÆAstroPreRouteÆConnect Ports to P/G (由于本次做的单元不需要画Pad,因此不需要选中Pad项;选中Update Tie Up/Down)CellÆInitialize Hierarchy Preservation二.整体布局1.Load TDF文件TimingÆLoad TDF (因为不需要Pad,因此是pin.tdf,而不是pad.tdf)2.设置布局Design SetupÆSet up Floorplan按照上面的表填好后,点set可以看到core的宽度和高度,再点OKCellÆSave As3.预布线放置电源环 PreRouteÆRectangular Rings (Net Name中填VDD,VSS)这块电路很小,因此不需要再放置电源条///////////////////////////////////////这步可以放在Timing Setup之后////////////////////////// 4.放置标准单元InPlaceÆPlacement Common OptionsPrePlaceÆPre-Placement OptimizationInPlaceÆDesign Placement//////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////// 三.时钟树综合1.Load 时序约束文件(SDC)在读入新的SDC文件之前,要将原有的约束去掉 ataRemoveTCTimingÆLoad SDCTimingÆTiming Data Check (存到Reports文件夹)(确定SDC文件能完全约束电路)2.Timing SetupTimingÆTiming SetupEnviroment中选中Ignore Propagated Clock和Include Non Propagated NetsParasitics (Operation Cond选中Max和Min,将Temperature中的Min设为0,Max设为100)Model (将Net Delay Model设为Elmore)TimingÆTiming ReportInPlaceÆPlacement Common Options 在Optimization Mode中选中TimingPrePlaceÆPre-Placement OptimizationInPlaceÆDesign PlacementastCheckDesignPostPlaceÆPost-Placement Optimization Phase 1astCheckDesignClockÆClock Common Options在Clock Nets项点Search出现右边的对话框,点右上角Show Root Clock Nets,选中SCLK,点OK,左边框中会出现SCLK。

数字IC后端设计流程

ASIC/SoC后端设计作业流程剖析关键词place route DSM megacell clock_tree STA OPT ECO引言众所周知,ASIC产品是从用硬件描述语言(verilog HDL,VHDL)开始进行数字逻辑电路设计的,经过相关的仿真、综合出门级网表、验证直至完成电路布局布线并优化,最终经流片成功形成的芯片产品。

随着中国经济的持续稳定地增长,国内生产厂家对IC需求增长势头强劲与自身设计IC能力薄弱的突出矛盾已经被国家和企业认识。

为了缓解这一矛盾并更多地实现IC自主设计,近两年国内陆续出现了一些著名的传统通信系统厂商设立的IC设计队伍,以及归国留学人员领头创办的创业型IC设计公司,他们大多数有相当强的前端设计能力,但在IC后端设计领域的实践经验还较欠缺。

在完成前端逻辑设计综合出门级网表后,真正能做好后端设计的公司还不多,有的则通过委托设计服务的方式完成后端布局布线及流片。

本文作者有多年从事覆盖前后端IC设计全流程并有每年几次成功流片数百万门级深亚微米SoC 的经验,并担任IC设计的项目管理工作,对国外大公司的设计流程十分熟悉,并愿意就积累的经验与国内同行分享交流,以利于国内IC设计水平的提高。

本文着重介绍国内设计公司薄弱的后端设计,介绍其流程并对在设计过程中的关键步骤进行一些讨论。

传统的后端设计流程指的是从门级网表(gate level netlist)开始的,根据设计要求的不同,后端流程可以分为扁平流程(flat flow)和层次化流程(hierarchy flow)两种,在深亚微米DSM(deep sub-micron)领域,又增加了布局加逻辑合成的前后端合二为一的扁平流程(flat flow)和分层流程(hierarchy flow)。

我们首先介绍传统的两种后端流程。

前后端合一的流程将作为另一个专题在以后讨论。

一、扁平流程(Flat flow)介绍最简单的后端设计是扁平(flat)流程,一般四百万门以下的设计均可使用这一流程。

Astro过程1

Astro过程1、产生Milkyway的参考库1). Astro输入的数据文件:●技术文件(.tf)●参考库(参考库由以下的文件产生:1、技术文件(.tf);2、GDSII文件(包含了物理版图信息);3、综合库文件(.lib or .db 包含了cell的时序和功能))●设计库(Design_library),由以下文件产生:1、技术文件(.tf);2、GDSII文件(.gds 包含了物理版图信息);3、顶层设计文件(.tdf)包含了pin和port的信息。

4、约束文件(.sdc 包含了时序约束和时钟的定义,来自于综合过程);5、网表文件(.v or .vhd or .edf)包含V erilog、VHDL或者EDIF文件;6、设计库文件(.db)包含了网表,时序和设计规则约束。

2). Astro产生的数据文件●布局后产生的时序文件(design.sdf)●寄生信息(parasitic.spef or parasitic.spf)●优化过后的网表(.v(flattened)or .hv(hierarchical))●Layout文件(.gds)●(optional)cell 放置位置信息(.pdef)●(optional)网表和布局信息(.def)●(optional)版图、时序和技术信息3)Milyway 库目录Synopsys的Milyway 库目录是目录和文件的集合。

顶层目录是参考库或着是设计库。

参考库包含标准单元库、宏库和引脚库,这几个库构成一个设计。

1)数据库●CEL view:版图物理单元数据,包含输入的和astro产生的;●FRAM:版图数据提取出的布局布线数据;●SMASH:打平的CEL view;●HTV:版图的层次化时序数据,类似于和其它synopsys工具的一个接口;2)时序、功耗和逻辑文件夹●LM(Logic Model)view:时序,功耗和逻辑信息(新的格式提供了类似于TIM和PWR的数据信息)。

数字IC设计——整理

数字集成电路设计整理一、概念1. ASIC——Application Specific Integrated Circuit专用集成电路ASIC在批量生产时与通用集成电路(IC)相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

ASIC分为全定制和半定制。

全定制设计需要设计者完成所有电路的设计,半定制使用库里的标准逻辑单元(Standard Cell),设计时可以从标准逻辑单元库中选择SSI(门电路)、MSI(如加法器、比较器等)、数据通路(如ALU、存储器、总线等)、存储器甚至系统级模块(如乘法器、微控制器等)和IP核,这些逻辑单元已经布局完毕,而且设计得较为可靠,设计者可以较方便地完成系统设计。

全定制能够比半定制的ASIC芯片运行速度更快。

2.IP——Intellectual Property知识产权3.数字后端指将前端设计产生的门级网表通过EDA设计工具进行布局布线和进行物理验证并最终产生供制造用的GDSII数据的过程。

其主要工作职责有:芯片物理结构分析、逻辑分析、建立后端设计流程、版图布局布线、版图编辑、版图物理验证、联络代工厂并提交生产数据。

作为连接设计与制造的桥梁,合格的版图设计人员既要懂得IC 设计、版图设计方面的专业知识,还要熟悉制程厂的工作流程、制程原理等相关知识。

4.Standard Cell——标准单元库5.RTL——寄存器传输级描述通过一个寄存器到另一个寄存器的逻辑变换和传输来描述设计。

逻辑值被存储在寄存器中,通过一些组合逻辑对其要求值,随后将结果存储于下一个寄存器。

RTL的功能类似于软件与硬件之间的桥梁。

是与工艺无关的网表的文本结构描述。

6.布局(Place)布线(Route)布图规划floorplan比布局更重要。

规划包括指令,macro的放置,电源线的设计power plan。

floorplan一旦确定,芯片的面积就定下来了,也与整个设计的timming和布通率有很大关系。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

dbAddAntennaLayerRule_libId 4 "VIA12"20 '(0.203 083.3375) dbAddAntennaLayerRule_libId 4 "VIA23"20 '(0.203 083.3375) dbAddAntennaLayerRule_libId 4 "VIA34"20 '(0.203 083.3375) dbAddAntennaLayerRule_libId 4 "VIA45"20 '(0.203 083.3375) dbAddAntennaLayerRule_libId 4 "VIA56"20 '(0.203 083.3375)Astro 笔记Y uzh 2009-11-13Astro 是数字后端的布局布线的重要工具,还数字后端设计中,关于Astro 的设计主要由以下几部分组成:【1】新建一个pnr 文件夹,在其子目录下创建clf cons in log lib out rpt script tf 以及一个makefile 文件【2】clf 文件夹中主要存放工艺延时功耗负载等相关文件以便导入主要可以有以下几个部分:antenna_*lm.clf *.clf.logic *.clf.power *.clf.time 可以由Foundry 提供的工艺库文件中拷贝【3】cons 文件夹中主要存放Macro PAD Locationa 文件Pin Location 文件,dbdefine 文件以及antenna rules 文件以便导入设计中使用【4】in 文件夹中主要存放有DC 综合后生成的综合网表*.sv 文件时序约束文件*.sdc 以及*.sdf 文件,但是需要对sdc 文件进行相关修改后才能作为Astro 布局布线的时序约束参考因此需要有一个Makefile 文件对其内容进行修改【5】lib 文件夹中存放有standard cell 的工艺库文件(如silterra18)Foundry 工艺库中拷贝【6】tf 文件夹中存放有设计工艺库的技术文件(如silterra18_*lm.tf)Foundry 工艺库中拷贝【7】script 为了布局布线修改方便常会将运行的Astro 命令导出到相应的脚本文件中,CTS 前布局一次为一个脚本,CTS 后优化布局为一个脚本,最后布线以及check 为一个脚本,存放在script 文件夹中分别命名为pnr_1.scm pnr_2.scm pnr_3.scm【8】其余的文件夹分别存放输出的报告和网表以及gds 文件,其中log 文件夹中为Astro 运行报告,rpt 中为Astro CTS clock skew 分析报告,out 中为gds 文件和布局布线后网表,以及Wire RC 参数提取文件*spefAntenna_rules 文件是截取Antenna_rules_*lm.clf 文件的一部分一般只截取dbAddAntennaLayerRule 的定义设计中如下截取:define _libId (dbGetCurrentLibId)dbDefineAntennaRule _libId 4 2 0 0dbAddAntennaLayerRule _libId 4 "METAL1" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL2" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL3" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL4" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL5" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL6" 400 '(0.203 0 8000.00 30000)dbDefine 文件是为了Astro 做时钟树综合优化时作准备的,在CTS 之前需调用该文件,Astro 做时钟树时只对它默认的DFF 的时钟管脚做相关处理一般是定义了clock 但我们设计需要对一些多扇出的复位信号scan 链信号做处理就需要专门声明下这也是时钟树需要处理的信号,就在dbDefine 做这样的声明,一般有同步复位、异步复位、scan_enable 以及宏单元的clk 信号,异步复位最常用需要做scan 链才定义SE,有Memory 时才定义clk,具体设置如下:(let* ((selectedlist (geGetSelectedSet (getEditWindow))))(for-each (lambda (x)(let* ((instName (dbFetchObjectField (geGetEditCell) x "name")))(dbDefineSyncPin (geGetEditCell) instName '( ("RN" "nonInvertRise" 0) ("RN" "invertRise" 0)) )(dbDefineSyncPin (geGetEditCell) instName '( ("SN" "nonInvertRise" 0) ("SN" "invertRise" 0)) );; (dbDefineSyncPin (geGetEditCell) instName '( ("SE" "nonInvertRise" 0) ("SE" "invertRise" 0)) );; (dbDefineSyncPin (geGetEditCell) instName '( ("CLK" "nonInvertRise" 0) ("CLK" "invertRise" 0)) )))selectedlist))tdf 文件定义相关的PAD 或者是PIN 的位置信息,坐标描述方法基本一致设计中根据实际的需要略有不同如下:tdfPurgePadConstrdefine step15define offset50define off0pin "clk"39 0 0"right"0(set! offset(+ step1 offset))pin "rstn"39 0 0"right"0(set! offset(+ step1 offset))pin "scan_mode"39 0 0"right"0(set! offset(+ step1 offset))pin "mic_fm_sel" 39 0 0 "right" 0 (set! offset(+ step1 offset))在Astro 布局布线时需要根据DC 综合时设置生成的时序约束文件对相关cel(l standard cell)进行布局优化,通常在Place 设置时考虑congestion 和time 因素,通常考虑关键性的时序路径,满足设计的时序约束条件,而对于非关键路径的cell 可以放置的远离些,增加延时,如果将非关键路径的cell 布局在关键时序路径布局区域就会对其产生影响,使其布线拥塞增加布线难度。

而对于DC 生成的时序约束文件并不是直接就是导入使用,DC 中估算连线延时采用wire_load_model 的方法估算,但在Astro 中我们实际对cell 进行布线直接提取wire 连线的RC 信息计算net delay 更为精确接近实际设计,同时对各个时钟的uncertainty 的定义也不需要了,CTS 后各个时钟负载和延时可以达到最佳平衡uncertainty 只由jitter 引起,虽然还是会存在skew (几乎可以忽略),latency 主要有 2 部分组成source_latency 和network_latency 一般设计只考虑network_latency ,Astro 不需要设置network_latency ,CTS 后各个DFF 的network_latency 的基本平衡了。

具体脚本如下:#!/bin/bash#echo "Enter the file name(<file>.sdc)"filename = ADPCM_Encoderrun:#read $(filename)cp $(filename).sdc $(filename).sdc.bakecho ":%s/set_wire_load_model/#set_wire_load_model/g" > $(filename).vimrcecho ":%s/-dont_scale//g" >> $(filename).vimrcecho ":%s/set_isolate_ports/#set_isolate_ports/g" >> $(filename).vimrcecho ":%s/set_clock_latency/#set_clock_latency/g" >> $(filename).vimrcecho ":%s/set_clock_uncertainty/#set_clock_uncertainty/g" >> $(filename).vimrcecho ":w!" >> $(filename).vimrcvim -e -s $(filename).sdc < $(filename).vimrcrm $(filename).vimrcAstro 布局布线主要流程*******************************************************************************************pnr1.scm CTS 之前布局布线以及优化设置*******************************************************************************************【1】设置db 库总线名称属性类型dbSetLibBusNameS tyle “ lib/silter ra18”“[%d]”【2】导入相关db 文件到工艺库文件1. Choose Tools > DataPrep2.Choose Cell Library > Library Preparation3.Click the Prepare Logical Librarybutton 4.Click the LIB/DB buttongePrepLibssetFormField "Library Preparation" "Library Name" "lib/silterra18"formButton "Library Preparation" "importLMDB"formButton "Library Preparation" "selectDB"setFormField "Library Preparation" "Min DB To Import" "../dc/lib_syn/db/slow.db"setFormField "Library Preparation" "Max DB To Import" "../dc/lib_syn/db/fast.db"formOK "Library Preparation"【3】根据设计层次导入库技术文件*.tfTech File > ReplacecmReplaceTechsetFormField "Replace Technology File" "Library Name" "lib/silterra18"setFormField "Replace Technology File" "Technology File Name" "tf/silterra18_6lm.tf"formOK "Replace Technology File"【4】读入DC 综合的网表根据设计约束对照LIB 库进行cell 的映射,此类映射方法有2 种。