上菲红:Cursor 9胜在性能良好

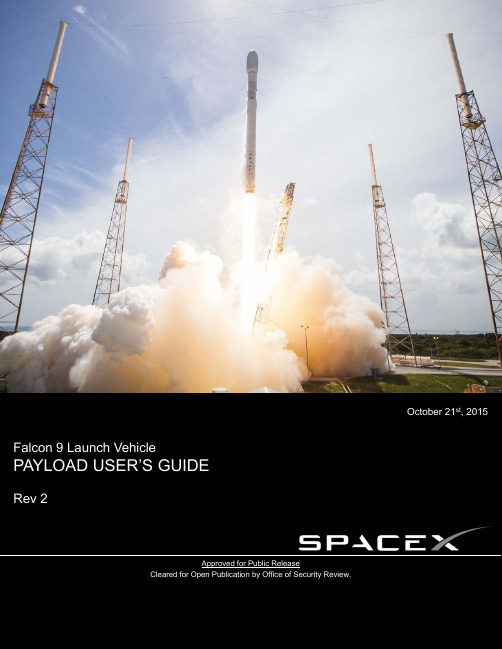

猎鹰9号火箭用户指南falcon9 usersguide rev 2.0

4.

5.

Revision 2

© 2015 Space Exploration Technologies Corp. All rights reserved.

2

Falcon User’s Guide 5.2 Electrical Interfaces 5.2.1 Connectivity during Payload Processing and on Launch Pad 5.2.2 Falcon-to-Payload Command Interface 5.2.3 Timing Services Interface Compatibility Verification Requirements 37 37 39 40 40 41 41 41 43 44 46 47 47 48 48 48 49 50 51 53 53 53 54 57 58 58 59 59 60 60 60 61 61 61 61 61 61 62 6TABLE OF CONTENTS

1. Introduction 1.1 User’s Guide Purpose 1.2 Company Description 1.3 Falcon Program Overview 1.4 Falcon Launch Vehicle Safety 1.5 Falcon Reliability 1.6 Pricing Vehicles 2.1 2.2 2.3 2.4 2.5 Falcon 9 Vehicle Overview Structure and Propulsion Retention, Release and Separation Systems Avionics, and Guidance, Navigation and Control Coordinate Frame 5 5 5 6 6 7 9 10 10 10 12 12 12 14 14 14 15 16 16 16 16 17 17 18 18 18 19 19 21 23 26 27 30 31 32 32 34 34 34 36

IEEE 1394 火线接口的设计

``FWDG 1.0TA03/02/2010 FireWire Design GuideAbstract: Guidelines for implementing FireWire (IEEE 1394) ports on both high level complex devices such as personal computers and simple devices such as inexpensive consumer electronics products. Includes references to normative specifi-cations as well as full reference designs that can be used as is or, with the careful consideration of the trade-offs, as a starting point for a more optimized design.FireWire Design Guide FWDG 1.0TA03/02/2010 1394 Trade Association Specifications are developed within Working Groups of the 1394 TradeAssociation, a non-profit industry association devoted to the promotion of and growth of the market forIEEE 1394-compliant products. Participants in Working Groups serve voluntarily and withoutcompensation from the Trade Association. Most participants represent member organizations of the 1394Trade Association. The specifications developed within the working groups represent a consensus of theexpertise represented by the participants.Use of a 1394 Trade Association Specification is wholly voluntary. The existence of a 1394 TradeAssociation Specification is not meant to imply that there are not other ways to produce, test, measure,purchase, market or provide other goods and services related to the scope of the 1394 Trade AssociationSpecification. Furthermore, the viewpoint expressed at the time a specification is accepted and issued issubject to change brought about through developments in the state of the art and comments received fromusers of the specification. Users are cautioned to check to determine that they have the latest revision of any1394 Trade Association Specification.Comments for revision of 1394 Trade Association Specifications are welcome from any interested party,regardless of membership affiliation with the 1394 Trade Association. Suggestions for changes indocuments should be in the form of a proposed change of text, together with appropriate supportingcomments.Interpretations: Occasionally, questions may arise about the meaning of specifications in relationship tospecific applications. When the need for interpretations is brought to the attention of the 1394 TradeAssociation, the Association will initiate action to prepare appropriate responses.Comments on specifications and requests for interpretations should be addressed to:Editor, 1394 Trade Association315 Lincoln, Suite EMukilteo, W A 98275USA1394 Trade Association Specifications are adopted by the 1394 Trade Association withoutregard to patents which may exist on articles, materials or processes or to otherproprietary intellectual property which may exist within a specification. Adoption of aspecification by the 1394 Trade Association does not assume any liability to any patentowner or any obligation whatsoever to those parties who rely on the specificationdocuments. Readers of this document are advised to make an independent determinationregarding the existence of intellectual property rights, which may be infringed byconformance to this specification.Published by1394 Trade Association315 Lincoln, Suite EMukilteo, WA 98275 USACopyright © 2010 by 1394 Trade AssociationAll rights reserved.Printed in the United States of AmericaFWDG 1.0TA FireWire Design Guide 03/02/2010IEEE CopyrightPortions of this specification are copied from published IEEE standards, by permission.The source documents are:IEEE Std 1394-1995, Standard for a High Performance Serial BusIEEE Std 1394a-2000, Standard for a High Performance Serial Bus – Amendment 1The IEEE copyright policy at /IPR/copyrightpolicy.html states, in part:Royalty Free PermissionIEEE-SA policy holds that anyone may excerpt and publish up to, but not more than, ten percent (10%) ofthe entirety of an IEEE-SA Document (excluding IEEE SIN books) on a royalty-free basis, so long as:1)proper acknowledgment is provided;2)the ‘heart’ of the standard is not entirely contained within the portion being excerpted.This included the use of tables, graphs, abstracts and scope statements from IEEE DocumentsFireWire Design Guide FWDG 1.0TA03/02/2010 ChecklistAll designers of devices with FireWire ports should look for the following:#2.1: Connectors (both plugs and sockets) shall meet the requirements laid out in the IEEE standards. (7)#2.2: Plugs shall have an overmold that includes strong tactile cues for orientation. (8)#2.3: Sockets should be oriented so that “thumb” part of plug is on top or on the left (9)#2.4: Sockets attached to a single PHY should be close together. (10)#2.5: FireWire 800 9-to-9 (1394b type 1) cable assemblies shields and ground shall not be shorted together. (10)#3.1: The wiring between the connector and the PHY (TP1 to TP2 and TP3 to TP4) shall be as short as possible. (14)#3.2: Ensure correct value for TPBIAS decoupling capacitor. (15)#3.3: Limit FW400 common mode choke to the minimum necessary to pass EMC (15)#3.4: Implement a transient protection circuit in a power provider to protect the PHY from late VG events. (15)#3.5: FireWire power should be current limited and filtered. (16)#3.6: VG must be capacitively connected to chassis ground and directly connected to PHY signal ground with minimal (pref-erably no) filtering. (16)#3.7: The socket shield shall be directly connected to chassis ground for all unisolated ports. (16)#3.8: The socket shield(s) shall be directly connected to VG at one place in the system. (17)#3.9: Systems that require isolated interfaces shall use a beta-only 1394b connection. (17)#3.10: FW800 ports should avoid common mode chokes. (18)#3.11: FW800 connector socket should internally bond the inner and outer shells. (18)#3.12: FW800 TPA and TPB shields have different termination requirements than each other and for FW400 shields. (18)#3.13: Ensure signal integrity of long traces to support front panel connectors. (18)#3.14: If a system has multiple PHYs and at least one of the PHYs has S800 or faster ports, then all the PHYs should be S800 or faster. (19)#4.1: Ensure that Power_class is set correctly. (21)#4.2: Ensure CONTENDER is deasserted (21)#4.3: Connect PCIe CLKREQ* (21)#4.4: TI PHY core voltage is 1.95V (22)#4.5: TI PHY core voltage filtering uses 1uF caps (22)#4.6: TI PHY oscillator voltage can be 1.95V (22)#4.7: Ensure correct PHY/LINK pin termination when using TI PHYs in repeater mode (22)#4.8: Ensure configuration and termination of unused port(s) on TI PHYs (22)#4.9: Ensure LKON/DS2 is correctly biased high or low (23)#4.10: Caution when TI 1394b PHY port 2 is unused or set to DS-only mode (23)#4.11: Note TI PHY max port speed is reported incorrectly for DS-mode only ports (23)#4.12: Use peaking inductors on bi-lingual ports on TI PHYs (23)#4.13: Tie PLLVDD_33 to the AVDD_3_3 power rail on TI PHYs. (23)#4.14: Ensure that TI PHY recommendations are met (23)#4.15: Connect Chex OHCI_PME# to a GPIO for optimal power management (23)#4.16: Ensure that Chex GRST# asserts only on link layer power cycle. (23)#4.17: Leave Chex GPIO’s as no-connects (24)#4.18: Bring Chex CYCLEOUT to a test point (24)#4.19: Connect VDD_33_AUX to 3.3V (24)#4.20: Ensure TI Link devices implementation requirements are met (24)#4.21: Ensure power is provided during sleep mode for TI Link devices. (24)#4.22: Ensure that G_RST* timing requirement is met (24)#4.23: G_RST* is asynchronous (24)#4.24: Ensure VAUX_DETECT is pulled high on FW643 (25)#4.25: Ensure FW643 power reset is stuffed consistently with regulation of 1.0V supply (25)#4.26: Ensure LSI integrated PHY/Link devices implementation requirements are met (25)#4.27: Ensure power is provided during sleep mode for LSI integrated PHY/Link devices. (25)#4.28: Ensure PME is uniquely identifiable to software for LSI FW323 v129. (25)#4.29: Internal or external pull-downs required on PHY/Link interface (27)#4.30: Special termination may be needed if PHY/Link propogation delay is > 1 ns (27)FWDG 1.0TA FireWire Design Guide 03/02/2010#5.1: All components and traces between the protection diode and the connector need to support 33V or higher. (29)#5.2: PHY operation should not be affected by power provider current limiter trips (29)#5.3: System operation of power providers should not be affected by power consumer inrush or shorts. (29)#5.4: Power Class 4 power providers should implement appropriate CSRs. (30)#5.5: Bus powered portable devices and peripherals should declare the appropriate power class. (30)#5.6: Power consumers should implement the power management CSRs. (30)#5.7: Ensure that CPS is correctly connected (32)#6.1: OHCI link must reliably meet real-time requirements under anticipated load. (40)FireWire Design Guide FWDG 1.0TA03/02/2010 Contents2. Mechanical (7)2.1 Connectors (7)2.2 End-to-end connections (10)3. Port design (14)3.1 Interfaces (14)3.2 Connector/PHY wiring (14)3.2.1 Termination (17)3.2.2 Front panel (“remote”) connector wiring guide (18)3.3 Testing Advice (19)4. System design (21)4.1 PHY selection (21)4.2 PHY configuration recommendations (21)4.2.1 General (21)4.3 Link layer recommendations (21)4.3.1 PCIe recommendations (21)4.4 Specific device recommendations (22)4.4.1 TI TSB81BA3 (22)4.4.2 TI XIO2213 (Cheetah Express, aka Chex) (23)4.4.3 Texas Instruments TSB82AA2 1394b link device (24)4.4.4 LSI FW643 (25)4.4.5 LSI FW323 (25)4.5 PHY/Link interface (27)4.5.1 Additional requirements (27)4.5.2 Layout guide (28)5. Cable power (29)5.1 Introduction (29)5.2 FireWire power checklistrecommendations (29)5.3 FireWire device guidelines (30)5.4 Example Circuits (31)5.4.1 Desktop alternate power provider (33)5.4.2 Desktop primary power provider with backup power pass-through (34)5.4.3 Portable computer (35)5.4.4 Peripherals or mobile devices (36)5.5 Notes (37)5.5.1 Power Classes (for reference) (37)5.5.2 Note on diode protection (37)5.5.3 Use of Power Down and Cable Not Active (38)5.5.4 Trade Association Cable Power Distribution Specification - proposed variations (39)6. Link selection (40)6.1 OHCI requirements (40)6.2 Target devices (40)6.2.1 Asynch peripherals (40)6.2.2 Media/consumer electronics (40)FWDG 1.0TA FireWire Design Guide 03/02/20107. Firmware/higher layers (41)7.1 Basic node operation (41)7.1.1 Bus initialization (41)7.1.2 Configuration ROM (41)7.1.3 Isochronous Resource Manager (41)7.1.4 Bus Manager (42)7.1.5 Required performance (42)7.1.6 Interoperability issues (42)7.2 Mass storage devices (42)7.2.1 SBP profile (42)7.2.2 A V profile (42)7.3 Imaging devices (42)7.3.1 Printers (42)7.3.2 Scanners (42)7.3.3 Still image cameras (42)7.3.4 Machine vision cameras (42)7.4 Consumer electronics (43)7.4.1 Tape recorders (43)7.4.2 Televisions (43)7.4.3 Set top boxes (43)7.4.4 Disks (43)7.4.5 Audio equipment (43)7.5 Professional (43)7.5.1 Audio (44)7.5.2 Video (44)7.6 Automobile (44)7.7 Industrial/Instrumentation (44)8.1 Layout recommendations for S800 1394b TSB81BA3 Physical Layer: (51)9. Firewire Design Guide – Robust Port Design (57)12.1 Conformance terminology (75)12.2 Technical glossary (75)FiguresFigure2-1— Plug overmold (8)Figure2-2— Socket orientation (as viewed from outside of bulkhead) (9)Figure2-3— Legacy socket orientation (as viewed from front of product) (9)Figure2-4— 1394b type 1 cable assembly and schematic (Beta plug to Beta plug) (11)Figure2-5— 1394b type 2 cable assembly and schematic (Legacy 6 circuit plug to Bilingual plug) (12)Figure2-6— 1934b type 3 cable assembly and schematic (Legacy 4-circuit plug to Bilingual plug) (13)Figure3-1— Measurement points (half connection is shown) (14)Figure5-1— A multiport Power Provider class 1/2/3 node (32)Figure5-2— A multiport Power Provider class 4 node (33)Figure5-3— A multiport Power Provider class 1/2/3 node, operating as Class 4 when power is not available (34)Figure5-4— A multiport Alternate Power Provider class 4 node (35)Figure5-5— A single port bus-powered (class 4) node (36)Figure5-6— A multiport bus-powered (class 4) node (36)Figure5-7— Diodes to provide power management domains (38)Figure8-1— Example FW800 OHCI Controller (46)Figure10-1— Example extendible two port power management IC (72)Figure10-2— Using multiple two port power management ICs (73)TablesTable2-1— Insertion and removal force (tentative) (7)Table2-2— 1394b type 1 (Beta to beta) end-to-end connections (11)Table2-3— Legacy 6 circuit to 1394b Bilingual end-to-end connections (12)Table2-4— Legacy 4 circuit to 1394b Bilingual end-to-end connections (13)Table3-1— 1394b receiver characteristics (14)Table4-1— Phantom cycles caused by MI cycle reflection (27)Table5-1— Power class (37)2.2.1ConnectorsItem #2.1:Connectors (both plugs and sockets) shall meet the requirements laid out in the IEEE stan-dards.Sockets must strongly resist “backwards” insertionThis means that the “narrow” part of the socket shall not have a split unless there is a mechanical reinforcement that pre-vents the narrow end from spreading when a plug is inserted backwards. It further means that the mechanical tolerences specified in [2], [3], and [4] must be met. In particular, the socket should meet the following insertion force requirements:Table2-1—Insertion and removal force(tentative)Condition Insertion/removalforceComment6-pin plug correctly aligned inserted into 6-pin socket9-pin plug correctly aligned inserted into 9-pin socket < 1 N measured using a plug that is at the maximum dimensions allowed by 1394, andmaximum value before any of the VG, VP, or TPx contactsmate, andmust have a noticeable “click” or “snap” when fully inserted6-pin plug correctly aligned removed from 6-pin socket9-pin plug correctly aligned removed into 9-pin socket > 1 N measured using a plug that is at the minimum dimensions allowed by 1394, andminimum value before any of the VG, VP, or TPx contactsseparate, andmust have a noticeable “click” or “snap” when removed6-pin plug reverse aligned inserted into 6-pinsocket9-pin plug reverse aligned inserted into 9-pinsocket > 10 N measured using a plug that is at the minimum dimensions allowed by 1394, andminimum force before any of the VG, VP, or TPx contactsmate, andsocket must be noticeably damaged by reverse insertion(allows diagnosis of improper use)Item #2.2:Plugs shall have an overmold that includes strong tactile cues for orientation.Overmold cues are to provide hints for where the user should put the thumb.a)Flat surface corresponds with “flat” surface on narrow axis b)Round surface corresponds with “angled” surface on narrow axisThis will assist in preventing attempted backwards connection (particularly if the connector placement rules described below are followed).Figure 2-1—Plug overmoldLegacy 6-pinBeta/bilingual 9-pinFWDG 1.0TA FireWire Design Guide 03/02/2010Item #2.3:Sockets should be oriented so that “thumb” part of plug is on top or on the leftSockets should have a standard orentation to aid the “blind” insertion of the plug. Since the plug overmold has features to encourage the placement of the thumb in a particular spot, and most people prefer to put their thumb on top of a plug as they insert it, the socket itself should be oriented so that the “thumb” feature is on top as viewed looking at the bulkhead from the outside. And since most people are right handed,. the alternate positioning should have the “thumb” feature on the left. Figures 2-2 and 2-3 illustrate the concept.Figure2-2—Socket orientation (as viewed from outside of bulkhead)... or as viewed from the front of a hypothetical product:Figure2-3—Legacy socket orientation (as viewed from front of product)FireWire Design Guide FWDG 1.0TA03/02/2010 Item #2.4:Sockets attached to a single PHY should be close together.Connectors, PHY, protection and termination components for a single port are best seen as a lumped circuit. The min. rise time for 1394a is 0.5 ns which implies 1 GHz waveforms, while the min. rise time for 1394b is 0.080 ns, over 6 GHz! If both front and back panel sockets are desired, then there are two choices:a)separate PHYs for front and back (two PHYs and one Link), orb) a very carefully designed “remote” socket where the entire path from the PHY termination network (seeclause3.2.2) to the socket is within 1394 requirements (110 ± 6 Ω differential mode and 33 ± 6 Ω common mode, more details in [2]). Note that this is quite unlikely to be successful for a S800 or faster port.2.2End-to-end connectionsItem #2.5:FireWire 800 9-to-9 (1394b type 1) cable assemblies shields and ground shall not be shorted together.Since the new 1394b connections are unfamiliar with designers, the end-to-end connections for the various 1394b cables are described in figure2-4, table2-2, figure2-5, table2-3, figure2-6 and table2-4.FWDG 1.0TA FireWire Design Guide03/02/2010NOTE—The legacy interface cables (type 2 9-to-6 and type 1 9-to-4) do short some of the shields and ground together. It is important that this be done correctly for each cable type.NOTE—Cable as defined in 1394b. Connectors are viewed as looking at the front plug face.Figure 2-4—1394b type 1 cable assembly and schematic (Beta plug to Beta plug)Table 2-2—1394b type 1 (Beta to beta) end-to-end connectionsSignal PCB pad Socket/plug name Socket/plug connection Cable Socket/plug connection Socket/plug name PCB pad SignalChassis Ground 13Chassis GroundOuter shell(no connect)Outer shell Chassis Ground12Chassis Ground Chassis Ground, HF to Logic Ground 11Cable Shield Ground Inner shell Outer shieldInner shellCable Shield Ground 10Chassis Ground, HF to Logic Ground TPA4TPA 4Signal pair #1 red2TPB 2TPB High frequency to Logic Ground 5TPA(R)5Signal pair #1 shield 9TPB(R)9Logic Ground TPA*3TPA*3Signal pair #1 green 1TPB*1TPB*Logic Ground 6VG 6Power pair #1 white 6VG 6Logic Ground (no connect)7SC 7(no connect)7SC 7(no connect)FW PWR 8VP 8Power pair #1 black 8VP 8FW PWR TPB 2TPB 2Signal pair #2 blue4TPA 4TPALogic Ground 9TPB(R)9Signal pair #2 shield 5TPA(R)5High frequency to Logic Ground TPB*1TPB*1Signal pair #2 orange 3TPA*3TPA*Chassis Ground, HF to Logic Ground 10Cable Shield Ground Inner shell Outer shieldInner shellCable Shield Ground 11Chassis Ground, HF to Logic Ground Chassis Ground12Chassis GroundOuter shell(no connect)Outer shellChassis Ground13Chassis Ground743215689743215689plug 1plug 2FireWire Design GuideFWDG 1.0TA 03/02/2010NOTE—Cable (reference) IEEE Std 1394-1995. Connectors are viewed as looking at the front plug face.Figure 2-5—1394b type 2 cable assembly and schematic (Legacy 6 circuit plug to Bilingual plug)Table 2-3—Legacy 6 circuit to 1394b Bilingual end-to-end connectionsSignalPCB padSocket/plug nameSocket/plug connectionCable Socket/plug connection Socket/plug name PCB pad Signal (no connect)Outer shell Chassis Ground12Chassis Ground Chassis Ground, HF to Logic Ground Cable Shield Ground Plug shell Outer shieldInner shellCable Shield Ground 10Chassis Ground, HF to Logic Ground TPA 6TPA 6Signal pair #1 red 2TPB 2TPB Logic Ground 2VG 2Signal pair #1 shield 9TPB(R)9Logic Ground TPA*5TPA*5Signal pair #1 green 1TPB*1TPB*Logic Ground2VG2Power pair #1 white 6VG 6Logic Ground (no connect)7SC 7(no connect)FW PWR 1VP 1Power pair #1 black 8VP 8FW PWR TPB 4TPB 4Signal pair #2 blue 4TPA 4TPALogic Ground 2VG 2Signal pair #2 shield 5TPA(R)5High frequency toLogic Ground TPB*3TPB*3Signal pair #2 orange 3TPA*3TPA*Chassis Ground, HF to Logic GroundCable Shield Ground Plug shell Outer shieldInner shellCable Shield Ground 11Chassis Ground, HF to Logic Ground (no connect)Outer shellChassis Ground13Chassis Ground432156743215689plug 1plug 2NOTE—Cable (reference) IEEE Std 1394a-2000. Connectors are viewed as looking at the front plug face.Figure 2-6—1934b type 3 cable assembly and schematic (Legacy 4-circuit plug to Bilingual plug)Table 2-4—Legacy 4 circuit to 1394b Bilingual end-to-end connectionsSignalPCB padSocket/plug nameSocket/plug connectionCable Socket/plug connection Socket/plug name PCB pad Signal (no connect)Outer shell Chassis Ground12Chassis Ground (no connect)Outer shieldInner shellCable Shield Ground 10Chassis Ground, HF to logic Ground TPA 4TPA 4Signal pair #1 red 2TPB 2TPB Logic Ground ShellPlug shell Signal pair #1 shield 9TPB(R)9Logic Ground TPA*3TPA*3Signal pair #1 green 1TPB*1TPB*(no connect)6VG 6Logic Ground (no connect)7SC 7(no connect)(no connect)8VP 8FW PWR TPB 2TPB 2Signal pair #2 blue 4TPA 4TPALogic Ground ShellPlug shell Signal pair #2 shield 5TPA(R)5High frequency to Logic Ground TPB*1TPB*1Signal pair #2 orange 3TPA*3TPA*(no connect)Outer shieldInner shellCable Shield Ground 11Chassis Ground, HF to logic Ground (no connect)Outer shellChassis Ground13Chassis Ground4321plug 1743215689plug 23.There are a number of good 1394 port design application notes. The TI notes on EMI [11] and layout [12] as well as the LSI design guide for the FW323 [13] are particularly good. Every designer of FireWire systems should be familiar with these documents. Much of the following is derived from those application notes.3.1InterfacesAll interface specifications apply at the points of entry and exit from the equipment. The interface specifications may be “valid” at other places. These points are identified as points TP2 and TP3 as shown in Figure 3-1. The specifications assume that all measurements are made after a mated connector pair, relative to the source or destination. TP1 and TP4are reference points for use by implementors to specify vendor components. In particular, PHY IC specs apply at TP1 for transmit and TP4 for receive.The reference points for all connections are those points TP2 and TP3 at the transitions between the cabinet and the cable shield. If sections of transmission line exist within the cabinet shield, they are considered to be part of the associated transmit or receive network, and not part of the cable plant.NOTE—Do not confuse “TPn” where “n” is the number one through four with the “TPx” where “x” is “A” or “B”. TPn refers to a test point and TPx refers to a twisted pair signal.3.2Connector/PHY wiringItem #3.1:The wiring between the connector and the PHY (TP1 to TP2 and TP3 to TP4) shall be as short as possible.The TPA and TPB pairs carry very high speed signals, and so must be imlemented using good design practices for high speed circuits and interfaces to external devices. The impedance requirements for the connector/PHY wiring shall meet 1394b requirements (included below for reference).Figure 3-1—Measurement points (half connection is shown)Table 3-1—1394b receiver characteristicsParameterS400βS800βS1600βUnitsInput impedance test conditions:TDR rise time 10010050ps Exception window a 700700700psInput impedance @ TP3:Through connection b 110 ± 20110 ± 20110 ± 20ΩAt termination c110 ± 10110 ± 10110 ± 10ΩTRANSMIT NETWORKRECEIVE NETWORKT+T-R+R-TP1TP2TP3TP4PHYPHYNOTE—1394 bilingual and FW400 ports have transmitter and receiver on both the TPA and TPB signals, so the receiver input impedance spec applies for both pairs.3.2.0.1TerminationThe TPA pair has the required 110 ¾ differential termination as close as possible to the PHY, with the center point of the termination attached to the PHY’s bias output for that port and capacitively to signal ground (each port on the PHY shall have an independent bias output – this is required to prevent a short on one port from causing all the other ports to not operate).Item #3.2:Ensure correct value for TPBIAS decoupling capacitor.The PHY’s tpbias output should be decoupled with a 0.33 μF capacitor to ground, unless the PHY is a TI PHY. TI PHYs need a 1.0 μF to ground, so as to guarantee a minimum ripple on the tpbias voltage under a worst-case speed-signaling scenario, which is necessary in the TI design to maintain stability of the tpbias driver. The lower value is needed when using non-TI PHYs in order to meet the 1394a timing specification for tpbias assertion and deassertion.3.2.0.2TP EMC/EMI protectionItem #3.3:Limit FW400 common mode choke to the minimum necessary to pass EMCFW400 ports may need a high speed common mode choke, particularly if the PHY-to-connector layout is long or runs near possible signal sources. Individual components must be used for each signal pair to limit crosstalk between TPA and TPB. The choke must allow the lower fequency common mode speed signals to get through (while removing high fre-quency common mode signals). In general, this means that the common mode impendence must be less than 165 Ohms at 100 MHz, and the differential impedence less than 15 ohm at 100 MHz.Products should use the minimum choke necessary to pass EMC. The design should anticipate evaluation of EMC com-pliance with several values (for example, the Murata DLP11SN range starts at 67 Ohms, with variants at 90 Ohms, 120Ohms and 160 Ohms), and with not using a common mode choke at all. This can be achieved by designing the layout to allow a common mode choke or a 0 Ohm resistor.3.2.0.3Transient protectionItem #3.4:Implement a transient protection circuit in a power provider to protect the PHY from late VG events.Power providers should have a diode clamping network between the PHY and the socket to provide two functions:a)ESD protection so that the high voltage is drained to the chassis, andDifferential skew5%5%5%UI Common mode input impedance> 550Ωa.Within the Exception-window no single impedance excursion shall exceed the Through-connection impedance tolerance for a period of twice the TDR rise time specification.b.Through connection impedance describes the impedance tolerance through a mated connector. This tolerance is greater than the termination or cable impedance due to limits in the technology of the connectors.c. The input impedance at TP3, for the termination, shall be recorded 4.0ns following the electrical reference plane determined by the receptacle on the receiver bulkheadTable 3-1—1394b receiver characteristicsParameterS400βS800βS1600βUnitsFireWire Design Guide FWDG 1.0TA03/02/2010 b)“Late VG” protection (so called because the power provided on VP can appear on the TPx signals if the VGconnection takes place after the VP and at least one of the TPx connections is completed). Note that this last function requires that chassis ground and signal ground have a low resistance connection somewhere (see Item #3.8:below).The high side clamp diodes use a 3.6V nominal zener diode prebiased with a 3.3V source via a 330 Ohm current liminting resistor (other sources may be used with an appropriate resistor value). This provides a nominal 2.4V, worst case 2.1V ESD and late-VG rail to the BAV99 diodes. In turn, allowing for a 0.6V drop through the diodes, this will permit FireWire signaling at up to 2.7V without compromising signal integrity. A late-VG event on the signal pairs will be drained back to ground via the Zener diode. Late VG events can be of a long duration, and they represent a return path for the VP supply, so the current must be directed back to VG. Despite its rating, the recommended Zener has been mea-sured as being capable of sustaining a current of 300mA, up to 2W, keeping the voltage level on the signal pins to less than 5.5V, which the PHY is also able to tolerate. Under more stress, either the PHY fails or the Zener. The Zener tends to fail short, which results in the TPA/TPB pairs being held to GND and preventing FireWire operation. Lower voltage Zeners, which have been used in some designs, tend to fail before the PHY, increasing the system return rate unnecessar-ily.ESD events are of a short duration and will be drained from digital ground to chassis ground and from there to earth ground. It is acceptable to use signal ground instead of chassis ground for the transient protection network since signal ground is capacitively connected to chassis ground at the connector. This can only be done if there is no ferrite on the VG path (see Item #3.6:below). The galvanic connection between chassis ground and signal ground must be low impedance at the frequencies not handled by the capacitive connection at the connector.If a common mode choke is used, then the transient supression network should be placed on the PHY side of the choke. The advantage of having the diodes on the PHY side is that the common mode choke can be placed closer to the connec-tor for better EMI performance.Late-VG does not occur on self powered devices.Transient protection iodes must have a very low capacitance (less than 0.5 pF).3.2.0.4Power and ground interface (VG/VP)Item #3.5:FireWire power should be current limited and filtered.VP should be current limited 1.5 A and EMI filtered to minimize system noise getting out to peripherals. Current limit can be done using a polyfuse, although their slow trip speed requires careful thought put towards the effect of momentary excess current draw. A choke between 50 ohm and 1000 ohm (at 100 MHz) is acceptable in the path for EMI filtering and should be located close to the sockets. A 0.010µf capacitor should connect to chassis ground immediately next to the socket.Item #3.6:VG must be capacitively connected to chassis ground and directly connected to PHY signal ground with minimal (preferably no) filtering.VG should AC connect to chassis ground immediately next to the socket using a 0.010µf capacitor. There must not be a significant impedance in the path between VG and the PHY signal ground since VG is the return path for the common mode speed signalling sent out on TPB and received on TPA. If a filter is implemented, it should be designed to pass the speed signal (100-120ns pulse of about 20ma on VG). Usually this means any ferrite in the VG path must be 50 ohm or less at 100 MHz.3.2.0.5Shield interfaceItem #3.7:The socket shield shall be directly connected to chassis ground for all unisolated ports.There should be a chassis ground plane underneath the socket for this purpose. The galvanic isolation options defined in 1394a and 1394-1995 should no longer be used.。

5114351_上菲红稳步迈向全系列动力供应商

0418□邮箱:***************专 题■ 本报记者 李晓菲 文/图4月20日,第十三届北京国际汽车展览会如期举行,上汽集团以集团形式参展。

作为上汽集团商用车板块关键零部件总成,上汽菲亚特红岩动力总成有限公司(以下简称“上菲红”)携旗下CURSOR、NEF、F1三大系列产品亮相,收获众多关注。

销量快速增长作为行业新兵,上菲红自2008年首台发动机下线以来,每年都以令人惊喜的速度快速增长,技术领先、品质可靠的产品是其销量快速增长的首要原因。

通过引进菲亚特动力科技的先进技术,上菲红发动机产品在动力性、燃油经济性、舒适性、环保等方面都能更好地满足用户需求。

为保证产品质量,上菲红还采用了WCM (世界级制造)生产管理系统,该系统是通过全员参与的方式,降低由于生产系统可靠性及运营低下导致的时间和资源浪费,改善生产效率,减少故障和提升质量的全面管理系统,专注于全体质量控制(TQC)、全体生产维护(TPM)、全体工业设计(TIE)、 及时交付(JIT),最终目标是将世界级制造延伸到所有工艺工程乃至所有供应商,从而实现生产过程零事故、生产设备零故障、生产材料零报废和产品质量零缺陷、物流过程零库存。

据介绍,上菲红目前的产品结构仍以CURSOR 系列为主,CURSOR 9是销售主力产品,在卡车、客车、工程机械、发电机组等领域均有所应用。

同时,轻型发动机F1系列的适配范围也逐步扩大,目前已经在轻客、皮卡、小型船舶等领域配装应用。

“2013年,上菲红完成了年初销售目标,销量达到23000台,这一销量的实现主要得益于上菲红在重卡市场产品认可度的提高以及出口市场的扩大。

”上菲红总经理Olivier Michard 表示。

目前,除了上汽依维柯红岩、南京依维柯等企业,上菲红动力产品还已经成功匹配宇通、华菱、武汉枭龙、山西中大、江苏巨超等众多国内品牌。

在国外市场,CURSOR 9已经配装美国CNH(凯斯纽荷兰)的农业设备;另外,CURSOR 9欧Ⅵ标准发动机已经开始在意大利IVECO 整车(卡车、客车)上批量配装。

宇通客车开辟车内自由呼吸新天地

04 □邮箱:***************宇通客车开辟车内自由呼吸新天地本报讯 客车业巨头宇通推出了能有效降低车内PM2.5的车载空气净化装置,由此,雾霾天气中乘车外出的人们在移动的公交车内终于可以解开口罩放松呼吸。

宇通早在2008年就开始关注车内空气质量问题并于去年1月成功研发出空气净化装置,在国内大范围雾霾天气出现后,又在最短时间内对装置进行更新升级,强化了PM2.5的净化功能,装置已于今年2月获得国家知识产权局专利。

该装置主要针对人员复杂及有机性污染物多的客车巴士开发,可实现对PM2.5的去除功能,也具备对甲醛、甲苯等本报讯 华菱星马一季度累计销售重卡5385辆、专用车1299辆,同比分别增长20.85%和25.75%,实现了自2011年以来的首次增长。

今年以来,公司加大了市场开拓力度和提升营销体系内部效能:所有销售人员重新配备,精英充实到市场;内部各岗位职能重新整合;完善营销体系内部沟通机制;利用现代化通信提高各项工作效率。

一系列举措有效推动了销售的高效率运转,一季度的大幅增长既有市场回暖的因素,更是华菱厚积薄发、提前准备的结果。

赵 勇华菱星马一季度劲增超20%本报讯 四川省芦山“4·20”7.0级强烈地震发生后,上汽依维柯红岩商用车有限公司快速响应,位于雅安范围内的红岩汉源服务站服务小分队当晚即赶往灾区,为抗震救灾军用车辆全力做好服务保障,同时义务为灾区民用车辆展开维修检测。

4月21日,第二批服务人员在天全县始阳镇集合,随时待命进入灾区。

雅安周边的8家红岩服务站已做好准备,实行24小时值班制度,利用专业的流动服务车辆对参加抗震救灾的军车、民用重卡实施现场救援,免收一切服务费用。

商 车灾后第一晚红岩汽车小分队进入芦山本报讯 近日,东风柳汽在业内首推体验式营销,针对新上市不久的霸龙康明斯M7C 在全国范围内开展免费试用活动,最长试用时间可达1个月,试用里程最长可达2万公里,将柳汽的价值营销上升到了新高度。

TSPL中文文档

目录文件字体规则 (1)系统设定指令 (2)SIZE (2)GAP (3)BLINE (4)OFFSET (5)SPEED (6)DENSITY (7)DIRECTION (8)REFERENCE (9)COUNTRY (10)CODEPAGE (11)CLS (12)FEED (13)FORMFEED (14)HOME (15)PRINT (16)SOUND (17)CUT (18)LIMITFEED (19)卷标内容设计指令 (20)BAR (20)BARCODE (21)BITMAP (25)BOX (26)ERASE (27)DMATRIX (28)MAXICODE (29)PDF417 (32)PUTPCX (34)REVERSE (35)TEXT (36)询问打印机状态指令 (38)<ESC>!? (38)~!A (40)~!T (41)~!C (42)~!I (43)~!F (44)~!@ (45)信息传递协议 (46)<ESC>! (46)<ESC>& (46)~# (47)WINDOWS DRIVER驱动程序指令 (48)!B (48)!J (49)!N (50)档案管理指令 (51)DOWNLOAD (51)REDRAW (59)EOP (60)FILES (61)KILL (62)MOVE (63)UPDATBIOS (64)BASIC 指令及函式 (65)ABS( ) (65)ASC( ) (66)CHR$( ) (67)END (68)EOF( ) (69)OPEN (71)READ (73)SEEK (75)LOF( ) (77)FREAD$( ) (77)FOR...NEXT.. (79)IF...THEN...ELSE (81)GOSUB...RETURN. (83)GOTO (85)INPUT (88)REM (90)OUT (91)GETKEY( ) (92)INT( ) (93)LEFT$( ) (94)LEN( ) (95)MID$( ) (96)RIGHT$( ) (97)STR$( ) (98)VAL( ) (99)BEEP (100)打印机外围功能设定指令 (101)SET COUNTER (101)SET CUTTER (103)SET KEY1 (105)SET KEY2 (105)SET LED1, LED2, LED3 (107)SET PEEL (108)SET DEBUG (109)SET GAP (110)SET RIBBON (111)SET COM1 (112)@LABEL (114)PEEL (115)LED1, LED2, LED3 (116)KEY1, KEY2 (117)YEAR (118)MONTH (119)DATE (120)WEEK (121)HOUR (122)MINUTE (123)SECOND (125)文件字体规则本文件使用以下字体规则文件规则描述[表示内容] 在`中括号内表示该参数为选项<ESC> <ESC>代表ASCII 27 字符,当打印机收到以该控制字符为启始之指令将立即响应(即使打印机在错误状态时也将实时回应)~ (ASCII 126), 该字符启始的指令用于询问打印机的状态注: 200 DPI: 1 mm = 8 dots 粗斜体Arial,字型,用于表300 DPI: 1 mm = 12 dots 示批注DOWNLOAD “TEST.BAS”当所列出的内容为程序SET COUNTER @1 1 时以Curier 字型表示@1=”0001”TEXT 10,10,”3”,0,1,1,@1PRINT 3,2EOP系统设定指令SIZE说明该指令用于设定卷标纸的宽度及长度指令语法(1) 英制系统(英寸)SIZE m, n(2) 公制系统(公厘)SIZE m mm, n mm参数说明m 标签纸的宽度 (不含背纸)n 标签纸的长度 (不含背纸)Note: 200 DPI: 1 mm = 8 dots*300 DPI: 1 mm = 12 dots范例(1) 英制系统 (英寸)SIZE 3.5, 3.00(2) 公制系统 (公厘)SIZE 100 mm, 100 mmGAP说明该指令定义两张卷标纸间的垂直间距距离指令语法(1) 英制系统 (英寸)GAP m, n(2) 公制系统 (公厘)GAP m mm, n mm参数说明m 两标签纸中间的垂直距离0 ≤ m ≤ 1 (英寸), 0 ≤ m ≤ 25.4 (公厘)n 垂直间距的偏移[-]n ≤标签纸张长度 (英寸或公厘)Note: 200 DPI : 1 mm = 8 dots300 DPI : 1 mm = 12 dots范例一般垂直间距设定(1) 英制系统 (英寸)GAP 0.12,0(2) 公制系统 (公厘)GAP 3 mm,0特殊垂直间距设定(1) 英制系统 (英寸)GAP 0.30,-0.10(2) 公制系统 (公厘)GAP 7.62 mm, -2.54 mmBLINE说明该指令用于设定黑标的高度及偏移位置指令语法(1) 英制系统 (英寸)BLINE m, n(2) 公制系统 (公厘)BLINE m mm, n mm参数说明m 黑标的高度,以英寸或公厘表示0.1 ≤m ≤1 (英寸), 2.54 ≤m ≤ 25.4 (公厘)n 黑标偏移量 0 ≤n ≤标签纸张高度范例(1) 英制系统 (英寸)BLINE 0.20,0.50(2) 公制系统 (公厘)BLINE 5.08 mm,12.7 mmOFFSET说明该指令用于控制在剥离模式时(pee-off mode)每张卷标停止的位置,该指令仅适用于剥离模式。

PIC16LF1508-ISS;PIC16F1508-ISS;PIC16LF1509-ISS;PIC16F1509-ISS;中文规格书,Datasheet资料

Trademarks The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC32 logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. Analog-for-the-Digital Age, Application Maestro, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, , dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, , PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. SQTP is a service mark of Microchip Technology Incorporated in the U.S.A. All other trademarks mentioned herein are property of their respective companies. © 2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved. Printed on recycled paper. ISBN: 978-1-61341-726-3

CANalyzer.J1939_Manual_EN

This symbol calls your attention to warnings.

Here you can find additional information.

Here is an example that has been prepared for you.

Step-by-step instructions provide assistance at these points.

User Manual

CANalyzer Option .J1939

Version 7.0 English

Imprint

Vector Informatik GmbH Ingersheimer Straße 24 D-70499 Stuttgart

The information and data given in this user manual can be changed without prior notice. No part of this manual may be reproduced in any form or by any means without the written permission of the publisher, regardless of which method or which instruments, electronic or mechanical, are used. All technical information, drafts, etc. are liable to law of copyright protection. © Copyright 2007, Vector Informatik GmbH All rights reserved.

国际电子(National Instruments)USB-7845R OEM 多功能数字实时接口设

SPECIFICATIONSNI USB-7845R OEMR Series for USB Multifunction RIO with Kintex-7 70T FPGA Français Deutsch日本語한국어简体中文/manualsThis document contains the specifications for the National InstrumentsUSB-7845R OEM device. Specifications are typical at 25 °C unless otherwise noted.Caution Using the NI USB-7845R OEM device in a manner not described in thisdocument may impair the protection the NI USB-7845R OEM device provides. Analog InputNumber of channels8 ............................................................................Input modes DIFF, NRSE, RSE (software-selectable; ............................................................................selection applies to all channels)Type of ADC Successive approximation register (SAR) ............................................................................Resolution16 bits ............................................................................Conversion time 2 µs ............................................................................Maximum sampling rate500 kS/s (per channel) ............................................................................Input impedancePowered on 1.25 GΩ ║ 2 pF....................................................................Powered off/overload 4.0 kΩ min....................................................................Input signal range±1 V, ±2 V, ±5 V, ±10 V (software-selectable) ............................................................................Input bias current±5 nA ............................................................................ ............................................................................Input offset current±5 nAInput coupling DC ............................................................................Overvoltage protection....................................................................Powered on±42 V maxPowered off±35 V max....................................................................Table 1. AI Operating Voltage Ranges Over TemperatureAI Absolute AccuracyAbsolute accuracy at full scale numbers is valid immediately following internal calibration and assumes the device is operating within 10 °C of the last external calibration. Accuracies listed are valid for up to one year from the device external calibration.Absolute accuracy at full scale on the analog input channels is determined using the following assumptions:•TempChangeFromLastExternalCal = 10 °C •TempChangeFromLastInternalCal = 1 °C•number_of_readings = 10,000•CoverageFactor = 3 σ1The minimum measurement voltage range is the largest voltage the NI USB-7845R OEM device is guaranteed to accurately measure.2| | NI USB-7845R OEM SpecificationsTable 2. AI Absolute Accuracy (Calibrated) (Continued)Table 3. AI Absolute Accuracy (Uncalibrated)Calculating Absolute AccuracyAbsoluteAccuracy=Reading⋅(GainError)+Range*(OffsetError)+NoiseUncertaintyGainError=ResidualGainError+GainTempco*(TempChangeFromLastInternalCal)+ReferenceTempco*(TempChangeFromLastExternalCal)OffsetError=ResidualOffsetError+OffsetTempco*(TempChangeFromLastInternalCal)+INL_ErrorNoiseUncertainty=Refer to the following equation for an example of calculating absolute accuracy.NI USB-7845R OEM Specifications| © National Instruments| 3Absolute accuracy at full scale on the analog input channels is determined using the following assumptions:•TempChangeFromLastExternalCal = 10 °C •TempChangeFromLastInternalCal = 1 °C•number_of_readings = 10,000•CoverageFactor = 3 σGainError=104.4ppm+20ppm*1+4ppm*10GainError=164.4ppmOffsetError=16.4ppm+4.18ppm*1+42.52ppmOffsetError=63.1ppmNoiseUncetainty=NoiseUncertainty=7.89µVAbsoluteAccuracy=10V*(GainError)+10V*(OffsetError)+NoiseUncertaintyAbsoluteAccuracy=2,283µVDC Transfer Characteristics ............................................................................INL Refer to the AI Accuracy TableDNL±0.4 LSB typ, ±0.9 LSB max ............................................................................No missing codes16 bits guaranteed ............................................................................CMRR, DC to 60 Hz-100 dB ............................................................................Dynamic CharacteristicsBandwidthSmall signal 1 MHz........................................................................................................................................Large signal500 kHz4| | NI USB-7845R OEM Specifications............................................................................Crosstalk-80 dB, DC to 100 kHzAnalog Output ............................................................................Output type Single-ended, voltage output ............................................................................Number of channels8 ............................................................................Resolution16 bits ............................................................................Update time 1.0 µs ............................................................................Maximum update rate 1 MS/sType of DAC Enhanced R-2R ............................................................................ ............................................................................Range±10 V ............................................................................Output coupling DCOutput impedance0.5 Ω............................................................................NI USB-7845R OEM Specifications| © National Instruments| 5............................................................................Minimum current drive±2.5 mAProtection Short circuit to ground ............................................................................Overvoltage protectionPowered on±15 V max....................................................................Powered off±10 V max....................................................................Power-on state User-configurable ............................................................................Power-on glitch-1 V for 1 µs ............................................................................Table 4. AO Operating Voltage Ranges for Over TemperatureAO Absolute AccuracyAbsolute accuracy at full scale numbers is valid immediately following internal calibration and assumes the device is operating within 10 °C of the last external calibration. Accuracies listed are valid for up to one year from the device external calibration.Absolute accuracy at full scale on the analog output channels is determined using the following assumptions:•TempChangeFromLastExternalCal = 10 °C •TempChangeFromLastInternalCal = 1 °C2The minimum measurement voltage range is the largest voltage the NI USB-7845R OEM device is guaranteed to accurately measure.6| | NI USB-7845R OEM SpecificationsTable 5. AO Absolute Accuracy (Calibrated) (Continued)Calculating Absolute AccuracyAbsoluteAccuracy=OutputValue*(GainError)+Range*(OffsetError)GainError=ResidualGainError+GainTempco*(TempChangeFromLastInternalCal)+ReferenceTempco*(TempChangeFromLastExternalCal)OffsetError=ResidualOffsetError+AOOffsetTempco*(TempChangeFromLastInternalCal)+INL_Error Refer to the following equation for an example of calculating absolute accuracy.Absolute accuracy at full scale on the analog output channels is determined using thefollowing assumptions:•TempChangeFromLastExternalCal = 10 °C•TempChangeFromLastInternalCal = 1 °CGainError=87.3ppm+12.6ppm*1+4ppm*10GainError=139.9ppmNI USB-7845R OEM Specifications| © National Instruments| 7OffsetError=41.1ppm+7.8ppm*1+61ppmOffsetError=109.9ppmAbsoluteAccuracy=10V*(GainError)+10V*(OffsetError)AbsoluteAccuracy=2,498µVDC Transfer CharacteristicsINL Refer to the AO Accuracy Table ............................................................................DNL±0.5 LSB typ, ±1 LSB max ............................................................................Monotonicity16 bits, guaranteed ............................................................................Dynamic CharacteristicsSlew rate-10 V/µs ............................................................................Noise250 µV rms, DC to 1 MHz ............................................................................Glitch energy at midscale transition±10 mV for 3 µs ............................................................................5V OutputOutput voltage 4.75 V to 5.1 V ............................................................................Output current0.5 A max ............................................................................Overvoltage protection±30 V ............................................................................ ............................................................................Overcurrent protection650 mA8| | NI USB-7845R OEM SpecificationsDigital I/OCompatibility LVTTL ............................................................................Logic family User-selectable ............................................................................Default software setting 3.3 V ............................................................................Maximum input 3.6 V ............................................................................NI USB-7845R OEM Specifications| © National Instruments| 9Table 10. Digital Output Logic Levels (Continued)Output currentSource 4.0 mA....................................................................Sink 4.0 mA....................................................................Input leakage current±15 µA max ............................................................................Input impedance50 kΩ typ, pull-down ............................................................................Power-on state Programmable, by line ............................................................................Protection±20 V, single line ............................................................................Digital I/O voltage switching time 2 ms max ............................................................................Note Refer to NI RIO Software Help for more information about switching times.Reconfigurable FPGAFPGA type Kintex-7 70T ............................................................................Number of flip-flops82,000 ............................................................................Number of LUTs41,000 ............................................................................Embedded block RAM4,860 kbits ............................................................................Number of DSP48 slices240 ............................................................................Timebase40, 80, 120, 160, or 200 MHz ............................................................................Timebase accuracy, onboard clock±100 ppm ............................................................................Calibration ............................................................................Recommended warm-up time15 minutesCalibration interval 1 year ............................................................................10| | NI USB-7845R OEM SpecificationsOnboard calibration referenceDC level3 5.000 V (±2 mV)....................................................................Temperature coefficient±4 ppm/°C max....................................................................Long-term stability±25 ppm/1,000 h....................................................................Note Refer to Calibration Certifications at /calibration to generate acalibration certificate for the NI USB-7845R OEM deviceBus Interface ............................................................................USB compatibility USB 2.0 Hi-Speed or Full-Speed4Data transfers DMA, interrupts, programmed I/O ............................................................................Number of DMA channels3 ............................................................................Power RequirementInput voltage9 V to 30 V ............................................................................Max power20 W ............................................................................ ............................................................................Overvoltage protection40 VNote You must use a UL Listed ITE power supply marked LPS with theNI USB-7845R OEM device.PhysicalNote If you need to clean the device, wipe it with a dry, clean towel.Dimensions (PCB)17.5 cm × 16.3 cm (6.9 in. × 6.4 in.) ............................................................................Weight183 g (6.45 oz) ............................................................................I/O connectors Analog- 1 × 50 pin box header, ............................................................................Digital- 3 × 34 pin box header3Actual value stored in Flash memory4Operating on a full-speed bus will result in lower performance and you might not be able to achieve maximum sampling/update rates.NI USB-7845R OEM Specifications| © National Instruments| 11Maximum Working VoltageMaximum working voltage refers to the signal voltage plus the common-mode voltage. Channel-to-earth±12 V, Measurement Category I ............................................................................Channel-to-channel±24 V, Measurement Category I ............................................................................Measurement Category I is for measurements performed on circuits not directly connected to the electrical distribution system referred to as MAINS voltage. MAINS is a hazardous live electrical supply system that powers equipment. This category is for measurements of voltages from specially protected secondary circuits. Such voltage measurements include signal levels, special equipment, limited-energy parts of equipment, circuits powered by regulated low-voltage sources, and electronics.Caution Do not use the NI USB-7845R OEM device for connection to signals inMeasurement Categories II, III, or IV.Note Measurement Categories CAT I and CAT O (Other) are equivalent. Thesetest and measurement circuits are not intended for direct connection to the MAINSbuilding installations of Measurement Categories CAT II, CAT III, or CAT IV. Environmental-40 °C to 70 °COperating temperature ............................................................................(IEC 60068-2-1, IEC 60068-2-2)Storage temperature-40 °C to 85 °C ............................................................................(IEC 60068-2-1, IEC 60068-2-2)10% to 90% RH, noncondensingOperating humidity ............................................................................(IEC 60068-2-56)Storage humidity (IEC 60068-2-56)5% to 95% RH, noncondensing ............................................................................ ............................................................................Pollution Degree2Maximum altitude2,000 m ............................................................................Indoor use only.Online Product CertificationTo obtain product certifications and the DoC for this product, visit /certification, search by model number or product line, and click the appropriate link in the Certification column.12| | NI USB-7845R OEM SpecificationsEnvironmental ManagementNI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.For additional environmental information, refer to the Minimize Our Environmental Impact web page at /environment. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.Waste Electrical and Electronic Equipment (WEEE)EU Customers At the end of the product life cycle, all products must be sent to aWEEE recycling center. For more information about WEEE recycling centers,National Instruments WEEE initiatives, and compliance withWEEE Directive 2002/96/EC on Waste Electrical and Electronic Equipment, visit/environment/weee.电子信息产品污染控制管理办法(中国RoHS)中国客户National Instruments符合中国电子信息产品中限制使用某些有害物质指令(RoHS)。

MX25L25635E, 3V, 256Mb, v1.3