LM4128DMFX-1.8中文资料

ISL28448中文资料

MDP0038

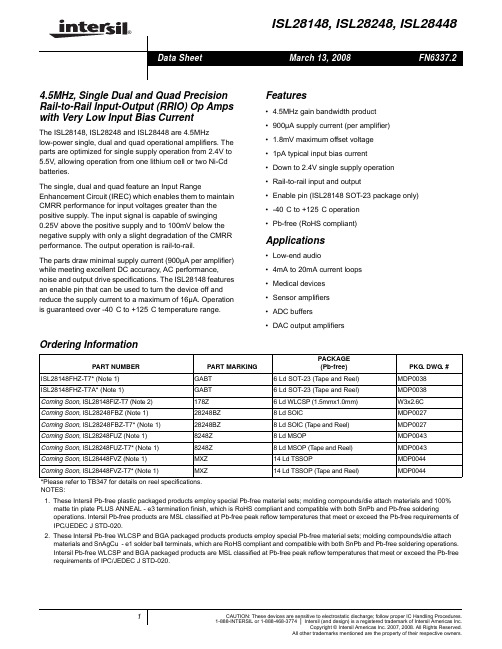

Coming Soon, ISL28148FIZ-T7 (Note 2)

178Z

6 Ld WLCSP (1.5mmx1.0mm)

W3x2.6C

Coming Soon, ISL28248FBZ (Note 1)

28248BZ

8 Ld SOIC

MDP0027

Coming Soon, ISL28248FBZ-T7* (Note 1)

Features

• 4.5MHz gain bandwidth product • 900µA supply current (per amplifier) • 1.8mV maximum offset voltage • 1pA typical input bias current • Down to 2.4V single supply operation • Rail-to-rail input and output • Enable pin (ISL28148 SOT-23 package only) • -40°C to +125°C operation • Pb-free (RoHS compliant)

2. These Intersil Pb-free WLCSP and BGA packaged products products employ special Pb-free material sets; molding compounds/die attach materials and SnAgCu - e1 solder ball terminals, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free WLCSP and BGA packaged products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

RT-241.81.8中文资料

ECONOLINE - DC/DC-Converter

RT Series, 1 Watt, DIP14, Isolated Outputs (Dual Output) Features

● ● ● ● ●

Twin Independent Outputs Output/Output Isolation 1kVDC Power Sharing on Outputs Input/Output Isolation 1kVDC No Heatsink Required

● ● ● ● ●

Toroidal Magnetics No Extern. Components Required Custom Solutions Available

UL94V-0 Package Material Efficiency to 80%

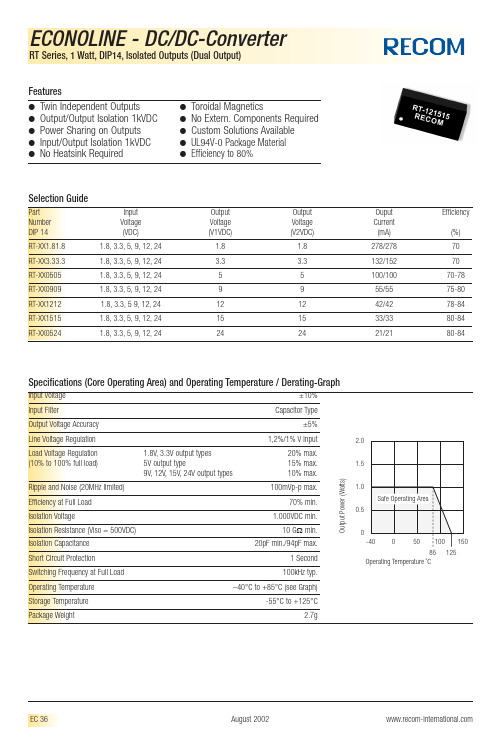

Selection Guide

Part Number DIP 14 RT-XX1.81.8 RT-XX3.33.3 RT-XX0505 RT-XX0909 RT-XX1212 RT-XX1515 RT-XX0524 Input Voltage (VDC) 1.8, 3.3, 5, 9, 12, 24 1.8, 3.3, 5, 9, 12, 24 1.8, 3.3, 5, 9, 12, 24 1.8, 3.3, 5, 9, 12, 24 1.8, 3.3, 5 9, 12, 24 1.8, 3.3, 5, 9, 12, 24 1.8, 3.3, 5, 9, 12, 24 Output Voltage (V1VDC) 1.8 3.3 5 9 12 15 24 Output Voltage (V2VDC) 1.8 3.3 5 9 12 15 24 Ouput Current (mA) 278/278 132/152 100/100 55/55 42/42 33/33 21/21 Efficiency (%) 70 70 70-78 75-80 78-84 80-84 80-84

MIC4128中文资料

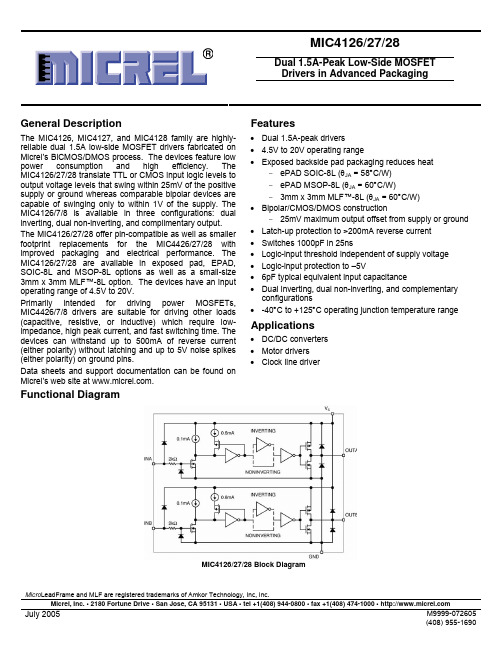

MIC4126/27/28Dual 1.5A-Peak Low-Side MOSFETDrivers in Advanced PackagingGeneral DescriptionThe MIC4126, MIC4127, and MIC4128 family are highly-reliable dual 1.5A low-side MOSFET drivers fabricated onMicrel’s BiCMOS/DMOS process. The devices feature lowpower consumption and high efficiency. TheMIC4126/27/28 translate TTL or CMOS input logic levels tooutput voltage levels that swing within 25mV of the positivesupply or ground whereas comparable bipolar devices arecapable of swinging only to within 1V of the supply. TheMIC4126/7/8 is available in three configurations: dualinverting, dual non-inverting, and complimentary output.The MIC4126/27/28 offer pin-compatible as well as smallerfootprint replacements for the MIC4426/27/28 withimproved packaging and electrical performance. TheMIC4126/27/28 are available in exposed pad, EPAD,SOIC-8L and MSOP-8L options as well as a small-size3mm x 3mm MLF™-8L option. The devices have an inputoperating range of 4.5V to 20V.Primarily intended for driving power MOSFETs,MIC4426/7/8 drivers are suitable for driving other loads(capacitive, resistive, or inductive) which require low-impedance, high peak current, and fast switching time. Thedevices can withstand up to 500mA of reverse current(either polarity) without latching and up to 5V noise spikes(either polarity) on ground pins.Data sheets and support documentation can be found onMicrel’s web site at .Features•Dual 1.5A-peak drivers• 4.5V to 20V operating range•Exposed backside pad packaging reduces heat–ePAD SOIC-8L (θJA = 58°C/W)–ePAD MSOP-8L (θJA = 60°C/W)–3mm x 3mm MLF™-8L (θJA = 60°C/W)• Bipolar/CMOS/DMOS construction–25mV maximum output offset from supply or ground•Latch-up protection to >200mA reverse current•Switches 1000pF in 25ns•Logic-input threshold independent of supply voltage•Logic-input protection to –5V•6pF typical equivalent input capacitance•Dual inverting, dual non-inverting, and complementaryconfigurations• -40°C to +125°C operating junction temperature rangeApplications• DC/DC converters• Motor drivers•Clock line driverFunctional DiagramMIC4126/27/28 Block DiagramOrdering InformationPin ConfigurationEPAD SOIC-8L (ME) EPAD MSOP-8L (MME)MLF-8L (ML)EPAD SOIC-8L (ME) EPAD MSOP-8L (MME)MLF-8L (ML)EPAD SOIC-8L (ME) EPAD MSOP-8L (MME)MLF-8L (ML)Pin DescriptionPin NumberPin NamePin Function1, 8 NC Not internally connected2 INA Control Input A: TTL/CMOS compatible logic input3 GND Ground4 INB Control Input B: TTL/CMOS compatible logic input.5 OUTB Output B: CMOS totem-pole output.6 V S Supply Input: +4.5V to +20V7 OUTA Output A: CMOS totem-pole output. EPGNDGround, backside pad.Part Number Configuration PackageJunction Temp. Range (1) Lead Finish MIC4126YME Dual Inverting EPAD 8-lead SOIC –40° to +125°C Pb-Free MIC4126YMME Dual Inverting EPAD 8-lead MSOP –40° to +125°C Pb-Free MIC4126YML Dual Inverting 8-lead MLF –40° to +125°C Pb-Free MIC4127YME Dual Non-inverting EPAD 8-lead SOIC –40° to +125°C Pb-Free MIC4127YMME Dual Non-inverting EPAD 8-lead MSOP –40° to +125°C Pb-Free MIC4127YML Dual Non-inverting 8-lead MLF –40° to +125°C Pb-Free MIC4128YME Inverting + Non-inverting EPAD 8-lead SOIC –40° to +125°C Pb-Free MIC4128YMME Inverting + Non-inverting EPAD 8-lead MSOP –40° to +125°C Pb-Free MIC4128YMLInverting + Non-inverting8-lead MLF–40° to +125°CPb-FreeAbsolute Maximum Ratings (1)Supply Voltage (V S)......................................................+24V Input Voltage (V IN)...........................V S + 0.3V to GND – 5V Junction Temperature (T J).........................................150°C Storage Temperature................................–65°C to +150°C Lead Temperature (10 sec.)......................................300°C ESD Rating, Note 3Operating Ratings (2)Supply Voltage (V S)......................................+4.5V to +20V Temperature Range (T J)...........................–40°C to +125°C Package Thermal Resistance3X3MLF™θJA.................................................60°C/W EPAD MSOP-8L θJA ...............................60°C/WEPADSOIC-8LθJA .................................58°C/WElectrical Characteristics (4)4.5V ≤ V S≤ 20V; Input voltage slew rate >1V/µs; C OUT = 1000pF. T A = 25°C, bold values indicate full specified temperature range;unless noted.Symbol Parameter Condition Min Typ Max Units InputV IH Logic 1 Input Voltage 2.42.41.41.6VV IL Logic 0 Input Voltage 1.11.30.80.8VI IN InputCurrent 0 ≤ V IN≤ V S–1 1 µA OutputV OH High Output Voltage V S–0.025 V V OL Low Output Voltage 0.025VR O Output Resistance I OUT = 10mA, V S = 20V 68 1012ΩI PK Peak Output Current 1.5 A I Latch-Up Protection Withstand reverse current >200 mA Switching Timet R Rise Time Test Figure 1 13203040nst F Fall Time Test Figure 1 15182540nst D1Delay Time Test Figure 1 37435060nst D2Delay Time Test Figure 1 40456070nsPower SupplyI S Power Supply Current V INA = V INB = 3.0V 1.41.54.58mAI S Power Supply Current V INA = V INB = 0.0V 0.180.190.40.6mANotes:1. Exceeding the absolute maximum rating may damage the device.2. The device is not guaranteed to function outside its operating rating.3. Devices are ESD sensitive. Handling precautions recommended. Human body model: 1.5kΩ in series with 100pF.4. Specification for packaged product only.Test CircuitFigure 1a. Inverting ConfigurationFigure 2a. Non-inverting ConfigurationFigure 1b. Inverting TimingFigure 2b. Non-inverting TimingTypical CharacteristicsApplication InformationSupply BypassingLarge currents are required to charge and discharge large capacitive loads quickly. For example, changing a 1000pF load by 16V in 25ns requires 0.8A from the supply input.To guarantee low supply impedance over a wide frequency range, parallel capacitors are recommended for power supply bypassing. Low-inductance ceramic MLC capacitors with short lead lengths (< 0.5") should be used. A 1.0µF film capacitor in parallel with one or two 0.1µF ceramic MLC capacitors normally provides adequate bypassing. GroundingWhen using the inverting drivers in the MIC4126 or MIC4128, individual ground returns for the input and output circuits or a ground plane are recommended for optimum switching speed. The voltage drop that occurs between the driver’s ground and the input signal ground, during normal high-current switching, will behave as negative feedback and degrade switching speed.The E-pad and MLF packages have an exposed pad under the package. It’s important for good thermal performance that this pad is connected to a ground plane.Control InputUnused driver inputs must be connected to logic high (which can be V S) or ground. For the lowest quiescent current (< 500µA), connect unused inputs-to-ground. A logic-high signal will cause the driver to draw up to 9mA. The control input voltage threshold is approximately 1.5V. The control input recognizes 1.5V up to V S as a logic high and draws less than 1µA within this range.Power DissipationPower dissipation should be calculated to make sure that the driver is not operated beyond its thermal ratings. Quiescent power dissipation is negligible. A practical value for total power dissipation is the sum of the dissipation caused by the load and the transition power dissipation (P L + P T).Load DissipationPower dissipation caused by continuous load current (when driving a resistive load) through the driver’s output resistance is:P L = I L2 R OFor capacitive loads, the dissipation in the driver is: P L = f C L V S2Transition DissipationIn applications switching at a high frequency, transition power dissipation can be significant. This occurs during switching transitions when the P-channel and N-channel output FETs are both conducting for the brief moment when one is turning on and the other is turning off.P T = 2 f V S QCharge (Q) is read from the following graph:Crossover Energy Loss per TransitionPackage Information8-Pin Exposed Pad SOIC (M)8-Pin Exposed Pad MSOP (MM)8-Pin MLF (ML)。

X84128I-1.8资料

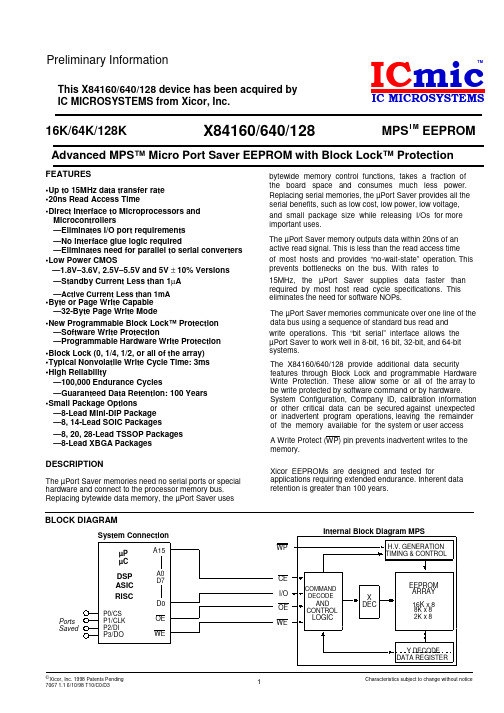

元器件交易网Preliminary InformationThis X84160/640/128 device has been acquired by IC MICROSYSTEMS from Xicor, Inc.ICmicTMIC MICROSYSTEMS16K/64K/128KX84160/640/128MPSTM EEPROMAdvanced MPS™ Micro Port Saver EEPROM with Block Lock™ ProtectionFEATURES•Up to 15MHz data transfer rate •20ns Read Access Time •Direct Interface to Microprocessors and Microcontrollers —Eliminates I/O port requirements —No interface glue logic required —Eliminates need for parallel to serial converters •Low Power CMOS —1.8V–3.6V, 2.5V–5.5V and 5V ± 10% Versions —Standby Current Less than 1µA —Active Current Less than 1mA •Byte or Page Write Capable —32-Byte Page Write Mode •New Programmable Block Lock™ Protection —Software Write Protection —Programmable Hardware Write Protection •Block Lock (0, 1/4, 1/2, or all of the array) •Typical Nonvolatile Write Cycle Time: 3ms •High Reliability —100,000 Endurance Cycles —Guaranteed Data Retention: 100 Years •Small Package Options —8-Lead Mini-DIP Package —8, 14-Lead SOIC Packages —8, 20, 28-Lead TSSOP Packages —8-Lead XBGA Packagesbytewide memory control functions, takes a fraction of the board space and consumes much less power. Replacing serial memories, the µPort Saver provides all the serial benefits, such as low cost, low power, low voltage, and small package size while releasing I/Os for more important uses. The µPort Saver memory outputs data within 20ns of an active read signal. This is less than the read access time of most hosts and provides “no-wait-state” operation. This prevents bottlenecks on the bus. With rates to 15MHz, the µPort Saver supplies data faster than required by most host read cycle specifications. This eliminates the need for software NOPs. The µPort Saver memories communicate over one line of the data bus using a sequence of standard bus read and write operations. This “bit serial” interface allows the µPort Saver to work well in 8-bit, 16 bit, 32-bit, and 64-bit systems. The X84160/640/128 provide additional data security features through Block Lock and programmable Hardware Write Protection. These allow some or all of the array to be write protected by software command or by hardware. System Configuration, Company ID, calibration information, or other critical data can be secured against unexpected or inadvertent program operations, leaving the remainder of the memory available for the system or user access A Write Protect (WP) pin prevents inadvertent writes to the memory. Xicor EEPROMs are designed and tested for applications requiring extended endurance. Inherent data retention is greater than 100 years.DESCRIPTIONThe µPort Saver memories need no serial ports or special hardware and connect to the processor memory bus. Replacing bytewide data memory, the µPort Saver usesBLOCK DIAGRAMSystem ConnectionµP µCA15 WPInternal Block Diagram MPSH.V. GENERATION TIMING & CONTROLDSP ASIC RISCPorts SavedP0/CS P1/CLK P2/DIA0 D7CE I/OCOMMAND DECODED0 OE WEOE WEAND CONTROLX DECEEPROM ARRAY 16K x 88K x 8 2K x 8LOGICP3/DOY DECODE DATA REGISTER© Xicor, Inc. 1998 Patents Pending7067 1.1 6/10/98 T10/C0/D31Characteristics subject to change without notice元器件交易网X84160/640/128PIN CONFIGURATIONS: Drawings are to the same scale, actual package sizes are shown in inches:8-LEAD PDIP 8-LEAD SOIC CE I/O WP V SS 1 2 X84160 3 X84640 4 .230 in. 8 7 6 5 V CC NC OE WE .190 in. NC VCC CE I/O 8-LEAD TSSOP 1 2 3 4 8 7 6 5 OE WE WP VSSPIN NAMES.114 in.X84160I/O CE OE WE WPData Input/Output Chip Enable Input Write Enable Input Supply Voltage Ground Output Enable Input Write Protect Input14-LEAD SOIC CE I/O NC NC NC WP V SS 1 2 3 4 5 6 7 .230 in. X84128 14 13 12 11 10 9 8 V CC NC NC NC NC OE WE .390 in.NC NC CE I/O NC NC NC WP VSS NC1 2 3 4 5 6 7 8 9 10X8464020 19 18 17 16 15 14 13 12 11NC NC VCC NC NC NC NC OE WE NC.250 in.roNC NC NC NC VCC NC NC .394 in. NC NC OE WE NC NC NC.252 in. 28-LEAD TSSOP NC NC CE CE CE I/O NC NC NC WP VSS NC NC NC 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 158-LEAD XBGA: Top View VCC 1 8 I/O .238 in. NC WE OE 2 7 CE 3 6 VSS 4 5 WPP2X84128e. 252 in..078 in.PIN DESCRIPTIONS Chip Enable (CE)ol etThe Chip Enable input must be LOW to enable all read/ write operations. When CE is HIGH, the chip is deselected, the I/O pin is in the high impedance state, and unless a nonvolatile write operation is underway, the device is in the standby power mode. Output Enable (OE) The Output Enable input must be LOW to enable the output buffer and to read data from the device on the I/O line.bsWrite Protect (WP) The Write Protect input controls the Hardware Write Protect feature. When WP is LOW and the nonvoltaile bit WPEN is “1”, nonvolatile writes of the X84160/640/128 control register is disabled, but the part otherwise functions normally. When WP is held HIGH, all functions, including nonvolatile write operate normally. WP going LOW while CS is still LOW will interrupt a write to the X84160/640/128 control register. If the internal Write cycle has already been initiated, WP going LOW will have no effect on write. The WP pin function is blocked when the WPEN bit in the control register is “0”. This allows the user to install the X84160/640/128 in a system with WP pin grounded and still be able to write to the control register. The WP pin functions will be enabled when the WPEN bit is set “1”.OWrite Enable (WE) The Write Enable input must be LOW to write either data or command sequences to the device. Data In/Data Out (I/O) Data and command sequences are serially written to or serially read from the device through the I/O pin.du cVCC VSS NC No Connect20-LEAD TSSOPPACKAGE SELECTION GUIDE841608-Lead PDIP 8-Lead SOIC 8-Lead TSSOP 8-Lead CSP/BGA 8-Lead PDIP 8-Lead SOIC 20-Lead TSSOP 8-Lead CSP/BGA 8-Lead PDIP 14-Lead SOIC 28-Lead TSSOP8464084128t.252 in.元器件交易网X84160/640/128DEVICE OPERATION The X84160/640/128 are serial EEPROMs designed to interface directly with most microprocessor buses. Standard CE, OE, and WE signals control the read and write operations, and a single l/O line is used to send and receive data and commands serially. Data Timing Data input on the l/O line is latched on the rising edge of either WE or CE, whichever occurs first. Data output on the l/O line is active whenever both OE and CE are LOW. Care should be taken to ensure that WE and OE are never both LOW while CE is LOW. Read Sequence A read sequence consists of sending a 16-bit address followed by the reading of data serially. The address is written by issuing 16 separate write cycles (WE and CE LOW, OE HIGH) to the part without a read cycle between the write cycles. The address is sent serially, most significant bit first, over the I/O line. Note that this sequence is fully static, with no special timing restrictions, and the processor is free to perform other tasks on the bus whenever the device CE pin is HIGH. Once the 16 address bits are sent, a byte of data can be read on the I/O line by issuing 8 separate read cycles (OE and CE LOW, WE HIGH). At this point, writing a ‘1’ will terminate the read sequence and enter the low power standby state, otherwise the device will await further reads in the sequential read mode. Sequential Read The byte address is automatically incremented to the next higher address after each byte of data is read. The data stored in the memory at the next address can be read sequentially by continuing to issue read cycles. When the highest address in the array is reached, the address counter rolls over to address 0000h and reading may be continued indefinitely. Reset Sequence The reset sequence resets the device and sets an internal write enable latch. A reset sequence can be sent at any time by performing a read/write “0”/read operation (see Figs. 1 and 2). This breaks the multiple read or write cycle sequences that are normally used to read from or write to the part. The reset sequence can be used at any time to interrupt or end a sequential read or page load. As soon as the write “0” cycle is complete, the part is reset (unless a nonvolatile write cycle is in progress). The second read cycle in this sequence, and any further read cycles, will read a HIGH on the l/O pin until a valid read sequence (which includes the address) is issued. The reset sequence must be issued at the beginning of both read and write sequences to be sure the device initiates these operations properly.Figure 1. Read SequenceCEObsOEWEol etI/O (IN)"0"A15 A14 A13 A12 A11 A10 A9 A8eP3A7 A6 A5 A4 A3 A2I/O (OUT) RESETWHEN ACCESSING: X84160 ARRAY: A15–A11=0 X84640 ARRAY: A15–A13=0 X84128 ARRAY: A15–A14=0LOAD ADDRESSroA1 A0du cD7 D6 D5 D4 D3 D2 D1 D0READ DATAt7008 FRM F04.1元器件交易网X84160/640/128Figure 2: Write SequenceCEOEWEI/O (IN)"0"A15 A14 A13 A12 A11 A10 A9 A8A7 A6 A5 A4 A3 A2 A1 A0du cD7 D6 D5 D4 D3 D2 D1 D0RESETWHEN ACCESSING: X84160 ARRAY: A15–A11=0 X84640 ARRAY: A15–A13=0 X84128 ARRAY: A15–A14=0LOAD ADDRESSroI/O (OUT)LOAD DATAP4ol etWrite Sequence A nonvolatile write sequence consists of sending a reset sequence, a 16-bit address, up to 32 bytes of data, and then a special “start nonvolatile write cycle” command sequence.epage, where data loading can continue. For this reason, sending more than 256 consecutive data bits will result in overwriting previous data. A nonvolatile write cycle will not start if a partial or incomplete write sequence is issued. The internal write enable latch is reset when the nonvolatile write cycle is completed and after an invalid write to prevent inadvertent writes. Note that this sequence is fully static, with no special timing restrictions. The processor is free to perform other tasks on the bus whenever the chip enable pin (CE) is HIGH. Nonvolatile Write Status The status of a nonvolatile write cycle can be determined at any time by simply reading the state of the l/O pin on the device. This pin is read when OE and CE are LOW and WE is HIGH. During a nonvolatile write cycle the l/O pin is LOW. When the nonvolatile write cycle is complete, the l/O pin goes HIGH. A reset sequence can also be issued during a nonvolatile write cycle with the same result: I/O is LOW as long as a nonvolatile write cycle is in progress, and l/O is HIGH when the nonvolatile write cycle is done.The nonvolatile write cycle is initiated by issuing a special read/write “1”/read sequence. The first read cycle ends the page load, then the write “1” followed by a read starts the nonvolatile write cycle. The device recognizes 32byte pages (e.g., beginning at addresses XXXXXX00000 for X84160). When sending data to the part, attempts to exceed the upper address of the page will result in the address counter “wrapping-around” to the first address on theObsThe reset sequence is issued first (as described in the Reset Sequence section) to set an internal write enable latch. The address is written serially by issuing 16 separate write cycles (WE and CE LOW, OE HIGH) to the part without any read cycles between the writes. The address is sent serially, most significant bit first, on the l/O pin. Up to 32 bytes of data are written by issuing a multiple of 8 write cycles. Again, no read cycles are allowed between writes.t"1" "0" START NONVOLATILE WRITE7008 FRM F05.1元器件交易网X84160/640/128CONTROL REGISTER The X84160/640/128 has one register that contains control bits for the devices. The control bits, WPEN, BP1, and BP0, are shown in Table 1. To read or change the contents of this register requires a one byte operation to address FFFFh. A read from FFFFh returns the one byte contents of the control register unused bits return 0. Continued reads return undefined data. A write to address FFFFh changes the value of the bits. Unused bits are written as “0”. Writing more than one byte to the control register is a violation and the operation will be aborted. After sending one byte to the control register, a start nonvolatile write cycle will latch in the new state. Table 1 7 WPEN 6 0 5 0 4 0 3 BP1 2 BP0 1 0 0 0 The Write Protect (WP) pin and the nonvolatile Write Protect Enable (WPEN) bit in the Status Register control the programmable hardware write protect feature. Hardware write protection is enabled when WP pin is LOW, and the WPEN bit is “1”. Hardware write protection is disabled when either the WP pin is HIGH or the WPEN bit is “0”. When the chip is hardware write protected, nonvolatile write is disabled to the Control Register, including the Block Protect bits and the WPEN bit itself, as well as the block-protected sections in the memory array. Only the sections of the memory array that are not block-protected can be written.Note: When the WP pin is tied to VSS and the WPEN bit is HIGH, the WPEN bit is write protected. It cannot be changed back to a “0”, as long as the WP pin is held LOW.WPEN 0 1 XWP X LOW HIGHProtected Blocks Protected ProtectedUnprotected Blocks Writable WritableProtectedTable 3. Block Lock ProtectionbsControl Register Bits BP1 0 0 1 1 BP0 0 1 0 1ol etWritableeWPEN: Write Protect Enable Bit The Write-Protect-Enable (WPEN) bit is an enable bit for the WP pin. Table 2Status Register WritableBP1, BP0: Block Protect Bits The Block Protect (BP0 and BP1) bits are nonvolatile and allow the user to select one of four levels of protection. The X84160/640/128 is divided into four segments. One, two, or all four of the segments may be protected. That is, the user may read the segments but will be unable to alter (write) data within the selected segments. The partitioning is controlled as illustrated in table 3 below.Protected WritableX84160 None 0600h–07FFh 0400h–07FFh 0000–07FFhPX84640 None5Array Address Protected X84128 None 3000h–3FFFh 2000h–3FFFh 0000h–3FFFh upper 1/4 upper 1/2 Full Array (Not including the control register.) Array1800h–1FFFh 1000h–1FFFh 0000–1FFFhOrodu ct元器件交易网X84160/640/128Low Power Operation The device enters an idle state, which draws minimal current when: —an illegal sequence is entered. The following are the more common illegal sequences: • Read/Write/Write—any time • Read/Write ‘1’—When writing the address or writing data. • Write ‘1’—when reading data • Read/Read/Write ‘1’—after data is written to device, but before entering the NV write sequence. —the device powers-up; —a nonvolatile write operation completes. While a sequential read is in progress, the device remains in an active state. This state draws more current than the idle state, but not as much as during a read itself. To go back to the lowest power condition, an invalid condition is created by writing a ‘1’ after the last bit of a read operation. Write Protection The following circuitry has been included to prevent inadvertent nonvolatile writes: —The internal Write Enable latch is reset upon power-up. —A reset sequence must be issued to set the internal write enable latch before starting a write sequence. —A special “start nonvolatile write” command sequence is required to start a nonvolatile write cycle.—The internal Write Enable latch is reset and remains reset as long as the WP pin is LOW, which blocks all nonvolatile write cycles. —The internal Write Enable latch resets on an invalid write operation. SYMBOL TABLEroWAVEFORM 6PeObsol etdu cINPUTS Must be steady May change from LOW to HIGH May change from HIGH to LOW Don’t Care: Changes Allowed N/A Will be steadyOUTPUTSWill change from LOW to HIGH Will change from HIGH to LOW Changing: State Not Known Center Line is High Impedancet—The internal Write Enable latch is reset automatically at the end of a nonvolatile write cycle.元器件交易网X84160/640/128ABSOLUTE MAXIMUM RATINGS* Temperature under Bias ...................... –65°C to +135°C Storage Temperature ........................... –65°C to +150°C Terminal Voltage with Respect to VSS .......................................–1V to +7V DC Output Current................................................... 5mA Lead Temperature (Soldering, 10 seconds)..........300°C RECOMMENDED OPERATING CONDITIONS Temperature Commercial Industrial Min. 0°C –40°C Max. +70°C +85°C +125°C *COMMENT Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Supply Voltage X84160/640/128X84160/640/128 – 2.5 X84160/640/128 – 1.8D.C. OPERATING CHARACTERISTICS (VCC = 5V ±10%) (Over the recommended operating conditions, unless otherwise specified.) Symbol ICC1 Parameter VCC Supply Current (Read) Min.PMax. 12 1 10 10 VCC x 0.3 VCC + 0.5 0.47LimitsroUnits mA Test Conditions OE = VIL, WE = VIH, I/O = Open, CE clocking = VCC x 0.1/VCC x 0.9 @ 10 MHzICC During Nonvolatile Write Cycle All Inputs at CMOS Levels CE = VCC, Other Inputs = VCC or VSS VIN = VSS to VCC VOUT = VSS to VCC mA µA µA µA V V V V IOL = 2.1mA IOH = –1mAMilitary† –55°C Notes: † Contact factory for Military availabilityISB1 ILI ILO VlL (1) VIH(1)VCC Standby CurrentInput Leakage CurrentOutput Leakage Current Input LOW VoltageInput HIGH VoltagebsVOLOutput LOW Voltage Output HIGH Voltage VCC – 0.8VOHNotes: (1) VIL Min. and VIH Max. are for reference only and are not tested.Ool etICC2VCC Supply Current (Write)e–0.5VCC x 0.7du ctLimits 4.5V to 5.5V 2.5V to 5.5V 1.8V to 3.6V元器件交易网X84160/640/128D.C. OPERATING CHARACTERISTICS (VCC = 2.5V to 5.5V) (Over the recommended operating conditions, unless otherwise specified.) Symbol Parameter Limits Min. Max. 300 Units Test Conditions OE = VIL, WE = VIH, I/O = Open, CE clocking = VCC x 0.1/VCC x 0.9 @ VCC = 2.5, 5 MHz ICC During Nonvolatile Write Cycle All Inputs at CMOS Levels CE = VCC, Other Inputs = VCC or VSS VIN = VSS to VCC VOUT = VSS to VCCICC1VCC Supply Current (Read)µAICC2 ISB1 ILI ILO VlL(1) VIH(1) VOL VOHVCC Supply Current (Write) VCC Standby Current Input Leakage Current Output Leakage Current Input LOW Voltage Input HIGH Voltage Output LOW Voltage Output HIGH Voltage VCC – 0.4 –0.5 VCC x 0.72 1 10 10 VCC x 0.3mA µA µA µA VVCC + 0.5 0.4PMax. 200 1 1 10 10 VCC x 0.3 VCC + 0.5 0.48ol etSymbolParametereD.C. OPERATING CHARACTERISTICS (VCC = 1.8V to 3.6V) (Over the recommended operating conditions, unless otherwise specified.) Limits Min. Units Test Conditions OE = VIL, WE = VIH, I/O = Open, CE clocking = VCC x 0.1/VCC x 0.9 @ VCC = 1.8V, 4 MHz ICC During Nonvolatile Write Cycle All Inputs at CMOS Levels CE = VCC, Other Inputs = VCC or VSS VIN = VSS to VCC VOUT = VSS to VCCICC1VCC Supply Current (Read)ICC2 ISB1 ILI ILOVCC Supply Current (Write) VCC Standby CurrentbsInput Leakage Current Output Leakage Current Input LOW Voltage Input HIGH Voltage Output LOW Voltage Output HIGH Voltage VCC – 0.2 –0.5 VCC x 0.7VlL(1)OVIH(1) VOL VOHNotes: (1) VIL Min. and VIH Max. are for reference only and are not tested.roV V V µA mA µA µA µA V V V Vdu cIOL = 1mA, VCC = 3V IOH = –400µA, VCC = 3V IOL = 0.5mA, VCC = 2V IOH = –250µA, VCC = 2Vt元器件交易网X84160/640/128CAPACITANCE Symbol CI/O(2) CIN(2) TA = +25°C, f = 1MHz, VCC = 5V Parameter Input/Output Capacitance Input Capacitance Max. 8 6 Units pF pF Test Conditions VI/O = 0V VIN = 0VPOWER-UP TIMING Symbol tPUR(3) tPUW(3) Parameter Power-up to Read Operation Power-up to Write OperationA.C. CONDITIONS OF TEST Input Pulse Levels Input Rise and Fall Times Input and Output Timing Levels5nsVCC x 0.5EQUIVALENT A.C. LOAD CIRCUITS5V 2.06KΩ OUTPUT 3.03KΩol eteP3V 2.8K Ω OUTPUT 30pF 5.6K Ω 30pF 2V9VCC x 0.1 to VCC x 0.92.39KΩOUTPUT30pF4.58KΩObsroNotes: (3) Time delays required from the time the VCC is stable until the specific operation can be initiated. Periodically sampled, but not 100% tested.du cMax. 2 5Notes: (2) Periodically sampled, but not 100% tested.tUnits ms ms元器件交易网X84160/640/128A.C. CHARACTERISTICS (Over the recommended operating conditions, unless otherwise specified.) Read Cycle Limits – X84160/640/128 VCC = 4.5V – 5.5V VCC = 2.5V – 5.5V VCC = 1.8V – 3.6V SymboltRC tCE tOE tOEL tOEH tLOW tHIGH tLZ(4)ParameterRead Cycle Time CE Access Time OE Access Time OE Pulse Width OE High Recovery Time CE LOW Time CE HIGH Time CE LOW to Output In Low Z CE HIGH to Output In High Z OE LOW to Output In Low Z OE HIGH to Output In High Z Output Hold from CE or OE HIGH WE HIGH Setup Time WE HIGH Hold TimeMin.70MaxMin.125Max.Min.25020 20 20 50 20 50 0 0 0 0 0 25 15 35 90 35 90 0du c25 70 25 70 70 180 70 180 0 0 0 25 0 0 25 25 30 30 25t OEH t OHZ HIGH Z t HZro0 0 0 0 25 25tHIGH tWEH tOHtHZ(4) tOLZ(4) tOHZ tOH tWES tWEH(4)P15e25Notes: (4) Periodically sampled, but not 100% tested. tHZ and tOHZ are measured from the point where CE or OE goes HIGH (whichever occurs first) to the time when I/O is no longer being driven into a 5pF load.ol ettRC tLOWtCECEbsWEtWES tOEt OELOEOI/Ot OLZ t LZDATA10tMax.Unitsns ns ns ns ns ns ns ns ns ns ns ns ns nsOb so l et ePr od u ctX84160/640/128Write Cycle Limits – X84160/640/128Notes:(5)t NVWC sequence until the self-timed, internal nonvolatile write cycle is completed.(6)Data is latched into the X84160/640/128 on the rising edge of CE or WE, whichever occurs first.(7)Periodically sampled, but not 100% tested.Symbol ParameterV CC = 4.5V – 5.5V V CC = 2.5V – 5.5V V CC = 1.8V – 3.6VUnits Min.Max.Min.Max.Min.Max.t NVWC (5)Nonvolatile Write Cycle Time 555ms t WCWrite Cycle Time70125250nst WP WE Pulse Width203550ns t WPH WE HIGH Recovery Time 5090180ns t CS Write Setup Time 000ns t CH Write Hold Time 000ns t CP CE Pulse Width203570ns t CPH CE HIGH Recovery Time 5090180ns t OES OE HIGH Setup Time 252550ns t OEH OE HIGH Hold Time 252550ns t DS (6)Data Setup Time 122030ns t DH (6)Data Hold Time 555ns t WPSU (7)WP HIGH Setup 100100150ns t WPHD (7)WP HIGH Hold100100150nsX84160/640/128CE Controlled Write CycleWE Controlled Write CycleOb soctX84160/640/1288-LEAD XBGA TYPE430±20X84640Z: Bottom ViewNOTE: ALL DIMENSIONS IN µMALL DIMENSIONS ARE TYPICAL VALUES20Ob soctX84160/640/1288-LEAD XBGA TYPEX84128: Bottom ViewNOTE: ALL DIMENSIONS IN µMALL DIMENSIONS ARE TYPICAL VALUES20Ob s octX84160/640/128NO TE:1.ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)2.PACKAGE DIMENSIONS EXCLUDE MOLDING FLASHTYP .8-LEAD PLASTIC DUAL IN-LINE P ACKAGE TYPE PHALF SHOULDER ALL MAX.X84160/640/1288-LEAD PLASTIC SMALL OUTLINE GULL WING P ACKAGE TYPE SNOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)X84160/640/128PACKAGING INFORMATION14-LEAD PLASTIC SMALL OUTLINE GULL WING P ACKAGE TYPE SNOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)Ob sou ctX84160/640/128PACKAGING INFORMATIONNOTE:ALL DIMENSIONS IN INCHES (IN P ARENTHESES IN MILLIMETERS)8-LEAD PLASTIC, TSSOP , PACKAGE TYPE V0° – 8°Ob so lt u ctX84160/640/128PACKAGING INFORMATIONNOTE:ALL DIMENSIONS IN INCHES (IN P ARENTHESES IN MILLIMETERS)20-LEAD PLASTIC, TSSOP PACKAGE TYPE V0° – 8Gage Plane Seating PlaneOb so lu ctX84160/640/128PACKAGING INFORMATIONNOTE:ALL DIMENSIONS IN INCHES (IN P ARENTHESES IN MILLIMETERS)28-LEAD PLASTIC, TSSOP PACKAGE TYPE V0° – 8Gage Plane Seating PlaneX84160/640/128LIMITED WARRANTYDevices sold by Xicor, Inc. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Xicor, Inc. makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Xicor, Inc. makes no warranty of merchantability or fitness for any purpose. Xicor, Inc. reserves the right to discontinue production and change specifications and prices at any time and without notice.Xicor, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Xicor, Inc. product. No other circuits, patents, licenses are implied.U.S. PATENTSXicor products are covered by one or more of the following U.S. Patents: 4,263,664; 4,274,012; 4,300,212; 4,314,265; 4,326,134; 4,393,481; 4,404,475;4,450,402; 4,486,769; 4,488,060; 4,520,461; 4,533,846; 4,599,706; 4,617,652; 4,668,932; 4,752,912; 4,829, 482; 4,874, 967; 4,883, 976. Foreignpatents and additional patents pending.LIFE RELATED POLICYIn situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurence.Xicor's products are not authorized for use in critical components in life support devices or systems.1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustainlife, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failureof the life support device or system, or to affect its safety or effectiveness.22。

X24320PIG-1.8资料

元器件交易网This X24320 device has been acquired by IC MICROSYSTEMS from Xicor, Inc.ICmicTMIC MICROSYSTEMS32KX24320400KHz 2-Wire Serial E PROM with Block Lock2 TM4K x 8 BitFEATURES•Save Critical Data with ProgrammableBlock Lock Protection 2 —Block Lock (0, 1/4, 1/2, or all of E PROM Array) —Software Write ProtectionDESCRIPTION 2 The X24320 is a CMOS Serial E PROM, internally organized 4K x 8. The device features a serial interface and software protocol allowing operation on a simple two wire bus. The bus operates at 400 KHz all the way down to 1.8V. Three device select inputs (S0–S2) allow up to eight devices to share a common two wire bus. A Write Protect Register at the highest address location, FFFFh, provides three write protection features: Software Write Protect, Block Lock Protect, and Programmable Hardware Write Protect. The Software Write Protect feature prevents any nonvolatile writes to the device until the WEL bit in the Write Protect Register is set. The Block Lock Protection feature gives the user four array block protect options, set by programming two bits in the Write Protect Register. The Programmable Hardware Write Protect feature allows the user to install the device with WP tied to VCC, write to and Block Lock the desired portions of the memory array in circuit, and then enable the In Circuit Programmable ROM Mode by programming the WPEN bit HIGH in the Write Protect Register. After this, the Block Locked portions of the array, including the Write Protect Register itself, are permanently protected from being erased.•In Circuit Programmable ROM Mode •400KHz 2-Wire Serial Interface—Programmable Hardware Write Protect—Schmitt Trigger Input Noise Suppression —Output Slope Control for Ground BounceNoise Elimination •Longer Battery Life With Lower Power —Active Read Current Less Than 1mA —Active Write Current Less Than 3mA —Standby Current Less Than 1µA •1.8V to 3.6V, 2.5V to 5.5V and 4.5V to 5.5V Power Supply Versions •32 Word Page Write Mode —Minimizes Total Write Time Per Word•Internally Organized 4K x 8 •Bidirectional Data Transfer Protocol •Self-Timed Write Cycle—Typical Write Cycle Time of 5ms •High Reliability —Endurance: 100,000 Cycles —Data Retention: 100 Years•8-Lead SOIC •14-Lead TSSOP •8-Lead PDIPFUNCTIONAL DIAGRAMSERIAL E PROM DATA AND ADDRESS (SDA)2DATA REGISTER Y DECODE LOGICCOMMAND DECODE AND CONTROLSERIAL E PROM ARRAY2SCLPAGE DECODE4K x 8 1K x 8LOGICBLOCK LOCK AND WRITE PROTECT CONTROL LOGICLOGIC1K x 8WRITE PROTECTS2 S1 S0DEVICE SELECTLOGICREGISTER2K x 8WPWRITE VOLTAGE CONTROL7035 FM 01©Xicor, 1995, 1996 Patents Pending 7035-1.2 4/25/97 T0/C2/D0 SH1Characteristics subject to change without notice元器件交易网X24320Xicor E PROMs are designed and tested for applications requiring extended endurance. Inherent data2PIN NAMES SymbolS0, S1, S2 SDA SCL WP VSS VCC NCretention is greater than 100 years.PIN DESCRIPTIONS Serial Clock (SCL)DescriptionDevice Select Inputs Serial Data Serial Clock Write Protect Ground Supply Voltage No Connect7035 FM T01The SCL input is used to clock all data into and out of the device.Serial Data (SDA) SDA is a bidirectional pin used to transfer data into and out of the device. It is an open drain output and may be wire-ORed with any number of open drain or open collector outputs. An open drain output requires the use of a pull-up resistor. For selecting typical values, refer to the Pullup resistor selection graph at the end of this data sheet. Device Select (S0, S1, S2) The device select inputs (S0, S1, S2) are used to set the first three bits of the 8-bit slave address. This allows up to eight devices to share a common bus. These inputs can be static or actively driven. If used statically they must be tied to VSS or VCC as appropriate. If actively driven, they must be driven with CMOS levels (driven to VCC or VSS). Write Protect (WP) The Write Protect input controls the Hardware Write Protect feature. When held LOW, Hardware Write Protection is disabled. When this input is held HIGH, and the WPEN bit in the Write Protect Register is set HIGH, the Write Protect Register is protected, preventing changes to the Block Lock Protection andPIN CONFIGURATIONNot to scale 8-Lead DIP/SOICS 0S1 2 3 4 * .244” X243208 7 6 5V* .197”1 2CC WPSV SSSCL SDA14-Lead TSSOPS 01 NC S1 2 3 4 5 6 7 .252”14 13 12 X24320 11 10 9 8V CC WP.200”NC NCV SS S 2NC NCNC SCL SDAWPEN bits.* SOIC Measurement7035 FM 022元器件交易网X24320Clock and Data Conventions Data states on the SDA line can change only during SCL LOW. SDA state changes during SCL HIGH are reserved for indicating start and stop conditions. Refer to Figures 1 and 2. Start Condition All commands are preceded by the start condition, which is a HIGH to LOW transition of SDA when SCL is HIGH. The device continuously monitors the SDA and SCL lines for the start condition and will not respond to any command until this condition has been met.DEVICE OPERATION The device supports a bidirectional bus oriented protocol. The protocol defines any device that sends data onto the bus as a transmitter, and the receiving device as the receiver. The device controlling the transfer is a master and the device being controlled is the slave. The master will always initiate data transfersand provide the clock for both transmit and receive operations. Therefore, the device will beconsidered a slave in all applications.Figure 1. Data ValiditySCLSDA DATA STABLE DATA CHANGE7035 FM 03Figure 2. Definition of Start and StopSCLSDA START BIT STOP BIT7035 FM 043元器件交易网X24320Stop ConditionAll communications must be terminated by a stop condition, which is a LOW to HIGH transition of SDA when SCL is HIGH. The stop condition is also used to place the device into the standby power mode after a read sequence. A stop condition can only be issued after the transmitting device has released the bus. Acknowledge Acknowledge is a software convention used to indicate successful data transfer. The transmitting device, either master or slave, will release the bus after trans- mitting eight bits. During the ninth clock cycle the receiver will pull the SDA line LOW to acknowledge that it received the eight bits of data. Refer to Figure 3. The device will respond with an acknowledge after recognition of a start condition and its slave address. If both the device and a write operation have been selected, the device will respond with an acknowledge after the receipt of each subsequent 8-bit word. In the read mode the device will transmit eight bits of data, release the SDA line and monitor the line for an acknowledge. If an acknowledge is detected and no stop condition is generated by the master, the device will continue to transmit data. If an acknowledge is not detected, the device will terminate further data transmissions. The master must then issue a stop condition return the device to the standby power mode and place the device into a known state. toFigure 3. Acknowledge Response From ReceiverSCL FROM MASTER189DATA OUTPUT FROMTRANSMITTERDATA OUTPUT FROM RECEIVERSTARTACKNOWLEDGE7035 FM 054元器件交易网X24320DEVICE ADDRESSING Following a start condition, the master must output the address of the slave it is accessing. The first four bits of the Slave Address Byte are the device type identifier bits. These must equal “1010”. The next 3 bits are the device select bits S0, S1, and S2. This allows up to 8 devices to share a single bus. These bits arecompared to the S0, S1, and S2 device select input pins. The last bit of the Slave Address Byte defines thedevice select input pins. If the compare is not successful, no acknowledge is output during the ninth clock cycle and the device returns to the standby mode. The word address is either supplied by the master or obtained from an internal counter, depending on the operation. The master must supply the two Word Address Bytes as shown in figure 4. The internal organization of the E array is 128 pages by 32 bytes per page. The page address is partially contained in the Word Address Byte 1 and partially in bits 7 through 5 of the Word Address Byte 0. The byte address is contained in bits 4 through 0 of the Word Address Byte 0. See figure 4.2operation to be performed. When the R/W bit is a one, then a read operation is selected. When it is zero thena write operation is selected. Refer to figure 4. After loading the Slave Address Byte from the SDA bus, the device compares the device type bits with the value “1010” and the device select bits with the status of theFigure 4. Device AddressingDEVICE TYPE IDENTIFIERDEVICE SELECT1010S 2S 1S 0R/WSLAVE ADDRESS BYTEHIGH ORDER WORD ADDRESS0000A11A10A9A8X24320 WORD ADDRESS BYTE 1LOW ORDER WORD ADDRESSA7A6A5A4A3A2A1A0WORD ADDRESS BYTE 0D7D6D5D4D3D2D1D0DATA BYTE7035 FM 065元器件交易网X24320WRITE OPERATIONS Byte Write For a write operation, the device requires the Slave Address Byte, the Word Address Byte 1, and the Word Address Byte 0, which gives the master access to any one of the words in the array. Upon receipt of the Word Address Byte 0, the device responds with an acknowledge, and waits for the first eight bits of data. After receiving the 8 bits of the data byte, the device again responds with an acknowledge. The master then terminates the transfer by generating a stop condition, at which time the device begins the internal write cycle to the nonvolatile memory. While the internal write cycle is in progress the device inputs are disabled and the device will not respond to any requests from the master. The SDA pin is at high impedance. See figure 5. Page Write The device is capable of a thirty-two byte page write operation. It is initiated in the same manner as the byte write operation; but instead of terminating the write operation after the first data word is transferred, the master can transmit up to thirty-one more words. The device will respond with an acknowledge after the receipt of each word, and then the byte address is internally incremented by one. The page address remains constant. When the counter reaches the end of the page, it “rolls over” and goes back to the first byte of the current page. This means that the master can write 32 words to the page beginning at any byte. If the master begins writing at byte 16, and loads 32 words, then the first 16 words are written to bytes 16 through 31, and the last 16 words are written to bytes 0 through 15. Afterwards, the address counter would point to byte 16. If the master writes more than 32 words, then the previously loaded data is overwritten by the new data, one byte at a time. The master terminates the data byte loading by issuing a stop condition, which causes the device to begin the nonvolatile write cycle. As with the byte write operation, all inputs are disabled until completion of the internal write cycle. Refer to figure 6 for the address, acknowledge, and data transfer sequence.Figure 5. Byte Write SequenceS TSIGNALS FROM THE MASTERA RSLAVE ADDRESSWORD ADDRESS BYTE 1WORD ADDRESS BYTE 0DATAS TO PT SDA BUSSIGNALS FROM THE SLAVES10100A C A C A C A CPKKKK7035 FM 07Figure 6. Page Write Sequence(0=n=31)SIGNALS FROM THE MASTER S TA RSLAVE ADDRESSWORD ADDRESS BYTE 1WORD ADDRESS BYTE 0DATA (0)DATA (n)S TO PT SDA BUSSIGNALS FROM THE SLAVES 10100A C A C A C A C A CPKKKKK7035 FM 086元器件交易网X24320Acknowledge Polling The maximum write cycle time can be significantly reduced using Acknowledge Polling. To initiateREAD OPERATIONSRead operations are initiated in the same manner as write operations with the exception that the R/W bit of the Slave Address Byte is set to one. There are three basic read operations: Current Address Reads, Random Reads, and Sequential Reads. Current Address Read Internally, the device contains an address counter that maintains the address of the last word read or written incremented by one. After a read operation from the last address in the array, the counter will “roll over” to the first address in the array. After a write operation to the last address in a given page, the counter will “roll over” to the first address on the same page. Upon receipt of the Slave Address Byte with the R/W bit set to one, the device issues an acknowledge and then transmits the eight bits of the Data Byte. The master terminates the read operation when it does not respond with an acknowledge during the ninth clock and then issues a stop condition. Refer to figure 8 for the address acknowledge, and data transfer sequence.Acknowledge Polling, the master issues a start condition followed by the Slave Address Byte for a write or read operation. If the device is still busy with the internal write cycle, then no ACK will be returned. If thedevice has completed the internal write operation, an ACK will be returned and the host can then proceedwith the read or write operation. Refer to figure 7 . Figure 7. Acknowledge Polling SequenceBYTE LOAD COMPLETED BY ISSUING STOP.ENTER ACK POLLINGISSUE STARTISSUE SLAVE ADDRESS BYTEISSUE STOP(READ OR WRITE)ACK RETURNED?NOIt should be noted that the ninth clock cycle of the read operation is not a “don’t care " .” To terminate a read operation, the master must either issue a stop condition during the ninth cycle or hold SDA HIGH during the ninth clock cycle and then issue a stop condition.YESHIGH VOLTAGE CYCLE COMPLETE. CONTINUENOFigure 8. Current Address Read SequenceSIGNALS FROM THE MASTERS TSEQUENCE?YES SDA BUSCONTINUE NORMAL READ OR WRITEA RSLAVE ADDRESSS TO PT S 1 01 0 1A CP DATA7035 FM 10ISSUE STOPCOMMAND SEQUENCESIGNALS FROM THE SLAVEKPROCEED7035 FM 097元器件交易网X24320Random Read Random read operation allows the master to access any memory location in the array. Prior to issuing the Slave Address Byte with the R/W bit set to one, the master must first perform a “Dummy” write operation. The master issues the start condition and the Slave Address Byte with the R/W bit low, receives an acknowledge, then issues the Word Address Byte 1, receives another acknowledge, then issues the Word Address Byte 0. After the device acknowledges receipt of the Word Address Byte 0, the master issues another start condition and the Slave Address Byte with the R/W bit set to one. This is followed by an acknowledge and then eight bits of data from the device. The master terminates the read operation by not responding with an acknowledge and then issuing a stop condition. Refer to figure 9 for the address, acknowledge, and data transfer sequence. The device will perform a similar operation called “Set Current Address” if a stop is issued instead of the second start shown in figure 9. The device will go into standby mode after the stop and all bus activity will be ignored until a start is detected. The effect of this operation is that the new address is loaded into the address counter, but no data is output by the device. The next Current Address Read operation will read from the newly loaded address. Sequential Read Sequential reads can be initiated as either a current address read or random read. The first Data Byte is transmitted as with the other modes; however, the master now responds with an acknowledge, indicating it requires additional data. The device continues to output data for each acknowledge received. The master terminates the read operation by not with an acknowledge and then issuing a stop condition. respondingThe data output is sequential, with the data from address n followed by the data from address n + 1. The address counter for read operations increments through all byte addresses, allowing the entire memory contents to be read during one operation. At the end of the address space the counter “rolls over ” to address 0000h and the device continues to output data for each acknowledge received. Refer to figure 10 for the acknowledge and data transfer sequence.Figure 9. Random Read SequenceSIGNALS FROM THE MASTER S T S TA RSLAVE ADDRESSWORD ADDRESS BYTE 1WORD ADDRESS BYTE 0A RSLAVE ADDRESSS TO PT SDA BUSSIGNALS FROM THE SLAVET 0A C A C A CS1 0 1 0S1A CPKKKKDATA7035 FM 11Figure 10. Sequential Read SequenceSIGNALS FROM THE MASTER SLAVE ADDRESS A C A C A CS TO PK 1A CKKSDA BUSSIGNALS FROM THE SLAVESPKDATA (1)DATA (2)DATA (n–1)DATA (n)(n is any integer greater than 1)7035 FM 128元器件交易网X24320WRITE PROTECT REGISTER (WPR) Writing to the Write Protect RegisterThe Write Protect Register can only be modified by performing a “ByteWrite” operation directly to the address FFFFh as described below. The Data Byte must contain zeroes where indicated in the procedural descriptions below; otherwise the operation will not be performed. Only one Data Byte is allowed for each register write operation. The part will not acknowledge any data bytes after the first byte is entered. The user then has to issue a stop to initiate the nonvolatile write cycle that writes BL0, BL1, and WPEN to the nonvolatile bits. A stop must also be issued after volatile register write operations to put the device into Standby. The state of the Write Protect Register can be read by performing a random byte read at FFFFh at any time. The part will reset itself after the first byte is read. The master should supply a stop condition to be consistent with the protocol, but a stop is not required to end this operation. After the read, the address counter contains WPEN: Write Protect Enable Bit (Nonvolatile) The Write Protect (WP) pin and the Write Protect Enable (WPEN) bit in the Write Protect Register control the Programmable Hardware Write Protection feature. Hardware Write Protection is enabled when the WP pin is HIGH and the WPEN bit is HIGH, and disabled when either the WP pin is LOW or the WPEN bit is LOW. Figure 12 defines the write protect status for each combination of WPEN and WP. When the chip is Hardware Write Protected, nonvolatile writes are disabled to the Write Protect Register, including the Block Lock Protect bits and the WPEN bit itself, as well as to the Block Lock protected sections in the memory array. Only the sections of the memory array that are not Block Lock protected, and the volatile bits WEL and RWEL, can be written. In Circuit Programmable ROM Mode Note that when the WPEN bit is write protected, it cannot be changed back to a LOW state; so write protection is enabled as long as the WP pin is held HIGH. Thus an In Circuit Programmable ROM function can be implemented by hardwiring the WP pin to VCC, writing to and Block Locking the desired portion of the array to be ROM, and then programming the WPEN bit HIGH. 0 0 Unused Bit Positions Bits 0, 5 & 6 are not used. All writes to the WPR must have zeros in these bit positions. The data byte output during a WPR read will contain zeros in these bits. Writing to the WEL and RWEL bits WEL and RWEL are volatile latches that power up in the LOW (disabled) state. While the WEL bit is LOW, writes to any address other than FFFFh will be ignored (no acknowledge will be issued after the Data Byte). The WEL bit is set by writing 00000010 to address FFFFh. Once set, WEL remains HIGH until either it is reset to 0 (by writing 00000000 to FFFFh) or until the part powers up again. Writes to WEL and RWEL do not cause a nonvolatile write cycle, so the device is ready for the next operation immediately after the stop condition. The RWEL bit controls writes to the Block Lock Protect bits, BL0 and BL1, and the WPEN bit. If RWEL is 0 then no writes can be performed on BL0, BL1, or WPEN. RWEL is reset when the device powers up or after any nonvolatile write, including writes to the Block Lock Protect bits, WPEN bit, or any bytes in the memory array. When RWEL is set, WEL cannot be0000h. Write Protect Register: WPR (ADDR = FFFFh)7 WPEN 6 0 5 0 4 BL1 3 BL0 2 1RWEL WELWEL: Write Enable Latch (Volatile) 0 = Write Enable Latch reset, writes disabled.1 = Write Enable Latch set, writes enabled.RWEL: Register Write Enable Latch (Volatile) 0 = Register Write Enable Latch reset, writes to the Write Protect Register disabled. 1 = Register Write Enable Latch set, writes to the Write Protect Register enabled.BL0, BL1: Block Lock Protect Bits (Nonvolatile) TheBlock Lock Protect Bits, BL0 and BL1, determine which blocks of the array are protected. A write to a protected block of memory is ignored, but will receive an acknowledge. The master must issue a stop to put the part into standby, just as it would for a valid write; but the stop will not initiate an internal nonvolatile write cycle. See figure 11.9元器件交易网X24320reset, nor can RWEL and WEL be reset in one write operation. RWEL can be reset by writing 00000010 toFFFFh; but this is the same operation as in step 3 described below, and will result in programing BL0, step 2. RWEL is reset to zero in step 3 so that user is required to perform steps 2 and 3 to make another change. RWEL must be 0 in step 3. If the RWEL bit in the data byte for step 3 is a one, then no changes are made to the Write Protect Register and the device remains at step 2. The WP pin must be LOW or the WPEN bit must be LOW before a nonvolatile register write operation is initiated. Otherwise, the write operation will abort and the device will go into standby mode after the master issues the stop condition in step 3. Step 3 is a nonvolatile write operation, requiring tWC to complete (acknowledge polling may be used to reduce this time requirement). It should be noted that step 3 MUST end with a stop condition. If a start condition is issued during or at the end of step 3 (instead of a stop condition) the device will abort the nonvolatile register write and remain at step 2. If the operation is aborted with a start condition, the master must issue a stop to put the device into standby mode.BL1, and WPEN.Writing to the BL and WPEN Bits A 3 step sequence is required to change the nonvola- tile Block Lock Protect or Write Protect Enable bits:1) Set WEL=1, Write 00000010 to address FFFFh (Volatile Write Cycle.) 2) Set RWEL=1, Write 00000110 to address FFFFh (Volatile Write Cycle.) 3) Set BL1, BL0, and/or WPEN bits, Write u00xy010 to address FFFFh, where u=WPEN, x=BL1, and y=BL0.(Nonvolatile Write Cycle.) The three step sequence was created to make it diffi cult to change the contents of the Write Protect Register accidentally. If WEL was set to one by aprevious register write operation, the user may start atABSOLUTE MAXIMUM RATINGS*Figure 11. Block Lock Protect Bits and Protected Addresses BL1 0 0 1 1 BL0 0 1 0 1 Protected AddressesNone C00h - FFFh 800h - FFFh 000h - FFFhArray Location No Protect Upper 1/4 Upper 1/2 Full Array7003 FRM T02Figure 12. WP Pin and WPEN Bit Functionality WP 0 X 1 WPEN X 0 1Memory Array Not Lock Block ProtectedMemory Array Block Lock ProtectedBlock Lock Bits Unprotected Unprotected ProtectedWPEN BitWritable Writable WritableProtected Protected ProtectedUnprotected Unprotected Protected7003 FRM T0310元器件交易网X24320Temperature under Bias X24320 ....................................... –65°C to +135°CStorage Temperature ........................ –65°C to +150°C Voltage on any Pin with Respect to VSS .................................... –1V to +7V D.C. Output Current ..............................................5mA Lead Temperature (Soldering, .............................. 300°C 10 seconds)*COMMENT Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.RECOMMENDED OPERATING CONDITIONS TemperatureCommercial IndustrialSupply VoltageX24320 X24320–2. 5 X24320–1. 8Limits4.5V to 5.5V 2.5V to 5.5V 1.8V to 3.6V7003 FRM T05Min.0°C –40°CMax.+70°C +85°C7003 FRM T04D.C. OPERATING CHARACTERISTICS Limits SymbolICC1 ICC2 ISB1 (1)ParameterVCC Supply Current (Read) VCC Supply Current (Write) VCC Standby CurrentMin.Max.1 3 5UnitsmA mA ∝ATest ConditionsSCL = VCC X 0.1/VCC X 0.9 Levels @ 400KHz, SDA = Open, All OtherInputs = VSS or VCC – 0.3VSCL = SDA = VCC, All Other Inputs = VSS or VCC – 0.3V,VCC = 5V ± 10% ISB2 (1) VCC Standby Current 1 ∝ASCL = SDA = VCC, All Other Inputs = VSS or VCC – 0.3V,VCC = 2.5V ILI ILO VlL (2) VIH (2) VOL Vhys (3) Input Leakage Current Output Leakage Current Input LOW Voltage Input HIGH Voltage Output LOW VoltageHysteresis of Schmitt Trigger Inputs10 10 –0.5 VCC x 0.7 VCC x 0.3 VCC + 0.5 0.4 VCC x 0.05∝A ∝A V V V VVIN = VSS to VCCVOUT = VSS to VCCIOL = 3mA7003 FRM T06CAPACITANCE TA = +25°C, f = 1MHz, VCC = 5VSymbolCI/O (3) CIN (3)ParameterInput/Output Capacitance (SDA) Input Capacitance (S0, S1, S2, SCL, WP)Max.8 6UnitspF pFTest ConditionsVI/O = 0V VIN = 0V7003 FRM T07Notes: (1)Must perform a stop command prior to measurement. (2)VIL min. and VIH max. are for reference only and are not 100% tested. (3)This parameter is periodically sampled and not 100% tested.11元器件交易网X24320A.C. CONDITIONS OF TESTInput Pulse LevelsInput Rise and Fall Times Input and Output Timing LevelsEQUIVALENT A.C. LOAD CIRCUITVCC x 0.1 to VCC x 0.9 10ns VCC X 0.57003 FRM T085V 1.53KΟ OUTPUT 100pF7035 FM 13A.C. OPERATING CHARACTERISTICS (Over the recommended operating conditions, unless otherwise specified.) Read & Write Cycle LimitsSymbolfSCL tI tAA tBUF tHD:STA tLOW tHIGH tSU:STA tHD:DAT tSU:DAT tR tF tSU:STO tDH tOFParameterSCL Clock FrequencyNoise Suppression Time Constant at SCL, SDA InputsMin.0 50 0.1 1.2 0.6 1.2 0.6Max.400UnitsKHz nsSCL LOW to SDA Data Out ValidTime the Bus Must Be Free Before a New Transmission Can Start0.9∝s ∝s ∝s ∝s ∝s ∝s ∝s nsStart Condition Hold Time Clock LOW Period Clock HIGH PeriodStart Condition Setup Time a Repeated Start Condition) (for0.6 0 100 300 300 0.6 50 20+0.1Cb (5) 300Data In Hold Time Data In Setup Time SDA and SCL Rise Time SDA and SCL Fall Time Stop Condition Setup Time Data Out Hold Time Output Fall Timens ns ∝s ns7003 FRM T09POWER-UP TIMING SymboltPUR tPUW(4)ParameterPower-up to Read Operation Power-up to Write OperationMax.1 5Unitsms ms7003 FRM T10Notes: (4)tPUR and tPUW are the delays required from the time VCC is stable until the specified operation can be initiated. These parameters are periodically sampled and not 100% tested.12。

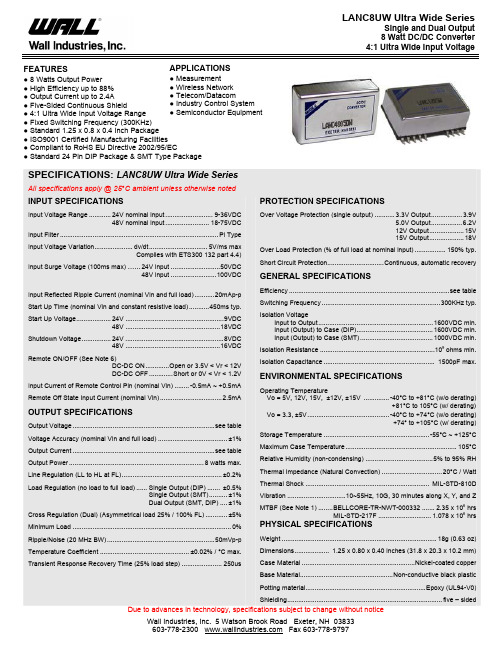

LANC2412UW8中文资料

FEATURES● 8 Watts Output Power● High Efficiency up to 88%● Output Current up to 2.4A● Five-Sided Continuous Shield● 4:1 Ultra Wide Input Voltage Range● Fixed Switching Frequency (300KHz) ● Standard 1.25 x 0.8 x 0.4 Inch Package ● ISO9001 Certified Manufacturing Facilities ● Compliant to RoHS EU Directive 2002/95/EC● Standard 24 Pin DIP Package & SMT Type PackageSPECIFICATIONS: LANC8UW Ultra Wide SeriesAll specifications apply @ 25°C ambient unless otherwise notedINPUT SPECIFICATIONSInput Voltage Range............24V nominal input..........................9-36VDC 48V nominal input........................18-75VDCInput Filter.......................................................................................Pi TypeInput Voltage Variation.....................dv/dt................................5V/ms maxComplies with ETS300 132 part 4.4)Input Surge Voltage (100ms max) …… 24V input ...........................50VDC 48V input .........................100VDCInput Reflected Ripple Current (nominal Vin and full load)...........20mAp-pStart Up Time (nominal Vin and constant resistive load)...........450ms typ.Start Up Voltage...................24V ......................................................9VDC48V ....................................................18VDCShutdown Voltage................24V ......................................................8VDC48V ....................................................16VDCRemote ON/OFF (See Note 6)DC-DC ON.............Open or 3.5V < Vr < 12V DC-DC OFF.............Short or 0V < Vr < 1.2VInput Current of Remote Control Pin (nominal Vin)........-0.5mA ~ +0.5mARemote Off State Input Current (nominal Vin)..................................2.5mAOUTPUT SPECIFICATIONSOutput Voltage..............................................................................see tableVoltage Accuracy (nominal Vin and full load) (1)Output Current..............................................................................see tableOutput Power..........................................................................8 watts max.Line Regulation (LL to HL at FL).......................................................±0.2%Load Regulation (no load to full load)......Single Output (DIP)....... ±0.5%Single Output (SMT)..........±1% Dual Output (SMT, DIP). (1)Cross Regulation (Dual) (Asymmetrical load 25% / 100% FL) (5)Minimum Load .......................................................................................0%Ripple/Noise (20 MHz BW)...........................................................50mVp-pTemperature Coefficient .................................................±0.02% / °C max.Transient Response Recovery Time (25% load step)......................250usPROTECTION SPECIFICATIONSOver Voltage Protection (single output)...........3.3V Output.................3.9V5.0V Output.................6.2V 12V Output...................15V 15V Output. (18V)Over Load Protection (% of full load at nominal input).................150% typ.Short Circuit Protection...............................Continuous, automatic recoveryGENERAL SPECIFICATIONS Efficiency........................................................................................see tableSwitching Frequency.................................................................300KHz typ.Isolation VoltageInput to Output...............................................................1600VDC min.Input (Output) to Case (DIP)..........................................1600VDC min. Input (Output) to Case (SMT)........................................1000VDC min.Isolation Resistance (109)ohms min.Isolation Capacitance............................................................. 1500pF max.ENVIRONMENTAL SPECIFICATIONSOperating TemperatureVo = 5V, 12V, 15V, ±12V, ±15V ..............-40°C to +81°C (w/o derating) +81°C to 105°C (w/ derating)Vo = 3.3, ±5V.............................................-40°C to +74°C (w/o derating) +74° to +105°C (w/ derating)Storage Temperature ..........................................................-55°C ~ +125°CMaximum Case Temperature.............................................................105°CRelative Humidity (non-condensing).....................................5% to 95% RHThermal Impedance (Natural Convection).................................20°C / WattThermal Shock .................................................................... MIL-STD-810DVibration ................................10~55Hz, 10G, 30 minutes along X, Y, and ZMTBF (See Note 1)........BELLCORE-TR-NWT-000332.......2.35 x 106hrsMIL-STD-217F .............................1.078 x 106hrsPHYSICAL SPECIFICATIONSWeight .....................................................................................18g (0.63 oz)Dimensions................... 1.25 x 0.80 x 0.40 inches (31.8 x 20.3 x 10.2 mm)Case Material ..............................................................Nickel-coated copperBase Material...................................................Non-conductive black plasticPotting material..................................................................Epoxy (UL94-V0)Shielding.....................................................................................five – sidedDue to advances in technology, specifications subject to change without noticeAPPLICATIONS● Measurement ● Wireless Network ● Telecom/Datacom ● Industry Control System ● Semiconductor EquipmentSAFETY & EMCApprovals and Standards.................IEC60950-1, UL60950-1, EN60950-1EMI (See Note 7)...............EN55022.............................................Class AESD....................EN61000-4-2…….. ……Perf. Criteria B Radiated Immunity...........EN61000-4-3……………10V/m Perf. Criteria AFast Transient..................EN61000-4-4...................±2KV Perf. Criteria BSurge (See Note 8)..........EN61000-4-5……………..±1KV Perf. Criteria BConducted Immunity…… EN61000-4-6……….…10 Vrms Perf. Criteria AOUTPUT VOLTAGE / CURRENT RATING CHARTOutput Current Input Current Model NumberInput RangeOutput Voltage Min. load Full load Output (2) Ripple & Noise No load (3) Full load (2) Efficiency (4)Capacitor(5)Load maxLANC2433UW8 3.3 VDC 0mA 2400mA 50mVp-p 40mA 407mA 85% 1330uF LANC2405UW8 5 VDC 0mA 1600mA 50mVp-p 40mA 402mA 87% 1330uFLANC2412UW8 12 VDC 0mA 666mA 50mVp-p 25mA 407mA 86% 288uFLANC2415UW8 15 VDC 0mA 533mA 50mVp-p 25mA 407mA 86% 200uF LANC2405DUW8 ±5 VDC 0mA ±800mA 50mVp-p 20mA 417mA 84% ±900uF LANC2412DUW8 ±12 VDC 0mA ±333mA 50mVp-p 25mA 407mA 86% ±133uFLANC2415DUW824VDC (9 - 36 VDC)±15 VDC 0mA ±267mA 50mVp-p 25mA 407mA 86% ±90uF LANC4833UW8 3.3 VDC 0mA 2400mA 50mVp-p 20mA 204mA 85% 1330uF LANC4805UW8 5 VDC 0mA 1600mA 50mVp-p 20mA 201mA 87% 1330uFLANC4812UW8 12 VDC 0mA 666mA 50mVp-p 13mA 201mA 87% 288uFLANC4815UW8 15 VDC 0mA 533mA 50mVp-p 13mA 198mA 88% 200uF LANC4805DUW8 ±5 VDC 0mA ±800mA 50mVp-p 10mA 208mA 84% ±900uF LANC4812DUW8 ±12 VDC 0mA ±333mA 50mVp-p 13mA 201mA 87% ±133uF LANC4815DUW8 48VDC (18 - 75 VDC) ±15 VDC 0mA ±267mA 50mVp-p 13mA 201mA 87% ±90uFNOTES1.BELLCORE TR-NWT-000332. Case I: 50% Stress, Temperature at 40ºC. (Ground fixed and controlled environment) MIL-STD-217F Notice2 @Ta=25 ºC, Full load (Ground, Benign, controlled environment) 2. Maximum value at nominal input voltage and full load. 3. Typical value at nominal input voltage and no load. 4. Typical value at nominal input voltage and full load. 5. Test by minimum Vin and constant resistive load. 6. The ON/OFF control pin voltage is referenced to -Vin.7. The LANC8UW Series can meet EN55022 Class A with an external capacitor in parallel with the input pins.Recommend: 24Vin: 1µF/50V48Vin: 0.47µF/100V8. An external filter capacitor is required if the module has to meet EN61000-4-5. The filter capacitor Wall Industries suggests: Nippon chemi-con KY Series, 220uF/100V, ESR 48m Ω.Air ± 8KV Contact ± 6KVMECHANICAL DRAWING(DIP) PIN CONNECTIONPIN SINGLE DUAL PIN SINGLE DUAL 1 CTRL CTRL 2 -INPUT -INPUT 23 +INPUT +INPUT 3 -INPUT -INPUT 22 +INPUT +INPUT 9 NC COMMON 16 -OUTPUTCOMMON 11 NC -OUTPUT 14 +OUTPUT +OUTPUTRecommended Filter for EN55022 Class B ComplianceLoadRecommended EN55022 Class B Filter Circuit LayoutThe components used in the Figure 1, together with the manufacturers’ part numbers for these components, are as follows:C1 C2 C3C4L1 LANC24xxUW8 4.7uF/50V N/A1000pF/2KV 1000pF/2KV325uH Common Choke LANC48xxUW8 1.5uF/100V 1.5uF/100V 1000pF/2KV 1000pF/2KV325uH Common ChokeFIGURE 1FIGURE 2(SMT) PIN CONNECTIONPIN SINGLE DUAL PIN SINGLE DUAL1 CTRL CTRL2 -INPUT -INPUT 23 +INPUT +INPUT 3 -INPUT -INPUT 22 +INPUT +INPUT 9 NC COMMON 16 -OUTPUT COMMON 11 NC -OUTPUT 14 +OUTPUT +OUTPUT Others NC NC Others NC NC1. All dimensions are in inches (mm) Tolerance: X.XX±0.02 (X.X±0.5) X.XXX±0.01 (X.XX±0.25)2. Pin pitch tolerance ±0.01 (0.25)LANC8UWSERIES。

LPC2148USB开发手册

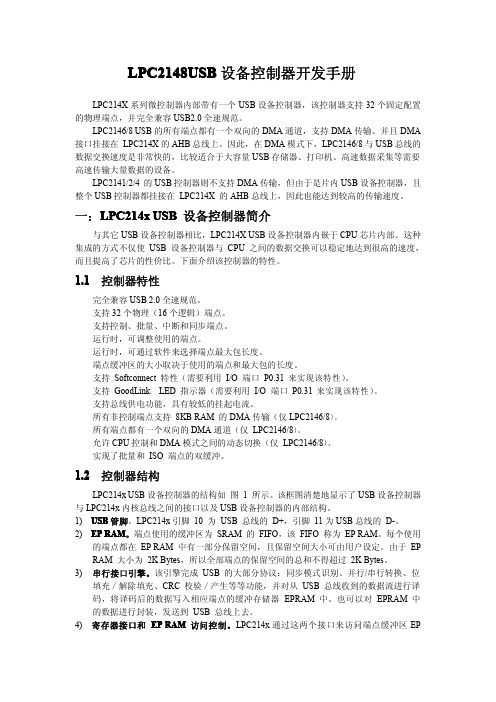

LPC214LPC21488USB设备控制器开发手册LPC214X系列微控制器内部带有一个USB设备控制器,该控制器支持32个固定配置的物理端点,并完全兼容USB2.0全速规范。

LPC2146/8USB的所有端点都有一个双向的DMA通道,支持DMA传输。

并且DMA 接口挂接在LPC214X的AHB总线上。

因此,在DMA模式下,LPC2146/8与USB总线的数据交换速度是非常快的,比较适合于大容量USB存储器、打印机、高速数据采集等需要高速传输大量数据的设备。

LPC2141/2/4的USB控制器则不支持DMA传输,但由于是片内USB设备控制器,且整个USB控制器都挂接在LPC214X的AHB总线上,因此也能达到较高的传输速度。

一:LPC214x USB设备控制器简介与其它USB设备控制器相比,LPC214X USB设备控制器内嵌于CPU芯片内部。

这种集成的方式不仅使USB设备控制器与CPU之间的数据交换可以稳定地达到很高的速度,而且提高了芯片的性价比。

下面介绍该控制器的特性。

1.1控制器特性完全兼容USB2.0全速规范。

支持32个物理(16个逻辑)端点。

支持控制、批量、中断和同步端点。

运行时,可调整使用的端点。

运行时,可通过软件来选择端点最大包长度。

端点缓冲区的大小取决于使用的端点和最大包的长度。

支持Softconnect特性(需要利用I/O端口P0.31来实现该特性)。

支持GoodLink LED指示器(需要利用I/O端口P0.31来实现该特性)。

支持总线供电功能,具有较低的挂起电流。

所有非控制端点支持8KB RAM的DMA传输(仅LPC2146/8)。

所有端点都有一个双向的DMA通道(仅LPC2146/8)。

允许CPU控制和DMA模式之间的动态切换(仅LPC2146/8)。

实现了批量和ISO端点的双缓冲。

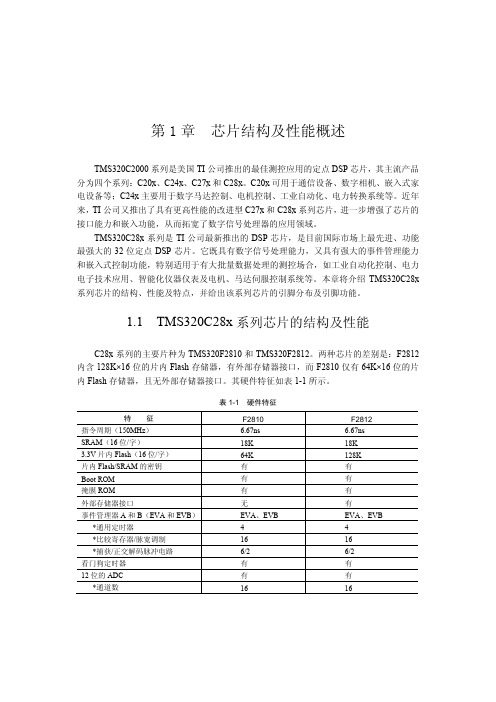

1.2控制器结构LPC214x USB设备控制器的结构如图1所示。

该框图清楚地显示了USB设备控制器与LPC214x内核总线之间的接口以及USB设备控制器的内部结构。

1N4148X中文资料

1N4148X200mWSwitching DiodesFeatures• Fast Switching Speed• For General Purpose Switching Applications•Surface Mount Package Ideally Suited for Automatic Insertion Maximum RatingsSymbol Parameter Rating UnitV RM Non-Repetitive Peak Reverse Voltage 100 VV RRM V RWM V R Peak Repetitive Reverse VoltageWorking Peak Reverse Voltage DC Blocking Voltage 75 VV R(RMS) RMS Reverse Voltage 53 I FM Forward Continuous Current 300 mAI o Average Rectified Output Current 150 mA I FSM Peak Forward Surge Current @1.0μs@1.0s2.0 1.0 A R θJAThermal Resistance Junction to Ambient 625 ℃/W P D Power dissipation 200 mW T J ,T STG Operating and Storage Junction Temperature-65 to +150 ℃ Electrical Characteristics @ 25O C Unless Otherwise SpecifiedSymbol Parameter Min Max Test Conditions V (BR) Reverse Breakdown Voltage75V --- I R =10μAI RReverse Voltage Leakage Current---1.0μA25nA V R =75V V R =20VV F Forward Voltage --- --- --- --- 0.715V 0.855V1.0V1.25VI F =5mAI F =10mA I F =100mA I F =150mA C T Total Capacitance --- 2.0pF V R =0V, f=1MHZt rr Reverse Recovery Time--- 4.0nsI R =I F =10mA, R L =100Ω, Rec. to 1.0mAomp onents 20736 Marilla Street Chatsworth! "# $ % ! "#TMMicro Commercial ComponentsMechanical Data• Marking Code: T4• Case Material: Molded Plastic. UL FlammabilityClassification Rating 94V-0V1N4148XMicro Commercial ComponentsMicro Commercial Components***IMPORTANT NOTICE***Micro Commercial Components Corp . reserve s the right to make changes without further notice to any product herein to make corrections, modifications , enhancements , improvements , or other changes .Micro Commercial Components Corp.does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights ,northe rights of others . The user of products in such applications shall assume all risks of such use and will agree to hold Micro Commercial Components Corp.and all the companies whoseproducts are represented on our website, harmless against all damages.***APPLICATIONS DISCLAIMER***Products offer by Micro Commercial Components Corp.are not intended for use in Medical,Aerospace or Military Applications.。

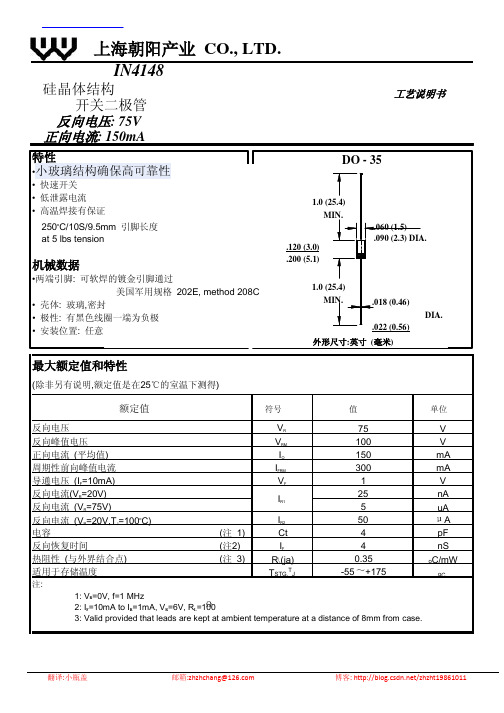

IN4148中文资料

DO - 35

1.0 (25.4) MIN.

.120 (3.0) .200 (5.1)

.060 (1.5) .090 (2.3) DIA.

1.0 (25.4) MIN.

.018 (0.46)

.022 (0.56) 外形尺寸:英寸 (毫米)

上海朝阳产业 CO., LTD.

IN4148

硅晶体结构 开关二极管

反向电压: 75V 正向电流: 150mA

工艺说明书

特性 •小玻璃结构确保高可靠性

• 快速开关 • 低泄露电流 • 高温焊接有保证

250oC/10S/9.5mm 引脚长度 at 5 lbs tension

机械数据

•两端引脚: 可软焊的镀金引脚通过 美国军用规格 202E, method 208C

翻译:小瓶盖

邮箱:zhzhchang@

博客: /zhzht19861011

nA

5

uA

反向电流 (VR=20V,TJ=100oC)

IR2

50

A

电容

(注 1)

Ct

4

pF

反向恢复时间

(注2)

IF

4

nS

热阻性 (与外界结合点) 适用于存储温度

注:

(注 3)

R(ja) TSTG,TJ

0.35 -55 +175

oC/mW

oC

1: VR=0V, f=1 MHz 2: IF=10mA to IR=1mA, VR=6V, RL=100 3: Valid provided that leads are kept at ambient temperature at a distance of 8mm from case.

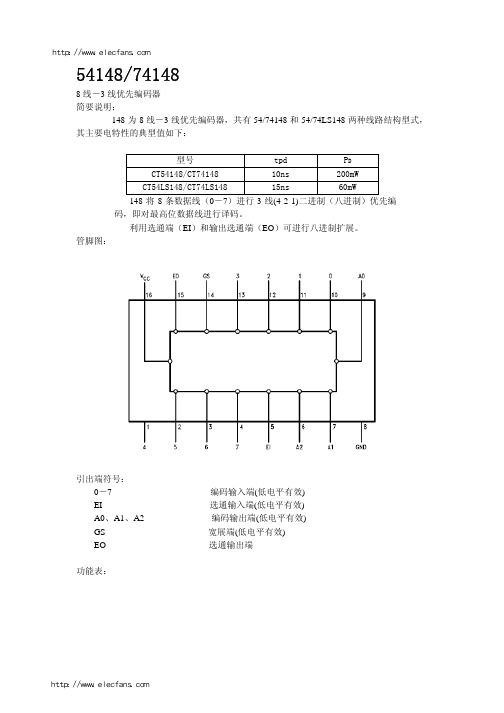

74LS148中文资料

http://www.elecfans.com

http://www.elecfans.com

说明:H-高电平 L-低电平 X-任意

极限值 电源电压------------------------------------------------7V 输入电压 54/74148-----------------------------------------5.5V 54/74LS148--------------------------------------7V 发射极间电压 54/74148 的两编码输入----------------------------5.5V 工作环境温度 54×××------------------------------ -55~125℃ 74×××------------------------------------0~70℃ 贮存温度-------------------------------------- -65~150℃

tPHL

(同相输出)

tPLH

EI->GS

tPHL

(同相输出)

tPLH

EI->EO

tPHL

(同相输出)

【2】:tPLH-输出由低到高电平传输延迟时间 tPHL-输出由高到低电平传输延迟时间

‘148 最大 15 14 19 19 10 25 30 25 15 15 12 15 15 30

‘LS148 最大 18 25 36 29 18 40 55 21 25 25 17 36 21 35

VCC=最小,VIH=2V,VIL=最大,IOL=最大

74

0.4

时输入电流

1-7 0,EI

Vcc=最大

in4148中文资料_数据手册_参数

SEMTECH ELECTRONICS LTD.

Subsidiary of Sino-Tech International (BVI) Limited ®

Dated: 14/01/2013 Rev: 01

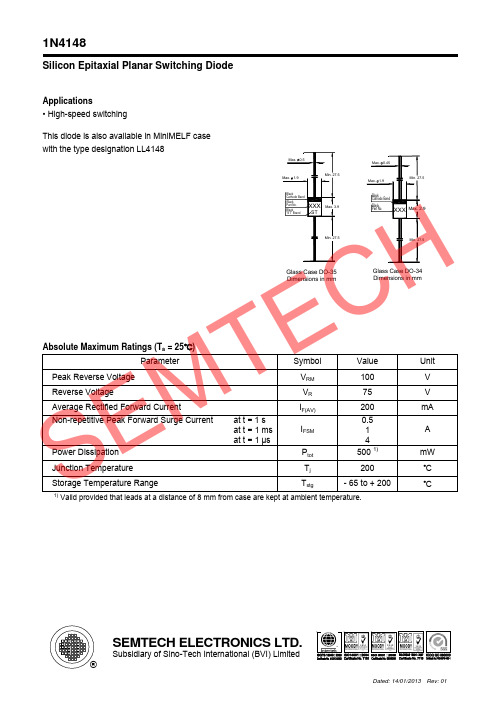

1N4148

Admissible power dissipation versus ambient temperature

Max. 0.5 Max. 1.9

Min. 27.5

Max. 0.45 Max. 1.9

Min. 27.5

Black Cathode Band

Black Part No.

Black "ST" Brand

XXX

ST

Max. 3.9

Black Cathode Band

Black Part No.

XXX Max. 2.9

Reverse Recovery Time at IF = 10 mA to IR = 1 mA, Irr = 0.1 x IR, VR = 6 V, RL = 100 Ω

Thermal Resistance Junction to Ambient Air

Vfr

-

trr

-

RthA

-

Rectification Efficiency at f = 100 MHz, VRF = 2 V

ηV

0.45

1) Valid provided that leads at a distance of 8 mm from case are kept at ambient temperature.

4

2.5

4 0.35 1)

-

pF V

ns K/mW

MEMORY存储芯片LL4148中文规格书

LL4148 — Small Signal Diode January 2016LL4148Small Signal DiodeOrdering InformationAbsolute Maximum Ratings (1), (2)Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be opera-ble above the recommended operating conditions and stressing the parts to these levels is not recommended. In addi-tion, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only. Values are at T A = 25°C unless otherwise noted.Notes:1.These ratings are based on a maximum junction temperature of 200°C.2.These are steady-state limits. Fairchild Semiconductor should be consulted on applications involving pulsed or low-duty-cycle operations.Part NumberDevice Marking Package Packing Method LL4148Color Band Marking SOD-80 2L Tape and Reel, 7 inch Reel, 2500 pcs SymbolParameter Value Unit V RRMMaximum Repetitive Reverse Voltage 100V I F(AV)Average Rectified Forward Current 200mA I fRecurrent Peak Forward Current 500mA I FSMNon-Repetitive Peak Forward Surge Current Pulse Width = 1.0 s 1.0A Pulse Width = 1.0 μs 2.0T STGStorage Temperature Range -65 to +200°C T J Operating Junction Temperature Range -55 to +175°C COLOR BAND MARKING1ST BANDBlackThe 1st Band indicates the cathode bandSOD80Cathode BandElectrical CharacteristicsValues are at T A = 25°C unless otherwise noted.Symbol Parameter Conditions Min.Max.UnitV R Breakdown Voltage I R = 100 μA100V I R = 5.0 μA75V F Forward Voltage I F = 10 mA 1.0VI R Reverse Leakage V R = 20 V25nA V R = 20 V, T A = 150°C50μAC T Total Capacitance V R = 0, f = 1.0 MHz 4.0pFt rr Reverse Recovery Time I F = 10 mA, V R = 6.0 V (60 mA),I rr = 1.0 mA, R L = 100 Ω4.0ns。

AO3418中文资料