ALD1116PAL;ALD1116SAL;中文规格书,Datasheet资料

爱达顿199162商品说明书

Eaton 199162Eaton Moeller® series PKZM0 Motor-protective circuit-breaker, 15kW, 25 - 32 A, Push in terminalsGeneral specificationsEaton Moeller® series PKZM0 Motor-protective circuit-breaker199162401508197246375 mm109 mm45 mm0.341 kgIEC/EN 60947VDE 0660ULCSAIEC/EN 60947-4-1UL 60947-4-1CSA-C22.2 No. 60947-4-1-14 CEUL File No.: E36332UL Category Control No.: NLRV CSA File No.: 165628CSA Class No.: 3211-05ULCSA PKZM0-32-PIProduct Name Catalog NumberEANProduct Length/Depth Product Height Product Width Product Weight Certifications Model CodeTurn buttonPhase-failure sensitivity (according to IEC/EN 60947-4-1, VDE 0660 Part 102)Motor protectionPhase failure sensitiveThree-pole 100,000 operations100,000 OperationsDIN rail (top hat rail) mounting optionalCan be snapped on to IEC/EN 60715 top-hat rail with 7.5 or15 mm height.40 Operations/hIII3Motor protective circuit breakerFinger and back-of-hand proof, Protection against direct contact when actuated from front (EN 50274)6000 V AC25 g, Mechanical, according to IEC/EN 60068-2-27, Half-sinusoidal shock 10 msAlso motors with efficiency class IE3Branch circuit: Suitable for group installations, (UL/CSA)-5 - 40 °C to IEC/EN 60947, VDE 0660≤ 0.25 %/K, residual error for T > 40°-25 - 55 °C, Operating rangeMotor starter combinations type MSC...Actuator type Features Functions Number of poles Lifespan, electricalLifespan, mechanicalMounting MethodMounting positionOperating frequencyOvervoltage categoryPollution degreeProduct categoryProtectionRated impulse withstand voltage (Uimp) Shock resistanceSuitable forTemperature compensationUsed withMax. 2000 m-25 °C55 °C25 °C40 °C40 °C80 °CDamp heat, cyclic, to IEC 60068-2-30 Damp heat, constant, to IEC 60068-2-781 x (1 - 6) mm²18 - 812 mm50 Hz60 Hz32 A7.5 kW15 kW690 V690 V32 A496 A, Irm, Setting range max. ± 20% tolerance, Trip blocksBasic device fixed 15.5 x Iu, Trip Blocks7.5 HP5 HP10 HP20 HP25 HPAltitude Ambient operating temperature - min Ambient operating temperature - max Ambient operating temperature (enclosed) - min Ambient operating temperature (enclosed) - max Ambient storage temperature - min Ambient storage temperature - max Climatic proofingTerminal capacity (flexible)Terminal capacity (solid/stranded AWG)Stripping length (main cable)Rated frequency - min Rated frequency - max Rated operational current (Ie)Rated operational power at AC-3, 220/230 V, 50 Hz Rated operational power at AC-3, 380/400 V, 50 Hz Rated operational voltage (Ue) - min Rated operational voltage (Ue) - max Rated uninterrupted current (Iu)Short-circuit releaseAssigned motor power at 200/208 V, 60 Hz, 3-phase Assigned motor power at 230/240 V, 60 Hz, 1-phase Assigned motor power at 230/240 V, 60 Hz, 3-phase Assigned motor power at 460/480 V, 60 Hz, 3-phase Assigned motor power at 575/600 V, 60 Hz, 3-phasePush in terminals032 A32 AOverload trigger: tripping class 10 A 9.56 W0 W0 W0 WMeets the product standard's requirements.Meets the product standard's requirements.Meets the product standard's requirements.Meets the product standard's requirements.Meets the product standard's requirements.Does not apply, since the entire switchgear needs to be evaluated.Does not apply, since the entire switchgear needs to be evaluated.Meets the product standard's requirements.Connection Number of auxiliary contacts (change-over contacts)Number of auxiliary contacts (normally closed contacts)Number of auxiliary contacts (normally open contacts)Overload release current setting - min Overload release current setting - max Tripping characteristic Equipment heat dissipation, current-dependent PvidHeat dissipation capacity PdissHeat dissipation per pole, current-dependent PvidStatic heat dissipation, non-current-dependent Pvs10.2.2 Corrosion resistance10.2.3.1 Verification of thermal stability of enclosures10.2.3.2 Verification of resistance of insulating materials to normal heat10.2.3.3 Resist. of insul. mat. to abnormal heat/fire by internal elect. effects10.2.4 Resistance to ultra-violet (UV) radiation10.2.5 Lifting10.2.6 Mechanical impact10.2.7 InscriptionsDoes not apply, since the entire switchgear needs to be evaluated.Meets the product standard's requirements.Does not apply, since the entire switchgear needs to be evaluated.Does not apply, since the entire switchgear needs to be evaluated.Is the panel builder's responsibility.Is the panel builder's responsibility.Is the panel builder's responsibility.Is the panel builder's responsibility.Is the panel builder's responsibility.The panel builder is responsible for the temperature rise calculation. Eaton will provide heat dissipation data for the devices.Is the panel builder's responsibility. The specifications for the switchgear must be observed.Is the panel builder's responsibility. The specifications for the switchgear must be observed.The device meets the requirements, provided the information in the instruction leaflet (IL) is observed.Motor Starters in System xStart - brochureSave time and space thanks to the new link module PKZM0-XDM32MEProduct Range Catalog Switching and protecting motorsSwitching and protecting motors - catalogDA-DC-00004889.pdfDA-DC-00004919.pdf121X042121X002eaton-manual-motor-starters-pkz-dimensions.epseaton-manual-motor-starters-pkz-dimensions-002.epseaton-manual-motor-starters-pkzm-pkzm0-dimensions.epsETN.PKZM0-32-PI.edzIL122024ZUWIN-WIN with push-in technologymotorschutzschalter_bis_32a_pi.dwgpkzm0_pi.stp10.3 Degree of protection of assemblies10.4 Clearances and creepage distances10.5 Protection against electric shock10.6 Incorporation of switching devices and components 10.7 Internal electrical circuits and connections10.8 Connections for external conductors10.9.2 Power-frequency electric strength10.9.3 Impulse withstand voltage10.9.4 Testing of enclosures made of insulating material 10.10 Temperature rise10.11 Short-circuit rating10.12 Electromagnetic compatibility10.13 Mechanical function BrochuresCatalogues Declarations of conformity DrawingseCAD modelInstallation instructions Installation videosmCAD modelEaton Corporation plc Eaton House30 Pembroke Road Dublin 4, Ireland © 2023 Eaton. All rights reserved. Eaton is a registered trademark.All other trademarks areproperty of their respectiveowners./socialmedia。

AUTOID6L(P)产品规格书

传感器分辨率

旋转视角 上下倾斜视角 左右偏移视角 对焦环境(VLD) 照度环境(LED) 环境光(太阳光) 可选子型号 SR

是门禁和出入境身份管理的理想之选; 医疗保健护理点应用中的患者腕带和单位 剂量;电子行业中常见的高密度条码 专为超高密度一维和二维条码以及制造业中的直接部件标记而优化设计 图像采集 2592*1944(拍照),480P 15/30fps(摄像) 自动对焦 支持双闪光灯(支持背照式) 500 万 HF 支持ISO15693、ISO14443A/B,支持NFC协议; HF频段13.56MHz 读取距离0~5cm (ISO15693),0-4cm(ISO14443A/B) GPS 地理位置信息采集

二、 AUTOID 6L(P)数据采集功能参数

功能 1 光学分辨率 旋转视角 上下倾斜视角 左右偏移视角 环境光 扫描景深 扫描频率 扫描宽度 激光功率 支持符号 0.004 英寸最小条宽 偏离垂直角度±35° 偏离正常角度±65° 偏离正常角度±50° 太阳光:10,000ft. Candles(107,640Lux) 人造光:450ft.candles(4,844Lux) 15.2cm(4mil),64.1cm(55mil) 每秒扫描最小 92,典型 104,最大 116 次(双向) 47°,35° 0.7mw±0.1mw UPC-A, UPC-E, EAN-8, EAN-13, Code 128, Code 39, Code 93, Code 11, Codabar, Interleaved 2 of 5,Discrete 2 of 5,Chinese 2 of 5,MSI,RSSI等

第 4 页 共 4 页

四、 AUTOID 6L(P)第三方应用开发支撑

LA6500-E, 规格书,Datasheet 资料

Monolithic Linear IC

LA6500

Overview

Power Operational Amplifier

The LA6500 is a power operational amplifier.

Features

• High output current (IO max = 1.0A) • High gain • With current limiter • Capable of being operated from single supply

1000×20 ∆VO

Application Circuit Example

+

VCC

5

2.2Ω

OUT

0.1µF

4

LA6500

3 2 1

+

VEE

−VIN +VIN

SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein. SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design. In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law. No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd. Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use. Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellctual property rights which has resulted from the use of the technical information and products mentioned above.

LIS8517_Datasheet _V1.1

-0.3V~35V 150 oC -40 oC~85 oC -55 oC~150 oC 260 oC

-0.3V~7V

-0.3V~650V

标识和订购信息

订购序号 LIS8517-D-G-TB

封装类型 DIP-8

版权© 莱士电子科技有限公司

莱士电子科技有限公司

封装编带 Tube

3/7

LIS-DS-8517-V1.1

MHz KHz KHz

%

ns mV ms

oC us ms

V uA Ω A nS nS

版权© 莱士电子科技有限公司

莱士电子科技有限公司

4/7

LIS-DS-8517-V1.1

LIS8517

两绕组-初级侧控制 LED 驱动开关

典型工作特性曲线

图1

由于不受辅助线圈供电限制,并且具有宽范围的工 作频率,系统输出功率 30W 至 45W 的情况下,仍能 保证良好的恒流特性,为设计系列机种提供良好基 础。

Min. Typ.

-

-

-

110

8.0

8.8

14.8 15.6

26

28

31

33

1.85

2

55

60

8.05 8.75

-

±6

-

450

970 1000

-

8

-

150

100

10

650

1.0

40 50

Max.

50 150 9.6 16.4 30 35

2.15 65 9.45 -

1030

-

-

1

6

Unit

A uA V V V V

保护

OTP OOP OSP

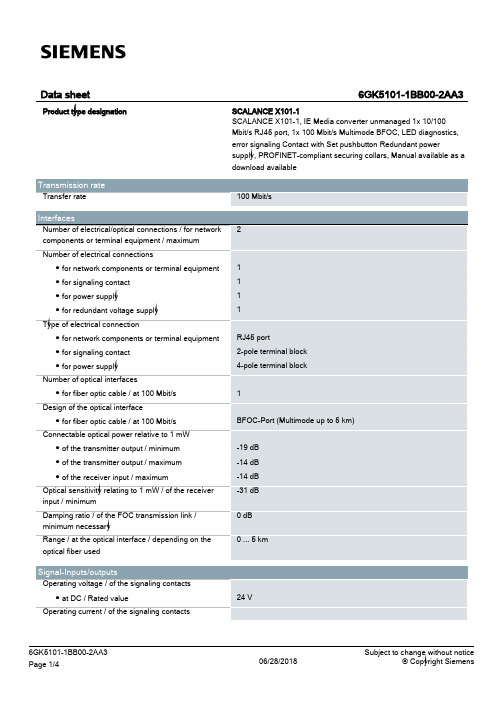

SCALANCE X101-1 商品说明书

24 V

6GK5101-1BB00-2AA3 Page 1/4

06/28/2018

Subject to change without notice © Copyright Siemens

● at DC / maximum

Supply voltage, current consumption, power loss Supply voltage ● external ● external Type of voltage / of the supply voltage Product component / fusing at power supply input Fuse protection type / at input for supply voltage Consumed current ● maximum Power loss [W] ● at DC / at 24 V

Compact 40 mm 125 mm 124 mm 0.55 kg

Yes Yes Yes

No No

FM3611: Class 1, Divison 2, Group A, B, C, D / T.., Class 1, Zone 2, Group IIC, T.. EN 600079-15 II 3 G EEx nA II T.. KEMA 06 ATEX 0021 X

Yes

Yes Yes Yes Yes Yes No 134 y

/snst

/simatic-net https:// /industry/infocenter /bilddb /cax https://

Security information

UL 60950-1, CSA C22.2 No. 60950-1 UL 1604 and UL 2279-15 (Hazardous Location), Class 1 / Division 2 / Group A, B, C, D / T.., Class 1 / Zone 2 / Group IIC / T.. EN 61000-6-3 EN 61000-6-4:2001 EN 61000-6-2:2001, EN 61000-6-4:2001 Yes Yes Yes

艾特顿111586型号电源保护设备说明说明书

Eaton 111586Eaton Moeller series xPole - PKP42 RCBO - residual-current circuit breaker with overcurrent protection. RCD/MCB, 32A, 30mA, MCB trip curve B, 2 p, RCCB trip char.: ACGeneral specificationsEaton Moeller series xPole - PKP42 RCBO - residual-current circuit breaker with overcurrent protection111586401508111146686 mm 75 mm 37 mm 0.25 kg CE Marked RoHS conformCE PKP42-32/2/B/003Product NameCatalog Number EANProduct Length/Depth Product Height Product Width Product Weight Compliances Certifications Model Code32 AIs the panel builder's responsibility. The specifications for the switchgear must be observed.4.5 kAMeets the product standard's requirements.Is the panel builder's responsibility. The specifications for the switchgear must be observed.3Does not apply, since the entire switchgear needs to be evaluated.Meets the product standard's requirements.0 kA50 HzIs the panel builder's responsibility.20.03 AType AC, AC current sensitive.40 °C0 W eaton-xpole-pkp42-rcbo-catalog-ca019055en-en-us.pdf eaton-xpole-protective-devices-catalog-ca019014en-en-us.pdfDA-DC-03_PKP.2eaton-xeffect-frbm6/m-characteristic-curve-003.jpgeaton-xpole-afdd-characteristic-curve-002.jpgeaton-xeffect-frbm6/m-dimensions-002.jpgeaton-xpole-pkp42-3d-drawing.jpgIL019140ZUeaton-xpole-combined-mcb-rcd-device-rcbo-packaging-manual-multilingual.pdfeaton-xeffect-frbm6/m-wiring-diagram-003.jpgRated operational current for specified heat dissipation (In) 10.11 Short-circuit ratingRated switching capacity (IEC/EN 61009)10.4 Clearances and creepage distances10.12 Electromagnetic compatibilityCurrent limiting class10.2.5 Lifting10.2.3.1 Verification of thermal stability of enclosures Rated short-circuit breaking capacity (EN 60947-2) Frequency rating10.8 Connections for external conductorsNumber of poles (total)Fault current ratingSensitivity typeAmbient operating temperature - maxHeat dissipation per pole, current-dependentBuilt-in depth Catalogues Certification reports Characteristic curve DrawingsInstallation instructions Wiring diagrams70 mmConnectable conductor cross section (solid-core) - min1 mm²10.9.3 Impulse withstand voltageIs the panel builder's responsibility.Number of polesTwo-poleAmbient operating temperature - min-25 °C10.6 Incorporation of switching devices and componentsDoes not apply, since the entire switchgear needs to be evaluated.10.5 Protection against electric shockDoes not apply, since the entire switchgear needs to be evaluated.Rated switching capacity4.5 kAEquipment heat dissipation, current-dependent5.5 WTripping characteristicB10.13 Mechanical functionThe device meets the requirements, provided the information in the instruction leaflet (IL) is observed.10.2.6 Mechanical impactDoes not apply, since the entire switchgear needs to be evaluated.10.9.4 Testing of enclosures made of insulating materialIs the panel builder's responsibility.Static heat dissipation, non-current-dependent0 WApplicationSwitchgear for residential and commercial applications10.3 Degree of protection of assembliesDoes not apply, since the entire switchgear needs to be evaluated.Voltage typeACNumber of poles (protected)2Leakage current typeACRated short-circuit breaking capacity (EN 61009-1)4.5 kATrippingNon-delayedOperating ambient temperature - min-25 °CHeat dissipation capacity0 WRelease characteristicBImpulse withstand currentPartly surge-proof, 250 AProduct rangePKP42Width in number of modular spacings210.2.3.2 Verification of resistance of insulating materials to normal heatMeets the product standard's requirements.10.2.3.3 Resist. of insul. mat. to abnormal heat/fire by internal elect. effectsMeets the product standard's requirements.Rated short-circuit breaking capacity (EN 61009)4.5 kAOperating ambient temperature - max40 °CVoltage rating230 V10.9.2 Power-frequency electric strengthIs the panel builder's responsibility.Connectable conductor cross section (solid-core) - max25 mm²Degree of protectionIP20Overvoltage categoryIIIPollution degree210.7 Internal electrical circuits and connectionsIs the panel builder's responsibility.Connectable conductor cross section (multi-wired) - min1 mm²Rated impulse withstand voltage (Uimp)4 kV10.10 Temperature riseThe panel builder is responsible for the temperature rise calculation. Eaton will provide heat dissipation data for the devices.Basic functionCombined RCD/MCB devicesRated current32 AConnectable conductor cross section (multi-wired) - max25 mm²TypeRCBO10.2.2 Corrosion resistanceMeets the product standard's requirements.Surge current capacity0.25 kA10.2.4 Resistance to ultra-violet (UV) radiationMeets the product standard's requirements.10.2.7 InscriptionsMeets the product standard's requirements.Rated short-circuit breaking capacity (IEC 60947-2)0 kADisconnection characteristicUndelayedProduct applicationSwitchgear for industrial and advanced commercial applicationsRated operational voltage (Ue) - maxEaton Corporation plc Eaton House30 Pembroke Road Dublin 4, Ireland © 2023 Eaton. All rights reserved. Eaton is a registered trademark.All other trademarks areproperty of their respectiveowners./socialmedia230 V250 VRated insulation voltage (Ui)。

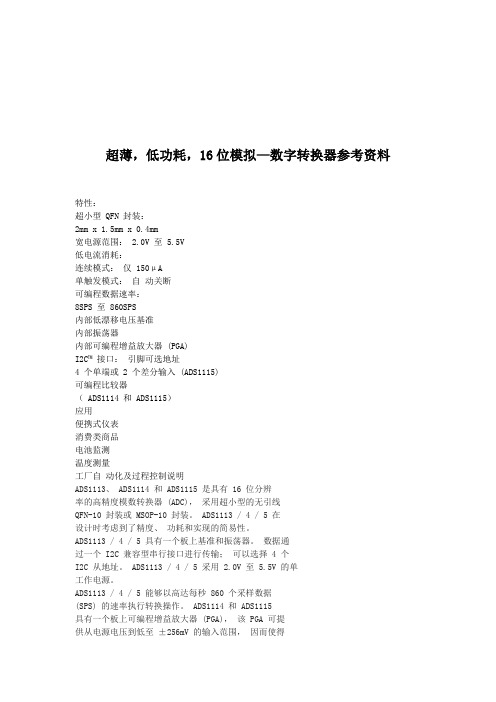

ads1115中文版

最小值

特征值

最大值

电力供应 的要求

电力供应 电压

2

5.5

V

供应 当前

电源关闭 当前 在 25° C

0.5

2

μA

电源关闭 当前,到 125°C

5

μA

运行 当前 在 25° C

150

200

μA

运行 当前 , 到 125° C

300

μA

电源 耗散

VDD = 5.0V

0.9

mW

VDD = 3.3V

0.5

最大额定值的绝对值

ADS1113,ADS1114,ADS1115

单位

VDD到GND

-0.3~+5.5

V

模拟输入电流

100,瞬间

mA

模拟输入电流

10,持续

mA

模拟输入电压对GND

-0.3到VDD+0.3

V

SDA,SCL,ADDR,ALERT/RDY电压对GND

-0.5到+5.5

V

最高结温

+150

℃

存储温度范围

9

SDA

SDA

SDA

数字I/O

串行数据:传输和接收数据

10

SCL

SCL

SCL

数字输入

串行时钟输入:ClocksdataonSDA

1)数控引脚可能是左浮动或接到地面。

定时要求

tLOW

tRtFtHDSTA

SCL

SDA

tBUF

tHDSTA

tHDDAT

tHIGHtSUSTAtSUSTO

tSUDAT

PSSP

300

GND AIN0

ALD1106中文资料

ADVANCED LINEAR DEVICES, INC.

ALD1106/ALD1116

QUAD/DUAL N-CHANNEL MATCHED MOSFET ARRAY

GENERAL DESCRIPTION

The ALD1106/ALD1116 are monolithic quad/dual N-channel enhancement mode matched MOSFET transistor arrays intended for a broad range of precision analog applications. The ALD1106/ALD1116 offer high input impedance and negative current temperature coefficient. The transistor pairs are matched for minimum offset voltage and differential thermal response, and they are designed for switching and amplifying applications in +2V to +12V systems where low input bias current, low input capacitance and fast switching speed are desired. These MOSFET devices feature very large (almost infinite) current gain in a low frequency, or near DC, operating environment. The ALD1106/ALD1116 are building blocks for differential amplifier input stages, transmission gates, and multiplexer applications, current sources and many precision analog circuits.

MH8S72DALD-6资料

DESCRIPTIONThe MH8S72DALD is 8388608 - word by 72-bit Synchronous DRAM module. This consists of nine industry standard 8Mx8 Synchronous DRAMs in TSOP and one industory standard EEPROM in TSSOP.The mounting of TSOP on a card edge Dual Inline package provides any application where high densities and large quantities of memory are required.This is a socket type - memory modules, suitable for easy interchange or addition of modules.FEATURESMax. Clock frequency -6:133MHz,-7,8:100MHzsingle 3.3V±0.3V power supplyBurst length- 1/2/4/8/Full Page(programmable)10pin 11pinPIN NO.PIN NAME PIN NO.PIN NAME PIN NO.PIN NAME PIN NO.PIN NAME 1VSS43VSS85VSS127VSS 2DQ044NC86DQ32128CKE0 3DQ145/S287DQ33129NC 4DQ246DQMB288DQ34130DQMB6 5DQ347DQMB389DQ35131DQMB7 6VDD48NC90VDD132NC 7DQ449VDD91DQ36133VDD 8DQ550NC92DQ37134NC 9DQ651NC93DQ38135NC 10DQ752CB294DQ39136CB6 11DQ853CB395DQ40137CB7 12VSS54VSS96VSS138VSS 13DQ955DQ1697DQ41139DQ48 14DQ1056DQ1798DQ42140DQ49 15DQ1157DQ1899DQ43141DQ50 16DQ1258DQ19100DQ44142DQ51 17DQ1359VDD101DQ45143VDD 18VDD60DQ20102VDD144DQ52 19DQ1461NC103DQ46145NC 20DQ1562NC104DQ47146NC 21CB063NC105CB4147NC CB12264VSS106CB5148VSS 23VSS65DQ21107VSS149DQ53 24NC66DQ22108NC150DQ54 25NC67DQ23109NC151DQ55 26VDD68VSS110VDD152VSS 27/WE069DQ24111/CAS153DQ56 28DQMB070DQ25112DQMB4154DQ57 29DQMB171DQ26113DQMB5155DQ58 30/S072DQ27114NC156DQ59 31NC73VDD115/RAS157VDD 32VSS74DQ28116VSS158DQ60 33A075DQ29117A1159DQ61 34A276DQ30118A3160DQ62 35A477DQ31119A5161DQ63 36A678VSS120A7162VSS 37A879CK2121A9163CK3 38A1080NC122BA0164NC 39BA181WP123A11165SA0 40VDD82SDA124VDD166SA1 41VDD83SCL125CK1167SA2 42CK084VDD126NC168VDD NC = No ConnectionVccVssD0 - D8D0 - D8/S0/S2CKE0D0 - D8D0 - D8D0 - D8/WE D0 - D8D0 - D85SDRAMs4SDRAMs+3.3pF cap.SCLWPCK3Serial Presence Detect Table IByte Function describedSPD enrty dataSPD DATA(hex)0Defines # bytes written into serial memory at module mfgr128801Total # bytes of SPD memory device256 Bytes 082Fundamental memory type SDRAM 043# Row Addresses on this assembly A0-A110C 4# Column Addresses on this assembly A0-A8095# Module Banks on this assembly 1BANK 016Data Width of this assembly...x72487... Data Width continuation0008Voltage interface standard of this assemblyLVTTL 019SDRAM Cycletime at Max. Supported CAS Latency (CL).A0Cy cle time for CL=310SDRAM Access from Clock6ns60tAC for CL=311DIMM Configuration type (Non-parity,Parity,ECC)ECC0212Refresh Rate/Type self refresh(15.625uS)8013SDRAM width,Primary DRAM x 80814Error Checking SDRAM data widthx 80815M inimum Clock Delay,Back to Back Random Column Addresses10116Burst Lengths Supported 1/2/4/8/Full page8F 17# Banks on Each SDRAM device4bank0418CAS# Latency 30419CS# Latency 00120Write Latency 00121SDRAM Module Attributes non-buffered,non-registered 0022SDRAM Dev ice Attributes:General Precharge All,Auto precharge0E 23SDRAM Cy cle time(2nd highest CAS latency)13ns D0Cy cle time for CL=224SDRAM Access form Clock(2nd highest CAS latency)7ns 70tAC for CL=225SDRAM Cy cle time(3rd highest CAS latency)N/A00N/A 0026SDRAM Access form Clock(3rd highest CAS latency)27Precharge to Active Minimum 20ns 1428Row Active to Row Active Min.15ns 0F 10ns -8-8-710ns A06ns 60-729RAS to CAS Delay Min 22.5ns 1730Active to Precharge Min50ns32-7,-8-6757.5ns -7,-8-6 5.4ns 54-7,-8-62/306-6N/A 00-6N/A 00-7,-8-622.5ns 17-7,-8-6-7,-8-6-7,-8-620ns 1420ns 1445ns 2DSerial Presence Detect Table II31Density of each bank on module64MByte 1036-61Superset Information (may be used in future)option 0062SPD Revision 63Checksum for bytes 0-62Check sum for -85764-71Manufactures Jedec ID code per JEP-108EMITSUBISHI 1CFFFFFFFFFFFFFF72Manufacturing locationMiyoshi,Japan 01Tajima,Japan 02NC,USA 03Germany 0473-90Manufactures Part Number MH8S72DALD-891-92Revision Code PCB revision rrrr 93-94Manufacturing date year/week code yyww 95-98Assembly Serial Number serial numberssssssss99-125Manufacture Specific Data option 00126Intetl specification frequency100MHz 64127Intel specification CAS# Latency support128+Unused storage locationsopen0032Command and Address signal input setup time 2ns 202033Command and Address signal input hold time1ns 1034Data signal input setup time 2ns 35Data signal input hold time1ns 10rev 1.2A 12Check sum for -717MH8S72DALD-64D483853373244414C442D36202020202020-7AF CL=2/3,AP,CK0,2MH8S72DALD-7-6,-8AD CL=3,AP,CK0,2-6-7,-8-6-7,-8-6-7,-8-6-7,-8Check sum for -6A41.5ns 150.8ns 08151.5ns 0.8ns 08-6-7,-8JEDEC2024D483853373244414C442D372020202020204D483853373244414C442D38202020202020PIN FUNCTIONBASIC FUNCTIONS/S Chip Select : L=select, H=deselect /RAS Command /CAS Command /WE CommandCKE Ref resh Option @ref resh commandA10Precharge Option @precharge or read/write commandCK def ine basic commandsThe MH8S72DALD provides basic functions,bank(row)activate,burst read / write, bank(row)precharge,and auto / self refresh.Each command is defined by control signals of /RAS,/CAS and /WE at CK rising edge. In addition to 3 signals,/S,CKE and A10 are used as chip select,refresh option,and precharge option,respectively.To know the detailed definition of commands please see the command truth table.Activate(ACT) [/RAS =L, /CAS = /WE =H]Read(READ) [/RAS =H,/CAS =L, /WE =H]Write(WRITE) [/RAS =H, /CAS = /WE =L]Precharge(PRE) [/RAS =L, /CAS =H,/WE =L]Auto-Refresh(REFA) [/RAS =/CAS =L, /WE =CKE =H]ACT command activates a row in an idle bank indicated by BA. READ command starts burst read from the active bank indicated by BA.First output data appears after /CAS latency. When A10 =H at this command,the bank is deactivated after the burst read(auto-precharge,READA ). WRITE command starts burst write to the active bank indicated by BA. Total datalength to be written is set by burst length. When A10 =H at this command, the bank is deactivated after the burst write(auto-precharge,WRITEA ). PRE command deactivates the active bank indicated by BA. This command also terminates burst read / write operation. When A10 =H at this command, both banks are deactivated(precharge all, PREA ).REFA command starts auto-refresh cycle. Refresh address including bank address are generated internally. After this command, the banks are precharged automatically.COMMAND TRUTH TABLECOMMAND MNEMONIC CKE n-1CKE n /S /RAS /CAS /WE BA0,1A10A0-9Deselect DESEL H X H X X X X X X No Operation NOP H X L H H H X X X Row Adress Entry &Bank Activate ACT H X L L H H V V V Single Bank Precharge PRE H X L L H L V L X Precharge All Bank PREA H X L L H L X H X Column Address Entry& Write WRITEHXLHLLVLVColumn Address Entry & Write with Auto-Precharge WRITEA H X L H L L V H VColumn Address Entry& Read READ H X L H L H V L VColumn Address Entry & Read with AutoPrecharge READA H X L H L H V H V Auto-Refresh REFA H H L L L H X X X Self-Refresh Entry REFS H L L L L H X X X Self-Refresh Exit REFSX L H H X X X X X X L H L H H H X X X Burst Terminate TERM H X L H H L X X X Mode Register SetMRSHXLLLLLLV*1H =High Level, L = Low Level, V = Valid, X = Don't Care, n = CK cycle number NOTE:1.A7-9 = 0, A0-6 = Mode AddressA11X X V X X VV V V X X X X X LCurrent State/S/RAS/CAS/WE Address Command Action IDLE H X X X X DESEL NOPL H H H X NOP NOPL H H L BA TBST ILLEGAL*2L H L X BA,CA,A10READ/WRITE ILLEGAL*2L L H H BA,RA ACT Bank Active,Latch RAL L H L BA,A10PRE/PREA NOP*4L L L H X REFA Auto-Refresh*5L L L L Op-Code,Mode-AddMRS Mode Register Set*5ROW ACTIVE H X X X X DESEL NOP L H H H X NOP NOPL H H L BA TBST NOPL H L H BA,CA,A10READ/READA Begin Read,Latch CA, Determine Auto-PrechargeL H L L BA,CA,A10WRITE/WRITEABegin Write,Latch CA,Determine Auto-PrechargeL L H H BA,RA ACT Bank Active/ILLEGAL*2 L L H L BA,A10PRE/PREA Precharge/Precharge All L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALREAD H X X X X DESEL NOP(Continue Burst to END) L H H H X NOP NOP(Continue Burst to END)L H H L BA TBST Terminate BurstL H L H BA,CA,A10READ/READA Terminate Burst,Latch CA, Begin New Read,Determine Auto-Precharge*3L H L L BA,CA,A10WRITE/WRITEA Terminate Burst,Latch CA, Begin Write,Determine Auto-Precharge*3L L H H BA,RA ACT Bank Active/ILLEGAL*2L L H L BA,A10PRE/PREA Terminate Burst,Precharge L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALFUNCTION TRUTH TABLEFUNCTION TRUTH TABLE(continued)Current State/S/RAS/CAS/WE Address Command Action WRITE H X X X X DESEL NOP(Continue Burst to END) L H H H X NOP NOP(Continue Burst to END)L H H L BA TBST Terminate BurstL H L H BA,CA,A10READ/READA Terminate Burst,Latch CA, Begin Read,Determine Auto-Precharge*3L H L L BA,CA,A10WRITE/WRITEATerminate Burst,Latch CA,Begin Write,Determine Auto-Precharge*3L L H H BA,RA ACT Bank Active/ILLEGAL*2L L H L BA,A10PRE/PREA Terminate Burst,PrechargeL L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALREAD with H X X X X DESEL NOP(Continue Burst to END) AUTO L H H H X NOP NOP(Continue Burst to END) PRECHARGE L H H L BA TBST ILLEGALL H L H BA,CA,A10READ/READA ILLEGALL H L L BA,CA,A10WRITE/WRITEAILLEGALL L H H BA,RA ACT Bank Active/ILLEGAL*2 L L H L BA,A10PRE/PREA ILLEGAL*2L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALWRITE with H X X X X DESEL NOP(Continue Burst to END) AUTO L H H H X NOP NOP(Continue Burst to END) PRECHARGE L H H L BA TBST ILLEGALL H L H BA,CA,A10READ/READA ILLEGALL H L L BA,CA,A10WRITE/WRITEAILLEGALL L H H BA,RA ACT Bank Active/ILLEGAL*2 L L H L BA,A10PRE/PREA ILLEGAL*2L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALFUNCTION TRUTH TABLE(continued)Current State/S/RAS/CAS/WE Address Command Action PRE -H X X X X DESEL NOP(Idle after tRP) CHARGING L H H H X NOP NOP(Idle after tRP) L H H L BA TBST ILLEGAL*2L H L X BA,CA,A10READ/WRITE ILLEGAL*2L L H H BA,RA ACT ILLEGAL*2L L H L BA,A10PRE/PREA NOP*4(Idle after tRP)L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALROW H X X X X DESEL NOP(Row Active after tRCD ACTIVATING L H H H X NOP NOP(Row Active after tRCD L H H L BA TBST ILLEGAL*2L H L X BA,CA,A10READ/WRITE ILLEGAL*2L L H H BA,RA ACT ILLEGAL*2L L H L BA,A10PRE/PREA ILLEGAL*2L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALWRITE RE-H X X X X DESEL NOP COVERING L H H H X NOP NOPL H H L BA TBST ILLEGAL*2L H L X BA,CA,A10READ/WRITE ILLEGAL*2L L H H BA,RA ACT ILLEGAL*2L L H L BA,A10PRE/PREA ILLEGAL*2L L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALFUNCTION TRUTH TABLE(continued)Current State/S/RAS/CAS/WE Address Command Action RE-H X X X X DESEL NOP(Idle after tRC) FRESHING L H H H X NOP NOP(Idle after tRC) L H H L BA TBST ILLEGALL H L X BA,CA,A10READ/WRITE ILLEGALL L H H BA,RA ACT ILLEGALL L H L BA,A10PRE/PREA ILLEGALL L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALMODE H X X X X DESEL NOP(Idle after tRSC) REGISTER L H H H X NOP NOP(Idle after tRSC) SETTING L H H L BA TBST ILLEGALL H L X BA,CA,A10READ/WRITE ILLEGALL L H H BA,RA ACT ILLEGALL L H L BA,A10PRE/PREA ILLEGALL L L H X REFA ILLEGALL L L L Op-Code,Mode-AddMRS ILLEGALABBREVIATIONS:H = Hige Level, L = Low Level, X = Don't CareBA = Bank Address, RA = Row Address, CA = Column Address, NOP = No Operation NOTES:1. All entries assume that CKE was High during the preceding clock cycle and the current clock cycle.2. ILLEGAL to bank in specified state; function may be legal in the bank indicated by BA,depending on the state of that bank.3. Must satisfy bus contention, bus turn around, write recovery requirements.4. NOP to bank precharging or in idle state.May precharge bank indicated by BA.5. ILLEGAL if any bank is not idle.ILLEGAL = Device operation and / or date-integrity are not guaranteed.FUNCTION TRUTH TABLE FOR CKECurrent State CKEn-1CKEn/S/RAS/CAS/WE Add ActionSELF - H X X X X X X INVALIDREFRESH*1L H H X X X X Exit Self-Refresh(Idle after tRC) L H L H H H X Exit Self-Refresh(Idle after tRC)L H L H H L X ILLEGALL H L H L X X ILLEGALL H L L X X X ILLEGALL L X X X X X NOP(Maintain Self-Refresh) POWER H X X X X X X INVALIDDOWN L H X X X X X Exit Power Down to IdleL L X X X X X NOP(Maintain Self-Refresh) ALL BANKS H H X X X X X Refer to Function Truth Table IDLE*2H L L L L H X Enter Self-RefreshH L H X X X X Enter Power DownH L L H H H X Enter Power DownH L L H H L X ILLEGALH L L H L X X ILLEGALH L L L X X X ILLEGALL X X X X X X Refer to Current State = Power Down ANY STATE H H X X X X X Refer to Function Truth Tableother than H L X X X X X Begin CK0 Suspend at Next Cycle*3 listed above L H X X X X X Exit CK0 Suspend at Next Cycle*3 L L X X X X X Maintain CK0 SuspendABBREVIATIONS:H = High Level, L = Low Level, X = Don't CareNOTES:1. CKE Low to High transition will re-enable CK and other inputs asynchronously.A minimum setup time must be satisfied before any command other than EXIT.2. Power-Down and Self-Refresh can be entered only from the All banks idle State.3. Must be legal command.SIMPLIFIED STATE DIAGRAMIDLEPRE CHARGEAUTO REFRESHSELF MODE REGISTERSETPOWER DOWNREADREADAWRITEWRITEAREAD SUSPENDREADA SUSPENDWRITE SUSPENDWRITEA SUSPENDPOWER ONCLK SUSPENDCKELCKEHCKEHCKEHACTCKEHCKELCKEHWRITEAREADAPREPOWER APPLIEDAutomatic Sequence TBST(for Full Page)TBST(for Full Page)POWER ON SEQUENCEBefore starting normal operation, the following power on sequence is necessary to prevent a SDRAM from damaged or malfunctioning.1. Apply power and start clock. Attempt to maintain CKE high, DQMB0-7 high and NOP condition at the inputs.2. Maintain stable power, stable clock, and NOP input conditions for a minimum of 200us.3. Issue precharge commands for all banks. (PRE or PREA)4. After all banks become idle state (after tRP), issue 8 or more auto-refresh commands.5. Issue a mode register set command to initialize the mode register.After these sequence, the SDRAM is idle state and ready for normal operation.MODE REGISTERCK Burst Length, Burst Type and /CAS Latency can be programmed by setting the mode register(MRS). The mode register stores these date until the next MRS command, which may be issue when both banks are in idle state. After tRSC from a MRS command, the SDRAM is ready for new command.Command AddressCKDQBurst TypeA2A1A0Initial Address BL Sequential InterleavedColumn Addressing000001010011100101110111-00-01-10-11--0012345670123456712345670103254762345670123016745345671232107654456701234567012356701234547610326701234567452301701201231232301300176540123103223013201--11210345632111842CK A0-9,11A10DQOPERATION DESCRIPTIONBANK ACTIVATEOne of four banks is activated by an ACT command.An bank is selected by BA0-1. A row is selected by A0-11.Multiple banks can be active state concurrently by issuing multiple ACT commands.Minimum activation interval between one bank and another bank is tRRD.PRECHARGEAn open bank is deactivated by a PRE command.A bank to be deactivated is designated by BA0-1.When multiple banks are active, a precharge all command (PREA, PRE + A10=H) deactivates all of open banks at the same time. BA0-1 are "Don't Care" in this case.Minimum delay time of an ACT command after a PRE command to the same bank is tRP.READA READ command can be issued to any active bank. The start address is specified by A0-8 (x8) . 1st output data is available after the /CAS Latency from the READ. The consecutive data length is defined by the Burst Length. The address sequence of the burst data is defined by the Burst Type. Minimum delay time of a READ command after an ACT command to the same bank is tRCD.When A10 is high at a READ command, auto-precharge (READA) is performed. Anycommand (READ, WRITE, PRE, ACT, TBST) to the same bank is inhibited till the internal precharge is complete. The internal precharge starts at the BL after READA. The next ACT command can be issued after (BL + tRP) from the previous READA. In any case, tRCD+BL > tRASmin must be met.CK CommandA0-9, 11A10DQCKA10DQCKCL=3 CL=2CK Command A10DQCK Command A10DQWRITE with Auto-Precharge (BL=4)WRITEA WRITE command can be issued to any active bank. The start address is specified by A0-8 (x8). 1st input data is set at the same cycle as the WRITE. The consecutive data length to be written is defined by the Burst Length. The address sequence of burst data is defined by the Burst Type. Minimum delay time of a WRITE command after an ACT command to the same bank is tRCD. From the last input data to the PRE command, the write recovery time (tWR) is required. When A10 is high at a WRITE command, auto-precharge (WRITEA) is performed. Any command (READ, WRITE, PRE, ACT, TBST) to the same bank is inhibited till the internal precharge is complete. The internal precharge starts at tWR after the last input data cycle. The next ACT command can be issued after (BL + tWR -1 + tRP) from the previous WRITEA. In any case, tRCD + BL + tWR -1 > tRASmin must be met.A0-9, 11BA0,1A0-9, 11BA0,1BURST INTERRUPTION[ Read Interrupted by Read ]Burst read oparation can be interrupted by new read of the same or the other bank. Random column access is allowed READ to READ interval is minimum 1 CKCK A10DQ[ Read Interrupted by Write ]Burst read operation can be interrupted by write of any active bank. Random column access is allowed. In this case, the DQ should be controlled adequately by using the DQMB0-7 to prevent the bus contention. The output is disabled automatically 1 cycle after WRITE assertion.CK A10DQA0-9,11BA0,1A0-9,11BA0,1Output disableby DQM by WRITE[ Read Interrupted by Precharge ]A burst read operation can be interrupted by precharge of the same bank . Read to PRE interval is minimum 1 CK. A PRE command output disable latency is equivalent to the /CAS Latency.Read Interrupted by Precharge (BL=4)CKDQDQ CommandDQCommandDQ CL=3CL=2DQCommandDQ[ Read Interrupted by Burst Terminate ]Similarly to the precharge, burst terminate command can interrupt burst read operation and disable the data output. The terminated bank remains active,READ to TBST interval is minimum of 1 CK. A TBSTcommand to output disable latency is equivalent to the /CAS Latency.Read Interrupted by Terminate (BL=4)CKDQCL=3DQDQDQCL=2DQDQ[ Write Interrupted by Write ]Burst write operation can be interrupted by new write of any active bank. Random column access is allowed. WRITE to WRITE interval is minimum 1 CK.Write Interrupted by Write (BL=4)CK Command A10DQWrite Ya 000Write Yb 000Da0Da1Da2Db0Dc0Dc1Write Yc 010Dc2Dc3[ Write Interrupted by Read ]Burst write operation can be interrupted by read of any active bank. Random column access is allowed. WRITE to READ interval is minimum 1 CK. The input data on DQ at the interrupting READ cycle is "don't care".Write Interrupted by Read (BL=4, CL=2)CKA10DQA0-9, 11BA0,1A0-9,11BA0,1don't care[ Write Interrupted by Precharge ]Burst write operation can be interrupted by precharge of the same bank. Write recovery time(tWR) is required from the last data to PRE command. During write recovery, data inputs must be masked by DQM.CKA10DQ[ Write Interrupted by Burst Terminate ]Burst terminate command can terminate burst write operation. In this case, the write recovery time is not required and the bank remains active.The WRITE to TBST minimum interval is 1CK.Write Interrupted by Burst Terminate (BL=4)CKCommandA10DQ ACTX a00TBSTDa0Da1A0-9,11 BA0,1A0-9,11 BA0,1WriteYa00WriteYb00Db0Db1Db2Db3[ Write with Auto-Precharge interrupted by Write or Read to anotehr Bank ]Burst write with auto-precharge can be interrupted by write or read to another bank . Next ACT command can be issued after (BL+tWR-1+tRP) from the WRITEA. Auto-precharge interrrupted by a command to the same bank is inhibited.CK A10DQCK A10DQA0-9,11BA0,1A0-9,11BA0,1[ Read with Auto-Precharge interrupted by Read to anotehr Bank ]Burst read with auto-precharge can be interrupted by read to another bank . Next ACT command can be issued after (BL+tRP) from the READA. Auto-precharge interrrupted by a command to the same bank is inhibited.CK A10DQA0-9,11BA0,1Full Page BurstFull page burst length is available for only the sequential burst type. Full page burst read or write is repeated untill aPrecharge or a Burst Terminate command isissued. In case of the full page burst , a read or write with auto-precharge command is illegal.Single WriteWhen single write mode is set, burst length for write is always one, independently of Burst Length defined by (A2-0).AUTO REFRESHSingle cycle of auto-refresh is initiated with a REFA(/CS=/RAS=/CAS=L,/WE=/CKE=H) command. The refresh address is generated internally. 4096 REFA cycle within 64ms refresh 64Mbit memory cells. The auto-refresh is performed on 4banks concurrently. Before performing an auto-refresh, all banks must be in the idle state. Auto-refresh to auto-refresh interval is minimum tRFC. Any command must not be issued before tRFC from the REFA command.CK/S/RAS/CAS/WECKEA0-11BA0,1Auto Refresh on All Banks Auto Refresh on All BanksSELF REFRESHSelf-refresh mode is entered by issuing a REFS command (/CS=/RAS=/CAS=L,/WE=H, CKE=L). Once the self-refresh is initiated, it is maintained as log as CKE is kept low.During the self-refresh mode, CKE is asynchronous and the only enabled input , all other inputs including CK are disabled and ignored, so that power consumption due to synchronous inputs is saved. To exit the self-refresh, supplying stable CK inputs, asserting DESEL or NOP command and then asserting CKE=H. After tRFC from the 1st CK edge follwing CKE=H, all banks are in the idle state and a new command can be issued after, but DESEL or NOP commands must be asserted till then.CK/S/RAS/CAS/WECKEA0-11BA0,1minimum tRFCfor recoveryCLK SUSPEND and POWER DOWNCKE controls the internal CLK at the following cycle. Figure below shows how CKE works. By negating CKE, the next internal CLK is suspended. The purpose of CLK suspend is power down, output suspend or input suspend. CKE is a synchronous input except during the self-refresh mode. CLK suspend can be performed either when the banks are active or idle. A command at the suspended cycle is ignored.CK(ext.CLK)CKEint.CLKCK CKE CKECK DQCKEDQM CONTROLDQMB0-7 is a dual function signal defined as the data mask for writes and the output disable for reads. During writes, DQMB0-7 masks input data word by word. DQMB0-7 to Data In latency is 0.During reads, DQMB0-7 forces output to Hi-Z word by word. DQMB0-7 to output Hi-ZCKCommandDQdisabled by DQMB=HABSOLUTE MAXIMUM RATINGSRECOMMENDED OPERATING CONDITION (Ta=0 ~ 70°C, unless otherwise noted)1:VIH(max)=5.5V f or pulse width less than 10ns.2.VIL(min)=-1.0 f or pulse width less than 10ns. CAPACITANCEAVERAGE SUPPLY CURRENT from Vdd(Ta=0 ~70°C, Vdd = 3.3 ± 0.3V, Vss = 0V, unless otherwise noted)AC OPERATING CONDITIONS AND CHARACTERISTICS(Ta=0 ~ 70°C, Vdd = 3.3 ± 0.3V, Vss = 0V, unless otherwise noted)Symbol Parameter Test Condition LimitsUnit Min.Max.VOH(DC)High-Level Output Voltage(DC)IOH=-2mA 2.4V VOL(DC)Low-Level Output Voltage(DC)IOL=2mA 0.4VVOH(AC)High-Level Output Voltage(AC)CL=50pF, IOH=-2mA 2V VOL(AC)Low-Level Output Voltage(AC)CL=50pF, IOL=2mA 0.8VIOZ Off-stare Output Current Q floating VO=0 ~ Vdd -55uA Ii Input Current VIH=0 ~ Vdd+0.3V -4545uA Note)1:Icc(max) is specif ied at the output open condition.2.Input signals are changed one time during 30ns.6301891806309909135270225-7, -8Test ConditionLimits (max)Unit tRC=min.tCLK=min, BL=1,CL=3mA CKE=L,tCLK=15ns, /CS>Vcc-0.2V mA CKE=CLK=L, /CS>Vcc-0.2VmA mA tCLK=min, BL=4, CL=3,all banks activ e(discerte)mA tRC=min, tCLK=min mA CKE <0.2VmACKE=H,tCLK=15ns,VIH>Vcc-0.2V,VIL<0.2V Symbol Icc1Icc2P Icc2PS Icc2NSIcc4Icc5Icc6Icc2N Parameteroperating currentone bank activ e (discrete)precharge stanby currentin power-down mode burst currentauto-refresh current self-refresh currentCKE=H,CLK=L,VIH>Vcc-0.2V,VIL<0.2V(f ixed)mA precharge stanby current in non power-down mode mA CKE=H,tCLK=15nsIcc3NS Icc3N CKE=H,CLK=LmA active stanby currentin non power-down modeone bank activ e (discrete)67518918081011709135270225-6AC TIMING REQUIREMENTS (SDRAM Component)(Ta=0 ~ 70°C, Vdd = 3.3 ± 0.3V, Vss = 0V, unless otherwise noted)Input Pulse Levels: 0.8V to 2.0V Input Timing Measurement Level: 1.4VCKSignal1.4V1.4VAny AC timing is referenced to the inputsignal crossing through 1.4V.Note:1 The timing requirements are assumed tT=1ns.If tT is longer than 1ns,(tT-1)ns should be added to the parameter.Limits Symbol Parameter -7Unit Min.Max.tCLK CK cycle timenstCH CK High pulse width 310ns tCL CK Low pilse width 3ns tT Transition time of CK 110nstIS Input Setup time(all inputs)2ns tIH Input Hold time(all inputs)1ns tRC Row cycle time 70ns tRCD Row to Column Delay 20nstRAS Row Active time 50100KnstRP Row Precharge time 20ns tWR Write Recovery time 20ns tRRD Act to Act Deley time20ns tRSC Mode Register Set Cycle time 10ns tSRX Self Refresh Exit time 10ns tREFRefresh Interval time64ms-8Min.Max.313311021702050100K 202020101064CL=2CL=31010ns -6Min.Max.2.5102.51101.50.867.52045100K 201515107.5647.5tRFC Refresh cycle time 80ns 8075tPDE Power Down Exit time 10ns 107.51.4V1.4VDQCKtACtOHtOHZSWITCHING CHARACTERISTICS (SDRAM Component)(Ta=0 ~ 70°C, Vdd = 3.3 ± 0.3V, Vss = 0V, unless otherwise note3)Output Load ConditionV OUTFor -63ns32.7CL=3Burst Write (single bank) @BL=4/CS/RAS/CAS /WECKE BA0,1DQACT#0WRITE#0PRE#0ACT#0WRITE#0CLKItalic parameter indicates minimum caseA0-8A10DQM A9,11Burst Write (multi bank) @BL=4/CS /RAS/CAS /WECKE BA0,1DQXX X 0Y01D0D0D0D0X X 0YD0D0D0D0ACT#0WRITE#0PRE#0ACT#0WRITE#001234567891011121314151617tRCDtRAS tWRtRPtRCtRCDD1D1D1D1XX X 1tRRD YtWR0X1XXX2tRRDACT#1WRITE#1PRE#1ACT#2CLKItalic parameter indicates minimum caseA0-8A10DQM A9,11。

艾瑟顿198931产品说明书

Eaton 198931Eaton Moeller® series Rapid Link - Speed controllers, 8.5 A, 4 kW, Sensor input 4, Actuator output 2, 400/480 V AC, Ethernet IP, HAN Q4/2, with manual override switch, with braking resistance, STO (Safe Torque Off), with fanGeneral specificationsEaton Moeller® series Rapid Link Speed controller198931195 mm270 mm 220 mm 3.81 kgCEIEC/EN 61800-5-1 UL approval UL 61800-5-1 RoHSRASP5-8424EIP-412R111S1Product NameCatalog NumberProduct Length/Depth Product Height Product Width Product Weight Certifications Catalog Notes Model Code3 fixed speeds and 1 potentiometer speedcan be switched over from U/f to (vector) speed control Connection ofInternal and on heat sink, temperature-controlled Fan Parameterization: KeypadParameterization: FieldbusParameterization: drivesConnect mobile (App) Parameterization: drivesConnectSelector switch (Positions: REV - OFF - FWD)Control unitManual override switchKey switch position OFF/RESETKey switch position HANDThermo-click with safe isolationFanBreaking resistanceTwo sensor inputs through M12 sockets (max. 150 mA) for quick stop and interlocked manual operation2 Actuator outputsInternal DC linkPC connectionKey switch position AUTOIGBT inverterBraking resistancePTC thermistor monitoring4-quadrant operation possibleFor actuation of motors with mechanical brakeBrake chopper with braking resistance for dynamic braking1 potentiometer speedSTO (Safe Torque Off)3 fixed speeds IP65NEMA 121st and 2nd environments (according to EN 61800-3)IIISpeed controllerEtherNet/IPC2, C3: depending on the motor cable length, the connected load, and ambient conditions. External radio interference suppression filters (optional) may be necessary.C1: for conducted emissions only2000 VAC voltageCenter-point earthed star network (TN-S network)Phase-earthed AC supply systems are not permitted.Vertical15 g, Mechanical, According to IEC/EN 60068-2-27, 11 ms, Half-sinusoidal shock 11 ms, 1000 shocks per shaftResistance: 10 - 150 Hz, Oscillation frequencyResistance: 57 Hz, Amplitude transition frequency on accelerationResistance: 6 Hz, Amplitude 0.15 mmResistance: According to IEC/EN 60068-2-6Features Fitted with:FunctionsDegree of protectionElectromagnetic compatibilityOvervoltage categoryProduct categoryProtocolRadio interference classRated impulse withstand voltage (Uimp)System configuration typeMounting positionShock resistanceVibrationsupply voltagevia adaptercable on roundor flexiblebusbar junctionDiagnostics andreset on thedevice and viaEthernet IPintegrated PTCthermistormonitoring andThermoclick withsafe isolationoptional: 4sensor inputswith M12-Yadapter forswitchover tocreep speedoptional: Fasterstop if external24 V failsTwo sensorinputs throughM12 sockets(max. 150 mA)for quick stopand interlockedmanualoperationwith AUTO -OFF/RESET -HAND keyswitcheswith selectorswitch REV -OFF - FWDAbove 1000 m with 1 % performance reduction per 100 m Max. 2000 m-10 °C40 °C-40 °C70 °CIn accordance with IEC/EN 50178< 95 %, no condensation Adjustable, motor, main circuit0.8 - 8.5 A, motor, main circuit< 10 ms, Off-delay< 10 ms, On-delay98 % (η)7.8 A3.5 mA120 %Maximum of one time every 60 seconds 380 V480 V380 - 480 V (-10 %/+10 %, at 50/60 Hz)PM and LSPM motorsSensorless vector control (SLV) Synchronous reluctance motorsU/f controlBLDC motors0 Hz500 HzAt 40 °CFor 60 s every 600 s12.7 AAltitudeAmbient operating temperature - min Ambient operating temperature - max Ambient storage temperature - min Ambient storage temperature - max Climatic proofing Current limitationDelay timeEfficiencyInput current ILN at 150% overload Leakage current at ground IPE - max Mains current distortionMains switch-on frequencyMains voltage - minMains voltage - maxMains voltage toleranceOperating modeOutput frequency - minOutput frequency - maxOverload currentOverload current IL at 150% overload45 Hz66 Hz8.5 A at 150% overload (at an operating frequency of 8 kHz and an ambient air temperature of +40 °C)4 kW400 V AC, 3-phase480 V AC, 3-phase0.1 Hz (Frequency resolution, setpoint value)200 %, IH, max. starting current (High Overload), For 2 seconds every 20 seconds, Power section50/60 Hz8 kHz, 4 - 32 kHz adjustable, fPWM, Power section, Main circuitAC voltageCenter-point earthed star network (TN-S network)Phase-earthed AC supply systems are not permitted.5 HP≤ 0.6 A (max. 6 A for 120 ms), Actuator for external motor brakeAdjustable to 100 % (I/Ie), DC - Main circuit≤ 30 % (I/Ie)400/480 V AC -15 % / +10 %, Actuator for external motor brake765 VDC10 kAType 1 coordination via the power bus' feeder unit, Main circuit24 V DC (-15 %/+20 %, external via AS-Interface® plug)400/480 V AC (external brake 50/60 Hz)Ethernet IP, built inPlug type: HAN Q4/2 Specification: S-7.4 (AS-Interface®) C1 ≤ 1 m, maximum motor cable length C3 ≤ 25 m, maximum motor cable length C2 ≤ 5 m, maximum motor cable lengthRated frequency - minRated frequency - maxRated operational current (Ie)Rated operational power at 380/400 V, 50 Hz, 3-phase Rated operational voltageResolutionStarting current - maxSupply frequencySwitching frequencySystem configuration type Assigned motor power at 460/480 V, 60 Hz, 3-phase Braking currentBraking torqueBraking voltageSwitch-on threshold for the braking transistorRated conditional short-circuit current (Iq)Short-circuit protection (external output circuits) Rated control voltage (Uc)Communication interfaceConnectionInterfacesCable lengthNumber of slave addresses: 31 (AS-Interface®)Max. total power consumption from AS-Interface® power supply unit (30 V): 250 mAMeets the product standard's requirements.Meets the product standard's requirements.Meets the product standard's requirements.Meets the product standard's requirements.Meets the product standard's requirements.Does not apply, since the entire switchgear needs to be evaluated.Does not apply, since the entire switchgear needs to be evaluated.Meets the product standard's requirements.Does not apply, since the entire switchgear needs to be evaluated.Meets the product standard's requirements.Does not apply, since the entire switchgear needs to be evaluated.Does not apply, since the entire switchgear needs to be evaluated.Is the panel builder's responsibility.Is the panel builder's responsibility.Is the panel builder's responsibility.Is the panel builder's responsibility.10.2.2 Corrosion resistance10.2.3.1 Verification of thermal stability of enclosures 10.2.3.2 Verification of resistance of insulating materials to normal heat10.2.3.3 Resist. of insul. mat. to abnormal heat/fire by internal elect. effects10.2.4 Resistance to ultra-violet (UV) radiation 10.2.5 Lifting10.2.6 Mechanical impact10.2.7 Inscriptions10.3 Degree of protection of assemblies10.4 Clearances and creepage distances 10.5 Protection against electric shock10.6 Incorporation of switching devices and components 10.7 Internal electrical circuits and connections 10.8 Connections for external conductors 10.9.2 Power-frequency electric strength 10.9.3 Impulse withstand voltageIs the panel builder's responsibility.The panel builder is responsible for the temperature rise calculation. Eaton will provide heat dissipation data for the devices.Is the panel builder's responsibility. The specifications for the switchgear must be observed.Is the panel builder's responsibility. The specifications for the switchgear must be observed.The device meets the requirements, provided the information in the instruction leaflet (IL) is observed.Generation change from RA-MO to RAMO 4.0Generation Change RA-SP to RASP5Generation change RAMO4 to RAMO5Configuration to Rockwell PLC for Rapid LinkGeneration Change RASP4 to RASP5Generation change from RA-SP to RASP 4.0Rapid Link 5 - brochureDA-SW-drivesConnect - installation helpDA-SW-USB Driver PC Cable DX-CBL-PC-1M5DA-SW-Driver DX-CBL-PC-3M0DA-SW-drivesConnect - InstallationshilfeDA-SW-drivesConnectDA-SW-USB Driver DX-COM-STICK3-KITMaterial handling applications - airports, warehouses and intra-logistics ETN.RASP5-8424EIP-412R111S1.edzIL034093ZUrasp5_v34.stpramo5_v34.dwgDA-DC-00004184.pdfDA-DC-00003964.pdfDA-DC-00004613.pdfDA-DC-00004612.pdfeaton-bus-adapter-rapidlink-speed-controller-dimensions-005.eps eaton-bus-adapter-rapidlink-speed-controller-dimensions-002.eps eaton-bus-adapter-rapidlink-speed-controller-dimensions-004.eps eaton-bus-adapter-rapidlink-speed-controller-dimensions-003.eps10.9.4 Testing of enclosures made of insulating material10.10 Temperature rise10.11 Short-circuit rating10.12 Electromagnetic compatibility 10.13 Mechanical function Applikasjonsmerknader BrosjyrereCAD model Installeringsinstruksjoner mCAD model SertifiseringsrapporterTegningerEaton Corporation plc Eaton House30 Pembroke Road Dublin 4, Ireland © 2023 Eaton. Med enerett. Eaton is a registered trademark.All other trademarks areproperty of their respectiveowners./socialmedia。

IRLML6401TRPBF;中文规格书,Datasheet资料

Fig 1. Typical Output Characteristics

Fig 2. Typical Output Characteristics

100.0

2.0

-I D , Drain-to-Source Current (Α )

T J = 25°C

10.0

RDS(on) , Drain-to-Source On Resistance (Normalized)

0.1

20µs PULSE WIDTH Tj = 25°C

0.01 0.1 1 10 100

20µs PULSE WIDTH Tj = 150°C

0.01 0.1 1 10 100

-V DS , Drain-to-Source Voltage (V)

-VDS, Drain-to-Source Voltage (V)

1200 VGS = 0V, f = 1 MHZ Ciss = C gs + Cgd, C ds SHORTED Crss = C gd

10

ID = -4.3A VDS =-10V

1000

-VGS , Gate-to-Source Voltage (V)

C, Capacitance(pF)

800

Ciss

Min. Typ. Max. Units ––– ––– ––– ––– ––– ––– ––– ––– 22 8.0 -1.3 A -34 -1.2 33 12 V ns nC

Conditions MOSFET symbol showing the G integral reverse p-n junction diode. TJ = 25°C, IS = -1.3A, VGS = 0V TJ = 25°C, IF = -1.3A di/dt = -100A/µs

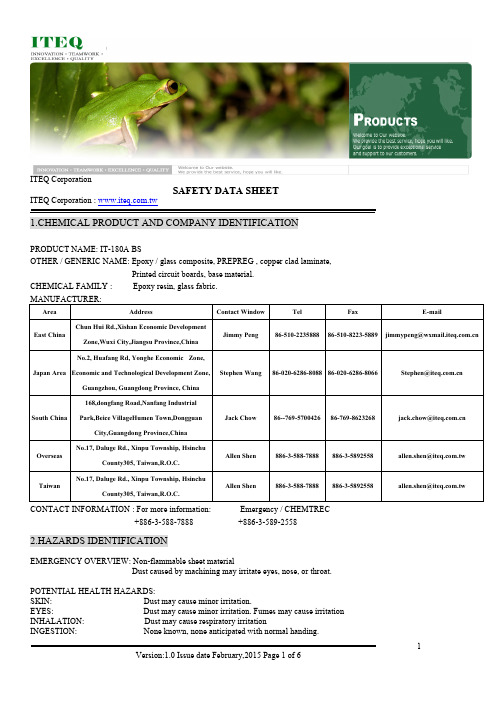

ITEQ Corporation IT-180A BS 安全数据表说明书

ITEQ CorporationSAFETY DATA SHEET1.CHEMICAL PRODUCT AND COMPANY IDENTIFICATIONPRODUCT NAME: IT-180A BSOTHER / GENERIC NAME: Epoxy / glass composite, PREPREG , copper clad laminate,Printed circuit boards, base material.CHEMICAL FAMILY : Epoxy resin, glass fabric.MANUFACTURER:Area Address Contact Window Tel Fax E-mailEast ChinaChun Hui Rd.,Xishan Economic DevelopmentZone,Wuxi City,Jiangsu Province,ChinaJimmy Peng 86-510-2235888 86-510-8223-5889 *********************Japan AreaNo.2, Huafang Rd, Yonghe Economic Zone,Economic and Technological Development Zone,Guangzhou, Guangdong Province, ChinaStephen Wang 86-020-6286-8088 86-020-6286-8066 ****************.cnSouth China168,dongfang Road,Nanfang IndustrialPark,Beice VillageHumen Town,DongguanCity,Guangdong Province,ChinaJack Chow 86--769-5700426 86-769-8623268 ******************.cnOverseasNo.17, Daluge Rd., Xinpu Township, HsinchuCounty305, Taiwan,R.O.C.Allen Shen 886-3-588-7888 886-3-5892558 *******************.tw TaiwanNo.17, Daluge Rd., Xinpu Township, HsinchuCounty305, Taiwan,R.O.C.Allen Shen 886-3-588-7888 886-3-5892558 *******************.tw CONTACT INFORMATION : For more information: Emergency / CHEMTREC+886-3-588-7888 +886-3-589-25582.HAZARDS IDENTIFICATIONEMERGENCY OVERVIEW: Non-flammable sheet materialDust caused by machining may irritate eyes, nose, or throat.POTENTIAL HEALTH HAZARDS:SKIN: Dust may cause minor irritation.EYES: Dust may cause minor irritation. Fumes may cause irritationINHALATION: Dust may cause respiratory irritationINGESTION: None known, none anticipated with normal handing.ITEQ CorporationSAFETY DATA SHEETClassifiable or probably non-carcinogenic (Group 3 ).Ingredients found on any of OSHA’s carcinogen lists are listed below.INGREDIENT NAME: NTP STATUS: IARC STATUS: OSHA LISTNone N/A N/A N/APOSITION / INFORMATION ON INGREDIENTSINGREDIENT NAME: CAS# % w/wGlass cloth 65997-17-3 40~70%B-Stage semi-cured epoxy of Multi-function resin 026265-08-7 40~70%Fillers type SiO2 powder 14808-60-7 10~20%We don’t have PFOSFor local ”Right to Know” compliance and other reasons, trace ingredients not listed above may appear in Section 15, Regulatory Information.4.FIRST AID MEASURESSKIN: Wash promptly with soap and running water. Do not rub or scratch.If irritation persists, consult physician.Remove contaminated clothing and wash thoroughly before reuseEYES: Flush immediately with plenty of low-pressure water for at least 20Minutes.Do not rub or scratch.If irritation persists, consult physician.INHALATION: Move to fresh air.Consult physician.INGESTION: If large amounts are ingested, consult physician.ADVICE TO PHYSICIAN:Treat symptomatically5.FIRE-FIGHTING MEASURESFLASH POINT: N/AFLASH POINT METHOD: N /AAUTOIGNITION TEMP: Not determined.UPPER FLAME LIMIT: N/ALOWER FLAME LIMIT: N/AFLAME PROPAGATION RATE: UL 94 V-0ITEQ CorporationSAFETY DATA SHEETEXTINGUISHING MEDIA: Water, CO2, foam, dry chemical, Halon.UNUSUAL FIRE ANDEXPLOSION HAZARDS:May give off toxic hydrogen bromide fumes when thermallyDecomposed.SPECIAL FIRE-FIGHTINGPROCEDURES:Wear proper protective equipment and self-contained breathingApparatus.6.ACCIDENTAL RELEASE MEASURESRESPONSE TO RELEASE: If material is not contaminated, return to container for use.If material is contaminated, pick up and place in container for disposal.Material is an article. Spill or release to the environment is unlikely. 7.HANDLING AND STORAGENORMAL HANDLING: Always wear recommended personal protective equipment. STORAGE: Store in a cool dry place.8.ENGINEERING CONTROLS / PERSONAL PROTECTIONENGINEERING CONTROLS:VENTILATION: Adequate ventilation should be provided to keep dust concentrationswithin acceptable exposure limits. Discharge from the ventilationsystem should comply with applicable air pollution control regulation GENERAL: Eyewash fountains and safety showers should be easily accessible. PERSONAL PROTECTIVE EQUIPMENT:SKIN PROTECTION: Impervious gloves and clothing should be worn for prolonged orRepeated contact.EYE PROTECTION: Safety glassesRESPIRATORY PROTECTION:Atmospheric levels of fibrous glass, copper, and other dusts should bemaintained below recommended exposure guidelines.If airborne contaminant is likely to exceed acceptable limits, use aNIOSH-approved respirator.ADDITIONAL: N/ARECOMMENDATIONS: N/AEXPOSURE GUIDELINES:INGREDIENT NAME: CAS# ACGIH TLV OSHA PEL OTHER LIMITSITEQ CorporationSAFETY DATA SHEET9.PHYSICAL AND CHEMICAL CHARACTERISTICSAPPEARANCE: Amber, gold, or yellow sheets which may have copper cladding on oneor both sides.PHYSICAL STATE: Solid.ODOR: None unless heated.BOILING POINT: N/AMELTING POINT: N/AMOLECULAR WEIGHT:N/ACHEMICAL FORMULA:N/APH: N/ASOLUBILITY IN WATER:InsolubleVAPOR PRESSURE: N/AVAPOR DENSITY: N/ASPECIFIC GRAVITY: 1.6-1.9EVAPORATION RATE: N/A%VOLATILES: <1.5%10. STABILITY AND REACTIVITYNORMALLY STABLE: YES.INCOMPATIBILITIES: Not determinedHAZARDOUS: CO, CO2, HBr, aromatic or aliphatic hydrocarbons. DECOMPOSITION PRODUCTS: Laser processing may result in copper fumes.HAZARDOUSPOLYMERIZATION: None11.TOXICOLOGICAL INFORMATIONIMMEDIATE ( ACUTE )EFFECTS:Dust may cause eye, skin, and respiratory irritation. DELAYED ( SUBCHRONIC ANDCHRONIC ) EFFECTS:NTP and IARC consider respirable glass wool a possible humanCarcinogen.IARC consider continuous glass filaments unclassifiable orNon-carcinogenic ( Group 3 ).ITEQ CorporationSAFETY DATA SHEET12.ECOLOGICAL INFORMATIONNot biodegradable.13.DISPOSAL CONSIDERATIONSRCRA HAZARDOUS WASTE: No.WASTE DISPOSAL METHOD: Landfill.Do not incinerate.Recycle copper.Disposal must comply with all local, regional, and national regulations. Information supplied here is for the material as shipped. Use or alteration of the product such as mixingwith other materials such as lead solder during the printed circuit boards fabrications process maychange the RCRA classification of the mixture and require alternative disposal procedures.14.TRANSPORTATION INFORATIONUS DOT HAZARD CLASS : Not regulated.US DOT ID NUMBER: N/A15.REGULATORY INFORMATIONTSCA INVENTORY STATUS : Resin system components used in this product are on the TSCAInventory list.OTHER TSCA ISSUES: None.16. Other materialSAFETY DATA SHEETRemark : This MSDS , described as satisfactorily as possible, does not cover every case of danger . Hazard information on paint product is estimated as a mixturebased on that of individual raw materials . Additionally , your use of thisinformation is beyond our control and may be beyond our knowledge.Therefore, the information is provided without any representation orWarranty express or implied.。

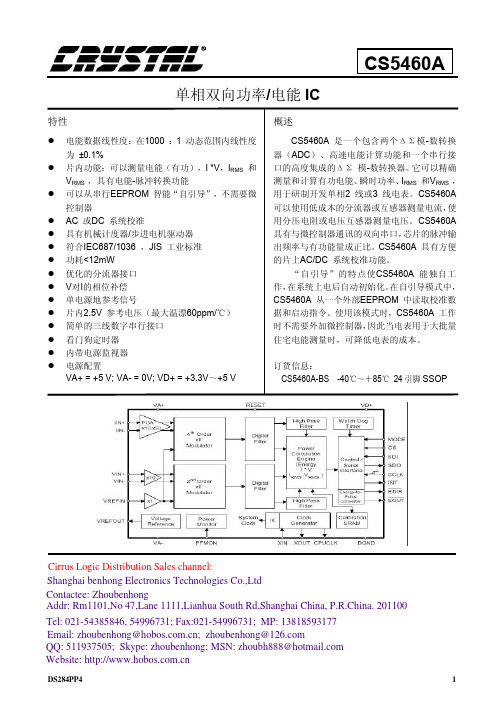

CS5460A中文数据手册

l 片内功能:可以测量电能(有功),I *V,IRMS 和 VRMS ,具有电能-脉冲转换功能

l 可以从串行EEPROM 智能“自引导”,不需要微 控制器

l AC 或DC 系统校准 l 具有机械计度器/步进电机驱动器 l 符合IEC687/1036 ,JIS 工业标准 l 功耗<12mW l 优化的分流器接口 l V对I的相位补偿 l 单电源地参考信号 l 片内2.5V 参考电压(最大温漂60ppm/℃) l 简单的三线数字串行接口 l 看门狗定时器 l 内带电源监视器 l 电源配置

VA+ = +5 V; VA- = 0V; VD+ = +3.3V~+5 V

概述

CS5460A 是一个包含两个ΔΣ模-数转换 器(ADC)、高速电能计算功能和一个串行接 口的高度集成的ΔΣ 模-数转换器。它可以精确 测量和计算有功电能、瞬时功率、IRMS 和VRMS , 用于研制开发单相2 线或3 线电表。CS5460A 可以使用低成本的分流器或互感器测量电流,使 用分压电阻或电压互感器测量电压。CS5460A 具有与微控制器通讯的双向串口,芯片的脉冲输 出频率与有功能量成正比。CS5460A 具有方便 的片上AC/DC 系统校准功能。

cs5460a单相双向功率电能ic特性rms具有电能脉冲转换功能可以从串行eeprom智能自引导不需要微控制器ac或dc系统校准符合iec6871036jis工业标准片内25v参考电压最大温漂60ppm电源配置va0v

FOXBORO I A Series HARDWARE产品规格说明书

FOXBORO ®The FBM214 HART ® Communication Input Interface Module provides eight input channels, each accepting a 4 to 20mA analog signal or a digital HART signal superimposed on a 4 to 20 mA analog input signal.FEATURESKey features of the FBM214 module are:Eight analog input channels, each accepting oneof the following inputs:•Standard 4 to 20 mA analog sensor signal •Digital HART Frequency Shift Keying (FSK) signal superimposed on a 4 to 20 mA analog input signal.FSK modem dedicated to each input channel forbi-directional digital communications with a HART field deviceAnalog to digital conversion of each of the 4to20mA input signals from the HART devicesSupport for the HART universal commandsnecessary to interface the field device with the I/A Series ® system databaseGalvanic isolation of the group of 8 inputchannels from ground and module logicCompact, rugged design suitable for enclosure inClass G3 (harsh) environmentsHigh accuracy achieved by sigma-delta dataconversions for each channelTermination Assemblies (TAs) for locally orremotely connecting field wiring to the FBM214Termination Assemblies for per channel internallyand/or externally loop powered transmitters.PSS 21H-2Z14 B4 Page 2OVERVIEWThe FBM214 HART Communication Input Interface Module contains eight 4to20mA group isolated analog input channels. The FBM214 supports any mix of standard 4to20mA devices and HART devices.The FBM214 serves as a HART communications field device host, enabling the I/A Series system to request and receive two digital messages per second from the field device. The message pass-through capability can be used to support HART universal, common practice, and device-specific commands, but not the burst communication mode. These commands are implemented using the Intelligent Field Device Configurator (IFDC — refer toPSS 21S-8A3 B3 for details).The FBM214 provides a common isolated power supply to power all eight channels. Optionally, the channels can be powered by an external power supply. However, when a common external power supply is used with two or more channels, a Cable Balun module is required to prevent channel cross talk.COMPACT DESIGNThe FBM214 has a compact design, with a rugged extruded aluminum exterior for physical protection of the circuits. Enclosures specially designed for mounting the FBMs provide various levels of environmental protection, up to harsh environments per ISA Standard S71.04.HIGH ACCURACYFor high accuracy, the module incorporates a Sigma-Delta converter which can provide new analog input values for each channel every 100 milliseconds.VISUAL INDICATORSLight-emitting diodes (LEDs) incorporated into the front of the module provide visual indication of the module’s operational status, and communication activity on the channels.EASY REMOVAL/REPLACEMENTThe module can be removed/replaced without removing field device termination cabling, power, or communications cabling.FIELDBUS COMMUNICATIONA Fieldbus Communication Module or a Control Processor interfaces the redundant 2 Mbps module Fieldbus used by the FBMs. The FBM214 module accepts communication from either path (A or B) of the redundant 2 Mbps fieldbus – should one path fail or be switched at the system level, the module continues communication over the active path.The use of an external power supply common to two or more loops requires a Cable Balun Module to maintain communication signal line balance.MODULAR BASEPLATE MOUNTINGThe module mounts on a modular baseplate which accommodates up to four or eight FBMs. The modular baseplate is either DIN rail mounted or rack mounted, and includes signal connectors for redundant fieldbus, redundant independent dc power, and termination cables.TERMINATION ASSEMBLIESField input signals connect to the FBM subsystem via DIN rail mounted TAs. The TAs used with theFBM214 are described in “TERMINATION ASSEMBLIES AND CABLES” on page8.PSS 21H-2Z14 B4Page 3CABLE BALUN MODULEThe Cable Balun module is used to maintain digital communication line balance for HART Transmitter to FBM loops that are powered from a common external power supply. This powering effectively connects one line of each loop together. Without the Baluns, in each loop so powered, the common connection at the external power supply, would cause near end crosstalk at the system end of the loop wiring cable. Loops using FBM internal power source do not require Baluns.The Cable Balun module contains multiple Baluns. One Balun segment is interconnected in each loop powered from an external power supply per the diagram above. There is one Cable Balun module.Figure 1. Cable Balun Module Cable Balun ModuleModule Model ModulePart No.No. of Balunsin the ModuleCBM-4P0903SV4PSS 21H-2Z14 B4Page 4FUNCTIONAL SPECIFICATIONSField Device ChannelsVERSION SUPPORTEDHART Protocol v6INTERFACE8 group-isolated channelsCOMMUNICATION TO THE DEVICEPoint-to-point, master/slave, asynchronous, half-duplex, at 1200 baud.ERROR CHECKINGParity on each byte, and one CRC check byte.SPEED2 messages per secondFASTEST ALLOWED ECB BLOCK PERIOD500 msecMAXIMUM DISTANCE (FBM214 TO FIELDDEVICE)Meets HART FSK physical layer specificationHCF_SPEC-54, Revision 8.1 [up to 3030 m(10000ft)](1).COMPLIANCE VOLTAGE18 V dc minimum at 20.5 mACURRENT INPUTSSense Resistor61.9 Ω nominalTotal Input Resistance280 Ω minimumAccuracy (Includes Nonlinearity)±0.03% of full scaleTemperature Coefficient50 ppm/ºCResolution15 bitsUpdate Rate100 msIntegration Time500 msCommon Mode Rejection>100 db at 50 or 60 HzNormal Mode Rejection>35 db at 50 or 60 HzMAXIMUM LOOP RESISTANCE280 Ω (not including the field device)(2)LOOP POWER SUPPLY PROTECTIONEach channel is galvanically group isolated,current limited and voltage regulated. All inputsare limited by their design to less than 30 mA. Ifthe current limit circuit shorts out, the current islimited to about 85 mA.FBM INPUT IMPEDANCE280 Ω minimumFBM INTERNAL POWER FOR FIELD DEVICE24 V dc ±10% common power supply for allchannels. Loop load limited to one device perchannel.ISOLATIONThe channels are not galvanically isolated fromeach other, but are galvanically isolated (bothoptical and transformer isolation) as a group from ground and module logic. Inputs use an internal FBM isolated power supply for field power. Themodule withstands, without damage, a potential of 600 V ac applied for one minute between the group-isolated channels and earth (ground).CAUTIONThis does not imply that these channels areintended for permanent connection tovoltages of these levels. Exceeding the limitsfor input voltages, as stated elsewhere in thisspecification, violates electrical safety codesand may expose users to electric shock. Fieldbus CommunicationCommunicates with its associated FCM or FCP via the redundant 2 Mbps module FieldbusHEAT DISSIPATION4 W (maximum)(1)The maximum allowable distance decreases when the loop is operated through an intrinsic safety barrier. The maximum distance ofthe field device from the FBM is a function of compliance voltage, wire gauge and voltage drop at the device.(2)In an intrinsic safety application, if a zener barrier is used between the FBM and the field device, the power supply must be set at24V dc +5%, -1%. There are no specific constraints with the use of galvanic barriers.PSS 21H-2Z14 B4Page 5 FUNCTIONAL SPECIFICATIONS (CONTINUED)Power RequirementsINPUT VOLTAGE RANGE (REDUNDANT)24V dc ±5%CONSUMPTION7 W (maximum)Regulatory ComplianceELECTROMAGNETIC COMPATIBILITY (EMC) European EMC Directive 89/336/EECMeets:EN 50081-2 Emission standardEN 50082-2 Immunity standardEN 61326 Annex A (Industrial Levels) CISPR 11, Industrial Scientific and Medical(ISM) Radio-frequency Equipment -Electromagnetic Disturbance Characteristics- Limits and Methods of MeasurementMeets Class A LimitsIEC 61000-4-2 ESD ImmunityContact 4 kV, air 8 kVIEC 61000-4-3 Radiated Field Immunity10 V/m at 80 to 1000 MHzIEC 61000-4-4 Electrical FastTransient/Burst Immunity2 kV on I/O, dc power and communicationlinesIEC 61000-4-5 Surge Immunity2kV on ac and dc power lines; 1kV on I/Oand communications linesIEC 61000-4-6 Immunity to ConductedDisturbances Induced by Radio frequencyFields10 V (rms) at 150 kHz to 80 MHz on I/O,dc power and communication linesIEC 61000-4-8 Power Frequency MagneticField Immunity30 A/m at 50 and 60 HzPRODUCT SAFETY (FBM AND CABLE BALUN) Underwriters Laboratories (UL) for U.S. andCanadaUL/UL-C listed as suitable for use inUL/UL-C listed Class I, Groups A-D;Division 2; temperature code T4 enclosurebased systems. These modules are also ULand UL-C listed as associated apparatus forsupplying non-incendive communicationcircuits for Class I, Groups A-D hazardouslocations when connected to specifiedI/A Series® processor modules as describedin the I/A Series DIN Rail MountedSubsystem User’s Guide (B0400FA). Wherepower is supplied by the FBM,communications circuits also meet therequirements for Class2 as defined inArticle725 of the National Electrical Code(NFPA No.70) and Section 16 of theCanadian Electrical Code (CSA C22.1).Conditions for use are as specified in theI/A Series DIN Rail Mounted SubsystemUser’s Guide (B0400FA).European Low Voltage Directive 73/23/EECand Explosive Atmospheres (ATEX) directive94/9/ECCENELEC (DEMKO) certified as EEx nA IICT4 for use in CENELEC certified Zone 2enclosure certified as associated apparatusfor supplying non-incendive field circuits forZone 2, Group IIC, potentially explosiveatmospheres when connected to specifiedI/A Series processor modules as describedin the I/A Series DIN Rail MountedSubsystem User’s Guide (B0400FA). Also,see Table1 on page9.Calibration RequirementsCalibration of the module or termination assembly is not required.PSS 21H-2Z14 B4Page 6ENVIRONMENTAL SPECIFICATIONS(3)OperatingTEMPERATUREModule-20 to +70°C (-4 to +158°F)Termination AssemblyPVC-20 to +50°C (-4 to +122°F)PA-20 to +70°C (-4 to +158°F) RELATIVE HUMIDITY5 to 95% (noncondensing)ALTITUDE-300 to +3,000m (-1,000 to +10,000ft)StorageTEMPERATURE-40 to +70°C (-40 to +158°F)RELATIVE HUMIDITY5 to 95% (noncondensing)ALTITUDE-300 to +12,000m (-1,000 to +40,000ft) ContaminationSuitable for use in Class G3 (Harsh) environments as defined in ISA Standard S71.04, based on exposure testing according to EIA Standard 364-65, Class III. Vibration7.5 m/S2 (0.75 g) from 5 to 500 Hz(3)The environmental limits of this module may be enhanced by the type of enclosure containing the module. Refer to the applicableProduct Specification Sheet (PSS) which describes the specific type of enclosure that is to be used.PSS 21H-2Z14 B4Page 7 PHYSICAL SPECIFICATIONSMountingMODULEFBM214 mounts on a modular baseplate. Thebaseplate can be mounted on a DIN rail(horizontally or vertically), or horizontally on a19-inch rack using a mounting kit. Refer toPSS21H-2W6B4 for details.TERMINATION ASSEMBLYThe TA mounts on a DIN rail and accommodates multiple DIN rail styles including 32mm (1.26in) and 35mm 1.38in).MassMODULE284 g (10 oz) approximateTERMINATION ASSEMBLYCompression181 g (0.40 lb) approximateRing Lug249 g (0.55 lb) approximateDimensions – ModuleHEIGHT102 mm (4 in)114 mm (4.5 in) including mounting lugsWIDTH45 mm (1.75 in)DEPTH104 mm (4.11 in)Dimensions – Termination AssemblySee page10.Part NumbersFBM214 MODULEP0922VTTERMINATION ASSEMBLIESSee “FUNCTIONAL SPECIFICATIONS –TERMINATION ASSEMBLIES” on page8. Termination CablesCABLE LENGTHSUp to 30 m (98 ft)CABLE MATERIALSPolyurethane or Hypalon®/XLPTERMINATION CABLE TYPEType 1 – See Table2 on page9.CABLE CONNECTION – TA25-pin male D-subminiatureConstruction – Termination AssemblyMATERIALPolyvinyl Chloride (PVC), compressionPolyamide (PA), compressionPVC, ring lugFAMILY GROUP COLORGreen – communicationTERMINAL BLOCKS3 tiers, 8 positionsField Termination ConnectionsCOMPRESSION-TYPE ACCEPTED WIRINGSIZESSolid/Stranded/AWG0.2 to 4 mm2/0.2 to 2.5 mm2/24 to 12 AWGStranded with Ferrules0.2 to 2.5 mm2 with or without plastic collarRING-LUG TYPE ACCEPTED WIRING SIZES#6 size connectors (0.375 in (9.5 mm))0.5 to 4 mm2/22 AWG to 12 AWGPSS 21H-2Z14 B4Page 8TERMINATION ASSEMBLIES AND CABLESField input signals connect to the FBM subsystem via DIN rail mounted Termination Assemblies, which are electrically passive.TAs for the FBM214 are available in the following forms: Compression screw type using Polyvinyl Chloride(PVC) materialCompression screw type using Polyamide (PA) material Ring lug type using PVC material.See the following “FUNCTIONAL SPECIFICATIONS –TERMINATION ASSEMBLIES” for a list of TAs used with the FBM214.The FBM214 provides sufficient loop resistance to allow use of the HART Hand-Held Terminal, or PC20 Intelligent Field Device Configurator (PSS 2A-1Z3 E).A removable termination cable connects the DIN railmounted TA to the FBM via a field connector on the baseplate in which the FBM is installed. Termination cables are available in the following materials: PolyurethaneHypalon XLP .Termination cables are available in a variety of lengths, up to 30 meters (98feet), allowing the Termination Assembly to be mounted in either theenclosure or in an adjacent enclosure. See Table 2 for a list of termination cables used with the TAs forthe FBM214.FUNCTIONAL SPECIFICATIONS – TERMINATION ASSEMBLIESFBM Type Input SignalTA Part NumberTermination TA Cable TACertification PVC (a)(a)PVC is polyvinyl chloride rated from -20 to +50°C (-4 to +122°F).PA is Polyamide rated from -20 to +70°C (-4 to +158°F).PA (a)Type (b)(b) C = TA with compression terminals; RL = TA with ring lug terminals.Type (c)(c)See Table 2 for cable part numbers and specifications.Type (d)(d)See Table 1 for Termination Assembly certification definitions.FBM2148 input channels, 4 to 20mA analog signal, alone or with HART signal superimposedP0916BX P0926EA P0926TD CRL11, 2PSS 21H-2Z14 B4Page 9Table 1. Certification for Termination AssembliesType Certification (a)(a)All TAs are UL/UL-C listed to comply with applicable ordinary location safety standards for fire and shock hazards. Hazardous locationtypes comply with ATEX directive for II 3 G use. They also comply with the requirements of the European Low Voltage Directive. All listings/certifications require installation and use within the constraints specified in DIN Rail Mounted Subsystem User’s Guide (B0400FA) and the conditions stated in UL and DEMKO reports.Type 1TAs are UL/UL-C listed as suitable for use in Class I; Groups A-D; Division 2 temperature code T4 hazardous locations. They are CENELEC (DEMKO) certified EEx nA IIC T4 for use in Zone 2 potentially explosive atmospheres.Type 2TAs are UL/UL-C listed as associated apparatus for supplying non-incendive field circuits Class I; Groups A-D; Division 2 hazardous locations when connected to specified DIN rail mounted FBMs and field circuits meeting entity parameter constraints specified in DIN Rail Mounted Subsystem User’s Guide (B0400FA). They are also CENELEC (DEMKO) certified as associated apparatus for supplying field circuits for Group IIC, Zone 2 potentially explosive atmospheres. Field circuits are also Class 2 limited energy (60 V dc, 30 V ac, 100 VA or less) if customer-supplied equipment meets Class 2 limits.Table 2. Cables Types and Part NumbersCable Lengthm (ft) Type 1P/PVC (a)Type 1H/XLPE (b)Cable Lengthm (ft) Type 1P/PVC (a)Type 1H/XLPE (b)0.5 (1.6)P0916DA P0916VA 10.0 (32.8) P0916DE P0916VE 1.0 (3.2) P0916DB P0916VB 15.0 (49.2) P0916DF P0916VF 2.0 (6.6)P0931RM P0931RR 20.0 (65.6) P0916DG P0916VG 3.0 (9.8) P0916DC P0916VC 25.0 (82.0) P0916DH P0916VH 5.0 (16.4)P0916DDP0916VD30.0 (98.4)P0916DJP0916VJ(a)P/PVC is polyurethane outer jacket and semi-rigid PVC primary conductor insulation.(b)H/XLPE is Hypalon outer jacket and XLPE (cross-linked polyethylene) primary conductor insulation.PSS 21H-2Z14 B4Page 10DIMENSIONS – NOMINALRELATED PRODUCT SPECIFICATION SHEETSCompression Termination AssemblyRing Lug Termination Assembly(a) Overall width – for determining DIN rail loading.(b) Height above DIN rail (add to DIN rail height for total).PSS NumberDescriptionPSS 21H-2W1 B3DIN Rail Mounted FBM Subsystem OverviewPSS 21H-2W2 B3DIN Rail Mounted FBM Equipment, Agency CertificationsPSS 21H-2Z14 B4Page 11PSS 21H-2Z14 B4 Page 12IPS Corporate Headquarters 5601 Granite Parkway Suite 1000 Plano, TX 75024United States of AmericaFoxboro Global Client Support Inside U.S.: 1-866-746-6477 Outside U.S.: 1-508-549-2424 or contact your local Foxboro representative.Facsimile: 1-508-549-4999Invensys, Foxboro, I/A Series and the IPS Logo are trademarks of Invensys plc, its subsidiaries, and affiliates. All other brand names may be trademarks of their respective owners.Copyright 2002-2010 Invensys Systems, Inc.All rights reservedMB 21A Printed in U.S.A. 0210。

IOTA DLS-55产品规格说明书