毕业设计FPGA的低频数字相位设计论文

FPGA频率计设计毕业设计(论文)

一、课程设计原理1、测频原理及误差分析本次课程设计采用直接测频法。

直接测频法就是在确定的闸门时间内,记录被测信号的脉冲个数。

这种方法的计数值也会产生最大为±1个脉冲误差。

进一步分析测量准确度。

设待测信号脉冲周期为T1,频率为F1,当闸门时间为T=1s 时,测量准确度为&=T1/T=1/F1。

由此可知直接测频法的测量准确度与信号的频率有关。

当待测信号频率较高时,测量准确度也较高,反之测量准确度也较低。

2、占空比测量原理占空比:占空比是指高电平在一个周期之内所占的时间比率。

方波的占空比为50%,占空比为0.5,说明正电平所占时间为0.5个周期。

在1S的闸门时间之内,只要我们利用50Mhz的时钟脉冲,对待测信号的高电平时间进行计数,得到一个num值。

最后num*20ns就是所求信号的占空比了。

二、系统的设计1、分频模块分频模块我们采用50Mhz的时钟频率产生待测的信号,和三个控制信号。

此程序要求将50Mhz分出1Mhz的频率,再产生1hz作为控制信号的标准输入时钟。

该模块产生的3个控制信号,分别为EN,LOAD,CLR。

CLR信号用于在每次测量开始时,对计数器进行复位,以清除上次测量的结果,该复位信号高电平有效。

EN为计数允许信号,在EN信号的上升沿时刻计数模块开始对输入信号的频率进行测量,在此1S时间里被测信号的脉冲数进行计数,即为信号的频率。

然后将值锁存,并送到数码管显示出来。

设置锁存器的好处是使显示的数据稳定,不会由于周期性的清零信号而不断闪烁。

在每一次测量开始时,都必须重新对计数器清0。

另外,也设计出另外一个进程process,产生同样地三个控制信号给占空比测量时提供使能,锁存和清零的能力。

部分程序如下:process(clk)beginif clk'event and clk = '1' thentemp1<=temp1+1;end if;end process;freq<=temp1(16); --381Hz=50Mhz/2^172、计数模块计数模块分为2个子模块。

基于fpga的频率计设计与实现本科毕设论文

唐山学院毕业设计设计题目:基于FPGA的数字频率计设计与实现系别:信息工程系班级:10应用电子技术(1)班*名:******师:***2013年6月10 日基于FPGA的数字频率计设计与实现摘要在电子设计领域,随着计算机技术、大规模集成电路技术、EDA(Electronics Design Automation)技术的发展和可编程逻辑器件的广泛应用,传统的自下而上的数字电路设计方法、工具、器件已远远落后于当今技术的发展。

基于EDA技术和硬件描述语言的自上而下的设计技术正在承担起越来越多的数字系统设计任务。

本课题的数字频率计设计,采用自上向下的设计方法。

本文首先综述了EDA 技术的概况,接着介绍硬件描述语言VHDL,可编程器件FPGA及频率测量的一般原理;然后介绍数字频率计的系统设计,频率计各系统模块的VHDL语言实现,最后利用QUARTUS Ⅱ集成开发环境进行编辑、综合、波形仿真,并下载到CPLD器件中,经实际电路测试,仿真和实验结果表明,此频率计具有较高的实用性和可靠性。

关键字:EDA FPGA 数字频率计VHDL语言Design and Implementation ofDigital Frequency Meter Based on FPGAAbstractIn the field of electronic design, with the development of computer technology, LSI technology, EDA (Electronics Design Automation)technology and wide application of programmable logic devices, the traditional bottom-up digital circuit design methods, tools, devices have far behind today's technology. The top-down design techniques based on EDA technology and hardware description language are taking on more and more digital system design task.The topic digital frequency meter design uses top-down design approach. First, this paper summarizes the overview of EDA technology, then it describes the hardware description language which is called VHDL, FPGA programmable device and the general principles of frequency measurement; then it introduces the system design of digital frequency meter, and the realization of frequency meter each system module VHDL. Finally using QUARTUSⅡ integrated development environment edits, synthesizes, and simulates, and download to the CPLD devices, by using the actual circuit testing, simulation and experimental results show that this frequency meter is high availability and reliability.Keywords:EDA; FPGA;digital frequency meter;VHDL language目录1 引言 (1)2 硬件描述语言(HDL) (2)2.1VHDL语言简介 (2)2.2 利用VHDL语言开发的优缺点 (3)3 电子设计自动化(EDA)发展概述 (4)3.1 EDA的简介 (4)3.2 EDA的发展史 (4)3.3基于EDA的FPGA/CPLD开发 (5)3.3.1 FPGA/CPLD的简介 (6)3.3.2 用FPGA/CPLD进行开发的优缺点 (7)4 频率计的测量及方案选择 (9)4.1 数字频率计工作原理概述 (9)4.2 测频原理及误差分析 (10)4.2.1常用测频方案 (10)4.2.2 等精度测频原理 (10)4.2.3误差分析 (11)5 数字频率计的系统设计与功能仿真 (13)5.1 系统的总体设计 (13)5.2 频率计模块 (14)5.2.1 测频控制模块 (14)5.2.2 锁存器模块 (15)5.2.3 十进制计数器模块 (16)5.3 显示模块 (17)5.3.1显示模块设计 (17)5.3.2译码器模块 (18)5.3.3四位二进制数与十六位二进制数转换的源程序 (19)5.3.4十六位二进制数与四位二进制数转换的源程序 (19)5.3.5四位二进制数与段码转换的源程序 (21)6 整形电路设计 (22)6.1 555定时器的工作原理 (22)6.2 施密特触发器 (23)6.2.1 电路结构 (23)6.2.2 工作原理 (23)6.3波形的整形 (24)7 软件测试及硬件下载 (25)7.1 QuartusII软件简介 (25)7.2 QuartusII的设计流程 (25)7.3 QuartusII软件的使用方法 (26)7.3.1 创建底层模块 (26)7.3.2 构建顶层模块 (30)7.4 下载及硬件实现 (32)8 结论 (34)谢辞 (35)参考文献 (36)附录Ⅰ频率计顶层文件 (38)附录Ⅱ源程序 (39)1引言21世纪人类将全面进入信息化社会,对微电子信息技术和微电子VLSI基础技术将不断提出更高的发展要求,微电子技术仍将继续是21世纪若干年代中最为重要的和最有活力的高科技领域之一。

基于FPGA数字频率计的设计(毕设1)

摘要近年来,随着科学技术的迅猛发展,人们生活水平以及物质水平的逐步提高,对电子产品的要求也越来越高,各行各业的竞争也逐渐激烈。

其中FPGA技术也取得了很大的成就!FPGA是现场可编程门阵列的简称,FPGA 的应用领域最初为通信领域,但目前,随着信息产业和微电子技术的发展,可编程逻辑嵌入式系统设计技术已经成为信息产业最热门的技术之一,应用范围遍及航空航天、医疗、通讯、网络通讯、安防、广播、汽车电子、工业、消费类市场、测量测试等多个热门领域。

并随着工艺的进步和技术的发展,向更多、更广泛的应用领域扩展。

越来越多的设计也开始以ASIC转向FPGA,FPGA正以各种电子产品的形式进入了我们日常生活的各个角落。

在学习一门技术之前我们往往从它的编程语言开始,如同学习单片机一样,我们从C语言开始入门,当掌握了C语言之后,开发单片机应用程序也就不是什么难事了。

学习FPGA也是如此,FPGA的编程语言有两种:VHDL 和Verilog。

作为在校大学生,我们现在学习了VHDL语言,通过两年的学习,我们掌握了VHDL各方面的技术要点,已能熟练运用到编程中去,其运用起来也很方便,能灵活实现各种电路功能。

此外还锻炼了我们良好的逻辑思维,因此在做FPGA数字频率的设计必须对VHDL语言有良好的掌握。

本文针对FPGA数字频率计的功能要求,从硬、软件两个方面对其阐述,重点对其软、硬件进行开发设计。

关键词:集成电路编辑语言特定功能目录摘要 (I)目录............................................................................................................................ I I 第一章绪论.. (4)1.1研究课题的背景 (4)1.2相关开发技术 (4)第二章对FPGA数字频率计的制作规划 (8)2.1问题引入 (8)2.2设计目的 (8)2.3设计要求 (8)2.4所需仪器仪表 (8)2.5设计内容、方法与步骤 (8)第三章 FPGA数字频率计的设计分析 (11)2.1设计要求 (11)2.2模块及模块的功能 (11)第四章 FPGA多周期同步测频原理 (18)4.1多周期同步测频法原理 (18)4.2设计实现 (19)4.3FPGA程序设计 (20)4.1DSP程序设计 (21)第五章基于FPGA的同步测周期高精度数字频率计的设计 (22)5.1同步测周期频率计的原理 (22)5.2数字频率计的VHDL实现 (22)5.3频率计的仿真验证 (23)第六章总结 (24)致谢 (25)参考文献 (26)第一章绪论1.1 研究课题的背景在许多领域中广泛应用的嵌入式计算系统(简称为嵌入式系统),是在更大的电子器件中嵌入的重复完成特定功能的计算系统,它经常不被器件的使用者所识别,但在各种常用的电子器件中能够找到这些嵌入式系统。

学位论文—基于fpga的数字频率计的设计论文

基于FPGA 的数字频率计的设计2004级电子信息工程专业 何亚军 指导教师 曾技摘要 随着数字电子技术的发展,频率测量成为一项越来越普遍的工作,在电子工程、资源勘探等相关应用上,频率计是工程技术人员必不可少的测量工具。

因此,测频原理及方法的研究正受到越来越多的关注。

目前许多高精度的数字频率计都采用单片机加上外部的高速计数器来实现。

但难以提高计数器的工作频率,而且测量的精度不高。

因此采用可编程逻辑器件(FPGA)来实现数字频率计。

应用VHDL 进行自顶向下的设计,即使用VHDL 模型在所有综合级别上对硬件设计进行说明、建模和仿真测试。

通过逻辑综合后,把适配生成的配置文件,通过编程器向FPGA\CPLD 进行下载。

最后进行硬件调试与验证。

本设计的系统除了脉冲整形、显示部分的电路不在可编程电路之中,其余的电路都集成在可编程逻辑器件中。

本设计具有测频范围宽、精度高、可靠性高等优点。

符合现代EDA 设计的要求。

关键词 频率,可编程逻辑器件,电子设计自动化,硬件描述语言1 绪论在电子技术领域内,频率与电压一样,也是一个基本参数。

随着现代科技的发展,时间及频率计量的意义已日益明显。

例如,在卫星发射、导弹跟踪、飞机导航、潜艇定位、大地测量、天文观测、邮电通信、广播电视、交通运输、科学研究、生产及生活等各个方面,都需要对时间及频率的计量,也都离不开对时间及频率的计量。

因此,测频原理及方法的研究正受到越来越多的关注。

目前多用电子计数器测频,它具有测量精度高、速度快、自动化程度高、操作简便、直接显示数字等特点,尤其是与微处理器相结合,实现了程控化和智能化,构成智能化计数器。

目前,电子计数器几乎取代了模拟式测量仪器。

而电子计数器测频法又有两种实现方法:直接计数测频法和等精度测频法。

直接计数测频法只是简单地记下单位时间内周期信号的重复次数,其计数值会有1±个计数误差。

此方法的测量精度主要取决于基准时间和计数器的计数误差。

低频数字式相位测量仪电子信息工程等专业毕业设计毕业论文[管理资料]

![低频数字式相位测量仪电子信息工程等专业毕业设计毕业论文[管理资料]](https://img.taocdn.com/s3/m/a56031d9647d27284a7351df.png)

摘要频率、相位测量仪器在生产和科研的各个部门被广泛应用。

,对测量精度的要求也越来越高。

针对传统的测频法和测周法测量精度不高的缺陷,,以AT89C51单片机为控制器件的新型频率测量方法:等精度测量方法。

利用同步门控制单片机的双计数器进行“相关计数”,应用单片机的数学运算和控制功能,实现了高低频率等精度测量,克服了通用频率计由于±1MSB误差在高低频段测量精度不等的缺陷,既满足测量精度的要求,又满足系统反应时间的要求。

用此方法实现的频率计具有高精度、低成本、易改进的特点,具有一定的实用性。

本文主要介绍了其系统构成和工作原理,以及系统的软硬件设计。

本论文基于相位数字化原理,针对传统的数字式相位计采用的脉冲填充计数法测量精度不高,误差大的缺陷,利用单片机与外部电路相结合,采用高频脉冲填充计数,多周期等精度测量的方法实现了相位差的高精度测量,着重介绍系统原理及软硬件实现方法。

关键词:单片机;等精度;误差;测相仪;相位差;计数器abstractFrequency and phase measurements in production and research equipment widely used in all sectors. Achieve digital measurements. Automation. Intelligent applications has become necessary now to the measurement accuracy requirements are increasingly high. In traditional law and geodetic survey frequency measurement accuracy is not high Week law wrong on a theory based on the number of frequencies to AT89C51 Danpianji control devices for the new frequency measurement methods : such precision measurements. Use Chanpianji double rod "relevant calculations", the application Danpianji the arithmetic and control functions, such as achieving a high frequency precision measurements overcome +1MSB overall frequency of errors in the measurement of low frequency bands ranging from precision errors to meet the measurement accuracy requirements and system response time meet the requirements. The frequency of use of this method to achieve a high-precision, low-cost, easy to improve features, a certain relevance. This article introduces the principles of its composition and working systems, as well as system software and hardware design.This paper based on the principles of 13,800 digitized against traditional digital phase of a pulse recharge count law is not high precision measurements, error big mistakes, and the use of external circuits Chanpianji combined using HF pulse recharge number, such as multi-cycle approach to achieve precision measurements of the high-precision measurement of transmitters, highlight the principles and system software and hardware to achieve.Keywords:Chanpian; such precision; Error; Testing of devices; Pairs; Counter目录绪论 (1)第一章系统工作原理 (3)1.1频率测量原理 (3)1.2相位测量原理 (4)第二章系统总体设计思路及方案分析 (5)2.1测频 (5)2.1.1 脉冲数倍频测频法 (5)2.1.2 脉冲数分频测频法 (5)2.1.3 测频-测周结合法 (5)2.1.4 多周期等精度测量方法 (6)2.2测相 (8)2.2.1 脉冲填充计数测相法 (8)2.2.2 多周期等精度测相法 (8)第三章系统硬件设计电路 (11)3.1测频电路设计 (11)3.1.1 信号放大整形电路 (11)3.1.2 外部分频电路 (13)3.1.3 同步门逻辑控制电路 (14)3.1.4 与单片机接口显示电路 (15)3.1.5 扩展报警电路 (16)3.2测相电路设计 (18)3.2.1 前级放大整形电路 (18)3.2.2 相位差测量电路 (20)3.2.3 相位极性判别电路 (21)第四章系统软件设计 (22)4.1主要任务 (22)4.2系统流程设计 (22)4.3总体流程图 (23)结论与分析 (24)致谢 (25)参考文献 (26)附录 (27)绪论随着无线电技术的发展与普及,“频率”已成为广大群众所熟悉的物理量调节收音机上的频率刻度盘可使你选听到你喜欢的电台节目;调节电视机上的微调旋钮可使得电视机对准电视台的广播频率,获得图象清晰的收看效果,这些已成为人们的生活常识。

基于FPGA与单片机控制技术结合的低频数字相位测量仪设计

设计(论文)题目:基于FPGA与单片机控制技术结合的低频数字相位测量仪设计一、基本任务及要求一)基本任务1)硬件设计:输入信号整形电路、单片机外围电路、显示电路;2)软件设计:数据采集模块的VHDL硬件描述语言实现、单片机控制程序。

二)要求1)本设计本分为三大基本组成部分:数据采集电路、数据运算控制电路和数据显示电路。

其功能为对两路输入正弦信号(1~5 V范围内变化)进行频率和相位测量(相位测量绝对误差≤2)及数字显示(相位读数为0~359.9,分辨力为0.1),其频率测量范围:20 Hz~20 kHz。

2)通过该项目设计,完成各单元模块的硬件设计,给出其设计过程和电路图;对数据采集、单片机控制模块分别给出VHDL硬件描述语言实现的源程序和控制程序,并进行程序调试及电路的仿真、给出仿真结果。

二、进度安排及完成时间:目录摘要 (IV)Abstract (V)第1章绪论.......................................................... - 1 -1.1 课题研究的背景................................................ - 1 -1.2 本课题的主要研究工作.......................................... - 3 - 第2章主要理论及技术................................................ - 4 -2.1 频率测量...................................................... - 4 -2.2 相位测量...................................................... - 5 -2.3 单门限电压比较器原理.......................................... - 6 -2.3.1 LM339介绍............................................... - 6 -2.4 FPGA可编程控制技术............................................ - 7 -2.4.1 FPGA 器件的设计开发流程.................................. - 7 -2.4.2 FPGA工作原理............................................ - 8 -2.4.3 VHDL语言介绍........................................... - 8 -2.4.4 Quartus II软件介绍...................................... - 9 -2.5 AT80C51单片机介绍............................................ - 10 - 第3章系统设计思路................................................. - 11 -3.1 系统总体设计思路............................................. - 11 -3.2 设计方案..................................................... - 11 - 第4章硬件设计...................................................... - 13 -4.1 信号整形电路的设计........................................... - 13 -4.2 FPGA数据采集电路的设计....................................... - 14 -4.3 单片机数据运算控制电路的设计................................. - 15 -4.4 数据显示电路的设计........................................... - 16 -4.4.1 LCD12864介绍........................................... - 16 -4.4.2 基本特性................................................ - 16 -4.4.3管脚说明................................................ - 16 -4.4.4 基本用途................................................ - 17 -4.4.5数据显示电路............................................ - 17 - 第5章软件设计...................................................... - 18 -5.1 FPGA数据测量电路............................................. - 18 -5.2 分频器模块................................................... - 19 -5.3 控制信号模块................................................. - 20 -5.4 数据检测模块................................................. - 22 -5.5 数据锁存模块................................................. - 23 -5.6 数据选择模块................................................. - 24 -5.7 FPGA数据测量模块总体设计..................................... - 26 -5.7 单片机数据运算控制电路....................................... - 27 - 结束语............................................................... - 30 - 参考文献............................................................. - 31 - 致谢............................................................... - 32 - 附录............................................................... - 33 - FPGA数据采集程序................................................. - 33 - 数据显示程序..................................................... - 36 - 硬件总电路图..................................................... - 40 -低频数字式相位测量仪的设计摘要:基于过零检测法原理,以单片机89C51和可编程逻辑器件CPLD为核心,从数据采集﹑数据运算控制、显示等电路功能电路设计,实现了一个低频数字式相位测量仪系统。

fpga毕业论文

fpga毕业论文FPGA技术在计算机和电子领域中得到越来越广泛的应用。

本文主要介绍了FPGA在数字信号处理中的应用。

文章首先介绍了FPGA的基本原理和结构,然后详细阐述了FPGA在数字信号处理中的应用,包括数字滤波器、均衡器、FFT等。

最后,文章对FPGA在数字信号处理中的应用进行了总结和展望。

一、FPGA概述FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,其硬件结构由可编程逻辑单元(LUT)、寄存器和互连资源组成,可以进行不同电路结构的编程和再编程。

FPGA 拥有很多优点,例如高度的可定制性、可重构性、高速性、大规模集成度、低功耗和低成本等,因此在数字电子、通信、图像处理、网络交换机、音视频处理、科学计算等领域中得到广泛应用。

二、FPGA在数字信号处理中的应用数字信号处理(Digital Signal Processing,DSP)是数字电子学的一个重要领域,用于处理数字信号。

FPGA在数字信号处理中的应用包括数字滤波器、均衡器、FFT、数字信号合成器、数字调制解调等,下面分别进行详细介绍。

(一)数字滤波器数字滤波器是一种数字信号处理器件,用于对数字信号进行滤波处理,滤除或增强特定频率的信号。

数字滤波器可以基于FPGA硬件平台进行设计和实现。

常见的数字滤波器包括低通滤波器、高通滤波器、带通滤波器和带阻滤波器等。

FPGA 实现数字滤波器具有高速处理、低延迟、低功耗、高精度和灵活性等优点。

(二)均衡器均衡器是用于抵消信号失真的一种电路装置,主要用于数字通信和音频处理。

FPGA可以实现各种类型的均衡器,如时域均衡器、频域均衡器、自适应均衡器等。

这些均衡器主要用于信道均衡、接收机均衡和发射机预失真等领域,能够提高系统的信号质量和稳定性。

(三)FFTFFT(Fast Fourier Transform,快速傅里叶变换)是一种数字信号处理算法,用于将时间域信号转换为频域信号。

毕业设计论文《低频数字式相位测量仪》

毕业设计论文《低频数字式相位测量仪》摘要该数字式相位测量仪以单片机 (89c52) 为核心 , 通过高速计数器 CD4040 为计数器计算脉冲个数从 , 而达到计算相位的要求 , 通过 8279 驱动数码管显示正弦波的频率,不采用一般的模拟的振动器产生 , 而是采用单片机产生 , 从而实现了产生到显示的数字化 . 具有产生的频率精确 , 稳定的特点 . 相移部分采用一般的 RC 移相电路 , 节省了成本。

一方案论证与比较 :1 常见正弦信号的测量方法 :方案一:采用模拟分离元件如二极管,三极管等非线性元件,实现频率的测量,检相的功能,使用起来方便,价格便宜,但采用分离元件由于分散性太大,不便于集成及数字化,而且测量误差大。

方案二:采用集成的检相器,检频器实现频率及相位的测量。

这种方法的实现框图如下:这种方法虽然可实现比较精确的测量,但由于模拟信号易受外界的干扰,不易调节,无法实现智能化,数字化的缺点,一般在要求较低的情况下使用。

方案三:此方案采用高速信号发生器产生 20MHz 的高频信号,其主要特点是采用 CD4040 高频计数器结合单片机,利用计数脉冲实现测量相位与频率的目标。

这种方法克服了模拟电路的缺点,实现了数字化与集成化。

本设计采用了这种方法。

这种方案的组成框图:二系统总体设计按照题目要求,我们设计的相位测量系统包括三部分:正弦波产生系统(包括频率调整电路),移相电路和相位显视系统,其总体框图如下:三各部分硬件电路设计及参数计算1、正弦波产生电路•方案一:利用 8038 芯片或 MAX038 可以实现压控的函数发生器通过改变少量的外围元件,可实现正弦波,方波,三角波,并可实现频率调节,但采用模拟器件由于元件分散性太大,即使使用单片函数发生器,参数也与外部元件有关,外接的电阻,电容对参数影响很大,因而产生的频率稳定度差,精度低,抗干扰能力差,调节困难,成本也高。

而且灵活性差,不能实现智能化。

低频数字相位测量仪毕业设计毕业论文及文献综述[管理资料]

![低频数字相位测量仪毕业设计毕业论文及文献综述[管理资料]](https://img.taocdn.com/s3/m/d060522076a20029bc642dd6.png)

摘要本文设计的是低频数字相位测量仪的软件控制部分。

在设计中采用MCU与FPGA 相结合的方案,将软件部分系统分为控制数据采集处理和单片机控制显示两部分的软件设计,本部分分软件设计充分发挥单片机控制运算能力强的特点来对其各个模块进行软件编程。

数据的采集利用FPGA去完成,可以准确地采集到两个同频正弦信号的相位差所对应的时间差以及信号的周期,从而更好地提高系统的可靠性。

再根据单片机具有较强的运算、控制能力的特点,我们通过对单片机最小系统来进行编程以之完成读取FPGA的数据,并根据所读取的数据计算待测信号的频率及两路同频信号之间的相位差。

同时通过软件编程来实现功能键的切换,由显示模块显示待测信号的频率和相位差。

关键字:数据采集; 单片机; 频率; 相位差;ABSTRACTThis paper is designed to phase low-frequency digital measuring instrument. this design which uses the combination of The MCU and FPGA will be divided the hardware into two parts of data acquisition processing and MCU minimum system ,it give full use to the features of MCU-controlled computing for power , the FPGA data acquisition for high speed and resource-rich . we use the FPGA to complete collection of the data, so we can accurately collect the phrase difference between the two-phase sinusoidal signal ,corresponding to the time difference and the cycle of signal, so as to greatly improve the reliability of the system. Then according to characteristics of the shrapnel-strong operation and the ability to control, we use the minimum system of MCU to complete the reading of data FPGA, then according to the data read calculate the frequency of signals under test and the phase difference between the two-way same frequency signal. At the same time, through the switching of function keys ,the frequency and phase of signals under test Will be showed by moduleKeyword:Data; Acquisition; SCM; Frequency; phase目录绪论 (1)相位测量原理 (2)输入与采集 (2)频率的测量 (2)相位差对应的时间差的测量 (3)2 设计要求与设计方案 (4)设计要求 (4)设计方案 (4)设计思路 (4)各模块的作用 (4)设计方案 (4)3 整机电路原理 (6)MCU控制FPGA电路 (6)MCU控制显示电路 (7)整机电路原理 (8)4 软件设计 (10)MCU控制FPGA的软件设计 (10)MCU控制FPGA电路框图 (10)软件设计思路 (11)MCU控制FPGA各程序流程图 (11)MCU控制显示的软件设计 (13)显示软件设计 (13)单片机控制显示程序流程图 (14)5 程序设计 (15)单片机的源程序 (15)结论 (27)致谢 (28)参考文献 (29)绪论随着科学技术的突飞猛进的发展,电子技术广泛的应用于工业、农业、交通运输、航空航天、国防建设、科研、生产等国民经济的诸多领域中,而电子测量技术又是电子技术中进行信息检测的重要手段,在现代科学技术中占有举足轻重的作用和地位。

毕业设计(论文)--基于fpga的数字频率计设计

前

在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。数字式频率计的测量原理有两类:一是直接测频法,即在一定闸门时间内测量被测信号的脉冲个数;二是间接测频法即测周期法,如周期测频法。直接测频法适用于高频信号的频率测量,通常采用计数器、数据锁存器及控制电路实现,并通过改变计数器阀门的时间长短在达到不同的测量精度;间接测频法适用于低频信号的频率测量,本设计中使用的就是直接测频法,即用计数器在计算1S内输入信号周期的个数。

数字频率计基本原理是用计数器来计算1S内输入信号周期的个数。如图2.3所示是4位十进制数字频率计的系统方框原理图,当系统正常工作时,脉冲发生器提供的1 Hz的输入信号,经过测频控制信号发生器进行信号的变换,产生计数信号,被测信号通过信号整形电路产生同频率的矩形波,送入计数模块,计数模块对输入的矩形波进行计数,将计数结果送入锁存器中,保证系统可以稳定显示数据,显示译码驱动电路将二进制表示的计数结果转换成相应的能够在七段数码显示管上可以显示的十进制结果[10]。

2

方案一: 采用小规模数字集成电路制作

被测信号经过放大整形变换为脉冲信号后加到主控门的输入端,时基信号经控制电路产生闸门信号送至主控门,只有在闸门信号采样期间内输入信号才通过主控门,若时基信号周期为T,进入计数器的输入脉冲数为N,则被信号的测频率其频率F=N/T,其原理方框图如图2.1所示[7]。

待测信号

我的毕业设计——基于FPGA的双路低频信号发生器

我的毕业设计——基于FPGA的双路低频信号发生

器

摘要

本设计是基于Altera公司的Cyclone II系列EP2C8Q208C8N芯片的双路低频信号发生器。

系统应用FPGA内部特有的可配置IP核和锁相环等设计信号发生器。

整个系统由触摸屏人机操控界面、红外操控、信号发生器、叠加电路组成。

信号发生器可输出两路相互独立的信号,信号类型有矩形波、三角波以及正弦波。

两路信号的频率、幅值、相位、占空比等参数都可通过红外遥控以及触摸屏调节和预置。

频率的预置范围为1000赫兹到2000赫兹,步进值为1赫兹。

幅值的预置范围为0V~5V,相位的预置范围为0°~360°,占空比预置范围为0~100%,且步进值都小于1。

当两路波形都为正弦信号时,可以通过叠加电路对两路正弦信号进行叠加。

系统结构框

本设计是以Altera公司的可编程芯片做载体,运用Verilog作为软件设计工具,从而实现DDS原理,即信号发生器的核心思想。

再加上信号发生器的硬件电路就可以输出特定的信号,也就是本设计中的数/模转换电路。

从电池兼容EMC考虑,该电路的布局要紧凑的硬件,使导线长度尽可能短。

这样即

可以避免内部自身线路时间的干扰,也可以避免外界的干扰,适当增加滤波器来屏蔽干扰。

这样就可以提高输出信号的质量。

所有信号的参数可以通过两种方式程控调节,即人机操控方式和红外遥控方式。

从图中可以看出系统。

基于FPGA控制的低频数字式相位测量仪研究

法 两 种 : 统 依 靠 模 拟 器 件 的 方 法 , 二 极 传 如 管 鉴 相法 、脉 冲计 数 法 等 , 量 系统 复 杂 、 测 需专 用 器件 、硬 件 成本 高 、而 且精 度不 高 。 随 着 集 成 电 路 的 发 展 , 用 大 规 模 集 成 电 利

本 系 统 充 分 利 用 FPGA 对 数 据 的 高 速 处 理 能 力 , 使 得 系 统 设 计 高 效 , 可 靠 。 与 传 统 相 位 测 量 仪 相 比 , 系 统 具 有 处 理 速 度 快 、稳 该 定 性 高 、 性 价 比 高 , 易 于 实现 的优 点 。该 系统 具 有 较 强 的 实 用 价 值 和 良好 的 工 程 应 用 前 景 。 [ 键 词 ] 杂 可 编 程 逻 辑 器 件 低 频 相 位 测 量 仪 F 关 复 PGA VH DL 语 言 [ 图分类号1 2 中 x5 【 献标 识 码 】 文 A [ 章 编 号 l0 7 4 6 ( 0 0 0 - 0 6 4 文 10 -9 l 2 l ) 1 0 7 -0

视 频 字 符叠 加 的 一 种较 好 的 选 考 文献 ]

【 】 应 用 电 视 一一设 备 原 理 与 工 程 实 践 1 Ⅸ 京 : 子 工 业 出 版 社 》 中 国 广 播 电 视 设 北 电 备 工 业 协 会 应 用 电 视 专 业协 会 . [】Ga mi NC. GP 2 / 0 tc n cl 2 r nI S 5 2 e h ia

・

应 用研 究 ・

基于 F G P A控 制 的低 频数 字 式 相位 测量 仪研 究

王 振 红 于 磊

( 方 工 业 大 学 信 息 工 程 学 院 北 京 1 0 4 ) 北 0 1 4

毕业设计(论文)-基于FPGA的数字频率计的设计

摘要在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得十分重要。

数字频率计是数字电路中的典型应用,是电子测量与仪表技术最基础的电子仪器之一,是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器。

与传统的频率计相比,数字频率计具有精度高、测量范围大、可靠性好等优点。

是频率测量的重要手段之一。

该论文研究基于FPGA的数字频率计的设计,在QuartusII环境中,运用VHDL语言完成数字频率计的设计,并对设计进行综合、编译、仿真。

通过仿真分析,证明该频率计测量结果的正确性。

本文的主要介绍了数字频率计的基本内容和重要性,并对数字频率计的国内外研究现状进行了总结;数字频率计设计开发环境,并对FPGA、QuartusII、VHDL进行了详细介绍对开发流程详细说明;根据实际需要对数字频率计设计方法、方案进行了可行性比较,并对其实现的功能进行了具体要求,对设计模块进行了划分,并定义了每个模块所实现的功能;用VHDL语言编程,具体实现频率计各个模块的功能, 对数字频率计仿真并验证其功能。

关键词: FPGA;QuartusII;VHDL;频率计AbstractIn electronics,frequency is one of the most basic parameters.And it have a close relationship with many measurement program of electrical parameters and measurement results, so the measurement of frequency is very important.Digital frequency meter is a typical applications in digital circuit,and one of the most basic electronic devices in electronic measurement and instrumentation technology.Digital frequency meter is an indispensable measuring instruments for scientific research and production as computers, communications equipment, audio, video. Compared with the conventional frequency counter,digital frequency meter have a high accuracy, measurement range and a good reliability. It is one of important measure for frequency measurement:The thesis research in design of digital frequency meter,FPGA-based. VHDL language is used to complete the design of digital frequency meter in QuartusII,and completed thesis with composited, compiled, simulated. Through simulation and analysis, The results show that the accuracy of measure for the frequency. This article mainly introduces the importance and basic content of digital frequency meter, and current research is summarized .the main tasks and content of this design are summarized.Design and development environment of digital frequency meter are introduced.FPGA, QuartusII and VHDL are described in detail.According to the actual needs of the digital frequency meter, design method and design program are compared to achieve the functions of their specific requirements, and defines the functions of each module to achieve the function.Keywords : FPGA,QuartusII ,VHDL,digital frequency met目录摘要 (I)Abstract (II)第1章绪论 (1)1.1 课题背景与意义 (1)1.2 课题目的 (1)1.3 技术指标 (1)第2章FPGA开发相关知识简介 (3)2.1 FPGA的介绍 (3)2.2 FPGA开发环境 (4)软件开发环境——Quartus II的介绍 (4)软件仿真环境——Modelsim的介绍 (5)2.3 硬件描述语言——Verilog HDL (6)2.4 FPGA开发流程 (8)本章小结 (11)第3章频率计的设计方案 (12)3.1 系统的总体设计 (12)3.1.1 设计思路 (12)频率计的基本原理 (12)3.2 数字频率计原理方框图 (13)本章小结 (13)第4章频率计的实现 (14)4.1 时钟信号分频模块的设计 (14)4.2 测频控制信号发生模块的设计 (15)4.3 十进制计数模块的设计 (16)4.4 八位十进制计数模块的设计 (18)4.5 三十二位锁存器模块的设计 (20)4.6 顶层模块的设计 (20)本章小结 (23)结论 (24)致谢 (25)参考文献 (26)附录1 译文 (27)附录2 英文参考资料 (30)第1章绪论1.1 课题背景与意义在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,频率的测量就显得尤为重要,而频率计的研究工作更具有重大的科研意义。

基于FPGA的FIR数字低通滤波器的设计毕业设计论文

毕业设计(论文)题目(中文):基于FPGA的FIR数字低通滤波器的设计(英文):The Design of FIR Digital Filter Based on FPGA上海师范大学天华学院本科毕业设计(论文)诚信声明本人郑重声明:所呈交的毕业设计(论文),题目《基于FPGA 的FIR数字低通滤波器的设计》是本人在指导教师的指导下,进行研究工作所取得的成果。

对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式注明。

除此之外,本设计(论文)不包含任何其他个人或集体已经发表或撰写过的作品成果。

本人完全意识到本声明应承担的法律责任。

作者(签名):日期:2012年04月27日毕业设计(论文)任务书(2012届)题目(中文):基于FPGA的FIR数字低通滤波器的设计(英文):The Design of FIR Digital Filter Based on FPGA系部电子与信息工程系专业班级电子信息工程08秋1班日期: 2011 年 10 月毕业设计(论文)原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。

尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。

对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。

作者签名:日期:指导教师签名:日期:使用授权说明本人完全了解大学关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分或全部内容。

作者签名:日期:学位论文原创性声明本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。

单片机和FPGA相结合的低频数字相位设计论文

1引言本设计采用单片机和FPGA相结合的电路实现方案。

考虑到FPGA具有集成度高,I/O 资源丰富,稳定可靠,可现场在线编程等优点,而单片机具有很好的人机接口和运算控制功能,所以采用FPGA和单片机相结合,构成整个系统的测控主体。

自1985年Xilinx公司推出第一片现场可编程逻辑阵列(FPGA)至今,FPGA已经成为当今电子设计应用市场上首选的可编程逻辑器件之一。

从航空航天到数字信号处理,再到汽车家电等消费领域,无处不见FPGA的身影。

而且,随着微电子等工艺的进步,FPGA器件本身的性能逐年在提高,使得FPGA器件与其他同类器件相比更有竞争力。

在这个各类电子设计器件百花齐放的时代,广大消费者需要对这些电子设计器件有个更深入地了解,从而为自己的科研学习或工业生产挑选到既能满足各项性能指标要求,又经济实惠的合适的电子设计器件。

因此,进行FPGA器件的应用研究并进行各类电子设计产品的性能优势对比分析是一项很有价值和实际意义的工作。

随着EDA技术的高速发展,电子系统的设计技术和工具发生了深刻的变化,大规模可编程逻辑器件FPGA的出现,给设计人员带来了诸多方便。

利用它进行产品开发,不仅成本低、周期短、可靠性高,而且可以随时在系统中修改其逻辑功能。

FPGA器件的成本越来越低,Actel公司发布第三代的基于Flash的可编程逻辑方案。

这些新的FPGA芯片最低价将达到1.5美元,代表了全球最低成本的FPGA,并且相对于基于SRAM的FPGA来说具有保密的优势。

基于Flash的FPGA可以提供加密、低功耗、上电工作、可重复编程的方案。

目前生产FPGA的公司主要有Xilinx、Altera、Actel、Lattice、QuickLogic等,生产的FPGA品种和型号繁多。

尽管这些FPGA的具体结构和性能指标各有特色,但它们都有一个共同之处,即由逻辑功能块排成阵列,并由可编程的互连资源连接这些逻辑功能块,从而实现不同的设计。

基于FPGA控制的低频数字式相位测量仪研究(胡云朋

基于FPGA控制的低频数字式相位测量仪研究胡云朋(电子信息工程学院微电子及固体电子专业 113114310)摘要:提出了一种基于Verilog开发的低频数字相位测量仪设计。

系统以FPGA为核心,构成完备的测量系统,可以对20Hz-20KHz的频率范围的信号进行频率、相位等参数的精确测量。

硬件结构简单,程序简单可读性强,与传统电路相比,具有处理速度快、稳定性高、性价比高的特点。

关键字:相位测量仪、FPGA、Verilog语言目录第一章研究背景 (3)第二章方案设计与论证 (3)一、设计指标要求 (3)二、设计方案论证 (4)第三章系统硬件设计 (6)硬件电路的设计: (6)第四章软件系统设计 (7)一、FPGA完成的任务 (7)二、FPGA芯片内部电路框图 (7)三、FPGA的Verilog程序及仿真结果 (7)第五章结束语 (11)参考文献: (11)第一章 研究背景随着科学技术的突飞猛进的发展,电子技术广泛的应用于工业、农业、交通运输、航空航天、国防建设等国民经济的诸多领域中,而电子测量技术又是电子技术中进行信息检测的重要手段,在现代科学技术中占有举足轻重的作用和地位。

相位是交流信号的重要参数。

相位差的测量是电子和电力测量中经常遇到的问题,测量两路同频信号的相位差在工程上有着重要的意义。

其测量方法可分为模拟和数字方法两种:传统依靠模拟器件的方法,如二极管鉴相法、脉冲计数法等,测量系统复杂、需专用器件、硬件成本高、而且精度不高。

随着集成电路的发展,利用大规模集成电路来完成各种高速、高精度电子仪器的设计,已经成为一种行之有效的方法。

采用这种技术制成的电子仪器电路结构简单、性能可靠、测量精确且易于调试,而且精度明显高于一般的模拟式测量。

在工业和民用场合, 为了对各种低频信号进行测量分析,常常引入相位测量仪。

低频数字式相位测试仪在工业领域中是经常用到的一般测量工具,例如在电力系统中,当电网合闸时,要求两电网电信号的相位相同,如果两路信号的相位不同,会出现很大的电网冲激电流,对供电系统产生巨大的破坏力,因此,精确测量出两个信号的相位差是非常重要的。

低频数字式相位测量仪 vhdl fpga

低频数字式相位测量仪栏目树形导航| 首页 | 学习中心 | 课设与竞赛 | 下载中心 | 图片现场 | 技术留言 | 关于我们 | 本站提供 ||竞赛与设计首页|关于竞赛|历届电子竞赛题目|竞赛作品选编|历届仪器元器件范围|单片机课程设计|您现在的位置:奔跑的单片机 >> 课设与竞赛 >> 竞赛作品选编 >> 信息正文用户登录新用户注册低频数字式相位测量仪热【字体:小大】低频数字式相位测量仪作者:lintel 信息来源:本站原创点击数:8523 更新时间:2006-4-3低频数字式相位测量仪(C题)摘要:设计了一基于现场可编程门阵列(FPGA)的低频数字式相位测量仪。

该测量仪包括数字式移相信号发生器和相位测量仪两部分,分别完成移相信号的发生及其频率、相位差的预置及数字显示、发生信号的移相以及移相后信号相位差和频率的测量与显示几个功能。

其中数字式移相信号发生器可以产生预置频率的正弦信号,也可产生预置相位差的两路同频正弦信号,并能显示预置频率或相位差值;相位测量仪能测量移相信号的频率、相位差的测量和显示。

两个部分均采用基于FPGA的数字技术实现,使得该系统具有抗干扰能力强, 可靠性好等优点。

关键词:现场可编程门阵列(FPGA)数字式相位测量仪Abstrct:The paper deals with designing of a low frequency phasemeasurement system based on FPGA technology. This phase measurement system includes two modules---a signal generator and a phase measurementsubsystem. Its signal generator module can generate a sin wave withpreconcerted frequency and two waves with preconcerted phase difference. It can continuously change signal phases through phase shifting. And its phase measurement subsystem has functions of measuring signal phase andphase difference of two signals. All of its three modules adopt digitaltechnology base on FPGA. This system is characteristic of its strongantijamming performance and fine stability.Key words:FPGA/Digital/Phase measurement system目录0 引言 (3)1 系统设计1.1设计要求 (3)1.2 方案比较 (4)1.2.1相位测量仪方案 (4)1.2.2移相网络方案 (4)1.2.3正弦波信号发生器方案 (5)1.2.4频率测量方案 (5)1.2.5幅度控制方案 (6)1.2.6滤波选择方案 (6)1.2.7显示界面方案 (7)1.3方案论证 (7)1.3.1总体思路 (7)1.3.2设计方案 (7)2单元电路设计2.1相位测量仪 (7)2.1.1原理方框图 (7)2.1.2相位测量原理 (8)2.1.4电路图分析………………………………………………………………………………2.2数字式移相信号发生器 (10)2.2.1 数字移相原理 (10)2.2.2正弦波信号发生 (10)3 软件设计3.1用VHDL编写程序…………………………………………………………………………123.2 程序流程 (12)3.2.1 等精度频率测量的实现 (12)3.3程序清单仿真 (13)4 系统测试……………………………………………………………………………………145 结论…………………………………………………………………………………………17参考文献……………………………………………………………………………………17 附录 (17)0.引言同频率正弦信号间的相位差测量在电工技术、工业自动化、智能控制及通讯、电子等许多领域都有着广泛的应用,如电工领域中的电机功角测试,介质材料损耗角的确定等。

基于FPGA的低频数字相位测量仪的设计

1引言关于低频数字相位测量系统的设计与实现方法,提出了以单片机最小系统和复杂可编程逻辑芯片为核心的电路设计模型。

相位的数字测量方法基本分为硬件电路测量与A/D采样后利用软件计算两种。

硬件法测量由于电路结构比较复杂,易受外界干扰影响以及准确度较差的缺点,限制了其作用进一步发挥。

近年来,随着计算机硬件及其外围设备的日益发展,以数字信号处理为核心的软件法测量技术在相位差的测量中得到了越来越多关注,并且得到了较快发展。

同频率正弦信号间的相位差测量在电工技术、工业自动化、智能控制及通讯、电子等许多领域都有广泛的应用,如电工领域中的电机功角测试,介质材料的损耗角的确定等。

因此相位差测量有着广泛的实用价值。

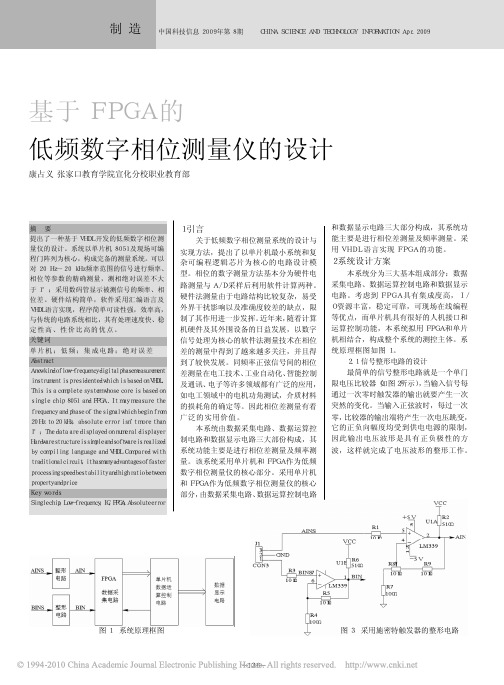

本系统由数据采集电路、数据运算控制电路和数据显示电路三大部份构成,其系统功能主要是进行相位差测量及频率测量。

该系统采用单片机和FPGA作为低频数字相位测量仪的核心部分。

采用单片机和FPGA作为低频数字相位测量仪的核心部分,由数据采集电路、数据运算控制电路基于FPGA的低频数字相位测量仪的设计康占义 张家口教育学院宣化分校职业教育部图1 系统原理框图图3 采用施密特触发器的整形电路和数据显示电路三大部分构成,其系统功能主要是进行相位差测量及频率测量。

采用VHDL语言实现FPGA的功能。

2系统设计方案本系统分为三大基本组成部分:数据采集电路、数据运算控制电路和数据显示电路。

考虑到FPGA具有集成度高,I/O资源丰富,稳定可靠,可现场在线编程等优点,而单片机具有很好的人机接口和运算控制功能,本系统拟用FPGA和单片机相结合,构成整个系统的测控主体。

系统原理框图如图1。

2.1 信号整形电路的设计最简单的信号整形电路就是一个单门限电压比较器(如图2所示),当输入信号每通过一次零时触发器的输出就要产生一次突然的变化。

当输入正弦波时,每过一次零,比较器的输出端将产生一次电压跳变,它的正负向幅度均受到供电电源的限制,因此输出电压波形是具有正负极性的方波,这样就完成了电压波形的整形工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

毕业设计FPGA的低频数字相位设计论文1引言本设计采用单片机和FPGA相结合的电路实现方案。

考虑到FPGA具有集成度高,I/O 资源丰富,稳定可靠,可现场在线编程等优点,而单片机具有很好的人机接口和运算控制功能,所以采用FPGA和单片机相结合,构成整个系统的测控主体。

自1985年Xilinx公司推出第一片现场可编程逻辑阵列(FPGA)至今,FPGA已经成为当今电子设计应用市场上首选的可编程逻辑器件之一。

从航空航天到数字信号处理,再到汽车家电等消费领域,无处不见FPGA的身影。

而且,随着微电子等工艺的进步,FPGA 器件本身的性能逐年在提高,使得FPGA器件与其他同类器件相比更有竞争力。

在这个各类电子设计器件百花齐放的时代,广大消费者需要对这些电子设计器件有个更深入地了解,从而为自己的科研学习或工业生产挑选到既能满足各项性能指标要求,又经济实惠的合适的电子设计器件。

因此,进行FPGA器件的应用研究并进行各类电子设计产品的性能优势对比分析是一项很有价值和实际意义的工作。

随着EDA技术的高速发展,电子系统的设计技术和工具发生了深刻的变化,大规模可编程逻辑器件FPGA的出现,给设计人员带来了诸多方便。

利用它进行产品开发,不仅成本低、周期短、可靠性高,而且可以随时在系统中修改其逻辑功能。

FPGA器件的成本越来越低,Actel公司发布第三代的基于Flash的可编程逻辑方案。

这些新的FPGA 芯片最低价将达到1.5美元,代表了全球最低成本的FPGA,并且相对于基于SRAM的FPGA 来说具有保密的优势。

基于Flash的FPGA可以提供加密、低功耗、上电工作、可重复编程的方案。

目前生产FPGA的公司主要有Xilinx、Altera、Actel、Lattice、QuickLogic等,生产的FPGA品种和型号繁多。

尽管这些FPGA的具体结构和性能指标各有特色,但它们都有一个共同之处,即由逻辑功能块排成阵列,并由可编程的互连资源连接这些逻辑功能块,从而实现不同的设计。

典型的FPGA通常包含三类基本资源:可编程逻辑功能块、可编程输入/输出块和可编程互连资源。

可编程逻辑功能块是实现用户功能的基本单元,多个逻辑功能块通常规则地排成一个阵列结构,分布于整个芯片;可编程输入/输出块完成芯片内部逻辑与外部管脚之间的接口,围绕在逻辑单元阵列四周;可编程内部互连资源包括各种长度的连线线段和一些可编程连接开关,它们将各个可编程逻辑块或输入/输出块连接起来,构成特定功能的电路。

用户可以通过编程决定每个单元的功能以及它们的互连关系,从而实现所需的逻辑功能。

不同厂家或不同型号的FPGA,在可编程逻辑块的内部结构、规模、内部互连的结构等方面经常存在较大的差异。

除了上述构成FPGA基本结构的三种资源以外,随着工艺的进步和应用系统需求的发展,一般在FPGA中还可能包含以下可选资源:存储器资源(块RAM、分布式RAM);数字时钟管理单元(分频/倍频、数字延迟、时钟锁定);算数运算单元(高速硬件乘法器、乘加器);多电平标准兼容的I/O接口;高速串行I/O接口;特殊功能模块(以太网MAC等硬IP核);微处理器(PowerPC405等硬处理器IP核)。

下面介绍两种FPGA的一般结构。

第一种包括5个可配置部分:(1)可配置逻辑块,用于实现大部分逻辑功能;(2)在可配置逻辑块的四周分布着可编程的输入输出块(Input/Output Blocks),提供封装引脚与内部逻辑之间的连接接口;(3)丰富的多层互连结构的可编程连线;(4)片上的随机存取块状RAM;(5)全数字式延迟锁相环(DLL)时钟控制块,与每个全局时钟输入缓冲器相连,该闭环系统确保时钟边沿到达内部触发器与其到达输入引脚同步,有效地消除时钟分配的延迟。

另一种FPGA器件主要包括:(1)逻辑阵列,由多个逻辑阵列块(Logic Array Blocks)排列而成,用于实现大部分逻辑功能;(2)在芯片四周分布着可编程的输入输出单元(Input/Output Elements),提供封装引脚与内部逻辑之间的连接接口;(3)丰富的多层互连结构的可编程连线;(4)片上的随机存取块状RAM;(5)锁相环(PLL),用于时钟的锁定与同步、能够实现时钟的倍频和分频;(6)高速的硬件乘法器,有助于实现高性能的DSP功能。

目前绝大部分FPGA都采用查找表技术,最基本逻辑单元都是由LUT和触发器组成的。

查找表简称为LUT,本质上就是一个RAM。

目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1的RAM。

当用户通过原理图或VHDL语言描述了一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM。

这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出该地址对应的内容,然后输出即可。

由于LUT主要适合SRAM工艺生产,所以目前大部分FPGA都是基于SRAM工艺的。

而SRAM工艺的芯片在掉电后信息就会丢失,因此需要外加一片专用的配置芯片。

在上电的时候,由这个专用配置芯片把数据加载到FPGA中,FPGA 就可以正常工作。

少数FPGA产品采用反熔丝或Flash工艺,掉电后配置信息不会丢失,因此这种FPGA芯片不需要外加的专用配置芯片。

单片机集成度高、功耗低、速度快、价格便宜、实用灵活、开发周期短。

自从20世纪80年代单片机首次推出以来,一经上市便显示出强大的生命力,以其独特的优点迅速占领市场并获得了广泛使用,并且很快在全世界得到广泛的推广与应用。

一直到现在,单片机技术正日臻完善,国内外的单片机热更是经久不衰,对于电子信息产业的发展更具有“倍增器”的作用。

因此新型单片机已成为21世纪极具发展潜力和影响力的一项电子科技产品。

目前,单片机正朝着兼容性、单片系统化、多功能和低功耗的方向发展。

单片机与单片系统、智能传感器、网络通信等高新技术的融合必将成为21世纪新的经济增长点。

随着微电子技术和计算机技术的迅速发展,单片机升级换代的速度在不断加快,涉及新型单片机原理、接口技术、外围电路设计及应用技术的知识也在不断更新。

该设计中系统实现的增益程控放大功能和增益程控衰减功能主要是通过单片机、单片机外围电路、接口技术以及一些单片机原理来完成的,单片机成了整个电路中的“中心枢纽”,在功能键的控制下,单片机来完成对各个模块的控制。

在整个过程中,单片机完成信号的接受、处理、传出,在人为的操作下,控制着整个电路的工作状态。

随着电子技术的高速发展,现在的电子系统逐渐实现了智能化、人性化、最优化,并且富有了系统性、社会性。

除了能够满足系统功能和性能指标要求外,还具有很多优点:如电路简单、电磁兼容性好、可靠性高、系统集成度高、调试简单方便、操作简便、性能价格比高。

从系统的角度看,电子系统是能按特定的控制信号,执行所设想的功能,由一组元器件(通常电子器件)连成的一个整体。

从单级放大器到最复杂的计算机等很多设备都可以称为一个电子系统。

可以从很多元器件集成为一个功能单元,再用若干个功能单元去描述一个系统。

一般来说,电子系统分为模拟型、数字型及两者兼而有之的混合型三种,无论哪一种电子系统,他们都是能够完成某种任务的电子设备。

通常把规模较小、功能单一的电子系统称为单元电路,实际应用中的电子系统由若干单元电路组成。

一般的电子系统由输入、输出、信息处理三大部分组成,用来实现对信息的采集处理、变换与传输功能。

对于模拟电子系统,输入电路主要起到系统与信号源的阻抗匹配,信号的输入与输出连接方式的转换,信号的综合等作用,输出电路主要解决与负载或被控对象的匹配和输出足够大的功率去驱动负载的问题。

而对于数字电子系统,输入与输出电路主要解决与现场信号和控制对象的接口问题,输入电路往往由一些转换器或锁存器组成,而输出电路也由一些对应的转换器和驱动器组成。

在工业和民用场合,为了对各种低频信号进行测量分析,常常引入相位测量仪。

同频信号间相位差的测量在电力系统、工业自动化、智能控制及通信、电子、地球物理勘探等许多领域都有着广泛的应用。

尤其在工业领域中,相位不仅是衡量安全的重要依据,还可以为节约能源提供参考。

因此,研究和设计低频数字相位测量仪将会为国民经济的发展起到推动和促进作用。

2 概述2.1 FLEX10KK简介FLEX10K是工业界第一个嵌入式的可编程逻辑器件,采用可重构的CMOS SRAM工艺,把连续的快速通道互连与独特的嵌入式阵列结构相结合,同时也结合了众多可编程器件的优点来完成普通门阵列的宏功能。

FLEX10K的集成度已达到25万门。

它能让设计人员轻松地开发出集存储器、数字信号处理器及特殊逻辑(包括32位多总线系统)等强大功能于一身的芯片,已经推出了FLEX10K、FLEX10KA、FLEX10KV、FLEX10KE等分支系列。

其中EPF10K20是FLEX10K系列器件之一。

FLEX10K系列器件主要由嵌入式阵列块、逻辑阵列块、快速通道(FAST TRACK)互连和I/O单元四部分组成。

由于FPGA器件的基于SRAM结构,数据具有挥发性,所以每次上电使用时必须重新下载数据。

对FPGA数据下载可通过下载电缆、专用配置芯片或微处理器等方式完成。

在本设计中,采用配置芯片EPC1441来完成。

EPC1441配置芯片属于EPROM结构,而不具有可擦写性。

2.2 VHDL硬件描述语言2.2.1 VHDL语言的发展状况[1]VHDL的英文全名是Very-High-Speed Integrated Circuit Hardware Description Language,诞生于1982年。

1987年底,VHDL被IEEE(The Institute of Electrical and Electronics Engineers)和美国国防部却认为标准硬件描述语言。

自IEEE公布了VHDL的标准版本(IEEE-1076)之后,各EDA公司相继推出了自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL 接口。

此后VHDL在电子设计领域得到了广泛的接收,并逐步取代了原有的非标准硬件描述语言。

1933年,IEEE对VHDL进行论文修订,从更高的抽象层次和系统描述能力上扩展VHDL的内容,公布了新版本的VHDL,即IEEE标准的1076-1993版本。

现在,VHDL和Verilog语言作为IEEE的工业标准硬件描述语言,又得到众多EDA公司的支持,在电子工程领域,以成为事实上的通用硬件描述语言。

有专家认为,在新世纪中,VHDL语言将承担起几乎全部的数字系统设计任务。

2.2.2 VHDL的特点VHDL主要用于描述数字系统的结构、行为、功能和接口。

除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法十分类似于一般的计算机高级语言。