用74L161构成模14加法计数器(置数法)

大学课程《数字电子技术基础》试题及答案(三)

大学课程《数字电子技术基础》试题及答案一、填空题组合逻辑电路1. 数字电路按逻辑功能的不同特点可分为两大类,即: 逻辑电路和 逻辑电路 。

答:组合 、时序2. 从一组输入数据中选出一个作为数据传输的常用组合逻辑电路叫做 。

答:数据选择器3.用于比较两个数字大小的逻辑电路叫做 。

答:数值比较器4. 驱动共阳极七段数码管的译码器的输出电平为 有效,而驱动共阴极的输出电平为 有效。

答:低、高5.一个8选1的多路选择器(数据选择器),应具有 个地址输入端。

答:3个6.编码器的逻辑功能是把输入的高低电平编成一个 ,目前经常使用的编码器有普通编码器和优先编码器两类。

答:二值代码7.译码器的逻辑功能是把输入的二进制代码译成对应的 信号,常用的译码器有二进制译码器,二-十进制译码器和显示译码器三类。

答:输出高、低电平8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。

答:10111111二、选择题组合逻辑电路1.74LS138是3线-8线译码器,译码输出为低电平有效,若输入A 2A 1A 0=100时,输出= 。

A 、00010000,B 、11101111C 、11110111D 、10000000答:B2.在下列逻辑电路中,不是组合逻辑电路的是( )。

A 、译码器B 、编码器C 、全加器D 、寄存器 答:D3.在下列逻辑电路中,不是组合逻辑电路的是( )。

A. 译码器B. 编码器C. 全加器D.寄存器 答:D4. 八选一数据选择器组成电路如下图所示,该电路实现的逻辑函数是Y= 。

A. ABC ABC ABC ABC +++ B. ABC ABC + C. BC ABC +D. ABC ABC ABC ABC +++ 答:D5.七段显示译码器是指 的电路。

A. 将二进制代码转换成0~9数字B. 将BCD 码转换成七段显示字形信号C. 将0~9数字转换成BCD 码D. 将七段显示字形信号转换成BCD 码 答:B6.组合逻辑电路通常由 组合而成。

74 161 计数器

54161/741614位二进制同步计数器(异步清除)简要说明:161为可预置的4位二进制同步计数器,共有54/74161和54/74LS161两种线路结构型式,其主要电特性的典型值如下:型号 F MAX P DCT54161/CT74161 32MHz 305mWCT54LS161/CT74LS161 32MHz 93mW161的清除端是异步的。

当清除端CLEAR为低电平时,不管时钟端CLOCK状态如何,即可完成清除功能。

161的预置是同步的。

当置入控制器LOAD为低电平时,在CLOCK上升沿作用下,输出端QA-QD与数据输入端A-D相一致。

对于54/74161,当CLOCK由低至高跳变或跳变前,如果计数控制端ENP、ENT为高电平,则LOAD应避免由低至高电平的跳变,而54/74LS161无此种限制。

161的计数是同步的,靠CLOCK同时加在四个触发器上而实现的。

当ENP、ENT均为高电平时,在CLOCK上升沿作用下QA-QD同时变化,从而消除了异步计数器中出现的计数尖峰。

对于54/74161,只有当CLOCk为高电平时,ENP、ENT才允许由高至低电平的跳变,而54/74LS161的ENP、ENT跳变与CLOCK无关。

161有超前进位功能。

当计数溢出时,进位输出端(RCO)输出一个高电平脉冲,其宽度为QA的高电平部分。

在不外加门电路的情况下,可级联成N位同步计数器。

对于54/74LS161,在CLOCk出现前,即使ENP、ENT、CLEAR发生变化,电路的功能也不受影响。

管脚图:引出端符号:PCO 进位输出端CLOCK 时钟输入端(上升沿有效)CLEAR 异步清除输入端(低电平有效)ENP 计数控制端ENT 计数控制端ABCD 并行数据输入端LOAD 同步并行置入控制端(低电平有效)QA-QD 输出端功能表:说明:H-高电平L-低电平X-任意↑-低到高电平跳变极限值电源电压------------------------------------------------7V输入电压54/74161-----------------------------------------5.5V54/74LS161---------------------------------------7VENP与ENT间电压54/74161-----------------------------------------5.5V 工作环境温度54×××------------------------------ -55~125℃74×××------------------------------------0~70℃ 贮存温度-------------------------------------- -65~150℃推荐工作条件:CT54161/CT74161 CT54LS161/CT74LS161单位最小额定最大最小额定最大54 4.5 5 5.5 5.5V 电源电压Vcc74 4.75 5 5.25 4.75 5 5.25输入高电平电压V IH 2 2 V54 0.80.7V 输入低电平电压V IL74 0.80.8输出高电平电流I OH-800-400 μA54 16 4mA 输出低电平电流I OL74 16 8时钟频率f CP0 25 0 25 MHzCLOCK 25 25ns 脉冲宽度tWCLEAR 20 20A-D、ENP 20 20ns 建立时间t setLOAD 25 20保持时间t H0 0 ns 时序图:逻辑图静态特性(T A 为工作环境温度范围)`161 `LS161参数测试条件【1】最小最大最小最大单位I IK =-12mA -1.5V IK 输入钳位电压 Vcc 最小I IK =-18mA-1.5 V54 2.4 2.5V OH 输出高电平电压Vcc=最小,V IH =2V ,V IL =最大, I OH =最大74 2.42.7V54 0.4 0.4V OL 输出低电平电压 V CC =最小,V IH =2V ,V IL =最大,I OL =最大740.40.5VA -D,ENP,CLEAR1 0.1I I 最大输入电压时输入电流 LOAD,CLOCk,ENT Vcc=最大 V I =5.5V (‘LS161为7V )1 0.2 mAA -D,ENP,CLEAR40 20LOAD 40 40 I IH 输入高电平电流 CLOCK,ENT Vcc=最大 V IH =2.4V (‘LS161为2.7V )80 40 μA A -D,ENP,CLEAR-1.6-0.4 LOAD -1.6 -0.8 V IL 输入低电平电流CLOCK,ENTVcc=最大 V IL =0.4V-3.2-0.8 mA 54-20-57-20 -100I OS 输出短路电流 Vcc=最大74-18-57-20 -100mA54 85 31IccH 输出高电平时电源电流Vcc=最大,LOAD 先接高电平,再接低电平,其余输入接高电平 74 94 31 mA54 91 32IccL 输出低电平时电源电流Vcc=最大,CLOCK 先接高电平,再接低电平,其余输入接低电平74101 32mA【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

74ls161模16计数器工作原理

74ls161模16计数器工作原理

74LS161是一款常见的模16计数器,它可以实现二进制计数,并且在计数达到16时自动复位回0,以实现循环计数。

74LS161的工作原理如下:

1. 74LS161内部包含4个触发器(T型触发器),用于存储当

前计数的二进制值。

2. 计数器通过时钟输入引脚(CLK)来接收时钟脉冲。

3. 在每个时钟脉冲上升沿时,计数器开始进行计数。

4. 当计数值达到15时,触发器会将其输出为二进制数1111

(即15)。

5. 当下一个时钟脉冲到来时,触发器会将其输出复位为二进制数0000(即0),从而实现循环计数。

需要注意的是,74LS161还包含一个使能引脚(ENP),通过

使能引脚可以控制计数器的启停。

当使能引脚为高电平时,计数器开始计数;当使能引脚为低电平时,计数器停止计数,并且输出保持不变。

总结起来,74LS161模16计数器通过时钟脉冲来进行计数,

并且在达到指定值时自动复位回0,实现循环计数。

通过使能

引脚可以控制计数器的启停。

关于74LS161集成计数器的清零和置数

关于用74LS161集成计数器构成电子钟用74LS161做出十进制和六进制很简单,但在做小时的显示时就遇到了困难。

此处只讨论二十四进制的显示。

最初我们的方案是首先将161个位输出中的第0位和第3位取出送入与非门,即取出的是9,得到的结果再送回161的同步置数端,将此时161的输出1001的下一个输出变成0000,实现十进制。

当然前提是161的置数端全部都接地,即低电平。

同时将161个位的第0 位,第1位和时位的第1位接入与非门,即取出的是00100011,得到的结果送入161个位和时位的同步置数端,则二十三的下一个数是零。

但是实际结果却并非如此,因为两次置数产生了混淆,即第一次置数和第二次置数同时发生,而它们的结果不同,输出却接到相同的芯片的相同管脚,那么这个管脚的真正状态到底取决于什么呢,此处便产生了混淆。

二十四进制的显示必然是不正常的。

重新仔细的阅读了数电教材上对于161用法中异步清零和同步置数的讲解,突然想到可以利用置数和清零的区别来把小时个位的进位和个位、时位的清零区分开。

这源于置数和清零的区别:清零的信号是立即产生的,比如都对于十进制来说,若采用清零法,则应该利用9的二进制,1001的下一位1010来产生脉冲信号,将输出端的第一位和第三位通过与非门得到低电平将161清零,也就是说我们利用的真正状态是10的二进制。

而如果我们采用置数法,因为芯片的设计原因,在计数器进入9的二进制1001后,输出端并没有立即置数,而是保持该状态不变,直到下一个时钟脉冲的上升沿到来为止,这个1001是一个稳定的状态,我们利用它的第0位和第三位通过与非门得到低电平将161置位为0000,才能形成十进制,那么我们利用的真正状态是9的二进制,而不是10,这就是清零与置数的根本区别。

那么如果我们要做一个电子钟中的二十四进制应该采用哪种方法呢:答案是两种都采用。

首先前文中已经说明,利用两片161将二十四进制的个位与十位分开进行显示,用一个十进制和三进制来组成二十四进制的方法是行不通的。

用74L161构成模14加法计数器(置数法)

数电技术课程实践班级:12电本姓名:徐保霞学号:201292150118 指导教师:崔用明设计一个用74L161组成的14进加法计数器一、摘要:本设计主要是对四位二进制同步计数器74L161(异步清除)的同步预置控制端进行分析设计,使74LS161能克服触发器的工作速度的差异情况以及竞争冒险现象,实现了使同步预置信号能够持续足够长的时间,从而使74LS161能够从0000这一状态复位变为1101状态,成功得竞争结果,实现十四进制计数器的设计。

英文摘要:This design is mainly to four binary synchronous counter 74 L161 (asynchronous clearance) analyze the synchronous reset control end of the design, make a 74 ls161 can overcome the trigger the differences of working speed and competitive adventure phenomenon, has realized the synchronous preset signal can be sustained long enough, so that 74 ls161 can this state is reset to 0000 from 1101, a competition to succeed as a result, achieve 14 into the design of the system counter.关键词:计数器、同步预置二、设计要求1)熟练掌握加法计数器、74L161的基本概念。

2)实现14进加法计数器的设计3) 掌握并分析结果三、设计步骤1、电路组成框图(图1-1)图1-12、电路原理图(图1-2)图1-23、元器件选择74L161、与非门、数码管4、参数的设计计算设0000为预置数,则十四进制加法计数器的有效态为0000、0001、0010、0011、0100、0101、0110、0111、1000、1001、1010、1011、1100、1101(图1-3)图(1-3)将输入端的数据d3d2d1d0=0000设为预置数,在输入时钟脉冲CP上升沿的作用下,EP、ET、R D接高电平,当输出端Q l输出为低电平时接与非门,此时Q l 输出为高电平,与Q3 Q2 Q0再通过一个与非门,此时“0”接入L D,实现R D=1、L D=0,达到设计要求输出为预置数0000。

74ls161功能

74ls161功能

74LS161是一种四位二进制同步计数器,具有以下功能:

1. 递增计数:74LS161可以在时钟信号的驱动下完成二进制计数的递增。

当触发时钟信号时,计数器会将输出值加1,并将其显示在输出端口上。

2. 自动复位:计数器可以经过一定的计数周期后自动返回初始计数值。

通过连接复位信号到复位引脚,计数器可以在达到指定周期后自动复位到预定计数值,从而实现循环计数的功能。

3. 异步并行装载:计数器可以通过设置和存储加载值,以异步并行的方式将某个特定的初始值加载到计数器中。

这个初始值可以通过外部引脚或与其他逻辑电路相连的引脚传输,从而实现计数器的初始化。

4. 消隐功能:计数器内部具有输出控制门电路,可以根据特定的控制信号控制输出的使能情况。

当消隐使能信号有效时,计数器的输出将被禁用和消隐,从而可以达到隐藏输出的目的。

5. 异常检测:计数器内部具有检测器电路,可以检测并报告计数器的溢出和下溢情况。

当计数器的计数值超过最大值或低于最小值时,检测器将会触发异常信号,从而向其他逻辑电路报告异常情况。

总的来说,74LS161是一种功能强大的计数器,可以实现二进制数值的递增、循环计数、异步并行装载、消隐功能以及异常情况的检测和报告。

它在数字系统设计中起到重要的作用,广泛应用于计数、时序控制和状态机等领域。

74LS161异步置零法构成任意进制计数器的Multisim仿真

15 3 -

《 电子设计 工 程)0 1年 第 l 21 4期

2 异 步 置 零 法 M ut i 仿 真 方 案 设 计 ls im

21 异 步 置 零 法 的 状 态 图 及 仿 真 方 案 设 计 要 求 . 用 M hs 0版 本 以 构 成 1 u iml i 0进 制 计 数 器 为 例 ,说 明 Mu im 仿 真 方 案 设 计 。 hs i 异步置零法 1 0进 制 计 数 器 的 状 态 图 如 图 1 示 .其 中 所

sg a sa d t eo e l p o u p ts as T a s i n sae a d t e a fa y c r n u e e in sae a ay e . u n i l v ra f t u i l. r n i o t t n i d ly o s n h n n h o n g t me o o sr s tsg a y n lz d A b g i l Mu ii 1 h sm 0,t a lc r g rmo eo 4 S 6 o n e s k ,i p i td o t a d t ec re t n i ie . h smeh d h t o k t g e d f7 L 1 1c u tri mit e s on e u , n o r c i sgv n T i c i s a h o to s t e h u s o a ewo k n v fr so o n e sa ed f c l t ea ay e n e f d b l cr n cd v c s et s e q e t n t t r igwa e o f u t r i u t ob n z d a d v r i ye e t i e ie . l t i h t h m c y i l i e o

数字电子技术考试卷及答案 (5)

七、(本题12分)画出用74161的异步清零功能构成的80进制计数器的连线图。

八、(本题15分)用D触发器设计一个按自然态序进行计数的同步加法计数器。

要求当控制信号M=0时为5进制,M=1时为7进制(要求有设计过程)。

7《数字电子技术基础》期末考试A卷标准答案及评分标准8910北京航空航天大学2004-2005 学年第二学期期末《数字数字电子技术基础》考试A 卷班级______________学号_________姓名______________成绩_________2007年1月18日班号学号姓名成绩《数字电路》期末考试A卷注意事项:1、答案写在每个题目下面的空白处,如地方不够可写在上页背面对应位置;2、本卷共5页考卷纸,7道大题;((a)74LS85四、逻辑电路和各输入信号波形如图所示,画出各触发器Q 端的波形。

各触发器的初始状态为0。

(本题12分)五、由移位寄存器74LS194和3—8译码器组成的时序电路如图所示,分析该电路。

(1)画出74LS194的状态转换图;(2)说出Z 的输出序列。

(本题13分)CP CP六、已知某同步时序电路的状态转换图如图所示。

(1)作出该电路的状态转换表;(2)若用D触发器实现该电路时写出该电路的激励方程;(3)写出输出方程。

(本题15分)七、电路由74LS161和PROM组成。

(1)分析74LS161的计数长度;(2)写出W、X、Y、Z的函数表达式;(3)在CP作用下。

分析W、X、Y、Z端顺序输出的8421BCD码的状态(W为最高位,Z为最低位),说明电路的功能。

(本题16分)《数字电子技术基础》期末考试A卷标准答案及评分标准一、1、按照波形酌情给分。

北京航空航天大学2005-2006 学年第二学期期末《数字电子技术基础》考试A 卷班级______________学号_________姓名______________成绩_________2006年7月12日班号学号姓名成绩N图712Q Q Y(状态转换、设计过程和步骤对得10分,化简有误扣3-5分)七、MN=00时,是5进制,显示最大数字为4;MN=01时,是6进制。

《数字电子技术》实验指导书

数字电子技术实验指导书电气与电子工程学院实验一门电路逻辑功能及测试一、实验目的1. 熟悉门电路逻辑功能2. 熟悉数字电路实验仪及示波器使用方法二、实验仪器及材料1. 双踪示波器2. 器件74LS00 二输入端四与非门 2片74LS20 四输入端双与非门 1片74LS86 二输入端四异或门 1 片三、实验内容1.测试门电路逻辑功能(1).选用双四输入与非门74LS20一只,插入14P锁& 紧插座上按图1.1接线、输入端接K1-K16(电平开关输出插口),输出端接电平显示发光二极管(L1-L16任意一个)(2).将电平开关按表1.1置位,分别测输出电压及逻辑状态。

表 1.1输出输出1 2 4 5 Y 电压(V)H H H HL H H HL L H HL L L HL L L L2.异或门逻辑功能测试(1).选二输入四异或门电路74LS86,按图1.2接线,输入端1、2、4、5接电平开关,输出端A、B、Y接电平显示发光二极管。

(2).将电平开关按表1.2置位拨动,将输出结果填入表中。

表 1.2输入输出A B Y Y电压L L L LH L L LH H L LH H H LH H H HL H L H3、逻辑电路的逻辑关系(1).用74LS00、按图1.3,1.4接线,将输入输出逻辑关系分别填入表1.3、表1.4中,表1.3输入输出A B YL LL HH LH H表1.4输入输出A B Y ZL LL HH LH H(2).写出上面两个电路逻辑表达式。

五、实验报告1.按各步骤要求填表并画逻辑图。

2.回答问题:(1)怎样判断门电路逻辑功能是否正常?(2)与非门一个输入接连续脉冲,其余端什么状态时允许脉冲通过?什么状态时禁止脉冲通过?(3)异或门又称可控反相门,为什么?实验二组合逻辑电路(半加器、全加器)一、实验目的1.掌握组合逻辑电路的功能测试。

2.验证半加器和全加器的逻辑功能。

3.学会二进制数的运算规律。

数字电子技术基础-74LS161的学习

(二)组成任意进制计数器

• 1.反馈清零法

• (1)异步反馈清零法 (2)同步反馈清零法

2.反馈置数法

• (1)异步反馈置数法 (2)同步反馈置数法

(1)异步反馈清零法

• 例5-14 用集成计数器74X161和必要的门电路构成6进制计数器, 要求使用反馈清零法。

CR Q1n Q2 n Q1n • Q2 n

• 当M=0时的卡诺图 当M=1时的卡诺图

CR MQ2Q0 MQ3 CR MQ2Q0 MQ3

• 当M=0时的卡诺图 当M=1时的卡诺图 CR M(Q2 Q0 ) M(Q1 Q3) MQ2Q0 MQ1Q3

CR M(Q2 Q0 ) M(Q1 Q3) MQ2Q0 MQ1Q3

输出

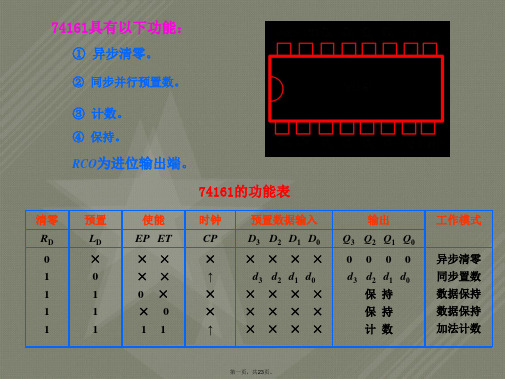

Q3 Q2 Q1 Q0 0000 D CB A

保持 保持 计数

工作模式

异步清零 同步置数 数据保持 数据保持 加法计数

(二)4位二进制同步加法计数器芯片 74X163

二、集成计数器的应用

• (一)计数器容量扩展 16*16=256进制

• 1.同步级联方式

2.异步级联方式

• (1)两片74X161异步 级联构成256进制计数 器

• 在0010 0100状态反馈清零。

用74X161组成60进制计数器。

• (1)清0法 74X161为异步清0。

• (60)D=(00111100)B • 状态从00000000到00111011变化。

用74X161组成60进制计数器。 • (2)置数法 74X161为同步置数。

• (59)D=(00111011)B • 状态从00000000到00111011变化。

方法十三:用同步反馈置数(置1010)方法实现,使用 RCO信号。

实验报告七

选预置数D3D2D1D0=0000;

写出D5-1的二进制数码:D4=0100;

再根据D4数码写出置数信号表达式: Q2 ; LD

最后根据置数信号表达式画出连线图。

例 用 74LS160的置数法构成七进制加法计数器

741LS60的有效状态是10个状态,在此选后七个状态为循环 计数状态即0011~1001。所以选预置数为:D3D2D1D0=1001 ; 74LS160是同步置数的,选

1) 异步清零:当 RD 0 时,不管其他输入端的状态如何, 不论有无时钟脉冲CP,计数器输出将被直接置零(Q3Q2QlQ0= 0000),称为异步清零。 2) 同步并行预置数:当 RD 1, LD 0 时,在输入时钟脉 冲CP上升沿的作用下,并行输入端的数据d3d2d1d0被置入计数 器的输出端,即Q3Q2QlQ0=d3d2d1d0。由于这个操作要与CP上 升沿同步,所以称为同步预置数。 3)计数功能:当 RD LD EP ET 1 时,在CP端输入 计数脉冲,计数器进行二进制加法计数。 4)保持功能:当 R D LD 1 ,且 EP ET 0 ,即两个 使能端中有0时,则计数器保持原来的状态不变。这时,如 EP=0、ET=1,则进位输出信号CO保持不变;如ET=0则不 管EP状态如何,进位输出信号CO为低电平0。

集成计数器产品多数是二进制和十进制计数器,如果需要其 他进制的计数器,可用现有的二进制或十进制计数器,利用 其清零端或预置数端,外加适当的门电路连接构成任意进制 计数器。如果手边有M进制的集成计数器,要构成N进制的计 数器,当M>N时用一片M进制的计数器就可以实现;当M<N时 则需要多片M进制的计数器下面分别介绍实现的方法。

LD CO ;

最后根据置数信号表达式画出连线图。

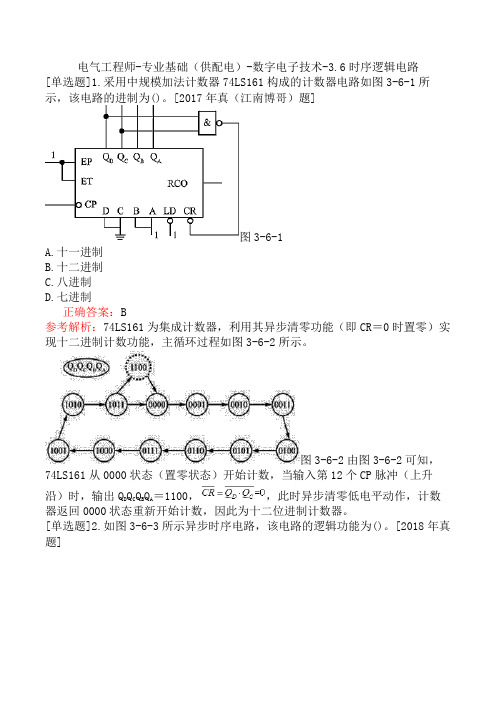

电气工程师-专业基础(供配电)-数字电子技术-3.6时序逻辑电路

电气工程师-专业基础(供配电)-数字电子技术-3.6时序逻辑电路[单选题]1.采用中规模加法计数器74LS161构成的计数器电路如图3-6-1所示,该电路的进制为()。

[2017年真(江南博哥)题]图3-6-1A.十一进制B.十二进制C.八进制D.七进制正确答案:B参考解析:74LS161为集成计数器,利用其异步清零功能(即CR=0时置零)实现十二进制计数功能,主循环过程如图3-6-2所示。

图3-6-2由图3-6-2可知,74LS161从0000状态(置零状态)开始计数,当输入第12个CP脉冲(上升沿)时,输出Q D Q C Q B Q A=1100,,此时异步清零低电平动作,计数器返回0000状态重新开始计数,因此为十二位进制计数器。

[单选题]2.如图3-6-3所示异步时序电路,该电路的逻辑功能为()。

[2018年真题]图3-6-3A.八进制加法计数器B.八进制减法计数器C.五进制加法计数器D.五进制减法计数器正确答案:C参考解析:JK触发器的特征方程为:可知:故可列真值表如表3-6-1。

由真值表可知,此电路完成了5种状态的循环转换,为五进制加法计数器。

表3-6-1[单选题]3.图3-6-4所示电路中,对于A、B、和D的波形,触发器FF0和FF1输出端Q0、Q1的波形是()。

[2018年真题]图3-6-4 A.B.C.D.正确答案:B参考解析:D触发器的特征方程为:Q n+1=D,则Q0np>=D,由A脉冲的上升沿触发。

JK触发器的特征方程为:则由B脉冲的下降沿触发,即为B项。

[单选题]4.图示3-6-5电路的逻辑功能为()。

[2014年真题]图3-6-5A.异步8进制计数器B.异步7进制计数器C.异步6进制计数器D.异步5进制计数器正确答案:D参考解析:解题步骤如下:①分析电路组成。

该电路是由三个下降沿触发的JK触发器组成的电路。

由于触发器1的时钟信号为触发器0的输出,故为异步时序逻辑电路。

数电作业-用74ls161设计同步加法计数器

H a r b i n I n s t i t u t e o f T e c h n o l o g y设计说明书(论文)课程名称:数字电子技术基础设计题目:同步加法计数器设计院系:航天学院自动化班级:0804101设计者:龚翔宇学号:24设计时间:【问题重述】试用同步加法计数器74LS161(或74LS160)和二4输入与非门74LS20构成百以内任意进制计数器,并采用LED数码管显示计数进制。

采用555定时器构成多谐振荡电路,为同步加法计数器提供时钟输入信号。

【设计思路】同步加法计数器74LS161为16进制计数器,要设计一个60进制的计数器,用555定时器设计多谐振荡电路,为同步加法计数器74LS161提供时钟输入信号并且用LED数码管显示结果。

要用16进制的161计时器设计60进制的,必须将其改装为10进制的。

将2个161联级,低位向高位进位6次,然后置零——即基本设计思路。

【基本元件】74LS161(两片)二4输入与非门74LS20(一片)555定时器【设计方案】555定时器提供时钟信号用555构成的多谐振荡器用555定时器构成的多谐振荡器如图所示。

555定时器可以方便的接成施密特触发器,在其基础上再改接成多谐振荡器。

o u可输出触发脉冲信号。

74LS161接为十进制计数器本方案使用置数法将161改装为十进制的计数器。

用如图所示。

D C B A Q Q Q Q 在经过1000时置数控制端LD =0,74LS161处在置数状态,D C B AQ Q Q Q 重新回到1111, 跳过了中间6个状态,由16进制转换为十进制计数器。

RCO 仍为进位输出。

对于低位芯片,全以0态作为起始状态,经过10-1=9状态后,产生置数控制信号1001。

这样,当第10个时钟的上升沿到达时,计数器置数为0000,每个芯片跳过剩余状态,成为10进制的计数器。

对于高位芯片,以取全0态作为起始状态,经过6个状态后,计数器清零,每个芯片跳过剩余状态,成为6进制的计数器。

数电作业-用74ls161设计同步加法计数器

Harbin I nstituteof Technology设计说明书(论文)课程名称:数字电子技术基础设计题目:同步加法计数器设计________ 院系:航天学院自动化_______班级:0804101 ______________设计者:龚翔宇_________________学号: 1080410124 ___________设计时间:2010.11 ____________【问题重述】试用同步加法计数器74LS161 (或74LS160)和二4输入与非门74LS20构成百以内任意进制计数器,并采用LED数码管显示计数进制。

采用555定时器构成多谐振荡电路,为同步加法计数器提供时钟输入信号。

【设计思路】同步加法计数器74LS161为16进制计数器,要设计一个60进制的计数器,用555定时器设计多谐振荡电路,为同步加法计数器74LS161提供时钟输入信号并且用LED数码管显示结果。

要用16进制的161计时器设计60进制的,必须将其改装为10进制的。

将2个161联级,低位向高位进位6次,然后置零一一即基本设计思路。

【基本元件】1. 74LS161 (两片)2. 二4输入与非门74LS20 (一片)3. 555定时器【设计方案】555定时器提供时钟信号4 8555二二Cs用555构成的多谐振荡器用555定时器构成的多谐振荡器如图所示。

555定时器可以方便的接成施密特触发器,在其基础上再改接成多谐振荡器。

U。

可输出触发脉冲信号。

74LS161接为十进制计数器本方案使用置数法将161改装为十进制的计数器。

用如图所示。

Q D Q C Q B Q A在经过1000时置数控制端LD =0,74LS161处在置数状态,Q D Q C Q B Q A重新回到1111,跳过了中间6个状态,由16进制转换为十进制计数器。

RCO仍为进位输出。

对于低位芯片,全以0态作为起始状态,经过10-仁9状态后,产生置数控制信号1001。

74LS161

图2 集成计数器的级联 (2)用反馈清零法获得任意进制计数器 由于集成计数器一般都设置有清零端和置数端,而且无论是 清零还是置数都有同步和异步之分。例如,4 位二进制同步加法计 数器74LS163的清零和置数均采用同步方式,而有的只有异步清 零功能。获得任意进 制计数器的方法很多,本书只介绍用反馈清 零法获得任意进制计数器。 如用74LS16l构成九进制加法计数器,九进制计数器(N=9) 有9个状态,而74LS161在计数过程中有16个状态(M=[6), 正常循环从0000到1111,要构成九进制加法计数器,此时必须设 法 跳过M-N(16 - 9=7)个状态。74LS161具有异步清零功能, 在其计数过程当中,不管它的输出处于哪 一状态,只要在异步清 零输人端加一低电平电压,使CR=0,74LS161的输出会立即从 那个状态回到0000状 态。清零信号(CR=0)消失后,74LS161 又从0000状态开始重新计数。 如图3(a)所示的九进制计数器,就是借助74LS161的异步 清零功能实现的。如图3(b)所示电路是九进 制计数器的主循环 状态图。

பைடு நூலகம்

计数器的种类很多,按其进制不同分为二进制计数器、十 进制计数器、N进制计数器;按触发器翻转是否 同步分为 异步计数器和同步计数器;按计数时是增还是减分为加法 计数器、减法计数器和加/减法(可逆 )计数器。下面首 先介绍二进制计数器。 1.集成二进制计数器74LS161 74LS161是4位二进制同步加法计数器,除了有二进 制加法计数功能外,还具有异步清零、同步并行置数 、 保持等功能。74LS161的逻辑电路图和引脚排列图如图1 所示,CR是异步清零端,LD是预置数控制端,D0 ,D1, D2,D3是预置数据输人端,P和T是计数使能端,C是进 位输出端,它的设置为多片集成计数器的级 联提供了方 便。 74LS161的功能表如表1所示。由表可知,74LS161 具有以下功能。

数电作业-用74ls161设计同步加法计数器

数电作业-用74ls161设计同步加法计数器

74LS161 设计同步加法计数器

74LS161 是一种 TTL 元件,它可以用来设计同步加法计数器,具有高速、高效率、

稳定可靠等性能特点。

这种计数器可以用于电路或系统中,用于跟踪、记录、测量或控制。

用74LS161设计同步加法计数器包括信号路径、加法器、存贮器和控制电路的设计,

实现步进、计数和读取功能。

信号路径负责提供计数器和外界的数据输入和输出,加法器

负责计算位投入的数据,存贮器负责存放计数结果,控制电路负责控制存贮器的读取和写入。

它对内部计数器进行加法计数,为实现同步加法计数所采用的技术主要有两种,一种

是全同步,另一种是公共同步加法器(CPGA)。

全同步技术是通过集成存储器实现同步加

法计数,其主要优点是硬件结构简单、计数操作快速,它不需要控制信息来设置存储器;CPGA 技术在额外的控制电路的基础上,用梳状结构的存储器实现同步加法计数,这种技

术允许计数器暂停,但是比全同步技术要复杂。

通过分析,其实74LS161可以应用的情况很广,只要将信号路径、加法器、存贮器和

控制电路进行合理组合,就可以构建出多种不同的同步加法计数器,从而获得不同功能的

输出结果。

同时,有些设计并不需要复杂的控制电路,也可以设计出高效简便的计数系统。

另外,数字处理中的各种计数器也可以用74LS161设计,从而可以方便的实现复杂运算。

74LS161所采用的技术可以实现快速的计算、统计和存储处理,而且可以满足灵活性

和实用性要求,因此,它广泛用于电子设备中。

74LS161的逻辑功能-谭

输出

Q3 Q2 Q1 Q0

0000 d3 d2 d1 d0

保持 保持 计数

工作模式

异步清零 同步置数 数据保持 数据保持 加法计数

第一页,共23页。

第二页,共23页。

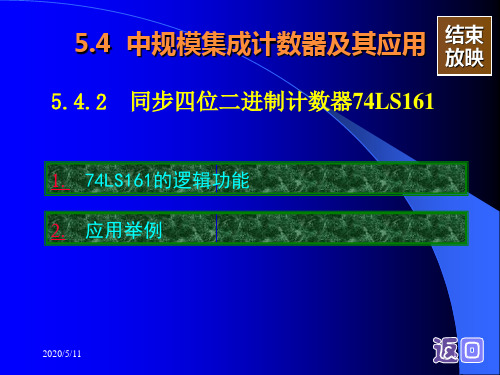

5.4 中规模集成计数器及其应用

结束 放映

5.4.2 同步四位二进制计数器74LS161

1. 74LS161的逻辑功能 2. 应用举例

有进位时,高位计数功能T =1; 无进位时,高位保持功能T =0。

第十五页,共23页。

用两片CT74LS161级联成16×16进制同步加法计数器

低位片

高位片

在计到1111以前,CO1=0,高位片保持原状态不变 在计到1111时,CO1=1,高位片在下一个CP加一

② 再用脉冲反馈法

第十六页,共23页。

第十四页,共23页。

(3)利用多片74LS161实现大容量计数 ① 先用级联法 计数器的级联是将多个集成计数器(如M1进制、M2 进制)串接起来,以获得计数容量更大的N(=M1×M2)

进制计数器。

一般集成计数器都设有级联用的输入端和输出端。

同步计数器实现的方法: 低位的进位信号→高位的保持功能控制端(相当于触发 器的T端)

利用与非门拾取状态1001 令D3 D2 D1 D0=0000 可实现从0开始计数的十进制计数 (0000到1001)

改变与非门的输入信号, 可以实现其它进制计数。

第十三页,共23页。

用74LS161构成从0开始计数的十进制计数器

利用与非门拾取状态1010

实现十进制计数 (0000到1001)

改变与非门的输入信号 ,可以实现其它进制计数。

例:用集成计数器74163和与非门组成的6进制计数器。

74LS161的逻辑功能1

在计到1111时,CO1=1,高位片在下一个CP加一 ② 再用脉冲反馈法

2013-7-11 14

例:用两片74LS161级联成五十进制计数器

0010 0011

十进制数50对应的二进制数为0011 0010 实现从0000 0000到0011 0001的50进制计数器

2013-7-11 15

作业题

实现十进制计数 (0110到1111)

改变D3 D2 D1 D0的状态,可以实现其它进制计数。 2013-7-11 10

图5-24 用74LS161构成从0开始计数的十进制计数器

利用与非门拾取状态1001 令D3 D2 D1 D0=0000

可实现从0开始计数的十进制计数 (0000到1001)

改变与非门的输入信号, 可以实现其它进制计数。 2013-7-11 11

同步计数器实现的方法: 低位的进位信号→高位的保持功能控制端(相当 于触发器的T端) 有进位时,高位计数功能T =1; 无进位时,高位保持功能T =0。

2013-7-11 13

用两片CT74LS161级联成16×16进制同步加法计数器

低位片

高位片

在计到1111以前,CO1=0,高位片保持原状态不变

状态 输出

图3-35 74LS161的外引线图 图3-36 74LS161的逻辑符号 CP输入 并行

输入

表5-14 74LS161的功能表

异步清0功 能最优先 同步并 行置数 CP上升 沿有效

2013-7-11

CO= Q3 Q2 Q1 Q0 CTT

4

2013-7-11

图5-22 74LS161的时序图

5-8 5-9 5-10

2013-7-11

16

采用74X161器件设计计数器-置数法

数字电路与逻辑设计授课教师:陈东电路与电子技术基础教学部本次授课内容 —— 采用74X161设计计数器(同步置数法)74X161器件的功能74X161设计计数器总结与练习采用普通触发器设计计数器电路的过程:缺点: 设计过程复杂、材料成本高、电路故障率高。

采用集成计数器设计计数器电路的优势:设计过程简单、材料成本低、电路故障率低,电路可重构性强。

74X161器件的功能74X161是一种4位二进制同步计数器,能进行M=16的 加法计数,还具有计数控制、置数、清零、进位等功能。

电路符号功能表直接清零端预置数控制端计数控制端计数输出端预置数据输入端 进位输出端计数脉冲输入端状态转移图74X161器件的应用 —— 固定模值计数器的设计应用单片74X161器件设计模值M≤16的计数器时,是从74X161器件(模值为16)的状态转移图中跨越(16-M)个状态,得到具有M个状态的计数器。

实现状态跨越既可以采用同步置数的方法,也可采用异步清零法。

同步置数法设计计数器的步骤:设计题目采用74X161设计模值M=10的计数器解:跨越后6个状态,保留包括'0000'在内的前10个状态。

状态转移图:跨越6个状态置数所谓“同步置数”是指置数过程与时钟边沿同步。

电路图:也可以跨越前6个状态,保留包括'1111'在内的后10个状态。

置数电路图:状态转移图:跨越6个状态也可跨越中间6个状态:状态转移图:置数跨越6个状态电路图:总结:74X161器件是一种常用的集成同步计数器,功能比较完整,使用方便,不仅可用于脉冲计数,也可用于分频、定时等。

利用74X161的清零功能和置数功能,正确设计反馈控制信号,可以实现任意固定模值的计数器电路,设计方法比较简单、电路性能良好。

练习题:题目:采用74X161设计一个M=11的同步计数器,要求初始状态从'0010'开始。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数电技术课程实践

班级:12电本

姓名:徐保霞

学号:201292150118 指导教师:崔用明

设计一个用74L161组成的14进加法计数器

一、摘要:本设计主要是对四位二进制同步计数器74L161(异步清除)的同步预置控制端进行分析设计,使74LS161能克服触发器的工作速度的差异情况以及竞争冒险现象,实现了使同步预置信号能够持续足够长的时间,从而使74LS161能够从0000这一状态复位变为1101状态,成功得竞争结果,实现十四进制计数器的设计。

英文摘要:This design is mainly to four binary synchronous counter 74 L161 (asynchronous clearance) analyze the synchronous reset control end of the design, make a 74 ls161 can overcome the trigger the differences of working speed and competitive adventure phenomenon, has realized the synchronous preset signal can be sustained long enough, so that 74 ls161 can this state is reset to 0000 from 1101, a competition to succeed as a result, achieve 14 into the design of the system counter.

关键词:计数器、同步预置

二、设计要求

1)熟练掌握加法计数器、74L161的基本概念。

2)实现14进加法计数器的设计

3) 掌握并分析结果

三、设计步骤

1、电路组成框图(图1-1)

图1-1

2、电路原理图(图1-2)

图1-2

3、元器件选择

74L161、与非门、数码管

4、参数的设计计算

设0000为预置数,则十四进制加法计数器的有效态为0000、0001、0010、0011、0100、0101、0110、0111、1000、1001、1010、1011、1100、1101(图1-3)

图(1-3)

将输入端的数据d3d2d1d0=0000设为预置数,在输入时钟脉冲CP上升沿的作用下,EP、ET、R D接高电平,当输出端Q l输出为低电平时接与非门,此时Q l 输出为高电平,与Q3 Q2 Q0再通过一个与非门,此时“0”接入L D,实现R D=1、L D=0,达到设计要求输出为预置数0000。

5、工作原理

74L161的有效状态,即0000、0001、0010、0011、0100、0101、0110、0111、1000、1001、1010、1011、1100、1101、1110、1111(图1-4)。

图1-4

74LS161具有以下功能:

①异步清零。

当R D=0时,不管其他输入端的状态如何,不论有无时钟脉冲

CP,计数器输出将被直接置零(Q

3Q

2

Q

l

Q

=0000),称为异步清零。

②同步预置数。

当R D=1、L D=0时,在输入时钟脉冲CP上升沿的作用下,输入端的数据d3d2d1d0被置入计数器的输出端,即Q3Q2Q l Q0=d3d2d1d0。

由于这个操作要与CP上升沿同步,所以称为同步预置数。

③计数。

当R D=L D=EP=ET=1时,在CP端输入计数脉冲,计数器进行二

进制加法计数。

④保持。

当R D=L D=1,且ET

EP =0,即两个使能端中有0时,则计数器保持原来的状态不变。

这时,如EP=0、ET=1,则进位输出信号C保持不变;如ET=0则不管EP状态如何,进位输出信号C为低电平0。

四、仿真

1、仿真图

2仿真结果

注:经过仿真没有出现误差

五、心得体会

通过这次的设计实践增强了自己的自学能力,自己查阅资料、设计电路图、参数计算等过程中我对这门课产生了兴趣,也掌握了很多课堂上没有学到的知识,使得自己的知识面更加广泛。

虽然在设计过程中遇到了困难,但通过向学长请教终于完成了,使我懂得无论做任何事都要认认真真、坚持不懈、不懂就问的态度。