集成电路芯片的射频测试技术-徐光

物理半导体行业中的射频测试技术手册

物理半导体行业中的射频测试技术手册在物理半导体行业中,射频测试技术是非常重要的,因为它能够用来测试和验证各种射频半导体器件的性能参数。

本手册将介绍与射频测试相关的重要技术和操作,以及如何优化测试策略和提高测试效率。

1. 射频测试基础射频测试是一种用于测量无线电频率和功率的技术。

它主要用于测试各种射频器件,例如放大器、混频器、功率放大器、滤波器和天线等。

射频测试需要使用一系列传感器、频谱仪、网络分析仪和信号源等仪器。

这些仪器都需要校准和配置,以确保测试的准确性和可靠性。

2. 射频测试参数在射频测试中,常用的参数包括频率、功率、增益、噪声指数、谐波和相位等。

这些参数可以通过网络分析仪和功率计等仪器来测量和分析。

此外,射频测试还需要对测试条件进行控制和调整,例如温度、湿度和电源噪声等。

3. 射频测试方法为了实现准确的射频测试,需要采用恰当的测试方法。

常见的测试方法包括网络分析法、功率传递法和功率反射法。

网络分析法可以测量信号的反射和传输等参数,功率传递法可以测量放大器等器件的功率增益,功率反射法可以测量器件的反射损耗和谐波等参数。

此外,射频测试还需要注意测试环境的干扰和电磁兼容性等问题。

4. 射频测试优化为了提高测试效率和准确性,需要进行射频测试优化。

优化的策略包括选择合适的测试环境、调整测试仪器的设置和校准、选择适当的测试方法和条件、以及使用自动化测试系统等。

此外,还需要进行数据分析和反馈,以指导测试策略的改进和优化。

结语射频测试是物理半导体行业中非常重要的一项技术,它可以帮助我们测量和分析各种射频器件的性能参数。

本手册提供了射频测试的基础知识、常用参数和方法,以及优化测试策略和提高测试效率的方法。

希望这些内容能够帮助您更好地理解射频测试技术,并在工作中取得更好的成果。

芯片集成电路电磁兼容测试技术

芯片集成电路电磁兼容测试技术摘要:当今,集成电路的电磁兼容性越来越受到重视,芯片电磁兼容(EMC)技术关乎整机电子系统及其周围电子器件的运行的安全可靠性,电磁兼容性。

电子设备和系统的生产商努力改进他们的产品以满足电磁兼容规范,降低电磁发射和增强抗干扰能力, 集成电路(IC)的电磁兼容性(EMC)的测试方法正受到越来越多的关注,文章基于国内外资料调研和课题组的研究成果, 介绍了器件级(IC)EMC测试方面的发展现状,测试标准,详细介绍了器件级(IC)主要的电磁兼容测试方法。

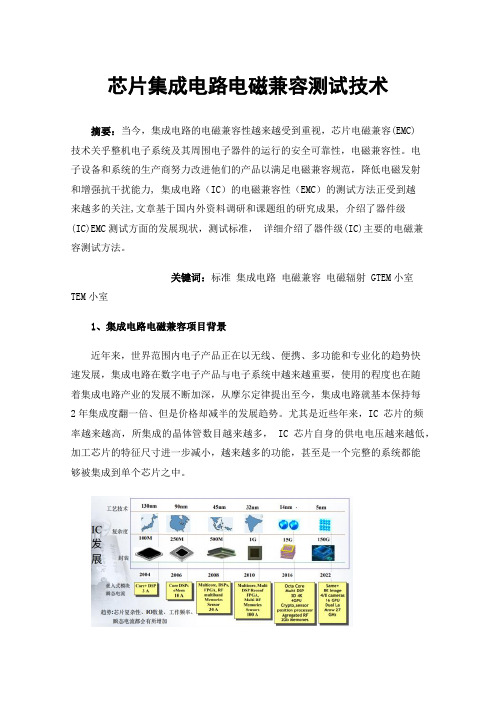

关键词:标准集成电路电磁兼容电磁辐射 GTEM小室TEM小室1、集成电路电磁兼容项目背景近年来,世界范围内电子产品正在以无线、便携、多功能和专业化的趋势快速发展,集成电路在数字电子产品与电子系统中越来越重要,使用的程度也在随着集成电路产业的发展不断加深,从摩尔定律提出至今,集成电路就基本保持每2年集成度翻一倍、但是价格却减半的发展趋势。

尤其是近些年来,IC 芯片的频率越来越高,所集成的晶体管数目越来越多, IC芯片自身的供电电压越来越低,加工芯片的特征尺寸进一步减小,越来越多的功能,甚至是一个完整的系统都能够被集成到单个芯片之中。

图1 IC发展总体趋势图2 IC性能发展趋势根据SEMI的分析报告,全球半导体市场从2015到2025年的预期份额,包括了各类型芯⽚所占的份额。

相⽚2015年的3427亿美元,预计在2025的市场份额将会达到6556亿美元,复合增长率为6.7%。

集成电路的快速发展,这为集成电路的大范围、多层次应用奠定了基础。

尤其在消费类产品领域,这种发展趋势尤为明显,各种数码类产品的普及就是很好的说明。

图3各类型芯⽚所占的份额图4 各尺寸芯⽚所占的份额这种快速发展也造成了电子系统电磁兼容性问题的日益突出,芯⽚复杂性、IO口的数量、⽚作频率、瞬态电流都会有所增加,这些发展均使得芯片级电磁兼容显得尤为突出,更高的集成度和使用密度,是片内和片外耦合的发生几率大大提高。

我国集成电路测试技术现状及发展策略

在当前21世纪的数字化时代,集成电路测试技术的发展已经成为全球科技领域的热点话题。

作为我国的一项战略性新兴产业,集成电路测试技术的现状和未来发展策略备受关注。

本文将就此主题展开全面评估,从深度和广度两个方面进行探讨,以帮助读者更全面地了解我国集成电路测试技术的发展现状和未来发展策略。

1. 我国集成电路测试技术现状在当前全球集成电路行业发展的大背景下,我国的集成电路测试技术正在经历着快速的发展。

随着科技创新和产业升级的不断推进,我国的集成电路测试技术已经取得了一系列重要的成就。

其中,包括了硬件设备的不断优化,测试技术的不断创新,以及标准化和规范化的不断提升。

与此我国的集成电路测试技术应用领域也在不断拓展,不仅包括了传统的消费电子领域,还涉及到了汽车电子、物联网、人工智能等新兴产业领域。

我国集成电路测试技术的现状呈现出了一种蓬勃发展的态势。

2. 我国集成电路测试技术的发展策略针对当前我国集成电路测试技术的现状,我们首先需要明确未来的发展目标和战略定位。

在此基础上,我们应该持续加大对集成电路测试技术的研发投入,加强对关键技术的攻关,致力于建设一批具有国际竞争力的高水平集成电路测试技术研发团队。

应该加强国际合作,吸引国际一流的技术人才和先进的技术理念,不断完善我国集成电路测试技术产业生态,加快技术创新和产业升级的步伐。

另外,在政策支持方面,相关部门还应当制定一系列有针对性的政策措施,推动整个集成电路测试技术产业链的健康发展。

3. 个人观点和总结从个人角度来看,我认为我国集成电路测试技术的现状已经非常可喜,但仍有很多方面需要不断完善和提升。

在未来的发展中,我国应该更加注重基础研究和核心技术创新,打造具有全球竞争力的集成电路测试技术产业。

应该更加注重产学研合作,加强技术人才培养和团队建设,为我国集成电路测试技术的跨越式发展和全球领先提供坚实的人才和技术基础。

我国集成电路测试技术的发展已经取得了一定的成就,但在未来的道路上仍需不懈努力。

半导体晶圆检测关键连续波深紫外激光光源研制

第53卷第4期2024年4月人㊀工㊀晶㊀体㊀学㊀报JOURNAL OF SYNTHETIC CRYSTALS Vol.53㊀No.4April,2024简㊀㊀讯半导体晶圆检测关键连续波深紫外激光光源研制徐国锋,王正平,王树贤,武㊀奎,梁㊀飞,路大治,张怀金,于浩海(山东大学晶体材料研究院,晶体材料国家重点实验室,济南㊀250100)深紫外激光是半导体领域的关键光源㊂基于非线性频率变换的全固态深紫外激光具有结构紧凑㊁价格低廉等优势,有广泛需求㊂受限于晶体非线性系数较线性介电常数小数个数量级,深紫外激光通常以具有高峰值(千瓦级)的脉冲形式获得,连续波深紫外激光效率较低,其实用化极其困难㊂高峰值的紫外激光通常会对半导体表面及内部产生损伤,限制了半导体晶圆缺陷等装备的应用和发展㊂当前,晶圆检测用关键瓦级连续波深紫外激光器制备技术被国外极少数几家企业高度垄断,我国相关研究和产业化技术急需发展㊂在我国多个项目的持续支持下,基于前期研究,山东大学晶体材料国家重点实验室于浩海教授㊁张怀金教授相关团队提出了瓦级连续波深紫外激光器设计方案,并解决了稳定性㊁高效输出及紫外损伤的系列工程化难题,研制出国内首台瓦级连续波深紫外激光器整机(见图1),激光波长为261nm,功率波动RMS <1%,达到实用化要求,稳定性等关键指标达到国际文献报道最优水平㊂与国外高度垄断的266nm 激光器相比,该激光器具有结构更紧凑㊁波长更短㊁效率更高㊁分辨率更高等优势,填补了国内市场空白,为我国晶圆检测装备的全国产化自主研发奠定了关键光源基础㊂同时,针对SiC㊁GaN 等宽禁带半导体的检测需求,也研制出了瓦级320nm 连续波深紫外激光器整机(见图2),可服务于我国第三代半导体产业的高速发展㊂目前,上述成果的核心技术已转让到有维光电有限公司,着力开展批量化生产㊂图1㊀瓦级261nm 连续波深紫外激光器㊂(a)整机照片;(b)激光光谱及功率稳定性(RMS =0.66%)图2㊀瓦级320nm 连续波深紫外激光器㊂(a)整机照片;(b)激光光谱及功率稳定性(RMS =0.81%)。

芯片检测 光谱

芯片检测光谱

芯片检测中的光谱技术是一种利用物质对特定波长光的吸收、发射或反射特性来进行材料分析的方法。

光谱检测技术在半导体制造和芯片质量控制中扮演着重要角色,它可以提供关于材料成分、纯度、晶体结构以及表面缺陷等的信息。

以下是几种常用的光谱检测技术及其在芯片检测中的应用:

1. 傅里叶变换红外光谱(FTIR): FTIR可以用来检测芯片材料中的化学成分和分子结构。

通过分析材料对红外光的吸收光谱,可以识别出特定的官能团,进而判断出材料的类型和纯度。

2. 拉曼光谱: 拉曼光谱是一种无损检测技术,它通过分析光子散射后的能量变化来获得材料的分子振动信息。

拉曼光谱能够提供晶体结构、应力状态、掺杂水平等的信息,对于半导体材料的质量控制非常有用。

3. 紫外-可见光谱(UV-Vis): UV-Vis光谱可以用来评估芯片表面的光吸收特性,从而检测污染物、氧化层厚度以及其他表面特性。

4. 荧光光谱: 荧光光谱技术可以用来检测芯片上的某些元素或化合物,因为它们在受到激发后会发出特定波长的光。

这种技术对于检测芯片上的微量杂质特别有效。

5. 近红外光谱(NIR): NIR光谱检测通常用于测量材料的浓度和组成,因为许多化学物质在近红外区域有特定的吸收峰。

光谱检测技术的关键优势在于其非接触性和高灵敏度,这使得它们能够在不损坏芯片的情况下提供精确的材料属性信息。

此外,光谱技术通常能够快速进行,适合在线监测和实时质量控制。

随着光谱仪器的不断进步,它们在芯片制造和检测中的应用也在不断扩大,有助于提高芯片的生产效率和产品质量。

集成电路的射频功率放大器设计与测试

集成电路的射频功率放大器设计与测试随着移动通信技术的迅速发展,无线通信设备在人们生活和工作中的应用越来越广泛。

而射频(Radio Frequency,简称RF)功率放大器作为无线通信系统中不可或缺的关键器件之一,具有放大无线信号、提高通信距离和传输速率等主要作用。

本文将从集成电路的角度出发,探讨射频功率放大器的设计原理、常见技术、测试方法和应用前景。

一、射频功率放大器的设计原理射频功率放大器是一种用于向电子设备输入射频信号的放大器,能够输出较大的放大功率。

其通常由输入匹配网络、放大器、输出匹配网络和直流电源四部分组成。

其中,输入匹配网络用于匹配输入信号和功率放大器的输入阻抗;放大器是实现信号放大的核心部件;输出匹配网络用于匹配输出阻抗和负载(如天线、滤波器等);直流电源用于提供放大器所需的直流电压,以维持其正常工作。

在射频功率放大器设计中,需要考虑多个因素,如放大器的线性度、稳定性、带宽等。

其中,线性度是射频功率放大器的重要性能指标之一。

在信号输入量较小的情况下,射频功率放大器的增益输出与输入信号之间呈线性增加关系。

然而,当输入信号过大时,放大器的输出增益将不再呈线性增加,而是出现非线性失真现象,导致输出信号扭曲变形,降低通信系统的可靠性和稳定性。

二、射频功率放大器的常见技术射频功率放大器的设计和应用非常广泛,同时也涌现了不少新型的技术。

以下是其中的几种常见技术:1、高效率功率放大器技术高效率功率放大器技术是一种利用半导体材料研究高效功率放大器的技术。

该技术能够有效利用电源,提供功率放大器所需的电能。

在高速数码信号传输领域,该技术已被广泛应用。

2、宽带功率放大器技术宽带功率放大器技术是一种能够应对多种频率信号的功率放大器。

在现有的通信系统中,频率范围十分广泛,因此需要一种宽带功率放大器来满足各种信号的放大需求。

3、全固态功率放大器技术随着微电子技术的不断发展,全固态功率放大器技术也逐渐成熟。

该技术能够在多个频段实现全负载、多个模拟和数字信号的放大。

射频集成电路系统 eda 关键技术与应用

射频集成电路系统 eda 关键技术与应用射频集成电路系统(RFIC)是指将射频电路和数字电路集成在一起的电路系统。

它在现代通信、雷达、卫星导航等领域中起着至关重要的作用。

EDA(Electronic Design Automation)是一种利用计算机辅助设计技术进行电子系统设计的方法。

在射频集成电路系统的设计过程中,EDA起着至关重要的作用。

EDA技术可以帮助设计工程师在设计过程中提高效率和准确性。

通过使用EDA工具,设计师可以利用各种模拟和数字设计工具来验证和优化射频集成电路系统的性能。

这些工具可以帮助设计师模拟和分析各种射频电路的特性,如增益、带宽、噪声等。

同时,EDA工具还可以帮助设计师进行电磁仿真,以解决射频集成电路系统中的电磁兼容性和电磁干扰等问题。

EDA技术还可以帮助设计师进行射频集成电路系统的布局和布线。

在射频集成电路系统中,布局和布线对性能和可靠性至关重要。

通过使用EDA工具,设计师可以对射频集成电路系统进行布局和布线的优化,以确保射频信号的完整性和稳定性。

同时,EDA工具还可以帮助设计师进行电源和地线的规划,以减少电磁噪声和信号干扰。

EDA技术还可以帮助设计师进行射频集成电路系统的仿真和验证。

在设计过程中,设计师需要验证射频集成电路系统的性能是否满足设计要求。

通过使用EDA工具,设计师可以对射频集成电路系统进行仿真和验证,以确保其性能和可靠性。

同时,EDA工具还可以帮助设计师进行电源和地线的规划,以减少电磁噪声和信号干扰。

EDA技术还可以帮助设计师进行射频集成电路系统的自动布局和布线。

在射频集成电路系统中,布局和布线过程繁琐且耗时。

通过使用EDA工具,设计师可以利用自动布局和布线技术来优化射频集成电路系统的性能和可靠性。

自动布局和布线技术可以帮助设计师快速生成高质量的布局和布线方案,从而提高设计效率。

EDA技术在射频集成电路系统的设计中起着至关重要的作用。

它可以帮助设计师提高设计效率和准确性,优化射频集成电路系统的性能和可靠性。

无锡市人民政府关于公布2013年度无锡市科学技术进步奖获奖项目的决定

无锡市人民政府关于公布2013年度无锡市科学技术进

步奖获奖项目的决定

文章属性

•【制定机关】无锡市人民政府

•【公布日期】2014.01.17

•【字号】锡政发[2014]10号

•【施行日期】2014.01.17

•【效力等级】地方规范性文件

•【时效性】现行有效

•【主题分类】机关工作

正文

无锡市人民政府关于公布2013年度无锡市科学技术进步奖获

奖项目的决定

(锡政发〔2014〕10号)

各市(县)和各区人民政府,市各委、办、局,市各直属单位:

根据《无锡市科学技术进步奖励办法》,经无锡市科学技术进步奖评审委员会评审,市政府决定,授予“大型清洁高效电站汽轮机空心叶片关键制造技术研发及应用”等79个项目2013年度无锡市科学技术进步奖,其中一等奖5项,二等奖19项,三等奖55项。

希望获奖单位和个人再接再厉,为推进“东方硅谷”建设、加快打造“四个无锡”作出新的贡献。

全市各单位要坚持创新驱动,大力提高自主创新能力,加快提升转型发展水平,确保我市在实现“第二个率先”新征程中继续走在全省前列。

附件:2013年度无锡市科学技术进步奖项目

无锡市人民政府

2014年1月17日

附件

2013年度无锡市科学技术进步奖项目。

K波段低噪声放大器芯片

K波段低噪声放大器芯片

艾萱;徐光;郑远;陈新宇;前锋;杨磊

【期刊名称】《通讯世界》

【年(卷),期】2015(000)013

【摘要】设计一款K波段低噪声放大器芯片,采用0.15μm PHEMT工艺,工作频段:22~23GHz,增益大于17dB,噪声系数小于2.4dB,1dB功率压缩点大于7dBm,输入/输出电压驻波比小于2,偏置电压5V,静态工作电流12mA,具有极低功耗。

【总页数】2页(P74-75)

【作者】艾萱;徐光;郑远;陈新宇;前锋;杨磊

【作者单位】南京电子器件研究所; 南京国博电子有限公司,江苏南京210016;南京电子器件研究所; 南京国博电子有限公司,江苏南京210016;南京电子器件研究所; 南京国博电子有限公司,江苏南京210016;南京电子器件研究所; 南京国博电子有限公司,江苏南京210016;南京电子器件研究所; 南京国博电子有限公司,江苏南京210016;南京电子器件研究所; 南京国博电子有限公司,江苏南京210016【正文语种】中文

【中图分类】TN722.3

【相关文献】

1.一种D波段低噪声放大器芯片设计 [J], 刘杰;蒋均;石向阳;田遥岭;

2.一种D波段低噪声放大器芯片设计 [J], 刘杰;蒋均;石向阳;田遥岭

3.S波段小型化宽带低噪声放大器的设计 [J], 豆刚; 张海峰; 向虎; 许庆

4.星载L波段宽带低噪声放大器芯片设计 [J], 赵博超;徐辉;殷盼;贺娟;张大为;徐鑫

5.X波段单片低噪声放大器芯片 [J], 彭龙新;周正林;蒋幼泉;林金庭;魏同立

因版权原因,仅展示原文概要,查看原文内容请购买。

集成电路芯片的射频测试技术

集成电路芯片的射频测试技术摘要:集成电路芯片设计制造,是目前国内电子设备和通信技术领域的热门话题,市场需求旺盛。

在集成电路测试中引入射频测试技术,有助于射频集成电路实现产品优质化和工艺自动化建设,!确保射频集成电路高效准确测试的同时,还能节约大量作业成本,因此得到普遍欢迎。

本文概括论述射频测试技术,功能和发展前景,详细介绍这项技术的作用原理,对射频测试技术进行全面分析,力求为射频集成电路测试提供更加优质的技术应用,促进电子设备和通信技术行业实现更快发展。

关键词:集成电路芯片;射频测试技术;检测引言:射频测试技术是专门用于射频集成电路测试的技术类型,在通信技术和电子设备领域获得了广泛应用,它是提高集成电路质量,加快检测效率的技术保障。

对提升国内集成电路产品质量的现实意义尤为重大。

相关人员还须高效开发利用包括直流在片测试系统,小信号参数测试技术以及测试数据统计技术等在内的射频测试技术应用奉献优质集成电路芯片供应市场需求。

1.射频测试技术与集成电路的其它技术类型不同,射频集成电路具有独具特色的射频测试技术。

目前在电子设备制造领域,网络通信技术领域,设计制造集成电路芯片已经有了突飞猛进的发展,但是,仍然难以满足人们对电子设备急剧上升的功能需求,要求集成电路必须大力提升产能和成品质量,才能有效应对旺盛的市场需求。

国内应用的集成电路种类中,射频集成电路的应用范围是最为普及的,技术人员对射频测试技术进行进一步研发利用,有助于射频集成电路提高产品质量,现实意义十分重大。

但是目前国内在研发集成电路技术方面侧重于设计制造集成电路的工艺方面,测试技术没有得到应有的重视。

作为最关键的射频集成电路技术类型,研发利用射频测试技术对提升国内射频集成电路产品质量意义尤为深远。

2.射频测试技术原理要成功研发利用射频测试技术,首要任务就是对这种技术的原理做到全面了解。

集成电路的优势在于小体积,自重轻,性能优良,有很长的使用寿命,在通信技术以及设计制造电子设备等领域备受青睐,应用范围极广,因此,研发利用集成电路,有助于国家在电子技术方面取得更大发展。

IC测试原理-射频无线芯片测试基础

IC测试原理-射频/无线芯片测试根底许伟达科利登系统1 引言芯片测试原理讨论在芯片开发和生产过程中芯片测试的根本原理,一共分为四章,下面将要介绍的是最后一章。

第一章介绍了芯片测试的根本原理,第二章介绍了这些根本原理在存储器和逻辑芯片的测试中的应用,第三章介绍了混合信号芯片的测试。

本文将介绍射频/无线芯片的测试。

2 射频/无线芯片测试根底射频/无线系统会同时包含一个发射器和接收器分别用于发送和接收信号。

我们先介绍发射器的根本测试,接下来再介绍接收器的根本测试。

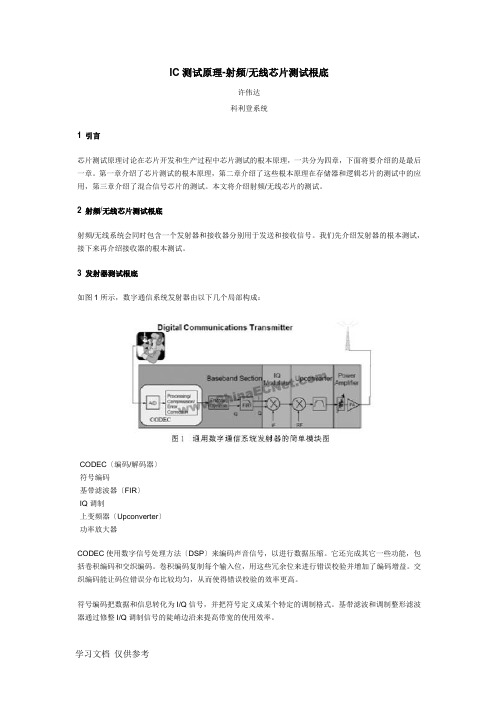

3 发射器测试根底如图1所示,数字通信系统发射器由以下几个局部构成:·CODEC〔编码/解码器〕·符号编码·基带滤波器〔FIR〕·IQ调制·上变频器〔Upconverter〕·功率放大器CODEC使用数字信号处理方法〔DSP〕来编码声音信号,以进行数据压缩。

它还完成其它一些功能,包括卷积编码和交织编码。

卷积编码复制每个输入位,用这些冗余位来进行错误校验并增加了编码增益。

交织编码能让码位错误分布比较均匀,从而使得错误校验的效率更高。

符号编码把数据和信息转化为I/Q信号,并把符号定义成某个特定的调制格式。

基带滤波和调制整形滤波器通过修整I/Q调制信号的陡峭边沿来提高带宽的使用效率。

IQ调制器使得I/Q信号相互正交〔积分意义上〕,因此它们之间不会相互干扰。

IQ调制器的输出为是IQ 信号的组合,就是一个单一的中频信号。

该中频信号经过上变频器转换为射频信号后,再通过放大后进行发射。

先进的数字信号处理和专用应用芯片技术提高了数字系统的集成度。

现在一块单一的芯片就集成了从ADC 转换到中频调制输出的大局部功能。

因此,模块级和芯片级的射频测试点会减少很多,发射器系统级和天线端的测试和故障分析就变得更加重要。

发射器的主要测试内容信道内测试·信道内测试采用时分复用或者码分复用的方法来测试无线数字电路。

可调谐半导体激光器研究及进展

半导体激光器调谐的物理机理是通过直接或间 接改变激光器谐振腔的长度 ,使谐振腔中谐振模式 位置产生微小移动 ,并通过频率选择元件 ,选择出频 率移动的波长. 半导体有源区能在较宽的波长范围 内产生光增益 ,这为波长调谐提供了必要条件. 目前 半导体激光器有源区广泛采用多量子阱 ( MQW) 结 构 ,当电流注入足够高时 ,量子阱结构能够在很宽的 波长范围内产生光增益 ,例如 In GaAsP/ InP 量子阱 材料光增益范围可达 285. 5nm[2 ] . 由于态密度被平 缓填充 ,增益的波长范围随注入电流增加而展宽. 当 电流达到一定值时 ,电子将占据第二个量子化能级 , 因此在大注入电流下 ,能获得极宽的增益谱. 一般来 说 ,为了获得更宽的增益谱 ,则需要极高的注入电流 密度 (通常大于 10kA/ cm2) ,而当有源区改用量子点 (QD) 结构时 ,则可以在比较低的注入电流密度 (1 — 2kA/ cm2) 下获得极宽的增益[3 ] . 总之 ,能够产生极 宽的宽增益范围的半导体材料是实现宽波长范围调 谐的理想介质.

φp = βL p = k ·neffp ·L p .

(4)

布拉格区的相位由耦合波方程得到 ,在布拉格反射

区可以近似表示为

φd

≈

π 2

+

(β -

π Λ)

·L d

=

π 2

+

( k ·neffb

-

πl Λ

)

·L p .

(5)

为简单起见 ,我们首先忽略相位区 ,激光器仅由

有源区和 DBR 区构成 [ 图 1 (a) ] . 图 1 (c) 画出了满

波长可调谐半导体激光器从 20 世纪 80 年代起 开发就很活跃 ,按结构划分主要有外腔半导体激光 器 、多电极半导体激光器 、垂直腔面发射激光器等 ; 按调谐机理划分 ,有电调谐 、热调谐和机械调谐三大 类 ;按整个调谐波长范围内的调谐特征划分 ,则有连 续可调 、非连续可调和准连续可调三类.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

,吴 ,陈 ,钱 ,陈 徐 光 振 海 金 远 峰 新 宇

(The 55

Abstract

, Wu Zhenhai, Chen Jinyuan, Qian Feng, Chen Xinyu

th

RF IC onWafer Test Technique

Research Institute

1

July

2010

Semiconductor Technology Vol 35 Supplement

191试 技 术 :集

櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶

, CETC , Nanjing 210016, China )

: RF test technique is one of the most important technology in RF IC process . Aim at the requirement of full performance test , a DC onwafer test system and a smallsignal S parameters test system are introduced which used in RF IC test , and the statistical program of test data and test yield is also been

2

0

引 言

,特 随 着 无 线 通 信 系 统 的 广 泛 应 用 别 是 3G 通 ,射 、高 频 集 成 电 路 向 着 高 频 段 性 能 的 方 信 的 推 广 ,因 ,同 , 此 对 射 频 测 试 的 要 求 越 来 越 高 时 向 演 进 “ ”的 集 成 电 路 应 用 商 对 射 频 集 成 电 路 的 零 失 效 要 求 对 射 频 电 路 提 出 了 试 要 求 规 的 ,也 。常 100 % 测 测 试 手 段 不 再 能 满 足 这 些 产 品 的 需 要 片 直 流 和 ,在 微 波 测 试 技 术 成 为 全 面 反 映 芯 片 性 能 的 必 备 手 段 。 同 时 在 片 测 试 技 术 也 为 质 量 过 程 提 供 相 应 的 工 艺 参 频 集 成 电 路 的 射 频 测 试 系 统 数 ,是 。因 1 射 质 量 流 程 控 制 中 重 要 的 技 术 支 撑 手 段 ,无 ,在 此 论 是 性 能 保 障 还 是 质 量 流 程 控 制 片 测 试 11 原 理 简 介 [ ] 技 术 都 是 产 品 开 发 中 的 一 个 重 要 环 节。 常 规 的 试 步 骤 是 将 装 到 测 试 夹 具 IC 测 IC 安 目 前 国 内 射 频 集 成 电 路 技 术 主 要 注 意 力 都 集 中 中 。进 。采 、成 行 单 个 测 试 用 此 种 方 法 速 度 慢 本

櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 櫶 doi 10 3969 / j issn 1003353x 2010 z1 052

:

集 成 电 路 芯 片 的 射 频 测 试 技 术

( ,南 中 国 电 子 科 技 集 团 公 司 第 五 十 五 研 究 所 京 210016) :射 。针 ,提 摘 要 频 测 试 是 射 频 集 成 电 路 生 产 的 关 键 技 术 对 全 面 性 能 测 试 的 要 求 出 了 用 于 射 频 直 流 在 片 测 试 系 统 和 小 信 号 数 测 试 系 统 完 成 了 测 试 数 据 统 计 及 成 品 率 统 计 程 序 ,并 IC 的 S参 的 编 写 试 结 果 表 明 系 统 解 决 了 射 频 芯 片 片 测 试 的 技 术 问 题 射 频 集 成 电 路 应 。测 ,该 ,为 100 % 在 用 提 供 了 有 力 保 障 。 关 键 词 频 集 成 电 路 片 测 试 流 测 试 信 号 数 :射 ;在 ;直 ;小 S参 :TN407;TN432 文 :A 文 :1003353X ( 中 图 分 类 号 献 标 识 码 章 编 号 刊 2010) 增 019103

,且 ,无 。 高 具 有 破 坏 性 法 进 行 试 100 % 测 、微 、直 而 在 片 测 试 是 以 探 针 台 波 探 针 流 偏 置 探 卡 为 基 本 测 试 设 备 配 备 相 应 的 测 试 仪 表 所 构 成 的 。这 裸 芯 片 测 试 平 台 不 仅 消 除 了 金 丝 长 度 和 测 试 夹 ,而 具 对 芯 片 性 能 的 影 响 且 解 决 了 传 统 测 试 方 法 只 “代 ”的 能 对 一 个 表 性 样 品 进 行 测 试 而 无 法 做 到 。同 ,在 能 测 试 的 难 题 时 片 测 试 的 测 试 速 100 % 性 ,并 且 不 需 要 针 对 不 度 比 传 统 的 装 架 测 试 大 大 提 高 ,降 , 同 芯 片 设 计 特 定 的 测 试 夹 具 低 了 人 力 和 成 本 真 正 做 到 了 在 控 制 成 本 的 同 时 提 高 测 试 性 能 和 测 试 。 效 率 流 在 片 测 试 系 统 12 直 。 直 流 在 片 测 试 系 统 针 对 的 对 象 是 片 GaAs 圆 直 流 在 片 测 试 主 要 包 括 直 流 终 测 和 试 两 个 PCM 测 。 重 要 内 容 芯 片 直 流 终 测 需 要 判 断 芯 片 中 每 一 级 管 子 的 性 ,因 ,直 能 此 对 于 多 级 管 子 的 芯 片 而 言 流 探 针 的 制 。 作 精 度 及 探 针 材 料 的 选 择 都 需 要 满 足 工 艺 的 要 求 ,由 ,在 对 于 放 大 器 而 言 于 功 放 管 芯 的 特 殊 性 直 流 。为 ,提 测 试 过 程 中 会 引 起 振 荡 了 避 免 振 荡 高 测 试 的 安 全 性 就 必 须 选 择 特 殊 材 料 的 探 针 并 且 需 要 在 直 。 流 探 针 卡 上 制 作 防 振 电 路 由 于 测 试 的 对 象 是 圆 片 上 的 数 千 只 芯 片 试 ,测 。建 的 准 确 性 和 速 度 都 是 测 试 中 要 解 决 的 关 键 问 题 立 自 动 的 直 流 在 片 测 试 系 统 时 采 用 探 针 并 联 的 ,同 方 式 一 次 测 量 多 个 器 件 的 方 法 来 提 高 测 试 速 度 将 每 个 芯 片 测 试 速 度 控 制 在 几 秒 量 级 。 。对 直 流 测 试 主 要 解 决 低 频 振 荡 的 问 题 于 控 制 电 路 用 很 多 直 流 探 针 将 每 个 接 地 连 接 起 来 ,采 ,全 。对 ,由 面 测 试 电 路 的 直 流 特 性 于 放 大 器 于 接 地 的 不 良 常 容 易 引 起 振 荡 成 放 大 器 烧 毁 时 ,常 ,造 ,同 放 大 器 由 于 功 耗 引 起 的 升 温 是 测 试 中 需 要 考 虑 的 另 一 个 问 题 。通 ;对 过 脉 冲 测 试 的 方 法 解 决 散 热 问 题 ,合 于 低 频 振 荡 的 问 题 适 的 波 电 路 以 及 多 级 RC 滤 [ ] 波 电 路 是 解 决 问 题 的 主 要 方 法。 LC 滤 信 号 数 测 试 技 术 13 小 S参 小 信 号 数 测 试 主 要 解 决 测 试 精 度 和 测 试 S 参

3

。控 ,因 稳 定 性 的 问 题 制 类 电 路 本 身 插 损 就 比 较 小 。同 , 此 对 系 统 的 精 度 要 求 较 高 时 由 于 小 信 号 测 量 ,外 输 入 功 率 比 较 小 界 的 干 扰 会 对 测 试 产 生 很 大 的 影 响 。 , 解 决 测 试 精 度 问 题 首 先 要 选 择 高 精 度 的 矢 网 。最 其 次 连 接 电 缆 的 驻 波 一 定 要 很 好 关 键 的 是 校 准 。 件 参 数 的 提 取 , Cascade 是 校 准 件 采 用 校 准 片 国 际 Cascade 的 ,校 上 著 名 的 探 针 台 和 校 准 片 的 供 应 商 准 片 的 设 计 。厂 ,便 和 工 艺 精 度 国 际 领 先 商 同 时 提 供 寄 生 参 数 ,提 于 微 波 测 试 系 统 的 校 准 高 测 试 系 统 的 测 试 精 [ ] 度。 ,可 另 外 为 了 减 小 外 界 的 干 扰 以 采 用 屏 蔽 罩 的 ,将 。 方 法 被 测 件 放 入 屏 蔽 罩 中 试 数 据 统 计 技 术 及 成 品 率 统 计 程 序 编 写 14 测 ,批 随 着 芯 片 工 艺 技 术 的 提 升 生 产 量 越 来 越 ,为 大 了 客 观 评 价 一 批 芯 片 的 性 能 就 必 须 对 数 据 进 ,根 。 行 统 计 分 析 据 统 计 结 果 指 导 设 计 和 工 艺 根 据 统 计 学 理 论 为 了 完 整 反 映 产 品 的 性 能 就 必 。根 须 进 行 期 望 和 方 差 的 统 计 据 单 片 的 性 能 指 标 进 ,如 :开 、衰 关 减 器 电 路 芯 片 的 微 波 行 不 同 的 统 计 ,驻 ;放 波 大 器 电 路 芯 片 的 微 波 性 性 能 参 数 有 插 损 ,驻 。为 波 了 提 高 统 计 效 率 和 统 计 结 能 参 数 有 增 益 果 的 准 确 性 ,必 。本 须 采 用 计 算 机 自 动 化 的 方 法 文 ,对 学 软 件 采 用 编 程 的 方 法 测 试 数 将 采 用 Matlab 数 、快 。 据 进 行 实 时 速 的 统 计 分 析 制 程 序 的 编 写 15 控 ,由 在 传 统 的 手 动 测 试 方 法 中 于 其 速 度 比 较 、可 低 靠 性 比 较 差 等 缺 点 使 其 不 能 满 足 批 量 生 产 的 需 求 了 解 决 测 试 速 度 的 问 题 般 仪 器 都 具 备 。为 ,一 司 推 出 的 功 程 控 的 功 能 。 Agilent VEE 是 Agilent 公 能 强 大 的 图 形 化 可 编 程 语 言 可 以 通 过 系 统 总 线 。它 。 对 测 试 仪 器 进 行 控 制 同 时 进 行 数 据 的 采 集 和 处 理 为 了 提 高 测 试 的 速 度 和 采 取 数 据 的 准 确 性 者 采 ,作 用 发 环 境 分 别 编 写 小 信 号 参 数 测 试 系 统 控 VEE 开 。 制 程 序 和 脉 冲 功 率 相 位 测 试 系 统 控 制 程 序