中科大DSP课件6

dsp课件

DSP的特点

DSP具有高效性

由于DSP采用数字信号处理器 进行信号处理,因此其处理效 率高,能够实现高速实时信号

处理。

DSP具有高精度

数字信号处理器可以实现对信 号的高精度处理,避免了模拟 信号处理中可能出现的误差和 失真。

快速傅里叶变换(FFT)

01

FFT是一种高效计算离散傅里叶变换(DFT)及其逆变换的算法

。

数字滤波器设计

02

数字滤波器是一种用于信号处理的算法,可以实现对信号的滤

波、去噪等功能。

数字信号处理(DSP)算法

03

DSP算法包括多种数字信号处理方法,如频域分析、时域分析

、功率谱分析等。

CHAPTER 04

DSP课件

目 录

• DSP概述 • DSP硬件平台 • DSP软件编程 • DSP在信号处理中的应用 • DSP的优化与扩展 • DSP的发展趋势与未来展望

CHAPTER 01

DSP概述

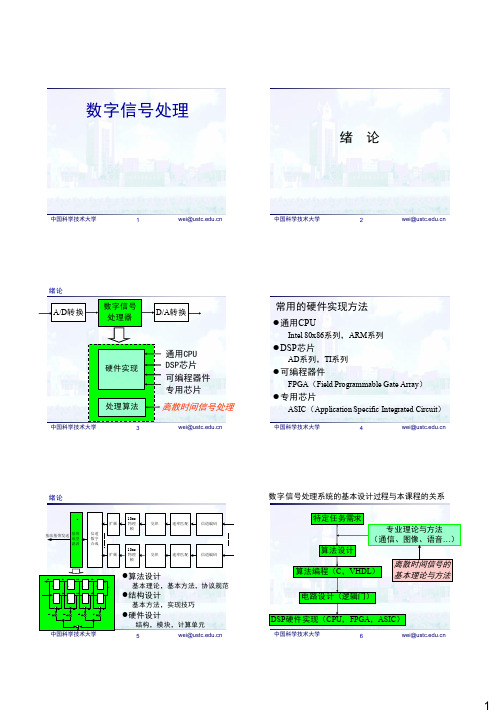

DSP的定义

数字信号处理(DSP)是一门涉及信号处理、算法设计、系统实现等领域的学科 。它主要研究如何利用数字信号处理器(DSP)对数字信号进行采集、变换、滤 波、估值、压缩等处理,以满足人们在不同领域的需求。

DSP扩展板

内存扩展板

用于扩展DSP的内存容量,提高数据处理能力。

数字IO扩展板

用于扩展DSP的数字输入输出接口,实现与外部设备的通信。

音频视频接口扩展板

用于扩展DSP的音频视频接口,实现音频视频数据的采集和输出。

DSP与其他设备的连接

DSP第六章6.3

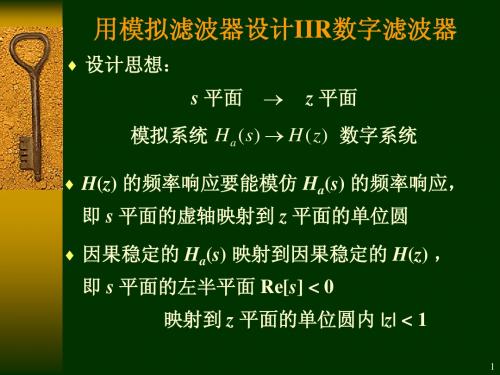

♦ 设计思想: 设计思想:

s 平面

→

z 平面

模拟系统 H a ( s ) → H ( z ) 数字系统

♦ H(z) 的频率响应要能模仿 Ha(s) 的频率响应, 的频率响应,

即 s 平面的虚轴映射到 z 平面的单位圆

♦ 因果稳定的 Ha(s) 映射到因果稳定的 H(z) ,

7

3、模拟滤波器的数字化方法 、

H a ( s ) → ha (t ) → ha (nT ) → h(n) → H ( z )

Ak H a (s) = ∑ k =1 s − sk ha (t ) = L [ H a ( s )] = ∑ Ak e u (t )

−1 N

N

sk t

k =1

h(n) = ha (nT ) = ∑ Ak e

∑

4

k

以改变程序中的T值 观察 的大小与频谱混叠失真的关 以改变程序中的 值,观察T的大小与频谱混叠失真的关 系。

17

%例6.3.2 用脉冲响应不变法设计数字滤波器程序: 用脉冲响应不变法设计数字滤波器程序 T=1; ; wp=0.2*pi/T; ws=0.35*pi/T; rp=1; rs=10; 的模拟滤波器指标 %T=1 s的模拟滤波器指标 的模拟滤波器指标 [N, wc]=buttord(wp, ws, rp, rs, 's'); ] %计算相应的模拟滤波器阶数N和3 dB截止频率 截止频率wc 计算相应的模拟滤波器阶数 和 截止频率 [B, A]=butter(N, wc, 's'); ] %计算相应的模拟滤波器系统函数 计算相应的模拟滤波器系统函数 [Bz, Az]=impinvar(B, A); ] %用脉冲响应不变法将模拟滤波器转换成数字滤波器 省略绘图部分。 省略绘图部分。 %T=1s

DSP第06讲

地址生成方式:重复操作

以RPTZ为例,说明单指令重复操作: 语法:RPTZ dst, #lk 说明:dst 清零且执行下一条指令 k+1 次 , 其中 常数 k 存放在循环计数器 RC 中。 举例 : RPTZ A, 1023; 重复执行下一条指令 1024 次

STL

A, *AR2+

地址生成方式:重复操作

地址生成方式:中断

'C54x 既支持软件中断 , 也支持硬件中断 : (1) 由程序指令 (INTR、TRAP或 RESET) 要求 的软件中断。 (2) 由外围设备信号要求的硬件中断。这种硬件 中断有两种形式 : ①受外部中断口信号触发的外部硬件中断。 ②受片内外围电路信号触发的内部硬件中断。

地址生成方式:中断

地址生成方式:重复操作

注意事项: 利用块重复操作进行循环,是一种零开 销循环。但由于只有一套重复寄存器, 因此块重复操作不能嵌套。 块重复操作可以响应中断。

地址生成方式:硬件复位

5.硬件复位 复位(RS)是一个不可屏蔽的外部中断, 它可以 在任何时候使‘C54x进入一已知状态。 正常操作是上电后RS引脚应至少保持5个时钟 周期的低电平,以确保数据、地址和控制线的 正确配置。 复位后(RS变高电平),处理器从FF80h处取指 , 并开始执行程序。

地址生成方式:分支转移

条件分支转移操作与无条件分支转移操作类似,但仅当 用户规定的一个或多个条件得到满足时才执行。如果 条件满足,就用分支转移指令的第2个字(分支转移地 址)加载PC,并从这个地址继续执行程序。

地址生成方式:分支转移

条件操作中的“条件”

地址生成方式:分支转移

BC[D]的语法为:BC[D] pmad,cond[,cond,[cond]] 其功能是,如果满足给定的条件 ,pmad 值赋给 PC 实现条件转移。若为延迟方式 , 此时紧跟该指令的 两条单字指令或一条双字指令先被取出执行 , 且不 会影响被测试的条件。若条件不 满足 ,PC 加 2, 条 件满足时程序跳到 pmad 地址处。 程序举例:

DSP第四章6概论

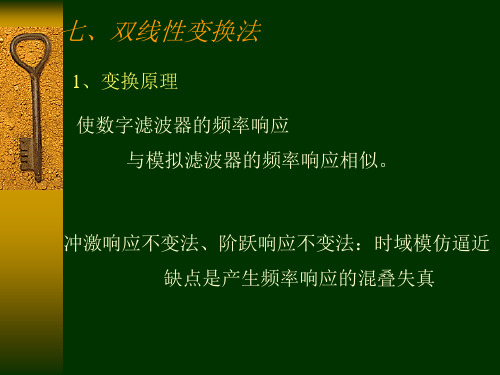

1、变换原理 使数字滤波器的频率响应

与模拟滤波器的频率响应相似。

冲激响应不变法、阶跃响应不变法:时域模仿逼近 缺点是产生频率响应的混叠失真

:[,]

1

:

T

,

T

tg 1T 2

z es1T

tg 1T 2

sin 1T 2

cos 1T 2

j 1T

j 1T

e 2 e 2

2 j j 1T

c tg 1T 2

s

c

1 1

z z

1 1

z cs cs

2、变换常数c的选择

1)低频处有较确切的对应关系: 1

1

c

tg

1T 2

c

1T 2

c 2 T

2)某一特定频率严格相对应: c c

c

c tg

1cT 2

c tg c

2

c

cctg

Байду номын сангаас

c

2

特定频率处频率响应严格相等,可以较准确地 控制截止频率位置

4、优缺点

优点:避免了频率响应的混迭现象

c tg

2 s 平面与 z 平面为单值变换

0 0 0 0

缺点:除了零频率附近, 与 之间严重非线性

1)线性相位模拟滤波器 非线性相位数字滤波器

2)要求模拟滤波器的幅频响应为分段常数型,不 然会产生畸变

分段常数型模拟滤波器 经变换后仍为分段常数 型数字滤波器,但临界 频率点产生畸变

j 1T

e 2 e 2

2

j 1T

j 1T

s1T

s1T

s

j

e2

j 1T

e 2

j 1T

dsp课件

在代码实现完成后,进行代码调试,确保程序的正确性和稳定性。

调试与测试结果分析总结

调试过程

在代码调试完成后,进行系统调试,确保各个模块之间的协调和正 常运行。

测试结果分析

对测试结果进行分析,包括性能测试、功能测试等,找出可能存在 的问题和不足。

总结

根据调试和测试结果,对项目进行总结,包括经验教训、改进方向等 ,为后续的项目提供参考和借鉴。

DSP课件

目录

• DSP概述 • DSP硬件结构与工作原理 • DSP软件编程与开发环境 • 典型应用案例分析 • DSP发展趋势与挑战 • 实践项目设计与实现

01 DSP概述

定义与发展

定义

数字信号处理(Digital Signal Processing,简称DSP)是一门涉及多个学科 的交叉学科,主要研究将模拟信号转换为数字信号,并对数字信号进行各种处 理。

通信信号处理应用

总结词

通信信号处理是数字信号处理的另一个重要应用领域,涉及信号的调制、传输和解调等环节。

详细描述

在通信信号处理中,数字信号处理技术可以用于信号的调制、编码、解调和解码等环节,同时还可以 进行信号特征提取、分类和识别等任务。具体的应用包括移动通信、卫星通信、数字电视和雷达信号 处理等。

未来DSP将进一步提高处理速度和效率,满足更 多复杂应用的需求。

更低的功耗

通过不断优化技术,降低DSP的功耗,延长设备 的使用寿命。

更广泛的应用领域

DSP将在更多领域得到应用,如智能家居、自动 驾驶、医疗保健等。

06 实践项目设计与 实现

项目需求分析与设计思路

明确项目目标

01

在开始实践项目之前,需要明确项目的目标,包括要实现的功

精品课件-DSP技术及应用-第6章

4

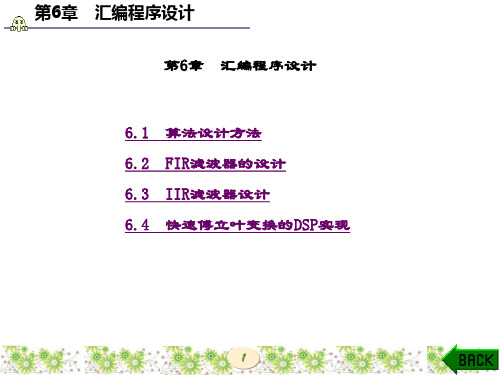

第6章 汇编程序设计

表的偏移地址的计算方法是, 将x=[0~2π)弧度变换到0~N -1之间的整数index。

x' N x 2

index=floor(x′)

(6.2)

则y=sin(x)

y=sin_table(index)

(6.3)

查表法速度快, 但表中两点之间的值需用靠近它们的值

32

第6章 汇编程序设计 第1次运算: src=src+h(0)×x(n), 运算后指针未超边界,

ARy→h+1, ARx→x+1; 第2次运算: src=src+h(1)×x(n-1), 运算后指针未超边

界, ARy→h+2, ARx→ x+2; … 第N次运算: src=src+h(N-1)×x[n-(N-1)], 运算后指

9

第6章 汇编程序设计

(6.5)

10

第6章 汇编程序设计 式(6.5)具有迭代性。 若系数用Q15格式表示, 从最里面的

括号开始计算, 均为乘加(减)运算, 可用C54x的汇编专用指令 快速实现。 余弦等其他函数也可用类似的方法处理。

正弦函数也可用迭代公式(6.6)计算, 但不推荐使用, 因 为它容易产生累加误差。

在程序存储器中定义滤波系数h向量, 首地址设为pmad。 在数据存储器定义一个缓冲区用于存放x序列值, 最新的数据存 放在缓冲区顶部, 最“老”的数据放在底部, 将辅助寄存器指 针ARx初始化并指向底部, 如图6.4所示。

22

第6章 汇编程序设计

图 6.4 线性缓冲区法的数据存储

23

第6章 汇编程序设计 设源累加器src初始化为0, pmad指针每计算一次就自动加1,

中科大操作系统原理与实现课件6_Process_synchronization1

.

.

.

.

.

.

another solution using counting value II

while (true) { /* produce an item and put in nextProduced */ while (count == BUFFER SIZE) ; // do nothing buffer [in] = nextProduced; in = (in + 1) % BUFFER SIZE; count++; }

.

.

.

.

.

.

Bounded-Buffer – Shared-Memory Solution III

Remove() Method

while (true) { while (in == out) ; // do nothing – nothing to consume // remove an item from the buffer item = buffer[out]; out = (out + 1) % BUFFER SIZE; return item; }

操作系统原理与设计

第6章 Processe Synchronization1(进程同步1)

陈香兰

中国科学技术大学计算机学院

2009年10月28日

.

.

.

.

.

.

提纲

Background The Critical-Section Problem Peterson’s Solution Synchronization Hardware TestAndSet Instruction Swap Instruction Semaphores 小结和作业

DSP课件 DSP Lecture6

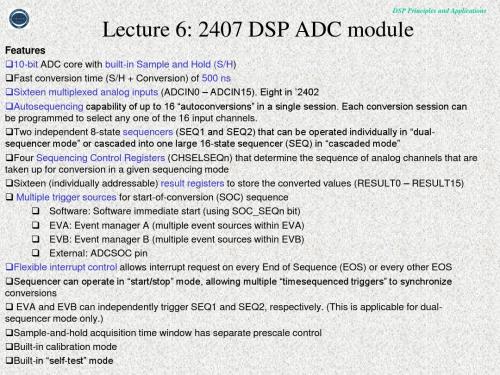

Lecture 6: 2407 DSP ADC module

Features 10-bit ADC core with built-in Sample and Hold (S/H) Fast conversion time (S/H + Conversion) of 500 ns Sixteen multiplexed analog inputs (ADCIN0 – ADCIN15). Eight in ’2402 Autosequencing capability of up to 16 ―autoconversions‖ in a single session. Each conversion session can be programmed to select any one of the 16 input channels. Two independent 8-state sequencers (SEQ1 and SEQ2) that can be operated individually in ―dualsequencer mode‖ or cascaded into one large 16-state sequencer (SEQ) in ―cascaded mode‖ Four Sequencing Control Registers (CHSELSEQn) that determine the sequence of analog channels that are taken up for conversion in a given sequencing mode Sixteen (individually addressable) result registers to store the converted values (RESULT0 – RESULT15) Multiple trigger sources for start-of-conversion (SOC) sequence Software: Software immediate start (using SOC_SEQn bit) EVA: Event manager A (multiple event sources within EVA) EVB: Event manager B (multiple event sources within EVB) External: ADCSOC pin Flexible interrupt control allows interrupt request on every End of Sequence (EOS) or every other EOS Sequencer can operate in ―start/stop‖ mode, allowing multiple ―timesequenced triggers‖ to synchronize conversions EVA and EVB can independently trigger SEQ1 and SEQ2, respectively. (This is applicable for dualsequencer mode only.) Sample-and-hold acquisition time window has separate prescale control Built-in calibration mode Built-in ―self-test‖ mode

dsp第6章 应用程序设计PPT课件

8

第6章 应用程序设计

6.1.1 FIR滤波器的基本结构

在数字滤波器中,FIR滤波器具有如下几个主 要特点:

① FIR滤波器无反馈回路,是一种无条件稳定 系统;

② FIR滤波器可以设计成具有线性相位特性。

2020/7/30

DSP原理及应用

9

2. fir2函数

第6章 应用程序设计

例6.1.1 带通滤波器的特性

设计一个FIR低通滤波器,其设计参数:

滤波器阶数:N=40; 截止频率:wp=0.35,

ws=0.4。

2020/7/30

DSP原理及应用

13

第6章 应用程序设计

6.1.5 FIR滤波器的设计实例

1.由给定的设计参数确定滤波器的系数

根据给定的设计参数,滤波器系数可由MATLAB 中的fir2函数产生,函数调用格式:

若h(n)为实数,且满足偶对称或奇对称的条件, 则FIR滤波器具有线性相位特性。

偶对称:h(n)= h(N-1-n);

奇对称:h(n)= -h(N-1-n)。 偶对称线性相位FIR滤波器的差分方程:

N1 2

y(n)bi[x(ni)x(nN1i)] i0

N——偶数

(6.1.4)

2020/7/30

DSP原理及应用

DSP原理及应用

6

第6章 应用程序设计

6.1.1 FIR滤波器的基本结构

FIR滤波器的结构 :

x(n-1)

x(n)

z-1

z-1

x(n-N+1)

z-1

+

y(n)

bN-1

bN-2

b1

b0

2020/7/30

DSP原理及应用

中科大数字信号处理课件

k

k

中国科学技术大学 42

x (k ) x (k n )

1 2

wei@

x ( n) h( n)

中国科学技术大学

7

1.4 离散时间线性非时变系统

1.4 离散时间线性非时变系统

交换律

x1(n) x2(n) x2(n) x1(n)

系统的稳定性:输入有界→ 输出有界 充要条件

Ω -2Ωs

中国科学技术大学

-Ω s

20

Ωs

2Ωs

wei@

1.2 连续时间信号的离散化

1.2 连续时间信号的离散化

关于取样信号频谱周期延拓的时域理解 考虑一个正弦信号x1(t)= ejΩ1t,对其作周期 为T的取样,

x1(nT ) e j1nT e j1nT e j 2nk e

卷积(和)运算

y (n) T [ x(n)] T [ x(k ) (n k )]

k

k

x(k )T [ (n k )] x ( k ) h( n k )

卷积运算

41 wei@

定义:

x1(n) x 2(n )

信号最高频率 h

中国科学技术大学 31

0

32

n

wei@

1.3 离散时间信号

1.3 离散时间信号

用单位取样序列表达任意信号

常用序列

x ( n)

k

x(k ) (n k )

1 单位阶跃序列 u (n) 0

n0 n0

x(n)

1

0

中国科学技术大学 33 wei@ 中国科学技术大学 34

DSP精品课件(华中科技大学)

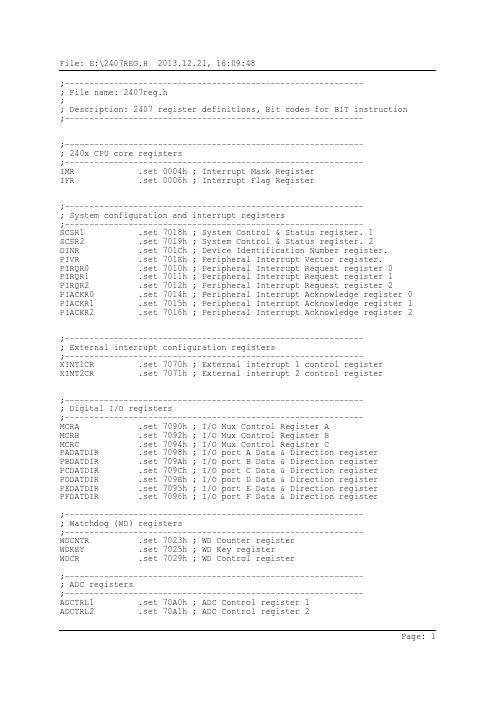

;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; File name: 2407reg.h;; Description: 2407 register definitions, Bit codes for BIT instruction ;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; 240x CPU core registers;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––IMR .set 0004h ; Interrupt Mask RegisterIFR .set 0006h ; Interrupt Flag Register;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; System configuration and interrupt registers;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––SCSR1 .set 7018h ; System Control & Status register. 1SCSR2 .set 7019h ; System Control & Status register. 2DINR .set 701Ch ; Device Identification Number register.PIVR .set 701Eh ; Peripheral Interrupt Vector register. PIRQR0 .set 7010h ; Peripheral Interrupt Request register 0 PIRQR1 .set 7011h ; Peripheral Interrupt Request register 1 PIRQR2 .set 7012h ; Peripheral Interrupt Request register 2 PIACKR0 .set 7014h ; Peripheral Interrupt Acknowledge register 0 PIACKR1 .set 7015h ; Peripheral Interrupt Acknowledge register 1 PIACKR2 .set 7016h ; Peripheral Interrupt Acknowledge register 2 ;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; External interrupt configuration registers;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––XINT1CR .set 7070h ; External interrupt 1 control registerXINT2CR .set 7071h ; External interrupt 2 control register;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; Digital I/O registers;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––MCRA .set 7090h ; I/O Mux Control Register AMCRB .set 7092h ; I/O Mux Control Register BMCRC .set 7094h ; I/O Mux Control Register CPADATDIR .set 7098h ; I/O port A Data & Direction register PBDATDIR .set 709Ah ; I/O port B Data & Direction register PCDATDIR .set 709Ch ; I/O port C Data & Direction register PDDATDIR .set 709Eh ; I/O port D Data & Direction register PEDATDIR .set 7095h ; I/O port E Data & Direction register PFDATDIR .set 7096h ; I/O port F Data & Direction register;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; Watchdog (WD) registers;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––WDCNTR .set 7023h ; WD Counter registerWDKEY .set 7025h ; WD Key registerWDCR .set 7029h ; WD Control register;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; ADC registers;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––ADCTRL1 .set 70A0h ; ADC Control register 1ADCTRL2 .set 70A1h ; ADC Control register 2MAXCONV .set 70A2h ; Maximum conversion channels register CHSELSEQ1 .set 70A3h ; Channel select Sequencing control register 1 CHSELSEQ2 .set 70A4h ; Channel select Sequencing control register 2 CHSELSEQ3 .set 70A5h ; Channel select Sequencing control register 3 CHSELSEQ4 .set 70A6h ; Channel select Sequencing control register 4 AUTO_SEQ_SR .set 70A7h ; Auto–sequence status registerRESULT0 .set 70A8h ; Conversion result register 0RESULT1 .set 70A9h ; Conversion result register 1RESULT2 .set 70Aah ; Conversion result register 2RESULT3 .set 70Abh ; Conversion result register 3RESULT4 .set 70Ach ; Conversion result register 4RESULT5 .set 70Adh ; Conversion result register 5RESULT6 .set 70Aeh ; Conversion result register 6RESULT7 .set 70Afh ; Conversion result register 7RESULT8 .set 70B0h ; Conversion result register 8RESULT9 .set 70B1h ; Conversion result register 9RESULT10 .set 70B2h ; Conversion result register 10RESULT11 .set 70B3h ; Conversion result register 11RESULT12 .set 70B4h ; Conversion result register 12RESULT13 .set 70B5h ; Conversion result register 13RESULT14 .set 70B6h ; Conversion result register 14RESULT15 .set 70B7h ; Conversion result register 15CALIBRATION .set 70B8h ; Calibration result, used to correct; subsequent conversions;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; SPI registers;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––SPICCR .set 7040h ; SPI Config Control registerSPICTL .set 7041h ; SPI Operation Control registerSPISTS .set 7042h ; SPI Status registerSPIBRR .set 7044h ; SPI Baud rate control registerSPIRXEMU .set 7046h ; SPI Emulation buffer registerSPIRXBUF .set 7047h ; SPI Serial receive buffer registerSPITXBUF .set 7048h ; SPI Serial transmit buffer registerSPIDAT .set 7049h ; SPI Serial data registerSPIPRI .set 704Fh ; SPI Priority control register;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; SCI registers;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––SCICCR .set 7050h ; SCI Communication control registerSCICTL1 .set 7051h ; SCI Control register 1SCIHBAUD .set 7052h ; SCI Baud Rate MS byte registerSCILBAUD .set 7053h ; SCI Baud Rate LS byte registerSCICTL2 .set 7054h ; SCI Control register 2SCIRXST .set 7055h ; SCI Receiver Status registerSCIRXEMU .set 7056h ; SCI Emulation Data Buffer registerSCIRXBUF .set 7057h ; SCI Receiver Data buffer registerSCITXBUF .set 7059h ; SCI Transmit Data buffer registerSCIPRI .set 705Fh ; SCI Priority control register;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; Event Manager A (EVA) registers;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––GPTCONA .set 7400h ; GP Timer control register AT1CNT .set 7401h ; GP Timer 1 counter registerT1CMPR .set 7402h ; GP Timer 1 compare registerT1PR .set 7403h ; GP Timer 1 period registerT1CON .set 7404h ; GP Timer 1 control registerT2CNT .set 7405h ; GP Timer 2 counter registerT2CMPR .set 7406h ; GP Timer 2 compare registerT2PR .set 7407h ; GP Timer 2 period registerT2CON .set 7408h ; GP Timer 2 control registerCOMCONA .set 7411h ; Compare control register AACTRA .set 7413h ; Full compare Action control register A DBTCONA .set 7415h ; Dead-band timer control register A CMPR1 .set 7417h ; Full compare unit compare register1 CMPR2 .set 7418h ; Full compare unit compare register2 CMPR3 .set 7419h ; Full compare unit compare register3 CAPCONA .set 7420h ; Capture control register ACAPFIFOA .set 7422h ; Capture FIFO status register ACAP1FIFO .set 7423h ; Capture Channel 1 FIFO TopCAP2FIFO .set 7424h ; Capture Channel 2 FIFO TopCAP3FIFO .set 7425h ; Capture Channel 3 FIFO TopCAP1FBOT .set 7427h ; Bottom reg. of capture FIFO stack 1 CAP2FBOT .set 7428h ; Bottom reg. of capture FIFO stack 2 CAP3FBOT .set 7429h ; Bottom reg. of capture FIFO stack 3 EVAIMRA .set 742Ch ; Group A Interrupt Mask Register EVAIMRB .set 742Dh ; Group B Interrupt Mask Register EVAIMRC .set 742Eh ; Group C Interrupt Mask Register EVAIFRA .set 742Fh ; Group A Interrupt Flag Register EVAIFRB .set 7430h ; Group B Interrupt Flag Register EVAIFRC .set 7431h ; Group C Interrupt Flag Register;––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; Event Manager B (EVB) registers;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––GPTCONB .set 7500h ; GP Timer control register BT3CNT .set 7501h ; GP Timer 3 counter registerT3CMPR .set 7502h ; GP Timer 3 compare registerT3PR .set 7503h ; GP Timer 3 period registerT3CON .set 7504h ; GP Timer 3 control registerT4CNT .set 7505h ; GP Timer 4 counter registerT4CMPR .set 7506h ; GP Timer 4 compare registerT4PR .set 7507h ; GP Timer 4 period registerT4CON .set 7508h ; GP Timer 4 control registerCOMCONB .set 7511h ; Compare control register BACTRB .set 7513h ; Full compare Action control register B DBTCONB .set 7515h ; Dead-band timer control register B CMPR4 .set 7517h ; Full compare unit compare register4 CMPR5 .set 7518h ; Full compare unit compare register5 CMPR6 .set 7519h ; Full compare unit compare register6 CAPCONB .set 7520h ; Capture control register BCAPFIFOB .set 7522h ; Capture FIFO status register BCAP4FIFO .set 7523h ; Capture Channel 4 FIFO TopCAP5FIFO .set 7524h ; Capture Channel 5 FIFO TopCAP6FIFO .set 7525h ; Capture Channel 6 FIFO TopCAP4FBOT .set 7527h ; Bottom reg. of capture FIFO stack 4 CAP5FBOT .set 7527h ; Bottom reg. of capture FIFO stack 5 CAP6FBOT .set 7527h ; Bottom reg. of capture FIFO stack 6 EVBIMRA .set 752Ch ; Group A Interrupt Mask Register EVBIMRB .set 752Dh ; Group B Interrupt Mask Register EVBIMRC .set 752Eh ; Group C Interrupt Mask Register EVBIFRA .set 752Fh ; Group A Interrupt Flag Register EVBIFRB .set 7530h ; Group B Interrupt Flag Register EVBIFRC .set 7531h ; Group C Interrupt Flag Register;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; CAN registers;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––CANMDER .set 7100h ; CAN Mailbox Direction/Enable register CANTCR .set 7101h ; CAN Transmission Control registerCANRCR .set 7102h ; CAN Recieve Control registerCANMCR .set 7103h ; CAN Master Control registerCANBCR2 .set 7104h ; CAN Bit Config register 2CANBCR1 .set 7105h ; CAN Bit Config register 1CANESR .set 7106h ; CAN Error Status registerCANGSR .set 7107h ; CAN Global Status registerCANCEC .set 7108h ; CAN Trans and Rcv Err countersCANIFR .set 7109h ; CAN Interrupt Flag RegisterCANIMR .set 710ah ; CAN Interrupt Mask RegisterCANLAM0H .set 710bh ; CAN Local Acceptance Mask MBX0/1CANLAM0L .set 710ch ; CAN Local Acceptance Mask MBX0/1CANLAM1H .set 710dh ; CAN Local Acceptance Mask MBX2/3CANLAM1L .set 710eh ; CAN Local Acceptance Mask MBX2/3CANMSGID0L .set 7200h ; CAN Message ID for mailbox 0 (lower 16 bits) CANMSGID0H .set 7201h ; CAN Message ID for mailbox 0 (upper 16 bits) CANMSGCTRL0 .set 7202h ; CAN RTR and DLCCANMBX0A .set 7204h ; CAN 2 of 8 bytes of Mailbox 0CANMBX0B .set 7205h ; CAN 2 of 8 bytes of Mailbox 0CANMBX0C .set 7206h ; CAN 2 of 8 bytes of Mailbox 0CANMBX0D .set 7207h ; CAN 2 of 8 bytes of Mailbox 0CANMSGID1L .set 7208h ; CAN Message ID for mailbox 1 (lower 16 bits) CANMSGID1H .set 7209h ; CAN Message ID for mailbox 1 (upper 16 bits) CANMSGCTRL1 .set 720Ah ; CAN RTR and DLCCANMBX1A .set 720Ch ; CAN 2 of 8 bytes of Mailbox 1CANMBX1B .set 720Dh ; CAN 2 of 8 bytes of Mailbox 1CANMBX1C .set 720Eh ; CAN 2 of 8 bytes of Mailbox 1CANMBX1D .set 720Fh ; CAN 2 of 8 bytes of Mailbox 1CANMSGID2L .set 7210h ; CAN Message ID for mailbox 2 (lower 16 bits) CANMSGID2H .set 7211h ; CAN Message ID for mailbox 2 (upper 16 bits) CANMSGCTRL2 .set 7212h ; CAN RTR and DLCCANMBX2A .set 7214h ; CAN 2 of 8 bytes of Mailbox 2CANMBX2B .set 7215h ; CAN 2 of 8 bytes of Mailbox 2CANMBX2C .set 7216h ; CAN 2 of 8 bytes of Mailbox 2CANMBX2D .set 7217h ; CAN 2 of 8 bytes of Mailbox 2CANMSGID3L .set 7218h ; CAN Message ID for mailbox 3 (lower 16 bits) CANMSGID3H .set 7219h ; CAN Message ID for mailbox 3 (upper 16 bits) CANMSGCTRL3 .set 721Ah ; CAN RTR and DLCCANMBX3A .set 721Ch ; CAN 2 of 8 bytes of Mailbox 3CANMBX3B .set 721Dh ; CAN 2 of 8 bytes of Mailbox 3CANMBX3C .set 721Eh ; CAN 2 of 8 bytes of Mailbox 3CANMBX3D .set 721Fh ; CAN 2 of 8 bytes of Mailbox 3CANMSGID4L .set 7220h ; CAN Message ID for mailbox 4 (lower 16 bits) CANMSGID4H .set 7221h ; CAN Message ID for mailbox 4 (upper 16 bits) CANMSGCTRL4 .set 7222h ; CAN RTR and DLCCANMBX4A .set 7224h ; CAN 2 of 8 bytes of Mailbox 4CANMBX4B .set 7225h ; CAN 2 of 8 bytes of Mailbox 4CANMBX4C .set 7226h ; CAN 2 of 8 bytes of Mailbox 4CANMBX4D .set 7227h ; CAN 2 of 8 bytes of Mailbox 4CANMSGID5L .set 7228h ; CAN Message ID for mailbox 5 (lower 16 bits) CANMSGID5H .set 7229h ; CAN Message ID for mailbox 5 (upper 16 bits) CANMSGCTRL5 .set 722Ah ; CAN RTR and DLCCANMBX5A .set 722Ch ; CAN 2 of 8 bytes of Mailbox 5CANMBX5B .set 722Dh ; CAN 2 of 8 bytes of Mailbox 5CANMBX5C .set 722Eh ; CAN 2 of 8 bytes of Mailbox 5CANMBX5D .set 722Fh ; CAN 2 of 8 bytes of Mailbox 5; Code security module (CSM) registers (Data memory)KEY3 .set 77F0h ; High word of the 64-bit KEY registerKEY2 .set 77F1h ; Third word of the 64-bit KEY registerKEY1 .set 77F2h ; Second word of the 64-bit KEY register KEY0 .set 77F3h ; Low word of the 64-bit KEY register; Code security module (CSM) registers (Program memory)PWL3 .set 0040h ; High word of the 64–bit passwordPWL2 .set 0041h ; Third word of the 64–bit passwordPWL1 .set 0042h ; Second word of the 64–bit password PWL0 .set 0043h ; Low word of the 64–bit password;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; I/O space mapped registers;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––WSGR .set 0FFFFh ; Wait-State Generator Control register FCMR .set 0FF0Fh ; Flash control mode register;––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––; Bit codes for Test bit instruction (BIT) (15 Loads bit 0 into TC) ;–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––BIT15 .set 0000h ; Bit Code for 15BIT14 .set 0001h ; Bit Code for 14BIT13 .set 0002h ; Bit Code for 13BIT12 .set 0003h ; Bit Code for 12BIT11 .set 0004h ; Bit Code for 11BIT10 .set 0005h ; Bit Code for 10BIT9 .set 0006h ; Bit Code for 9BIT8 .set 0007h ; Bit Code for 8BIT7 .set 0008h ; Bit Code for 7BIT6 .set 0009h ; Bit Code for 6BIT5 .set 000Ah ; Bit Code for 5BIT4 .set 000Bh ; Bit Code for 4BIT3 .set 000Ch ; Bit Code for 3BIT2 .set 000Dh ; Bit Code for 2BIT1 .set 000Eh ; Bit Code for 1BIT0 .set 000Fh ; Bit Code for 0。

DSP入门培训PPT资料18页

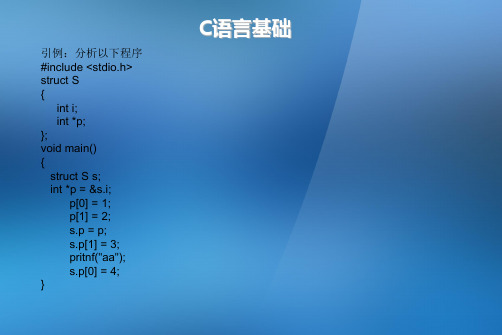

三、DSP中C表达式与基本语句

1、if语句 (1)整型变量与零值比较

应当将整型变量用“==”或“!=”直接与0比较。假设整型变量的名字为value, 它与零值比较的标准if 语句如下:

if (value == 0) if (value != 0) 不可模仿布尔变量的风格而写成 if (value) // 会让人误解value是布尔变量 if (!value)

三、DSP中C语言的关键字

意义 声明自动变量,缺省时编译器一般默认为auto 声明整型变量 声明双精度变量 声明长整型变量 声明字符型变量 声明浮点型变量 声明短整型变量 声明有符号类型变量 声明无符号类型变量 声明结构体变量 声明联合数据类型 声明枚举类型 声明静态变量 用于开关语句 开关语句分支 开关语句中的“其他”分支 跳出当前循环 声明寄存器变量 用以给数据类型取别名(当然还有其他作用)

优秀PPT下载:1ppt/xiazai/ PPT教程: 1ppt/powerpoint/

{ Word教程: 1ppt/word/

资料下载:1ppt/ziliao/ PPT课件下载:1ppt/kejian/

Excel教程:1ppt/excel/

范文下载:1ppt/fanwen/

int i;

int *p;

if ((x>=-EPSINON) && (x<=EPSINON)) 其中EPSINON是允许的误差(即精度)。

三、表达式与基本语句

2、循环语句的效率 C++/C循环语句中,for语句使用频率最高,while语句其次,do语句很少用。

提高循环体效率的基本办法是降低循环体的复杂性。

例子: for (row=0; row<100; row++) {

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

中国科学技术大学

10

wei@

6.1

线性相位下FIR滤波器的频率特性

⑷ h(n) 奇对称,N 偶数

H (ω )

6.1

线性相位下FIR滤波器的频率特性

Impulse Response 30 10 20 Type-4 Amplitude Response

1 H (ω ) = ∑ d (n )sin ω n − 2 n =0

w(n)

0.1 0 -0.1

0.5

w(n) 0 20 40 60 n Actual Impulse Response

0 -0.2

0.5

0

20 40 60 n Actual Impulse Response

0

0

20 40 60 n Magnitude Response in dB

-0.4

0

0

20 40 60 n Magnitude Response in dB

N 奇数 h (n ) 镜像反对称 N 偶数

中国科学技术大学 4 wei@

(偶对称) 群延迟均为 τ =

中国科学技术大学

(奇对称)

wei@

6.1

线性相位下FIR滤波器的频率特性

6.1

线性相位下FIR滤波器的频率特性

Impulse Response 10 5 h(n) Hr 0 -5 0 5 n a(n) coefficients 10 20 10 0 -10 -20 Type-1 Amplitude Response

( )

ω ≤ ωc

其他

N 的 FIR, ① 把hd(n)移动α = N − 1 个采样点(设N为奇数)

hd ( n ) =

1 2π

∫ω e

−

c

ωc

dω =

sin ωc n π n

ˆ (n ) ⋅ W (n ) ② 截取N个点,得到 h (n ) = h d R

1

Hamming窗,低通

中国科学技术大学 25 wei@ 中国科学技术大学

Blackman窗,带通

26 wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

Ideal Impulse Response 1 0.6 hd(n) w(n) 0.4 0.2 0 -0.2 0 20 30 40 n Actual Impulse Response 10 0 0 10 20 30 40 n Magnitude Response in dB Kaiser Window

N 2

0

π

2π

ω

5 h(n) Hr 0 5 n d(n) coefficients 10 Imaginary Part 5 d(n) 0 -5 0 5 n 10 1 0.5 0 -0.5 -1 -1 0 Real Part 1 11 10 10 0 -10 0 -5

0

0.5 frequency in pi units

0.5

6.3

频率抽样设计方法

0.6 h(n) 0.4 0.2 0 -0.2 0 10 20 n 30 40 Decibels

23

wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

Ideal Impulse Response 0.3 0.2 hd(n) 1 Hamming W indow

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

Ideal Impulse Response 0.4 0.2 hd(n) 1 Blackman Window

θ

18

θ

− 2π N 2π N

wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

① 因为截短,产生过渡带,宽度为窗函数的 主瓣宽度。对矩形窗, ∆ω = 4π

N

θ

H (ω ) H (0 )

肩峰值

② 增加N,可使过渡带变得陡峭,但对一个 固定的窗函数不能改变肩峰值大小。 Gibbs效应。

0 ≤ n ≤ N −1 1 矩形窗 WR (n ) = 其他, 0 sin ω c (n − α ) , n = 0, ..., N −1 即 h(n ) = π (n − α )

中国科学技术大学 16 wei@

ˆ (n ) = h (n − α ) = sin ω c (n − α ) h d d π (n − α )

0.3 0.2 Decibels

0

0.4 Decibels 0 20 40 n 60 0.2

0

h(n)

0.1 0 -0.1

50

h(n)

60

0 -0.2

0

20 n

40

60

0

0.2 0.3 frequency in pi units

1

-0.4

0

0.2 0.35 0.65 0.8 frequency in pi units

6.1

线性相位下FIR滤波器的频率特性

Impulse Response 40 10 Type-2 Amplitude Response

⑵ h(n) 偶对称,N 偶数

H (ω )

1 H (ω ) = ∑ b(n ) cos ω n − 2 n =0

N 2

ω

π

2π

5 h(n) 0 -5 0 5 10 n b(n) coefficients Hr

0

N −1 n = 1, 2, ... , 2

0.5 frequency in pi units

1

10

1 0.5 0 -0.5 -1 0 5 n 10 -1 0 Real Part 1 10

H(ω)关于 0, π, 2π奇对称 必有H(0)=H(π)=H( 2π)=0,带通

中国科学技术大学 9 wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

二、窗函数的选择 过渡带的宽度:与窗函数的主瓣宽度有关 肩峰值大小:与窗函数的旁瓣大小有关

0 -1 0 frequency in pi units M = 51 1

0 -1 0 frequency in pi units M = 101 1

Integrated Amplitude Response

6 FIR数字滤波器设计

6.1

线性相位下FIR滤波器的频率特性

中国科学技术大学

1

wei@

中国科学技术大学

2

wei@

6.1

线性相位下FIR滤波器的频率特性

6.1

线性相位下FIR滤波器的频率特性

在线性相位条件下, h(n ) = ± h( N − 1 − n )

20

0

-20

0

0.5 frequency in pi units

1

10

1 Imaginary Part 0.5 0 -0.5 -1 0 5 n 10 -1 0 Real Part 1 11

N b(n ) = 2h − n 2

N n = 1, 2, ... , 2

5 b(n) 0 -5

1

N N 2, ... , d (n ) = 2h − n n = 1, 2 2 H(ω)关于π偶对称,

必有H(0)=H( 2π)=0,高通

中国科学技术大学 11 wei@

中国科学技术大学

12

wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

常用窗函数 主瓣 矩形 4π/N 三角 8π/N Hanning 8π/N Hamming 8π/N Blackman 12π/N

中国科学技术大学

旁瓣 -13dB -25 -32 -42 -57

24

最小阻带衰减 -21dB -25 -44 -53 -74

wei@

中国科学技术大学

2

−∞ < n < ∞

hd(n)为无限时宽

中国科学技术大学 15 wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

hd (n )

n

h(n)的频率响应,频域卷积

H e jω =

( )

1 2π

π ˆ (e θ )W [e (ω θ ) ] dθ ∫πH

⑶ h(n) 奇对称,N 奇数

H (ω )

H (ω ) = ∑ c(n )sin ω n

n =0

h(n)

N −1 2

0

π

2π

ω

0 -5 0 5 n c(n) coefficients 10

5 c(n) 0 -5

Imaginary Part

N −1 c (n ) = 2h − n 2

1

Integrated Amplitude Response

1

选择窗函数的原则: ① 主瓣窄,使过渡带陡峭 ② 旁瓣低,减小肩峰和余振

0 -1 0 frequency in pi units 1

0 -1 0 frequency in pi units 1

中国科学技术大学

21

wei@

− jω n

故, H(ejω)对Hd(ejω)的逼近程度随截取长度而增加

中国科学技术大学 13 wei@ 中国科学技术大学 14 wei@

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

6.2

傅立叶级数法设计FIR滤波器(窗函数法)

理想低通的逼近

1 H d e jω = 0

一、基本设计方法 基于频域特性的解析表达与窗函数 给定Hd(ejω)导出hd(n)

6.2 傅立叶级数法设计FIR滤波器(窗函数法)