QFN元件生产过程及注意事项

QFN焊盘设计和工艺指南

QFN焊盘设计和工艺指南(湖州生力电子有限公司沈新海)一、基本介绍QFN(Quad Flat No Lead)是一种相对比较新的IC 封装形式,但由于其独特的优势,其应用得到了快速的增长。

QFN 是一种无引脚封装,它有利于降低引脚间的自感应系数,在高频领域的应用优势明显。

QFN 外观呈正方形或矩形,大小接近于CSP,所以很薄很轻。

元件底部具有与底面水平的焊端,在中央有一个大面积裸露焊端用来导热,围绕大焊端的外围四周有实现电气连接的I/O 焊端,I/O 焊端有两种类型:一种只裸露出元件底部的一面,其它部分被封装在元件内;另一种焊端有裸露在元件侧面的部分。

QFN 采用周边引脚方式使PCB 布线更灵活,中央裸露的铜焊端提供了良好的导热性能和电性能。

这些特点使QFN 在某些对体积、重量、热性能、电性能要求高的电子产品中得到了重用。

由于QFN 是一种较新的IC 封装形式,IPC-SM-782等PCB设计指南上都未包含相关内容,本文可以帮助指导用户进行QFN 的焊盘设计和生产工艺设计。

但需要说明的是本文只是提供一些基本知识供参考,用户需要在实际生产中不断积累经验,优化焊盘设计和生产工艺设计方案,以取得令人满意的焊接效果。

二、QFN封装描述QFN 的外形尺寸可参考其产品手册,它符合一般工业标准。

QFN 通常采用JEDECMO-220系列标准外形,在焊盘设计时可以参考这些外形尺寸(示例如图1)。

图 1 QFN元件三维剖视图和实物外观三、通用设计指南QFN的中央裸焊端和周边I/O焊端组成了平坦的铜引线结构框架,再用模铸树脂将其浇铸在树脂里固定,底面露出的中央裸焊端和周边I/O 焊端,均须焊接到PCB上。

PCB 焊盘设计应该适应工厂的实际工艺能力,以求取得最大的工艺窗口,得到良好的高可靠性焊点。

需要说明的是中央裸焊端的焊接,通过“锚”定元件,不仅可以获得良好的散热效果,还可以增强元件的机械强度,有利于提高周边I/O 焊端的焊点可靠性。

QFN与BGA生产注意事项

元件焊接注意事项

焊接温度

BGA焊接温度应根据焊锡膏的特性进行选择,通常为230-250℃, 并确保温度均匀分布。

焊接时间

焊接时间不宜过长,以免造成元件损坏或热损伤,通常为3-5秒。

焊锡量

焊锡量要适中,过多或过少都会影响焊接质量,应控制焊锡量在合 适的范围内。

元件放置与固定

元件放置

BGA元件应按照设计要求放置在 PCB上,确保位置准确,避免错 位和偏移。

02

QFN生产注意事项

生产环境要求

01

02

03

温度控制

QFN器件对温度较为敏感, 生产车间应保持恒温,避 免温度波动影响焊接质量。

湿度调节

保持适当的湿度,以防止 静电和灰尘对生产造成不 良影响。

洁净度要求

生产环境应保持洁净,减 少尘埃和污染物对QFN器 件的污染。

元件焊接注意事项

选择合适的焊料

元件固定

采用合适的固定方式,如通过钢 网或吸嘴将元件放置在PCB上, 并确保元件与PCB紧密贴合,防 止元件脱落或移位。

焊接质量检测

外观检查

通过目视或显微镜检查焊接外观,检查 是否存在虚焊、冷焊、气孔等焊接缺陷。

X光检测

通过X光检测技术对焊接内部进行检 测,检查是否存在焊接不良、焊锡填

充不足等问题。

防止元件损坏

元件损坏原因

在生产过程中,由于操作不当、材料 缺陷等原因可能导致QFN与BGA元件 损坏。

预防措施

加强来料检验,确保材料质量合格; 规范操作流程,确保生产过程中不发 生碰撞、划伤等情况;定期检查设备, 确保设备运行正常。

05

QFN与BGA差异注意事项

QFN特殊要求

1 2

封装尺寸

qfn封装流程

qfn封装流程QFN封装流程QFN(Quad Flat No-leads)封装是一种常见的集成电路封装技术,它具有尺寸小、焊接可靠性高等优点,在现代电子工业中得到广泛应用。

本文将介绍QFN封装的流程,并探讨其在电子封装领域的重要性。

一、QFN封装的概述QFN封装是一种无引线封装技术,其特点是焊盘位于芯片的底部,通过焊盘与印刷电路板(PCB)上的焊盘连接。

相比传统的封装技术,QFN封装具有更小的尺寸和更好的散热性能,适用于高密度集成电路的封装需求。

二、QFN封装的流程1. 芯片制备:首先,从硅片上切割出芯片,并进行测试和筛选。

然后,将芯片进行金属化处理,以便在后续的封装过程中与焊盘连接。

2. 焊盘制备:在PCB上制作焊盘,通常采用镀金或镀银的方式,以提高焊接可靠性和导电性能。

3. 芯片定位:将芯片精确地定位在PCB上的焊盘区域,通常采用自动化设备完成。

4. 焊接:使用热板或热风枪等设备,将芯片和焊盘加热至一定温度,然后利用焊料的润湿性将芯片与焊盘连接。

5. 清洗:清洗封装好的芯片,去除焊接过程中产生的杂质和污染物。

6. 芯片测试:对封装好的芯片进行功能性测试和可靠性测试,以确保其符合规定的电气性能要求。

7. 封装检验:对封装好的芯片进行外观检验和尺寸检验,以确保封装质量符合标准。

8. 封装包装:将封装好的芯片进行包装,通常采用真空包装或干燥包装,以保护芯片免受潮湿和静电等环境因素的影响。

三、QFN封装的重要性QFN封装在电子封装领域具有重要的应用价值。

首先,由于其尺寸小,QFN封装可以实现更高的元器件集成度,从而提高电路板的布局密度和系统性能。

其次,QFN封装的焊接可靠性高,能够有效减少因焊接引起的电路故障和失效。

此外,QFN封装还具有良好的散热性能,能够有效降低芯片的工作温度,提高系统的稳定性和可靠性。

四、结论QFN封装是一种常见且重要的集成电路封装技术,通过精确的制备和封装流程,能够实现小尺寸、高可靠性和良好的散热性能。

qfn化工工艺流程

qfn化工工艺流程QFN(Quad Flat No-Lead)是一种常见的表面贴装封装技术,广泛应用于集成电路领域。

下面将介绍QFN化工工艺流程,包括设计、制造、封装和测试等步骤。

首先,QFN的设计工艺流程包括电路设计和封装设计两个方面。

电路设计通过软件仿真和综合技术,确定芯片的电路结构和电器参数。

封装设计则是根据芯片的尺寸、引脚排列和焊盘布局等要求,设计QFN封装的外形和内部结构。

其次,制造工艺流程主要包括基片制备、电极制备、扩散、金属化和封装等步骤。

首先,基片制备包括晶圆制备、切割和抛光等工艺,用于制作芯片的基础材料。

然后,通过电极制备工艺将金属粉末与聚合物混合,并制成形状适配的电极片。

接下来,通过扩散工艺,将芯片的电极片与基片相结合,形成半导体结构。

随后,通过金属化工艺,在芯片的关键电极上涂覆金属层,用于连接内部电路。

最后,通过封装工艺将芯片封装在QFN封装中,形成成品。

第三,QFN的焊接工艺流程主要包括PCB制备、焊盘制备、焊接和检测等步骤。

首先,PCB制备包括基板的选材、切割和表面处理等工艺。

然后,通过焊盘制备工艺,在PCB上制造出与QFN封装引脚匹配的焊盘位置。

接下来,通过焊接工艺将QFN封装与PCB焊接在一起,形成电气和力学连接。

最后,通过检测工艺对焊接质量和尺寸进行验证,确保焊接质量符合要求。

最后,QFN的测试工艺流程主要包括电性能测试、物理性能测试和可靠性测试等步骤。

电性能测试通过测试设备对芯片的电器性能进行测试,包括电流、电压和频率等参数。

物理性能测试通过设备或技术手段对封装结构的机械性能进行测试,包括强度、导热性和耐温性等指标。

可靠性测试通过长时间高负载运行或模拟环境条件对QFN封装的可靠性进行测试,包括抗压力、抗震动和抗湿度等指标。

综上所述,QFN化工工艺流程是一个复杂的过程,包括设计、制造、封装和测试等多个环节。

只有通过精细的工艺控制和严格的质量检测,才能保证QFN封装的质量和可靠性。

QFN

摘要:QFN封装(Quard Flat No-lead方形扁平无引脚封装)具有良好的电和热性能、体积小、重量轻,其应用正在快速增长。

QFN的封装和CSP有些相似,但元件底部没有焊球,与PCB的电气和机械连接是通过PCB焊盘上印刷焊膏、过回流焊形成的焊点来实现的,对PCB焊盘设计和表面贴装工艺提出了一些新的要求。

印刷网板设计、焊后检查、返修等都是表面贴装过程中所应该关注的。

概述QFN是一种无引脚封装,呈正方形或矩形,封装底部具有与底面水平的焊盘,在中央有一个大面积裸露焊盘用来导热,围绕大焊盘的封装外围四周有实现电气连接的导电焊盘。

导电焊盘有两种类型:一种只裸露出封装底部的一面,其它部分被封装在元件内;另一种焊盘有裸露在封装侧面的部分(图1)。

与PCB的电气连接是通过在PCB焊盘上印刷焊膏、过回流焊形成焊点,将QFN焊盘和PCB上相应的焊盘连接起来实现的。

缩短了连接距离的导电焊盘可以提供良好的电性能;中央大的热焊盘可以将封装体的热量迅速传导到PCB上,具有良好的热性能。

QFN封装具有良好的电和热性能、体积小、重量轻,成为了许多新的应用的一种理想的选择。

在印制板上,封装的大面积裸露焊盘相对应的热焊盘,其尺寸设计与封装的大面积裸露焊盘尺寸相同;导电焊盘相对应的四周焊盘,其尺寸也和导电焊盘尺寸设计相似,但向外稍微长一些。

印刷网板设计能否得到完美、可靠的焊点,印刷网板设计是关键的第一步。

四周焊盘网板开口尺寸和网板的厚度的选取有直接的关系,一般较厚的网板可以采用开口尺寸略小于焊盘尺寸的设计,而较薄的网板开口尺寸可设计到1:1。

关键是面积比要符合IPC-7525有关的规定。

推荐使用激光制作开口并经过电抛光处理的网板。

如果网板厚度>150um,则可考虑采用电铸的网板。

在实际生产中,分别设计试验了150um和130um 厚度两种网板,使用AOI记录了印制板上3种不同封装尺寸的QFN器件(Type A、B和C)的焊膏印刷情况。

qfn封装管脚太近做不了阻焊桥

qfn封装管脚太近做不了阻焊桥QFN封装是一种常见的电子封装方式,其英文全称为Quad Flat No-lead,意为四侧无引脚扁平封装。

这种封装方式具有体积小、重量轻、传热性能好等优点,因此在现代电子设备中得到了广泛应用。

然而,QFN封装在制造和使用过程中也存在一些问题,其中之一就是管脚太近导致无法进行阻焊桥处理。

下面将详细说明这个问题及其产生的原因和解决方案。

一、QFN封装的特点QFN封装是一种常见的电子封装方式,它具有以下特点:1.四侧无引脚:QFN封装的引脚位于封装底部,呈矩阵排列,与PCB板连接时只能通过焊接方式实现。

2.扁平结构:QFN封装的形状为扁平,高度较低,因此可以方便地实现PCB板的微型化设计。

3.传热性能好:由于QFN封装的底部具有较大的传热面积,因此其传热性能较好,有利于电子设备的散热。

4.重量轻:QFN封装的重量较轻,因此可以减轻整个电子设备的重量。

二、阻焊桥的作用阻焊桥是PCB板制作过程中常用的一种工艺手段,其作用是在PCB板的焊盘之间通过涂覆阻焊剂来防止焊接时焊料流动。

阻焊桥的主要作用包括:1.防止焊料流动:在焊接过程中,焊料可能会因为温度变化而流动,导致焊点形状发生变化,影响焊接质量。

通过阻焊桥可以有效地防止焊料流动,保持焊点形状稳定。

2.提高焊接质量:阻焊桥可以有效地防止虚焊、短路等焊接缺陷的产生,提高焊接质量。

3.提高电路稳定性:阻焊桥可以保护PCB板上的电路免受外界环境的干扰和破坏,提高电路的稳定性。

三、QFN封装管脚太近导致阻焊桥无法制作的问题在制作PCB板时,如果使用QFN封装,可能会因为管脚太近而无法制作阻焊桥。

具体来说,问题产生的原因包括:1.引脚间距过近:QFN封装的引脚间距通常很近,有时甚至只有几个毫米。

如果在这个距离内制作阻焊桥,可能会导致阻焊剂无法完全覆盖焊盘,影响焊接质量。

2.焊盘尺寸过小:QFN封装的焊盘尺寸通常比较小,如果在这个尺寸内制作阻焊桥,可能会导致阻焊剂无法均匀涂覆在焊盘表面,影响焊接质量。

qfn工艺流程

qfn工艺流程

QFN(Quad Flat Non-leaded)封装工艺流程主要包括以下步骤:

1. 芯片准备:包括测试、切割和排序,以及放置在适当的载体上。

2. 基板准备:清洁电路板,确保表面平整、无污垢和残留物。

必要时,进行表面处理,如金属化和防焊处理。

3. 芯片粘贴:使用粘贴剂将芯片粘贴在基板上,确保芯片准确地对位。

4. 固化:将芯片和基板送入烘箱或其他固化设备中,使粘贴剂在适当的温度和时间下固化,确保芯片牢固地附着在基板上。

5. 焊接:将固化的芯片和基板送入焊接设备中,通常采用表面贴装技术(SMT),通过热风枪或回流焊炉进行焊接。

焊膏熔化,将芯片的引脚与基板上的焊盘连接。

6. 清洗和检查:清洗旨在去除焊接过程中产生的残留物和污垢,检查用于验证焊接质量、引脚连接性和任何可能的缺陷。

7. 封装后工艺:根据需要,进行一些附加的封装后工艺步骤,如测试、标记和包装。

这些步骤旨在验证芯片的功能、进行标识和保护封装后的芯片。

以上就是QFN工艺流程的主要步骤,每个步骤都有其特定的作用和要求,需要严格控制以保证产品质量。

QFN封装工艺PPT

Final Visual Inspection Packing

IC封裝材料

Leadf rame Copper/Alloy

Subs trate

Solde

r

Solder Alloy

balls

Gold wire

Gold

BT Resin

Epoxy (Silver

Molding Epoxy compound

Chip Substrate

(c) System encapsulated

Solder flip chip interconnect systems

Filled Epoxy Encapsulant

Silicon Chip

FR-4 Carrier

Package Types and Applications封裝類型及應用

根據天下雜誌2002 的100大企業調查,企業平均獲利水準約在1.3%,創 下十七年來的最低,正式宣告微利化時代的來臨。一般在開始規模約在 50 部銲線機,其投資額約在十億左右(含廠房與設施)。產品從雙排腳到 平面四面腳/膠帶線/球陣列/影像感應/薄膜晶體,因大部份同質性均高, 造成價格互相之間的排擠效應。而數個集團如安可、日月光、矽品,亦 夾其大公司、資本雄厚的優勢,試圖合併其他較小的公司,以利其價格 之主宰。同時大公司亦佔有〝量大〞的優勢,故與廠商的議價能力相當 高,如日月光可依據價格自由選擇廠商或更換廠商。而與購買者議價能 力,則受幾家大廠的殺價狀況所影響,致使購買者的轉換成本加大。而 未來低腳數球陣列產品亦漸漸被QFN產品所取代 。

QFN PACKAGING

QUAD FLAT NO-LEAD PACKAGE

封裝技術簡介

QFN(LPCC)封装PCB设计与装配指导

QFN(LPCC)封装PCB设计与装配指导QFN (LPCC)封装简介QFN封装具有成本低、表贴、塑封、热阻低,并能够应用于较高频段的特点。

这种封装的工业标准是“JEDEC MO-220”,可进一步描述为“散热增强型,无引线,且管脚间距极小的扁平、方形塑料封装”。

Hittite公司有很多采用QFN封装的标准产品,最高工作频率可达16GHz。

为了成功的将这类器件应用产品设计中,必须遵循正确的PCB设计、加工、以及装配方法。

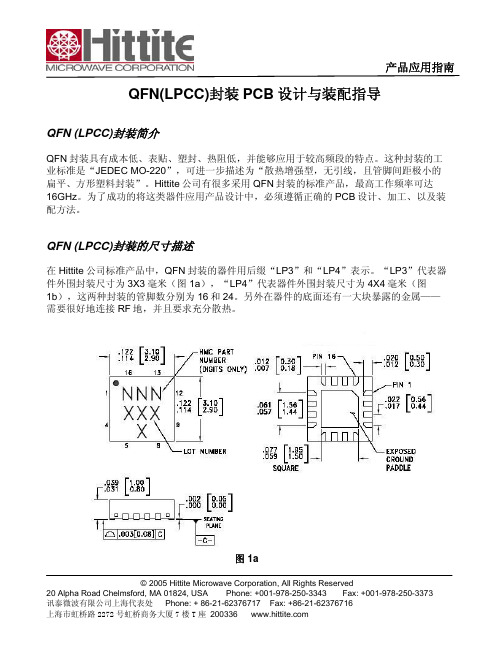

QFN (LPCC)封装的尺寸描述在Hittite公司标准产品中,QFN封装的器件用后缀“LP3”和“LP4”表示。

“LP3”代表器件外围封装尺寸为3X3毫米(图 1a),“LP4”代表器件外围封装尺寸为4X4毫米(图1b),这两种封装的管脚数分别为16和24。

另外在器件的底面还有一大块暴露的金属——需要很好地连接RF地,并且要求充分散热。

图 1a© 2005 Hittite Microwave Corporation, All Rights Reserved图 1bLP3 与 LP4 封装说明:1. 封装的主体材质——通过低应力注入形成的二氧化硅与硅相互浸透的塑模。

2. 管脚引线与背面接地焊盘的材料——铜合金。

3. 管脚引线与背面接地焊盘的镀层——锡 / 铅焊料。

4. 尺寸单位标注说明——英寸 [毫米]。

5. 管脚间距的容差为非累加。

6. 焊盘长度的最大毛刺尺寸为0.15mm,焊盘厚度的最大毛刺尺寸为0.05mm。

7. 封装的外形扭曲尺寸小于0.05mm。

8. 所有接地的引线与焊盘必须与PCB上RF地可靠连接。

QFN封装的PCB阻焊层与焊盘样式设计由于QFN封装管脚密集且背面又有一块接地的大焊盘,所以在PCB设计中应该格外注意焊盘的几何尺寸。

为了防止短路,在信号线与地之间必需有阻焊剂。

阻焊剂网格的最小尺寸为© 2005 Hittite Microwave Corporation, All Rights Reserved© 2005 Hittite Microwave Corporation, All Rights Reserved0.010英寸[0.25mm]。

QFN(LPCC)封装PCB设计与装配指导

QFN(LPCC)封装PCB设计与装配指导QFN (LPCC)封装简介QFN封装具有成本低、表贴、塑封、热阻低,并能够应用于较高频段的特点。

这种封装的工业标准是“JEDEC MO-220”,可进一步描述为“散热增强型,无引线,且管脚间距极小的扁平、方形塑料封装”。

Hittite公司有很多采用QFN封装的标准产品,最高工作频率可达16GHz。

为了成功的将这类器件应用产品设计中,必须遵循正确的PCB设计、加工、以及装配方法。

QFN (LPCC)封装的尺寸描述在Hittite公司标准产品中,QFN封装的器件用后缀“LP3”和“LP4”表示。

“LP3”代表器件外围封装尺寸为3X3毫米(图 1a),“LP4”代表器件外围封装尺寸为4X4毫米(图1b),这两种封装的管脚数分别为16和24。

另外在器件的底面还有一大块暴露的金属——需要很好地连接RF地,并且要求充分散热。

图 1a© 2005 Hittite Microwave Corporation, All Rights Reserved图 1bLP3 与 LP4 封装说明:1. 封装的主体材质——通过低应力注入形成的二氧化硅与硅相互浸透的塑模。

2. 管脚引线与背面接地焊盘的材料——铜合金。

3. 管脚引线与背面接地焊盘的镀层——锡 / 铅焊料。

4. 尺寸单位标注说明——英寸 [毫米]。

5. 管脚间距的容差为非累加。

6. 焊盘长度的最大毛刺尺寸为0.15mm,焊盘厚度的最大毛刺尺寸为0.05mm。

7. 封装的外形扭曲尺寸小于0.05mm。

8. 所有接地的引线与焊盘必须与PCB上RF地可靠连接。

QFN封装的PCB阻焊层与焊盘样式设计由于QFN封装管脚密集且背面又有一块接地的大焊盘,所以在PCB设计中应该格外注意焊盘的几何尺寸。

为了防止短路,在信号线与地之间必需有阻焊剂。

阻焊剂网格的最小尺寸为© 2005 Hittite Microwave Corporation, All Rights Reserved© 2005 Hittite Microwave Corporation, All Rights Reserved0.010英寸[0.25mm]。

qfn封装流程

qfn封装流程

QFN封装是一种新型的表面贴装封装技术,它具有体积小、重量轻、高密度、高可靠性等优点,因此在电子产品中得到了广泛应用。

下面

将介绍QFN封装的流程。

一、基板制备

首先需要准备好基板,通常使用FR-4玻璃纤维板或者陶瓷板。

基板需要经过表面处理,包括去除氧化层、清洗、沉积金属等步骤,以保证

焊接质量。

二、印刷焊膏

将焊膏印刷在基板上,焊膏的成分和厚度需要根据具体的封装要求进

行调整。

印刷焊膏的设备通常是自动化的,可以提高生产效率和质量。

三、贴片

将芯片贴在基板上,需要注意芯片的方向和位置。

贴片设备通常是自

动化的,可以提高生产效率和质量。

四、热压焊接

将基板和芯片放入热压机中,进行热压焊接。

热压焊接的温度和时间

需要根据具体的封装要求进行调整。

热压焊接可以使焊膏熔化,将芯

片和基板焊接在一起。

五、切割

将焊接好的基板切割成单个的QFN封装。

切割设备通常是自动化的,可以提高生产效率和质量。

六、测试

对QFN封装进行测试,包括外观检查、焊接质量检查、电性能测试等。

测试设备通常是自动化的,可以提高生产效率和质量。

七、包装

将测试合格的QFN封装进行包装,通常使用盘装或者卷装的方式。

包装设备通常是自动化的,可以提高生产效率和质量。

总之,QFN封装流程需要经过基板制备、印刷焊膏、贴片、热压焊接、

切割、测试和包装等步骤。

每个步骤都需要严格控制,以保证QFN封装的质量和可靠性。

手工焊接QFN器件

QFN封装具有成本低、表贴、塑封、热阻低等优点,适合用 在较高频率。

手工焊接过程中,要注意: 1、管脚之间不要短路; 2、器件背面金属接地要好,保证散热及射频性能。

1、准备工具 包括:热吹风枪,电烙铁,锡膏,吸锡带,镊子等

2、PCB图 布版过程中,一定要注意底部过孔接地,管脚间隙。

3、预上锡 用烙铁在管脚上预上锡;

4、涂匀焊盘 把焊盘上的锡涂匀,不要有突起或尖峰。

5、放置器件 把QFN期间放在焊盘上,注意管脚不要短路。

6、焊接 吹风枪应在器件的垂直正上方,注意控制温度和时间;

7、检查管脚 可以考虑适当补焊管脚,烙铁温度340-360℃,时

QFN封装工艺流程

常见质量:1.粘帖位置: die在lead frame上X-Y位置不超过+/-4miles; 2.Die 倾斜: <0.9miles;3.Epoxy void: 单个void面积占整个die面积的 比例<5%, Void总体面积<20%;4.Epoxy on die;注意事项: 1.Epoxy胶需保存在-45°±5°条件下, 使用前需回温2hrs;2.确保 FIFO(先进先出)生产原则

切割

第4道光检

包装

工艺目的:在产品的背面进行激光刻字,包括产品信息,公司信 息,生产日期,生产批次等

注意事项:1.功率不能太大,否则会伤到键合丝 ; 2.为防止出错,需用 dummy试打 常见质量:1.断码(可能原因:产品上有异物,Laser光的速度过快) ; 2. 码字不清晰(可能原因:Laser信号不稳定,频率设置过大)

QFN封装前道Front Of Line(FOL)

QFN封装前道工艺流程:

晶圆QA

磨片

贴膜

划片

第2道光检

二光(2nd Optical Inspection)

第3道光检

焊线

烘烤

贴片(装片)

第2道光检(FOL) 工艺目的:针对Wafer Saw之后在 显微镜下进行Wafer的外观检查,是 否有出现废品

QFN封装前道Front Of Line(FOL)

QFN封装前道工艺流程:

晶圆QA

磨片

贴膜

晶圆保护膜 (Dicing tape)

划片

切割 (Wafer Saw)

第3道光检

焊线

烘烤

第2道光检 贴片(装片)

工艺目的:使用金刚砂粒非常小的刀片, 安装在高速旋转的锭子上 根据wafer上的切割道对wafer进行切割成单个的die, 同时用去离 子水进行清洗 工艺过程:1.将wafer粘帖在mylar蓝膜上, 防止在切割时晶粒散 落;2.用Saw blade沿wafer切割线将wafer切割成单个的晶粒, 同 时冷却液清理wafer

180419电容器工艺流程及控制要点

180419电容器工艺流程及控制要点电容器工艺流程及控制要点:电容器是一种储存电能的元件,它通常由两个导电体之间的绝缘材料(电介质)组成。

电容器的工艺流程主要包括材料准备、电极制备、电容器组装和测试等环节。

以下是电容器工艺流程的详细介绍,以及其中的控制要点。

1.材料准备电容器的制作所需的主要材料包括金属电极、电介质以及封装材料等。

首先,需要选择适合的金属材料作为电极,常用的有铝、铜等。

然后,选取合适的电介质材料,如氧化铝、聚乙烯等。

最后,还需要准备封装材料,如胶水、塑料等。

控制要点:-选择高纯度、低含杂质的金属材料,以确保电极的导电性能和稳定性。

-选择合适的电介质材料,具有较高的绝缘性能和稳定性。

-严格控制材料的质量,确保各种材料的规格、尺寸和性能符合要求。

2.电极制备电极是电容器的核心组成部分,它决定了电容器的容量和性能。

电极的制备主要包括金属薄片的加工和处理等。

首先,选择合适的材料,并对其进行切割成薄片。

然后,对薄片进行化学处理,如金属表面活化、氧化等。

最后,将处理后的电极薄片进行压制、切割等工艺。

控制要点:-保证电极的厚度均匀,以确保电容器的容量稳定。

-优化电极的表面处理工艺,以增加电容器的绝缘性能和稳定性。

-严格控制电极的尺寸和形状,确保电极与电介质的接触面积均匀。

3.电容器组装电容器组装是将电极和电介质进行组合,形成电容器的过程。

首先,将电极和电介质按照一定的顺序和方式层叠在一起。

然后,通过压制、焊接等工艺将电极和电介质固定在一起。

最后,将固定好的电容器进行封装,以保护电容器的内部结构。

控制要点:-控制电极和电介质的层叠顺序和方式,以确保有效的电场分布和电容器的稳定性能。

-保证电极和电介质的层叠质量,如压力均匀、焊接牢固等。

-合理选择封装材料和工艺,以确保电容器具有良好的绝缘性能和长期耐用性。

4.测试电容器制造完成后,需要进行各项测试来确保其质量和性能。

首先,对电容器的外观进行检查,如表面光洁度、尺寸偏差等。

QFN与BGA生产注意事项

手腕带不能夹在周 转车上,而应插在 防静电地线专用插 孔中

四、焊接注意事项

焊接注意事项

焊接注意事项 设备取中心点要求

焊接注意事项 回流参数要求(不同的焊锡膏参数也会不同)

五、检验项目

五、检验项目

追求人生的美好!

我们的共同目标!

三、元件取放

1、所有QFN/BGA元件都为湿敏元件;

要求:恒温恒湿保存且开封24小时内使用完毕,如有未使用

完毕的要求干燥箱烘烤后使用!!

Humidity Indicator Card

20

元件Байду номын сангаас装要求

元件放置要求

1﹑使用條件:車間環境溫度在20℃~28℃,相對濕度在30%~70%之間﹔ 2﹑儲存條件:

QFN与BGA生产注意事项

2013-06-19

一、元件介绍 QFN:四边有引脚,引脚内弯元件;

俯视图 BGA:底部引脚元件;

侧视图

俯视图

侧视图

二、元件优缺点 QFN

a,节省空间 b,芯片小型化 c,芯片保护性好(外观、性能)

BGA a,高性能 B,节省空间

缺点 1、焊接效果不可视; 2、焊接要求高; 3、返修困难; 4、对员工要求高; 5、贴装精度要求高;

A.保持在有干燥材料的MBB密封包装(真空包装)状态下存储。 B.存储在MCDRY防潮箱内相對濕度<5%RH,溫度在20℃~28℃之間﹔

4﹑若溫濕度超出規定范圍﹐立即通知相關人員進行改善﹐同時采取相應的補救措施( 如放置干燥劑﹑調節室內溫度或取出故障防潮箱中的元件,放入合格的防潮箱內)。

5﹑各封閉區域之溫濕度環境空間敞開時間或開門不能超過5分鐘, 以確保溫濕度條件 能持續保證在管制範圍內.

提高QFN封装元件焊接质量的分析

提高QFN封装元件的焊接质量分析摘要:QFN封装元件由于具有良好的电和热性能、体积小、重量轻等优点,在电子产品中越来越广泛的推广和应用,目前,在航天电子产品中QFN也有不少应用。

QFN封装和CSP有些相似,但底部不是锡球,它有一个中央裸焊端和周围的电极接触点,均需要焊接到PCB上。

由于焊盘在元件的底部,焊接后返修困难大,要求每次焊接都要有良好的焊接效果。

关键字:QFN封装焊接质量虚焊网板引脚温度曲线返修1前言QFN(Quad Flat No-lead Package,四侧扁平无引脚封装)是一种焊盘尺寸小、体积小、以塑料和陶瓷作为密封材料的新兴的表面贴装芯片封装技术。

封装四侧配置有电极接触点,没有引脚,封装底部中央位置有一个面积裸露的焊盘,主要有导热和接地作用。

由于QFN封装不像传统的TSOP封装那样具有欧翼状引线,内部引脚于焊盘之间的电路径短,自感系数以及封装体内部线组很低,所以它能提供卓越的电性能。

此外,它还通过外露的引线框架焊盘提供了出色的散热性能,该焊盘具有直接散热的通道,用于释放封装体内的热量。

通常,将散热焊盘直接焊接在电路板上,并且PCB 中的散热孔有助于将多余的功耗扩散到铜接地板中,从而吸收多余的热量。

QFN 贴装占有面积比QFP 小,高度比QFP低,但是当印制板与封装之间产生应力时,在电极接触处就不能得到缓解。

因此电极接触点难于做到QFP的引脚那样多,一般从14到100左右。

在我们接触到的QFN中以塑料封装的为主,电极接触点中心距除1.27mm外,还有0.65mm和0.5mm两种。

由于它体积小、重量轻、散热效果好,非常适合应用在高密度印制电路板上,但是由于QFN的焊盘主要在元件的底部,它的焊接效果、检测以及返修是我们关注的焦点。

2控制散热焊盘上的锡膏量QFN中间散热焊盘上的锡膏量的多少是决定元件焊接质量的关键因素。

QFN中间的大焊盘通常有接地和散热的作用,通常为了避免大功率元件在散热不好的情况下失效,该焊盘的锡膏量应该尽可能的多以保证接触良好,但是一定要注意网板开口的比例,可以减少虚焊和短路的发生。

QFN封装元件组装及质量控制工艺

QFN封装元件组装及质量控制工艺史建卫【摘要】Q FN 封装由于具有良好的电和热性能、体积小、质量轻,在电子产品中被越来越广泛的推广和应用,针对Q FN 封装元件PC B 焊盘设计、焊膏印刷网板开孔设计、贴装工艺、焊接工艺及返修工艺进行了阐述。

%QFN (QuadFlatNo-Lead)Packinghasbeenwidelypromotedandappliedintheelectronic products because of its good electronical and therm al perform ance, sm all volum e and light w eight. In this article, PC B pad design, stencil design for solder paste printing, com ponent m ounting process, reflow soldering and rew ork process ofQ FN packing device w illbe system exposited in detail.【期刊名称】《电子工业专用设备》【年(卷),期】2015(000)002【总页数】10页(P21-30)【关键词】Q FN 封装;热焊盘;网板设计;回流焊接;返修【作者】史建卫【作者单位】中兴通讯股份有限公司,广东深圳518057【正文语种】中文【中图分类】TN605近几年来,由于QFN(方形扁平无引脚)封装具有良好的电热性能、体积小且质量轻,其应用正在快速增长。

采用微型引线框架(Micro Lead Frame)的QFN封装和CSP(Chip Size Package)封装有些相似,但元件底部没有焊球,与PCB 的电气和机械连接是通过PCB焊盘上印刷焊膏,经过回流焊形成的焊点来实现的。

QFN封装对工艺提出了新的要求,本文将系统的对其组装及质量控制工艺进行探讨。

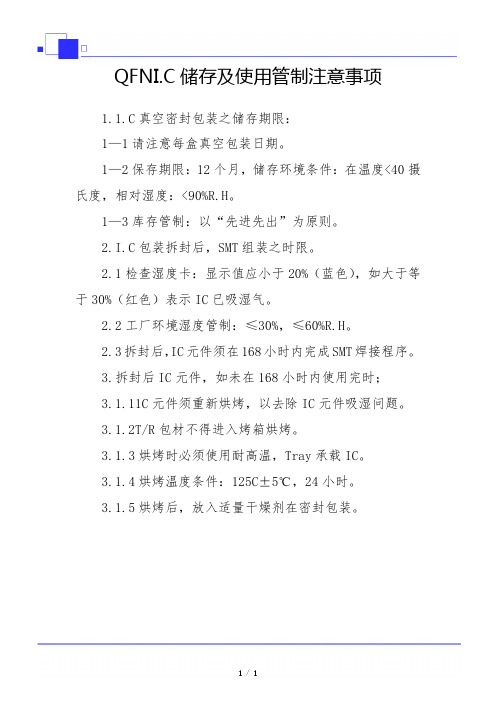

QFNI.C储存及使用管制注意事项

QFNI.C储存及使用管制注意事项

1.1.C真空密封包装之储存期限:

1—1请注意每盒真空包装日期。

1—2保存期限:12个月,储存环境条件:在温度<40摄氏度,相对湿度:<90%R.H。

1—3库存管制:以“先进先出”为原则。

2.I.C包装拆封后,SMT组装之时限。

2.1检查湿度卡:显示值应小于20%(蓝色),如大于等于30%(红色)表示IC已吸湿气。

2.2工厂环境湿度管制:≤30%,≤60%R.H。

2.3拆封后,IC元件须在168小时内完成SMT焊接程序。

3.拆封后IC元件,如未在168小时内使用完时;

3.1.11C元件须重新烘烤,以去除IC元件吸湿问题。

3.1.2T/R包材不得进入烤箱烘烤。

3.1.3烘烤时必须使用耐高温,Tray承载IC。

3.1.4烘烤温度条件:125C±5℃,24小时。

3.1.5烘烤后,放入适量干燥剂在密封包装。

1 / 1。

QFN封装技术简介

Wafer Grinding

Wafer Mount

Die Saw

Die Bond Wire Bond Molding

1st Plasma Clean 2nd Plasma Clean

Post Mold Cure

Marking

Ball Mount

Package Mount

Package Saw

Pick & Place

Final Visual Inspection

Packing

LOGO

IC封裝材料

Leadframe Copper/Alloy

Substrate

Solder balls Solder Alloy

Gold wire

BT Resin

Epoxy (Silver paste)

Molding compound

根據天下雜誌2002 的100大企業調查,企業平均獲利水準約在1.3%,創 下十七年來的最低,正式宣告微利化時代的來臨。一般在開始規模約在 50 部銲線機,其投資額約在十億左右(含廠房與設施)。產品從雙排腳到 平面四面腳/膠帶線/球陣列/影像感應/薄膜晶體,因大部份同質性均高, 造成價格互相之間的排擠效應。而數個集團如安可、日月光、矽品,亦 夾其大公司、資本雄厚的優勢,試圖合併其他較小的公司,以利其價格 之主宰。同時大公司亦佔有〝量大〞的優勢,故與廠商的議價能力相當 高,如日月光可依據價格自由選擇廠商或更換廠商。而與購買者議價能 力,則受幾家大廠的殺價狀況所影響,致使購買者的轉換成本加大。而 未來低腳數球陣列產品亦漸漸被QFN產品所取代 。

Die

Gold wire

金綫

Leadframe

晶片

金綫

導綫架

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

锡膏回温必须达到要求: 室温回温八小时;

使用期限: 钢板上八小时,开瓶后12小时;

锡膏印刷条件: 1.速度20-25mm/sec; 2.具有干擦,湿擦和真空擦功能,擦拭 频率: 2pnl/次,2小时手动擦拭一次; 3.脱模干净,锡膏厚度在范围内。

PDF 文件使用 "pdfFactory Pro" 试用版本创建

检 测

检 测

环境

温度:24+3度 湿度:30-60%

PDF 文件使用 "pdfFactory Pro" 试用版本创建

STENCIL

钢板开孔

GERBER图片 钢板图片

PDF 文件使用 "pdfFactory Pro" 试用版本创建

Electronics (SuZhou) CO. LTD

QFN元件

生产过程及作业要求

PDF 文件使用 "pdfFactory Pro" 试用版本创建

议程

环 境

PDF 文件使用 "pdfFactory Pro" 试用版本创建

X-RAY AOI REFLOW MOUNT PRINT STENCIL

2.PWA出Relow前必须保证在150度 以下,PEAK温度240-245度(无 铅);

3.必须保证充分的冷却方可以从轨道 上拿下。

PDF 文件使用 "pdfFactory Pro" 试用版本创建

AOI 检 测

100% AOI检测,严格控制误判率。

PDF 文件使用 "pdfFactory Pro" 试用版本创建

X-RAY检测

100% X-RAY检测,并作好标记;

PDF 文件使用 "pdfFactory Pro" 试用版本创建

THANKS!

PDF 文件使用 "pdfFactory Pro" 试用版本创建

MOUNT

度4小时(或按元器件要求);

2.做好贴片前的程式调教动作,确保坐标准确。

PDF 文件使用 "pdfFactory Pro" 试用版本创建

REFIOW

1.按锡膏厂商的推荐profile,参照罗 技PMP要求,严格控制各区温度及 升温降温速率;