红外遥控器控制系统的VHDL设计与FPGA实现

基于FPGA的红外家居遥控系统

基于FPG A 的红外家居遥控系统3陈立江, 赵 琦(北京航空航天大学电子信息工程学院 北京 100083) 3本项目受北航大学生科研训练计划(SRTP )项目经费支持 收稿日期:2006-11-10 收修改稿日期:2007-01-08摘 要:介绍红外家电遥控的码流和几种类型的编码方法,采用89S51单片机和现场可编程门阵列(FPG A )开发一款自学习式通用家电遥控器。

通过自制的简易遥控教练器与接收器实现对原本无遥控功能的电灯、电扇、窗帘等追加红外遥控功能。

通过G irder 软件实现对电脑的遥控。

通过对电脑、电视、VC D 等家用电器的测试,证明该遥控系统学习性能良好,操作简易,有效遥控距离可达5~7m 。

关键词:遥控; 编码; 自学习; FPG A ; LC D中图分类号:T N431.2 文献标识码:A 文章编号:C N11-1780(2007)03-0064-05引 言随着人们生活水平的提高,家用电器种类的增多,遥控器的种类也随之增加,不同种类的遥控器之间一般不能相互替代,这给人们的生活带来诸多不便。

在许多现存的通用家居遥控器中,大多是先将需使用遥控器的红外遥控编码人工分析出来,按“0”、“1”序列方式存储,使用时,先选择型号再进行控制。

目前家庭使用的电器越来越多,新的遥控编码组合层出不穷,无法得到所有类型的编码,因此此类通用型遥控器只适用于某一类电器的有限种品牌。

另一类通用遥控器是先将原遥控器的遥控波形完全记录下来,使用时再进行还原。

此类遥控器解决了无限编码的海量存储问题,但在需要遥控多个电器或遥控功能复杂时,不能满足需求[1]。

各类遥控器功能大致相同。

大多都有数字键、启动停止键、前进键、快进键和后退键,复杂的也就是再增加几个功能键。

现实生活中,由于用户的个体差异,特殊功能键的使用频率很低,甚至部分用户自始至终就从未使用过这类按键。

因此,这些按键完全可以简化和归类使用。

对于那些不宜简化和归类的少量特殊功能键,可以通过开辟自定义按键区的方法予以解决。

基于FPGA的红外遥控器设计【开题报告】

毕业论文开题报告电子信息工程基于FPGA的红外遥控器设计一、课题研究意义及现状红外线遥控是目前使用最广泛的一种通信和遥控手段。

由于红外线遥控装置具有体积小、功耗低、功能强、成本低等特点,因而,继彩电、录像机之后,在录音机、音响设备、空凋机以及玩具等其它小型电器装置上也纷纷采用红外线遥控。

工业设备中,在高压、辐射、有毒气体、粉尘等环境下,采用红外线遥控不仅完全可靠而且能有效地隔离电气干扰。

红外遥控技术在工农业生产,通信技术,家用电器等多种领域中得到了广泛的应用,特别是在门禁系统中的应用,更加受到了人们的瞩目。

由于红外线遥控不具有像无线电遥控那样穿过障碍物去控制被控对象的能力,所以,在设计家用电器的红外线遥控器时,不必要像无线电遥控器那样,每套(发射器和接收器)要有不同的遥控频率或编码(否则,就会隔墙控制或干扰邻居的家用电器),所以同类产品的红外线遥控器,可以有相同的遥控频率或编码,而不会出现遥控信号“串门”的情况。

这对于大批量生产以及在家用电器上普及红外线遥控提供了极大的方便。

由于红外线为不可见光,因此对环境影响很小,再由红外光波动波长远小于无线电波的波长,所以红外线遥控不会影响其他家用电器,也不会影响临近的无线电设备。

目前国外(主要是欧美市场)的遥控器几乎都是多功能遥控器,它们能够控制全球的绝大部分的视频设备甚至包括空调器。

这些遥控器一般由MCU进行控制,其价格一般都比较贵,达上百美金。

值得一提的是,目前全球的遥控器的80%是由中国大陆代工贴牌生产的,但关键芯片是别人的。

国外的遥控器主要通过超市等渠道进行销售,消费者可以根据自己的需要进行选择,其发展趋势是根据家庭的需要遥控器拥有更多的功能和更人性化的设计。

而在国内市场,遥控器绝大部分是单一型的遥控器,也就是一个遥控器控制一个视频设备,这与我国经济状况和消费习惯有关。

多功能(所谓万能)遥控器只是单一型的遥控器的补充,在一般的主流渠道是没有多功能遥控器销售的,许多消费者也就不知道有或者如何购买多功能遥控器,因此多功能遥控器的销量是相对很少的。

基于FPGA的红外遥控信号接收模块的设计

d i 03 6 / i n1 6 - 7 52 1 .5O 3 o: .9 9js 。5 3 4 9 . 10 .l l .s 0

塾 铲 蓬 擅 倚 罨 蕊 梭 蠛

常 涛 ,雪 琦

( 京航 天航 空大 学 软件 学院 ,北京 1 0 9 ) 北 0 11

摘 要 :文 中分 析 了红 外 线遥控 器 系统 的数据 编 码 和传 输 机 制 ,并 用V ro H L 言 设 计 了 ei g D 语 l

采 用P WM 方 法 编 码 , 即 脉 冲 宽 度 调 制 ,0码 由

收 稿 日期 :01 — 0 2 2 0 1—8

仪 小 父 侃

起始码

用户码

r r

用户反码

-

数据码

。。

甄孺反码

9 4s 2C5C0C3C6 Iz 5D I D m . C1C4C7C2 5 D 4D7 5 0C3C6 1C4 7 1D 6 m C C l3D C C C 。 D 丽 7 I

的 。数 据 码 为8位 ,可 编码 2 6种 状 态 ,代 表 实 际 5 所 按 下 的键 。 数 据 反 码 是 数 据 码 的各 位 求 反 ,通 过 比较 数 据 码 与 数 据 反 码 ,可 判 断接 收到 的数 据 是 否 正 确 。如 果 数 据 码 与 数 据 反 码 之 间 的关 系 不 满 足 相 反 的 关 系 ,则 本 次 遥 控 接 收有 误 ,数 据 应 丢弃 。 在 同 一 个 遥 控 器 上 ,所 有 按 键 的数 据 码 均

电平 是 上 述 格 式 图 中 的波 形 取 反 .即停 止 状 态 时

I 高 电平 ,然 后 接 收 到9 s 右 的 低 电平 后 进 R为 m左 入 准 备 状 态 。 由图 中分 析 可 以得 到 ,引 导 码 高 电

《Protel DXP电路设计基础教程》第12章:VHDL和FPGA设计[精品]

![《Protel DXP电路设计基础教程》第12章:VHDL和FPGA设计[精品]](https://img.taocdn.com/s3/m/5c4cdafe81eb6294dd88d0d233d4b14e85243eda.png)

use 库名.包名.all; 前面一句表示包中的指定项目可见(即可 以引用);后面一句的.all表示包中的所有项 目都可见。

12.2.4 VHDL配置指定

配置(Configuration)语句描述层与层之间的 连接关系以及实体与结构体之间的连接关系。 设计者可以利用这种配置语句来选择不同的构 造体。在仿真某个实体时,可以利用配置来选 择不同的构造体,进行性能对比实验以得到性 能最佳的构造体。

1 VHDL的三类对象 弥产沮糕宵敌收眠绣贤绸邱潦燥浑锚殴吓护求聚匣盼媒捆炉谈慧状镊棠例《Protel,,,,,DXP电路设计基础教程》第12章:VHDL和FPGA

每个元件实际上也是一个一个的实体。整个电 设计《Protel,,,,,DXP电路设计基础教程》第12章:VHDL和FPGA设计

1 VHDL的三类对象

设计《Protel,,,,,DXP电路设计基础教程》第12章:VHDL和FPGA设计

( entity ) 和 结 构 体 ( architecture ) 。 实 体 VHDL提供层次化结构描述的手段。

媒啤峡赢奄阴畸院只缠沏樱祸丽国魁悠停队舰悸给喂劣真占施疏猎舔渣怎《Protel,,,,,DXP电路设计基础教程》第12章:VHDL和FPGA

12.2 VHDL基本知识

12.2.1 VHDL程序基本结构 12.2.2 VHDL程序实体和结构体 12.2.3 VHDL程序包和设计库 12.2.4 VHDL配置指定 12.2.5 VHDL对象及其数据类型 12.2.6 VHDL表达式与运算操作符 12.2.7 VHDL子程序 12.2.8 VHDL顺序描述语句 12.2.9 VHDL并行描述语句 12.2.10 VHDL程序举例 12.2.11 VHDL小结

基于FPGACPLD设计与实现UART(VHDL)

基于FPGA/CPLD设计与实现UART(VHDL)1 引言由于微电子学和计算机科学的迅速发展,给EDA(电子设计自动化)行业带来了巨大的变化。

特别是进入20世纪90年代后,电子系统已经从电路板级系统集成发展成为包括ASIC、FPGA/CPLD和嵌入系统的多种模式。

可以说EDA 产业已经成为电子信息类产品的支柱产业。

EDA之所以能蓬勃发展的关键因素之一就是采用了硬件描述语言(HDL)描述电路系统。

就FPGA和CPLD开发而言,比较流行的HDL主要有Verilog HDL、VHDL、ABEL-HDL和 AHDL 等,其中VHDL 和Verilog HDL因适合标准化的发展方向而最终成为IEEE标准。

下面的设计就是用VHDL来完成实现的。

2 UART设计实例通常设计数字电路大都采用自顶向下将系统按功能逐层分割的层次化设计方法,这比传统自下向上的EDA设计方法有更明显的优势(当时的主要设计文件是电路图)。

因为由自顶向下的设计过程可以看出,从总体行为设计开始到最终逻辑综合,形成网络表为止。

每一步都要进行仿真检查,这样有利于尽早发现系统设计中存在的问题,从而可以大大缩短系统硬件的设计周期。

下面以UART的设计为例具体说明:(本设计只对本设计的总模块做各种基于MAX+PLUS II环境下的各种分析,对于各分模块只是作些必要的说明。

) UART(即Universal Asynchronous Receiver Transmitter 通用异步收发器)是一种应用广泛的短距离串行传输接口。

UART允许在串行链路上进行全双工的通信。

串行外设用到的RS232-C异步串行接口,一般采用专用的集成电路即UART实现。

如8250、8251、NS16450等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO),有时我们不需要使用完整的UART的功能和这些辅助功能。

或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。

基于FPGA的VHDL语言设计控制器SJA1000的IP软核设计

基于FPGA 的VHD1语言设计控制器SJA1000的IP 软核设计 分析了CAN 控制器SJA1ooO 的特点及CAN 协议通信格式。

设计了控制器SJA1OOO 的IP 软核,能为应用提供一个性能优良的、易于移植的控制器SJA1000,实现了对步进电机的控制。

控制局域网(CAN )属于现场总线的范畴,它是一种有效支持分布式控制或实时控制的串行通信网络。

与一般的通信总线相比,CAN 总线的数据通信可靠性、实时性和灵活性好,应用领域非常广泛,通常基于ARM 或51单片机,实现与CAN 控制器的通信联络。

与GA /SoPC 技术是实现嵌入式系统的最高形式,基于IP 软核的设计与应用也必将成为替代硬核的一种发展趋势。

凭借QUartUSI1和NiosII 工具,基于FPGA 的VHD1(或VeriIog )语言设计的IP 核能够提供灵活性和性能更好的控制器。

图1为一个基于FPGA 的控制器的CAN 总线节点。

其中PCA82C251是CAN 总线接收器,SJA1OOO 是CAN 总线通信控制器,PMM8713是驱动步进电机的脉冲分配器,FPGA 模块在节点模型中对SJAIooO 进行控制,并将接收到的帧信息进行处理,发送给脉冲分配器,以驱动步进电机。

在设计中采用自顶向下的设计方法。

通过分析SJΛ1000常用的控制芯片51单片机的功能,将其分为主要的4个模块:初始化模块、位查询模块、数据处理模块和缓冲区释放模块。

对SJA1000完成控制功能的过程用状态图描述如图2所示,这也是系统的主状态机。

4个状态对应上述的4个功能模块,首先在ini11a1_st-ate 完成对SJA1OOO 的初始化,在由init_end 值号给出初始化完成标志后,进入查询状态,即queerRBS 状态,由位看询模块完成此时对SJA1OO0的状态查询。

如果查询到SJA1OOo 缓冲区有帧信息,将qRBSend 置“1”,进入下一个状态frame_cope,即帧处理状态,此时由数据处理模块完成对缓冲区的数据读取,并作处理。

VHDL习题解答

V H D L习题解答(共15页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--VHDL 程序设计教程习题参考解答第一章习题参考答案1.什么是VHDLVHDL的实现有哪几种形态硬件描述语言(Hardware Description Language,HDL),顾名思义,是电子系统硬件行为描述、结构描述、数据流描述的语言。

VHDL语言的英文全名是Very High Speed Integrated Circuit Hardware Description Language,即超高速集成电路硬件描述语言。

2.简述VHDL的发展史。

1981年6月VHDL工作小组成立,提出了一个满足电子设计各种要求的能够作为工业标准的硬件描述语言。

1983年第三季度,由IBM公司、TI公司、Inter metrics公司签约,组成开发小组,工作任务是提出语言版本和开发软件环境。

1986年IEEE标准化组织开始工作,讨论VHDL语言标准,历时一年有余,于1987年12月通过标准审查,版本宣布实施,即IEEE STD 1076-1987。

1993年经过重新修订,发布版本,从而形成新的标准即IEEE STD 1076-1993。

2006年VHDL发布版本;2008年8月,VHDL 版本发布,解决了版本中发现的多个问题。

2009年1月,IEEE公布了VHDL 的标准版本,最新VHDL标准IEEE 1076-2008在2009年1月实施。

3. 详述VHDL设计IP模块的流程。

第1种设计形态,VHDL程序以IP模块的形态存在,VHDL-IP设计流程如图所示。

IP模块是与集成电路工艺无关的芯片设计方案,可以移植到不同的设计环境。

IP产品形态有规范,有IP包装规则和复用规则,是原生态的芯片硬件设计产品。

图 VHDL-IP设计流程4. 简答VHDL设计用FPGA实现的意义。

可编程器件FPGA具有容量大、密度高等特点,是科学实验、小批量生产、样机研制的载体。

用FPGA芯片实现自学习型红外遥控器设计

器功能 于一体,实现对多个家电设备的遥控。 据 文献 调 查 , 目前 所 以 学 习 型 遥 控 器 都 用 微 处

理 器通过运 行程 序软件来实现,基本都采用波

形 复制 的 方法 来 解 决 学 习 不 同 遥 控 编 码 格 式 的 问题 。 本 文利 用F P GA 器 件 为 载 体 , 通 过 V e r i l o g HD L语 言 设 计 数 字 逻 辑 电 路 的 方 法 来 实 现 学 习 型红 外 遥控 器 。 为 了 解 决 波 形 复 制 方 法 带 来 的 存储 容 量 大 的 问 题 , 根 据 每 种 红 外 遥 控 编 码 格 式 的 引 导 码 不 同 , 提 出 通 过 引 导 码 识 别时 序 电路 。 识 别 不 同 类 型 的 红 外 遥 控 编 码 , 并 根 据 不 同编 码 方 法 设 计 不 同 的 解 码 电 路 。 同 时 采用 按 键 复用 的 时 序 电 路 设 讨‘ , 解 决 一 个 按 键 可 以遥 控 不 同类 型 设 备 的 问题 。

习状态 ( s t a t e c t r —l , b 1 ),

态a在遥控状态下 ,按 下遥控某 个按键 ,通过 操作某个按键 , 产生按键 对应 的存储单元地址 , 并读取该存储单 元的地址 数据 ,将 数据送 给对 应的发射调制 电路 ,将数据进制 调制,然后送 给发射二极管 。在学 习状态 下,按 下需要学习 的按键 , 然后接 收被学习按键 的遥控编 码信号,

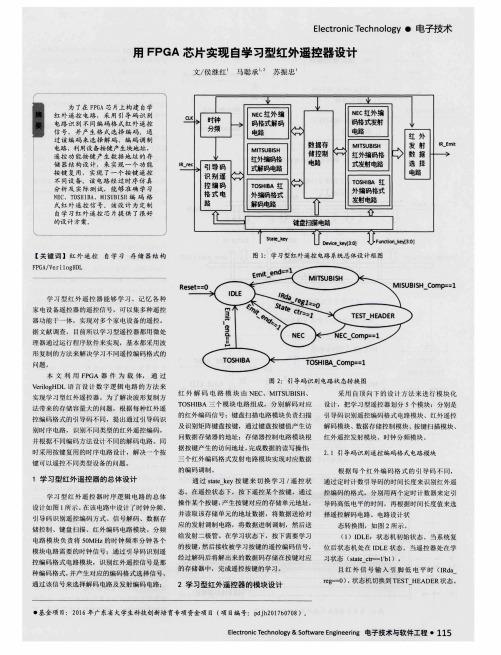

1 学 习型 红 外 遥 控 器 的 总 体 设 计

学 习 型 红 外 遥 控 器 时 序 逻 辑 电路 的 总 体 设计如 图 l 所示 。 在 该 电 路 中 设 计 了时 钟 分 频 、 引 导码 识 别遥 控 编码 方 式 、 信 号 解 码 、 数 据 存 储 控 制 、键 盘 扫 描 、 红 外编 码 电 路 模 块 。 分 频

基于fpga的红外遥控信号解码设计

电子技术与软件工程Electronic Technology & Software Engineering 电子技术Electronic Technology基于FPGA 的红外遥控信号解码设计文/陈韵文肖顺文郑瑞王涌罗春梅(西华师范大学电子信息工程学院 四川省南充市 637009 )摘 要:本文针对红外遥控信号解码电路,设计了基于FPGA 的红外遥控信号解码电路系统。

本系统包括红外解码关键电路设计和红 外解码状态机设计。

经过电路仿真,FPGA 板级测试,本电路系统达到红外遥控信号解码电路功能要求。

关键词:Verilog HDL;红外遥控;FPGA红外遥控具有体积小、信息传输可靠、功耗低、成本低等显著特点⑴,广泛应用于家用家电、工业控制等领域。

红外线为不可见光, 不受电磁环境的干扰,方向性好,同时也具有不干扰其他用电设备工作,不影响周边环境的良好优点,因此,研究红外遥控系统工作 原理并设计实现显得尤为必要。

本文采用Verilog HDL 来设计实现红外遥控信号的解码,这种基于FPGA 实现的红外解码比传统方式 解码速度更快、精确率更高。

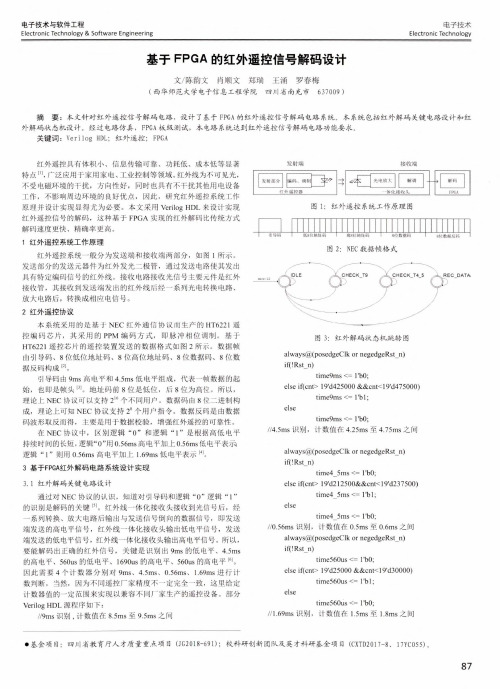

1红外遥控系统工作原理红外遥控系统一般分为发送端和接收端两部分,如图1所示。

发送部分的发送元器件为红外发光二极管,通过发送电路使其发出具有特定编码信号的红外线。

接收电路接收光信号主要元件是红外接收管,其接收到发送端发出的红外线后经一系列光电转换电路、放大电路后,转换成相应电信号。

2红外遥控协议本系统采用的是基于NEC 红外通信协议而生产的HT6221遥控编码芯片,其采用的PPM 编码方式,即脉冲相位调制。

基于 HT6221遥控芯片的遥控装置发送的数据格式如图2所示。

数据帧由引导码、8位低位地址码、8位高位地址码、8位数据码、8位数 据反码构成[2]o引导码由9ms 高电平和4.5ms 低电平组成,代表一帧数据的起 始,也即是帧头⑶。

地址码前8位是低位,后8位为高位。

本科论文设计-基于fpga的可遥控智能彩灯控制器设计与实现

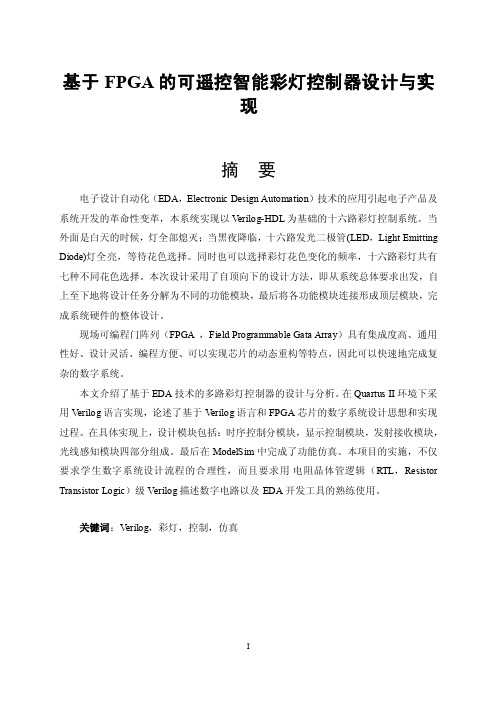

基于FPGA的可遥控智能彩灯控制器设计与实现摘要电子设计自动化(EDA,Electronic Design Automation)技术的应用引起电子产品及系统开发的革命性变革,本系统实现以V erilog-HDL为基础的十六路彩灯控制系统。

当外面是白天的时候,灯全部熄灭;当黑夜降临,十六路发光二极管(LED,Light Emitting Diode)灯全亮,等待花色选择。

同时也可以选择彩灯花色变化的频率,十六路彩灯共有七种不同花色选择。

本次设计采用了自顶向下的设计方法,即从系统总体要求出发,自上至下地将设计任务分解为不同的功能模块,最后将各功能模块连接形成顶层模块,完成系统硬件的整体设计。

现场可编程门阵列(FPGA ,Field Programmable Gata Array)具有集成度高、通用性好、设计灵活、编程方便、可以实现芯片的动态重构等特点,因此可以快速地完成复杂的数字系统。

本文介绍了基于EDA技术的多路彩灯控制器的设计与分析。

在Quartus II环境下采用V erilog语言实现,论述了基于V erilog语言和FPGA芯片的数字系统设计思想和实现过程。

在具体实现上,设计模块包括:时序控制分模块,显示控制模块,发射接收模块,光线感知模块四部分组成。

最后在ModelSim中完成了功能仿真。

本项目的实施,不仅要求学生数字系统设计流程的合理性,而且要求用电阻晶体管逻辑(RTL,Resistor Transistor Logic)级Verilog描述数字电路以及EDA开发工具的熟练使用。

关键词:V erilog,彩灯,控制,仿真大连东软信息学院毕业设计(论文) Abstract Design and Iplementation of Remote Intelligent Lights Controller Based on FPGAAbstractElectronic Design Automation (EDA, Electronic Design Automation) technology application cause the revolutionary change of Electronic products and systems development, the system implementation based on V erilog HDL - ten all lights control system.When the day is outside, lights all out, when night came, ten all led lights all light, waiting for design and color choice. At the same time, also can choose design and color of lights change frequency, ten all lights a total of seven different colors to choose.The design has adopted the top-down design method, namely from the overall system requirements, from top to bottom of the design task decomposition into the different function module, finally each function module is connected to form the top module, the overall design of system hardware.Field Programmable gate Array (FPGA, Field Programmable Gata Array) with high integration, good generality, flexible design, programming, convenient, can realize the dynamic reconfiguration of chips and other characteristics, so you can quickly complete the complex digital system.This paper introduces the design and analysis of multiple lights controller based on the EDA technique.In the QuartusII environment using V erilog language, discusses the digital system design idea of V erilog language and the FPGA chip and the implementation process based on.On the concrete realization,Design modules include: Sequential control module, display control module, launch receiving module, light perception module four parts.Finally complete functional simulation in ModelSim.The implementation of this project, not only requests the student to the rationality of the digital system design process, and asked to use resistance Transistor Logic (RTL, Resistor Transistor Logic) level V erilog digital circuit and skilled use of EDA tools.Key words: V erilog, Lantern, Control, Simulation目录摘要 (I)ABSTRACT (II)第1章绪论 (1)1.1 课题研究背景与意义 (1)1.2 课题研究内容与方法 (2)第2章关键技术介绍 (3)2.1 VERILOG HDL (3)2.2 自上而下设计 (4)2.3 有限状态机 (5)第3章系统需求分析 (8)3.1 系统设计目标 (8)3.2 系统功能需求 (8)3.3 系统非功能需求 (8)3.4 系统开发环境 (8)3.4.1 硬件环境 (8)3.4.2 软件环境 (9)3.5 系统可行性分析 (11)3.6 外围电路分析 (12)3.6.1 控制电路 (12)3.6.2 显示电路 (12)3.6.3 系统流程图 (12)第4章系统设计 (14)4.1 系统设计指导原则 (14)4.2.1 数据通道模块设计 (16)4.2.2 控制单元模块设计 (17)第5章系统实现 (19)5.1 控制单元的部分实现 (19)5.2 数据通道中的部分实现 (20)第6章系统测试 (21)6.1 控制单元仿真 (21)6.2 数据通道仿真 (21)6.3 分频模块仿真 (21)6.4 显示模块仿真 (22)6.5 系统整体仿真 (22)第7章结论 (23)致谢 (25)第1章绪论1.1 课题研究背景与意义科学技术的无限发展,人民生活水平的不断提高,都使得彩灯装饰在现代生活中变为一种可增强人们的美感饰具,同时也可作为广告宣传,不仅增添节日的气氛,也为着人们的生活增添亮丽。

基于VHDL的红外遥控电子琴

基于VHDL的红外遥控电子琴

刘振

【期刊名称】《无线互联科技》

【年(卷),期】2012(000)004

【摘要】远程遥控技术应用越来越广泛,本研究旨在将红外遥控技术进一步推广。

论文通过对38K红外遥控发射接收和蜂鸣器发声原理的研究,采用VHDL编程语言设计红外遥控器的控制系统,通过改变蜂鸣器发声频率,实现了不同的音色,从而制作出红外遥控的电子琴

【总页数】1页(P20-20)

【作者】刘振

【作者单位】华南理工大学,广东广州510641

【正文语种】中文

【相关文献】

1.红外遥控器控制系统的VHDL设计与FPGA实现 [J], 佟国香;孙国强;李广军

2.VHDL教学中的电子琴设计 [J], 葛灿;韩延义;上官诚江

3.基于ARM+Linux的模拟电子琴设计 [J], 胡淼元;何文德;杨凤年

4.基于机器视觉的智能电子琴 [J], 林训烨;冯玲;吴予萌

5.基于Android的少儿电子琴练习软件设计与开发 [J], 安翼飞;于营

因版权原因,仅展示原文概要,查看原文内容请购买。

红外遥控器控制系统的VHDL设计与FPGA实现

文章编号:1007-6735(2004)02-0189-04收稿日期:2003-07-27作者简介:佟国香(1968-),女,讲师.红外遥控器控制系统的VHDL 设计与FPGA 实现佟国香1, 孙国强1, 李广军2(1.上海理工大学计算机工程学院,上海 200093; 2.电子科技大学通信工程学院,成都 610058)摘要:采用VHDL 语言设计了红外遥控器的控制系统.该系统通过了实时仿真和验证,并下载到FPGA 中执行,可实现键值及客户码的读入、红外发射码的生成及发送等功能.电路模块的程序代码可重复使用,可方便地嵌入到各类需要红外遥控控制的嵌入式系统中.关键词:VHDL 设计;FPGA;红外遥控器中图分类号:TN 876 文献标识码:AVHDL design and FPGA implementation of the controlsystems in infrared remote controllerTONG Guo xiang 1, SUN Guo qiang 1, LI Guang jun 2(1.College of Compu ter Engineerin g,Un iver sity of Shan ghai for Scien ce an d Technology,Shan ghai 200093,China ;2.School of Com m un ication an d In form ation En gin eering,University of Electron ic Scienceand Technology of China ,Chen gdu 610058,Chin a )Abstract:The co ntrol systems in an infrared remo te controller are designed using VHDL.The VHDL d e sign is verified throu gh simu lation and imp lem ented using FPGA.The System functions includ e key data cod es and custom cod es reading,infrared em itting code generating and emitting,etc.The VHDL cod es of the system s are reusable and can b e emb edd ed in systems requiring infrared remo te control.Key words:VHDL desi gn ;FPGA ;Inf r a r edr emot e con tr ol红外遥控作为一种单向红外通讯技术,因其具有性能稳定、使用方便以及成本低廉等特点,已经在消费类电器中得到普遍的应用.随着对电器产品的智能化和使用便利性要求的进一步提高,红外遥控的应用已开始从其传统的家用电器领域向智能设备等新领域扩展[1].由于集成电路制造工艺和设计水平的不断提高,将此类传统的分立电路功能集成到嵌入式的系统中已成为可能[2,3].本文根据嵌入系统的要求进行了红外遥控器控制系统的设计.设计中脉冲信号调制采用了PPM 方式,红外遥控器的控制系统采用了超高速集成电路硬件描述语言(VeryHigh speed integrated circuit hardware Description Language,VHDL),并通过现场编程门阵列器件(Field Pvogrammable Gate Arrays,FPG A)实现系统功能.1 系统组成及引脚功能红外遥控器的控制系统由发射和接收两部分组成.发射部分主要包括:时序产生电路、键盘扫描电路、键编码电路、键值消抖电路、客户码生成电路、键值和客户码译码及存储电路、REM 输出电路等模块.发射部分设计框图如图1所示,其主要引脚功能上海理工大学学报第26卷 第2期J.U niversity of Shanghai fo r Science and T echnolog yV ol.26 No.2 2004如下:C LK:系统时钟的输入端,接455k Hz 时钟信号;CCS:客户码输入端;KI/O 0~KI/O 7:客户码输入及键输出引脚;KI 0~KI 3:键输入引脚;REM:发送码输出引脚;LMP:有发送码输出时,LMP 为高电平.接收部分主要包括:时序产生电路、接收信号的解调电路、解码电路、有效键的检测电路、客户码输出电路及键值输出电路等模块.接收部分设计框图如图2所示,其主要引脚功能如下:CLK:系统时钟的输入端,接455kHz 时钟信号;SIN:接收信号的输入端;K 0~K 7:键值输出端;C 0~C 7:客户码输出端.图1 发送电路总体设计框图Fig.1 Block diagram of the emittingcircuit图2 接收电路总体设计框图Fig.2 Block diagram of the receiving circuit2 系统设计红外遥控发射部分电路的实现原理是通过计数器产生键扫描信号,键编码电路检测到有键按下后产生键值.由客户码生成电路产生客户码,通过译码电路将客户码和键值译码产生32位的编码,由REM 输出电路加载38kHz 的载频信号,并由REM 引脚输出,同时LMP 引脚的输出由低电平转为高电平.接收部分的实现和发送部分相对应,主要由时序电路产生38kHz 的接收频率,直接将38kHz 的调190上海理工大学学报2004年第26卷制信号解调为基带信号,提供给解码电路进行解码操作.其基本工作过程为:当解调电路接收到38kHz 的信号时,输出一控制信号给解码电路,解码电路的输出,一方面提供给键值和客户码输出电路,另一方面提供给有效码检测电路进行检测.键值和客户码输出电路在检测电路输出有效之前处于高阻态.一旦检测到有效的接收键,则开启键和客户码输出电路将客户码和键值输出.由于发送和接收两部分的功能在实现上有类似之处,本文以下部分主要介绍红外遥控发送功能的设计实现.3 发送控制的设计3.1 时序产生电路由于自由计数器的位数与合成时占用资源成正比的关系,故采用10位计数器作为自由计数器.对系统时钟455kHz 进行分频,产生系统中各种需要的频率和控制时序.主要频率有:a .38kHz 的载频信号,是455kHz 信号的12分频.b .0.56ms 、1.125ms 和2.25ms 时钟信号.c .键扫描信号采用9ms 的时钟信号,是2.25ms 的时钟信号的4分频.3.2 键扫描电路键扫描电路的作用是提供4 8键的扫描信号,并负责把32个键的状态储存起来.当有键按下时产生按键请求信号KEY -req,为减少系统功耗,当有键按下时才使分频器的各种频率信号送出,供其他模块动作,无键按下时只允许分频器送出键扫描信号.键扫描信号变化规律为00000001 00000010 00000100 00001000 00010000 00100000 010000000 10000000 00000001周而复始,并从引脚KI/O 7、KI/O 6、KI/O 5、KI/O 4、KI/O 3、KI/O 2、KI/O 1、KI/O 0输出.4位返回值从引脚KI 0、KI 1、KI 2、KI 3扫入,并由8个4位的锁存器依次将键的状态值锁存,以提供给键编码电路进行编码.3.3 键编码电路及消抖这部分电路的功能是读入按键的状态码,并检测是否有多键按下,产生相应的状态标志.对于多键按下的情况采用N 值轮回的方式处理.系统如果没有多键按下则进行编码动作,生成待发送的键值.在此过程中还产生键值的装载信号SHIFTLOAD 、键编码电路的复位信号CNT -CLR 和消抖电路的控制信号.键值消抖电路的输出决定编码电路的有效输出.消抖原理是采用两次生成的键值相等即作为有效键.键编码电路在消抖后产生键值KEY [7..0]、键值的反码/KEY[7..0]以及键有效状态信号.3.4 客户码生成电路客户码生成电路的作用是读入上拉电阻和二极管的连接状态,生成客户码并锁存等待译码.图3为上拉电阻和二极管的连接状态的一个实例.上拉电阻的状态在刚上电时即读入8位寄存器中,刚上电时引脚KI/O 7、KI/O 6、KI/O 5、KI/O 4、KI/O 3、KI/O 2、KI/O 1、KI/O 0作为输入引脚,在3位计数器输出第一个COUT 的下沿将上拉电阻状态锁存.此后的操作中,引脚KI/O 7、KI/O 6、KI/O 5、KI/O 4、KI/O 3、KI/O 2、KI/O 1、KI/O 0均作为输出引脚.二极管的连接状态的读入,是在时钟脉冲的控制下依次从KI/O 0~KI/O 7引脚输出状态1,CCS 接收端在移位时钟作用下,依次从CCS 引脚移入二极管的连接状态.二极管的连接状态表示为:未接二极管的引脚状态移入0;接二极管的引脚状态移入1.移满8位后即把状态值锁存,待译码电路译码.在设计中引脚CCS 、KI 0~KI 3、KI/O 0~KI/O 7配置内部下拉电阻.图3 客户码设置电路Fig.3 Circuit for c ustomer code setting3.5 键值和客户码译码及存储电路将已经锁存的键值和客户码翻译成可发送的编码,并储存用于发送.这部分电路由键值及客户码译码电路和REPEAT 码生成电路组成,并包括了两种码制的输出控制.键值和客户码译码电路的实现原理,是分别用两种频率(455kHz 的256分频和512分频),对频率为455kHz 的512分频,占空比为1/4的信号进行采样,当待译码为1时采样得到的信号为1000,待译码为0时采样得到的信号为10,并依次装入128位的移位寄存器.另外,在移位过程中,需要对移位位数计数,当移位寄存器的移位个数移满128位时停止移位,同时启动客户码和键值发送电路,开始发送LEADER CODE(9ms 的1和4ms 的0),紧接着发送客户码和键值(共108ms).发送结191 第2期佟国香等:红外遥控器控制系统的VHDL 设计与FPGA 实现束后,键仍然处于按下状态,则发送REPAET 码.3.6 REM(遥控码)输出电路REM 输出电路主要实现发送码的调制.电路原理是采用了一个2路的开关电路,键值和客户码译码及存储电路的输出作为2路开关的选择端.当键值和客户码译码及存储电路的输出为1时,发送载频信号;当键值和客户码译码及存储电路的输出为0时,REM 输出为0.REM 输出波形如图4所示. 图中!状态包括:头标志(9ms 的1和4ms 的0)、客户码和键值及停止位.∀状态为:重复码(9ms 的1和2.25ms 的0以及停止位0.56ms 的1).图4 REM 输出波形Fig.4 REM output waveform产生红外发射码的时序仿真图形见图5.图中的REM 输出为加载载频信号之后的输出.图5 REM 输出时序仿真Fig.5 Simulation of REM output4 结 论采用VHDL 语言设计的红外遥控器的控制系统,通过下载到FPG A,外加红外驱动和放大电路可以实现红外遥控功能.用此种方法设计硬件电路,将有助于提高开发的效率,增加已有开发成果的可继承性以及缩短开发时间.参考文献:[1] 侯伯亨,顾新.VHDL 硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,1998,4~7.[2] [美]Skahill K.可编程逻辑系统的VHDL 设计技术[M].朱明程,孙普译.南京:东南大学出版社,1998,5~8.[3] 李建华.实用遥控器原理与制作[M].北京:人民邮电出版社,1996,64~67.192上海理工大学学报2004年第26卷。

基于VHDL的红外遥控编译码器毕业论文.

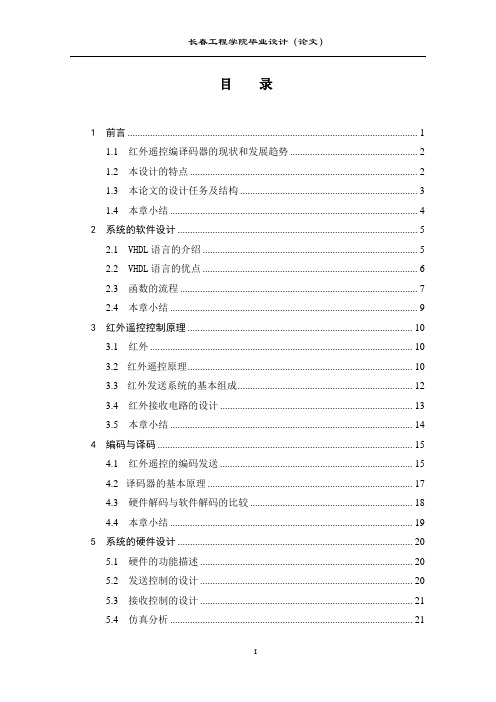

目录1 前言 (1)1.1 红外遥控编译码器的现状和发展趋势 (2)1.2 本设计的特点 (2)1.3本论文的设计任务及结构 (3)1.4 本章小结 (4)2 系统的软件设计 (5)2.1 VHDL语言的介绍 (5)2.2 VHDL语言的优点 (6)2.3 函数的流程 (7)2.4本章小结 (9)3 红外遥控控制原理 (10)3.1 红外 (10)3.2红外遥控原理 (10)3.3红外发送系统的基本组成 (12)3.4 红外接收电路的设计 (13)3.5 本章小结 (14)4 编码与译码 (15)4.1 红外遥控的编码发送 (15)4.2译码器的基本原理 (17)4.3 硬件解码与软件解码的比较 (18)4.4 本章小结 (19)5 系统的硬件设计 (20)5.1 硬件的功能描述 (20)5.2 发送控制的设计 (20)5.3 接收控制的设计 (21)5.4 仿真分析 (21)5.5本章小结 (22)6 总结 (23)参考文献 (24)致谢 (25)附录 (26)1前言目前市面上的编译码器多种多样,而其主要用于家电设备及一些电子产品当中,而红外遥控编译码器也是极其常见的,然而技术和经济的发展使得数字化趋势越来越强烈,很多时候已经不能满足用户要求。

红外遥控编译码器就是在普通编译码器的基础上,应市场需求而产生的,它能控制不同种类的设备,并且操作方便,深受顾客的欢迎,这也决定了红外遥控编译码器具有广阔的应用前景[9]。

红外遥控由于其发射和接收方便、结构简单、成本低、可靠性较高, 因而早已在家用电器中得到广泛应用。

目前在智能仪器和工业控制系统中的应用也越来越广泛。

红外遥控本质属于红外信息传输的一种应用形式。

红外传输大体分为数据的传输和控制信息(指令) 的传输二类。

数据的传输一般来说传输的信息量会较大, 因此一般会要求有较高的传输速度, 对于可靠性的要求则针对数据的具体应用而异, 在计算机、PDA 等设备上采用的IRDA 界面就是这种应用的典型代表。

基于FPGA的红外线型学习遥控器

重庆大学本科生课外实践技术报告项目名称:基于FPGA的学习型红外遥控器设计学院:专业:指导老师:实验日期:引言随着人们生活水平的提高,家用电器的种类增多,红外遥控器的种类也随之增加,不同种类的遥控器之间由于采用的编码格式不同,使得不同产品的遥控器不能相互兼容,用户在使用的过程中容易产生混乱,给人们的生活带来诸多不便。

针对这一现况,万能遥控器便应需出现了,目前主要分为两种类型,编码型和学习型。

编码型万能遥控器需要各大电器制造商生产的遥控器的控制码编码格式,使用时选定相应机型,遥控器便可提取出其编码,再和38k的载波进行ASK 调制便可驱动红外线发射管进行控制信号发射了,但其显著的缺点是使用时需要查询冗长的机器型号手册。

相对之下另外一种学习型的万能遥控器机理就比较简单了,其对不同遥控器发出的信号(解调后的信号)进行记录,待控制时调用出存储的信号对载波进行调制,便可驱动红外线发射管发射红外线对设备进行控制了。

通过对比这两种万能遥控器的设计方案可知,相对编码型遥控器,自主学习型遥控器原理简单,实现较为方便。

基于此本文尝试着设计了一款基于FPGA的红外线学习型遥控器,主要由FPGA控制模块、红外线接收模块、红外线发射模块和存储模块组成。

在本文中详细的给出了设计的原理、技术方案、软硬件的实现过程等,并在附录中给出了各单元电路图、主程序和仿真电路图。

1设计方案与指标1.1设计原理简介基于FPGA制作一个红外遥控器,并可通过程序控制记忆按键功能,达到遥控器的自主学习功能,其实现原理框图如下:图1系统框图由原理框图可知,本设计主要由5个部分组成,FPGA控制器、红外线发射器、红外线接收器、学习遥控指示灯和操作键组成。

遥控器自主学习工作进程如下:一、红外线接收器接收红外信号;二、红外接收模块对信号进行放大、检波、整形,解调出基带信号;三、FPGA控制器将解调出的信号的高、低电平的时间宽度进行储存;四、当要发射红外信号时,从储存区中还原出相应的红外遥控编码,以其对38kHz的载波信号进行调制;五、调制出的控制信号驱动红外发光二极管发射红外信号,从而实现对设备的控制。

基于FPGA的红外遥控彩灯控制器的设计

基于FPGA的红外遥控彩灯控制器的设计严丰;陈学英【期刊名称】《现代电子技术》【年(卷),期】2015(000)019【摘要】A multi⁃mode coloured⁃lantern display control system with infrared remote control based on FPGA was designed, which has the advantages of low⁃cost,reliable performance and excellent scalability. The circuit structure of the system is intro⁃duced in detail. A construction method of infrared remote control system is put forward,which takes the infrared emission chip SC9148B and peripheral circuit as the transmitter,the integrated infrared chip HS0038B as the receiver,and FPGA as the core controller. This system was verified by time sequence simulation and FPGA logic validation. The actual results show that thisde⁃sign can realize the functions of decoding control of infrared remote control signal for the coloured lanterns,storage and decod⁃ing of the key value signal,and multi⁃mode coloured⁃lantern display.%设计一种基于现场可编程逻辑器件FPGA的红外遥控彩灯多模式显示控制系统。

红外编码与解码的VHDL实现

红外编码与解码的VHDL实现红外遥控在家电中应用广泛,采用VHDL语言设计红外遥控器的控制系统,该系统通过了实时仿真的验证,可现实键值读入,红外发射码的生成及发送功能。

电路模块的程序代码可重复使用,可方便的嵌入到各类需要红外遥控控制器的嵌入式系统中,本次窗帘的遥控器电路就是用VHDL语言编写,并下载至CPLD中执行。

红外遥控作为一种单向红外通讯技术,因其具有性能稳定、使用方便以及成本低廉等特点,已经在消费电器中得到了普遍的应用。

随着对电器产品智能化和使用便利性要求的进一步提高,红外遥控的应用已经从传统家电领域向智能设备等新领域扩展。

由于集成电路制造工艺的设计水平的不断提高,将此类奋力电路功能集成到嵌入式系统中已成为可能。

本文设计脉冲信号调制采用了PPM方式,红外遥控系统采用了VHDL语言编写,来实现该电路的功能。

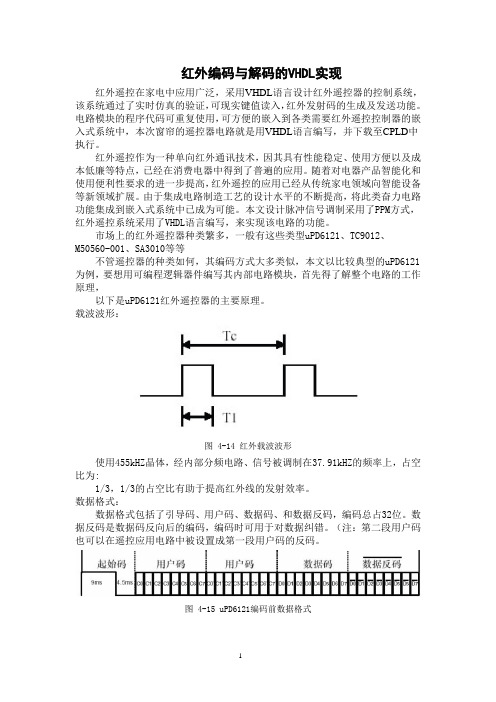

市场上的红外遥控器种类繁多,一般有这些类型uPD6121、TC9012、M50560-001、SA3010等等不管遥控器的种类如何,其编码方式大多类似,本文以比较典型的uPD6121为例,要想用可编程逻辑器件编写其内部电路模块,首先得了解整个电路的工作原理,以下是uPD6121红外遥控器的主要原理。

载波波形:图 4-14 红外载波波形使用455kHZ晶体,经内部分频电路、信号被调制在37.91kHZ的频率上,占空比为:1/3,1/3的占空比有助于提高红外线的发射效率。

数据格式:数据格式包括了引导码、用户码、数据码、和数据反码,编码总占32位。

数据反码是数据码反向后的编码,编码时可用于对数据纠错。

(注:第二段用户码也可以在遥控应用电路中被设置成第一段用户码的反码。

图 4-15 uPD6121编码前数据格式使用455kHZ晶体时各代码所占用的时间图 4-16 uPD6121编码后数据格式位定义:用户码或者数据码中的每一位可以是位‘0’,也可以是位‘1’。

区分‘0’和‘1’是利用脉冲的时间间隔来区分,这种编码方式称为脉冲位置调制方式,英文简称PPM。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

文章编号:1007-6735(2004)02-0189-04收稿日期:2003-07-27作者简介:佟国香(1968-),女,讲师.红外遥控器控制系统的VHDL 设计与FPGA 实现佟国香1, 孙国强1, 李广军2(1.上海理工大学计算机工程学院,上海 200093; 2.电子科技大学通信工程学院,成都 610058)摘要:采用VHDL 语言设计了红外遥控器的控制系统.该系统通过了实时仿真和验证,并下载到FPGA 中执行,可实现键值及客户码的读入、红外发射码的生成及发送等功能.电路模块的程序代码可重复使用,可方便地嵌入到各类需要红外遥控控制的嵌入式系统中.关键词:VHDL 设计;FPGA;红外遥控器中图分类号:TN 876 文献标识码:AVHDL design and FPGA implementation of the controlsystems in infrared remote controllerTONG Guo xiang 1, SUN Guo qiang 1, LI Guang jun 2(1.College of Compu ter Engineerin g,Un iver sity of Shan ghai for Scien ce an d Technology,Shan ghai 200093,China ;2.School of Com m un ication an d In form ation En gin eering,University of Electron ic Scienceand Technology of China ,Chen gdu 610058,Chin a )Abstract:The co ntrol systems in an infrared remo te controller are designed using VHDL.The VHDL d e sign is verified throu gh simu lation and imp lem ented using FPGA.The System functions includ e key data cod es and custom cod es reading,infrared em itting code generating and emitting,etc.The VHDL cod es of the system s are reusable and can b e emb edd ed in systems requiring infrared remo te control.Key words:VHDL desi gn ;FPGA ;Inf r a r edr emot e con tr ol红外遥控作为一种单向红外通讯技术,因其具有性能稳定、使用方便以及成本低廉等特点,已经在消费类电器中得到普遍的应用.随着对电器产品的智能化和使用便利性要求的进一步提高,红外遥控的应用已开始从其传统的家用电器领域向智能设备等新领域扩展[1].由于集成电路制造工艺和设计水平的不断提高,将此类传统的分立电路功能集成到嵌入式的系统中已成为可能[2,3].本文根据嵌入系统的要求进行了红外遥控器控制系统的设计.设计中脉冲信号调制采用了PPM 方式,红外遥控器的控制系统采用了超高速集成电路硬件描述语言(VeryHigh speed integrated circuit hardware Description Language,VHDL),并通过现场编程门阵列器件(Field Pvogrammable Gate Arrays,FPG A)实现系统功能.1 系统组成及引脚功能红外遥控器的控制系统由发射和接收两部分组成.发射部分主要包括:时序产生电路、键盘扫描电路、键编码电路、键值消抖电路、客户码生成电路、键值和客户码译码及存储电路、REM 输出电路等模块.发射部分设计框图如图1所示,其主要引脚功能上海理工大学学报第26卷 第2期J.U niversity of Shanghai fo r Science and T echnolog yV ol.26 No.2 2004如下:C LK:系统时钟的输入端,接455k Hz 时钟信号;CCS:客户码输入端;KI/O 0~KI/O 7:客户码输入及键输出引脚;KI 0~KI 3:键输入引脚;REM:发送码输出引脚;LMP:有发送码输出时,LMP 为高电平.接收部分主要包括:时序产生电路、接收信号的解调电路、解码电路、有效键的检测电路、客户码输出电路及键值输出电路等模块.接收部分设计框图如图2所示,其主要引脚功能如下:CLK:系统时钟的输入端,接455kHz 时钟信号;SIN:接收信号的输入端;K 0~K 7:键值输出端;C 0~C 7:客户码输出端.图1 发送电路总体设计框图Fig.1 Block diagram of the emittingcircuit图2 接收电路总体设计框图Fig.2 Block diagram of the receiving circuit2 系统设计红外遥控发射部分电路的实现原理是通过计数器产生键扫描信号,键编码电路检测到有键按下后产生键值.由客户码生成电路产生客户码,通过译码电路将客户码和键值译码产生32位的编码,由REM 输出电路加载38kHz 的载频信号,并由REM 引脚输出,同时LMP 引脚的输出由低电平转为高电平.接收部分的实现和发送部分相对应,主要由时序电路产生38kHz 的接收频率,直接将38kHz 的调190上海理工大学学报2004年第26卷制信号解调为基带信号,提供给解码电路进行解码操作.其基本工作过程为:当解调电路接收到38kHz 的信号时,输出一控制信号给解码电路,解码电路的输出,一方面提供给键值和客户码输出电路,另一方面提供给有效码检测电路进行检测.键值和客户码输出电路在检测电路输出有效之前处于高阻态.一旦检测到有效的接收键,则开启键和客户码输出电路将客户码和键值输出.由于发送和接收两部分的功能在实现上有类似之处,本文以下部分主要介绍红外遥控发送功能的设计实现.3 发送控制的设计3.1 时序产生电路由于自由计数器的位数与合成时占用资源成正比的关系,故采用10位计数器作为自由计数器.对系统时钟455kHz 进行分频,产生系统中各种需要的频率和控制时序.主要频率有:a .38kHz 的载频信号,是455kHz 信号的12分频.b .0.56ms 、1.125ms 和2.25ms 时钟信号.c .键扫描信号采用9ms 的时钟信号,是2.25ms 的时钟信号的4分频.3.2 键扫描电路键扫描电路的作用是提供4 8键的扫描信号,并负责把32个键的状态储存起来.当有键按下时产生按键请求信号KEY -req,为减少系统功耗,当有键按下时才使分频器的各种频率信号送出,供其他模块动作,无键按下时只允许分频器送出键扫描信号.键扫描信号变化规律为00000001 00000010 00000100 00001000 00010000 00100000 010000000 10000000 00000001周而复始,并从引脚KI/O 7、KI/O 6、KI/O 5、KI/O 4、KI/O 3、KI/O 2、KI/O 1、KI/O 0输出.4位返回值从引脚KI 0、KI 1、KI 2、KI 3扫入,并由8个4位的锁存器依次将键的状态值锁存,以提供给键编码电路进行编码.3.3 键编码电路及消抖这部分电路的功能是读入按键的状态码,并检测是否有多键按下,产生相应的状态标志.对于多键按下的情况采用N 值轮回的方式处理.系统如果没有多键按下则进行编码动作,生成待发送的键值.在此过程中还产生键值的装载信号SHIFTLOAD 、键编码电路的复位信号CNT -CLR 和消抖电路的控制信号.键值消抖电路的输出决定编码电路的有效输出.消抖原理是采用两次生成的键值相等即作为有效键.键编码电路在消抖后产生键值KEY [7..0]、键值的反码/KEY[7..0]以及键有效状态信号.3.4 客户码生成电路客户码生成电路的作用是读入上拉电阻和二极管的连接状态,生成客户码并锁存等待译码.图3为上拉电阻和二极管的连接状态的一个实例.上拉电阻的状态在刚上电时即读入8位寄存器中,刚上电时引脚KI/O 7、KI/O 6、KI/O 5、KI/O 4、KI/O 3、KI/O 2、KI/O 1、KI/O 0作为输入引脚,在3位计数器输出第一个COUT 的下沿将上拉电阻状态锁存.此后的操作中,引脚KI/O 7、KI/O 6、KI/O 5、KI/O 4、KI/O 3、KI/O 2、KI/O 1、KI/O 0均作为输出引脚.二极管的连接状态的读入,是在时钟脉冲的控制下依次从KI/O 0~KI/O 7引脚输出状态1,CCS 接收端在移位时钟作用下,依次从CCS 引脚移入二极管的连接状态.二极管的连接状态表示为:未接二极管的引脚状态移入0;接二极管的引脚状态移入1.移满8位后即把状态值锁存,待译码电路译码.在设计中引脚CCS 、KI 0~KI 3、KI/O 0~KI/O 7配置内部下拉电阻.图3 客户码设置电路Fig.3 Circuit for c ustomer code setting3.5 键值和客户码译码及存储电路将已经锁存的键值和客户码翻译成可发送的编码,并储存用于发送.这部分电路由键值及客户码译码电路和REPEAT 码生成电路组成,并包括了两种码制的输出控制.键值和客户码译码电路的实现原理,是分别用两种频率(455kHz 的256分频和512分频),对频率为455kHz 的512分频,占空比为1/4的信号进行采样,当待译码为1时采样得到的信号为1000,待译码为0时采样得到的信号为10,并依次装入128位的移位寄存器.另外,在移位过程中,需要对移位位数计数,当移位寄存器的移位个数移满128位时停止移位,同时启动客户码和键值发送电路,开始发送LEADER CODE(9ms 的1和4ms 的0),紧接着发送客户码和键值(共108ms).发送结191 第2期佟国香等:红外遥控器控制系统的VHDL 设计与FPGA 实现束后,键仍然处于按下状态,则发送REPAET 码.3.6 REM(遥控码)输出电路REM 输出电路主要实现发送码的调制.电路原理是采用了一个2路的开关电路,键值和客户码译码及存储电路的输出作为2路开关的选择端.当键值和客户码译码及存储电路的输出为1时,发送载频信号;当键值和客户码译码及存储电路的输出为0时,REM 输出为0.REM 输出波形如图4所示. 图中!状态包括:头标志(9ms 的1和4ms 的0)、客户码和键值及停止位.∀状态为:重复码(9ms 的1和2.25ms 的0以及停止位0.56ms 的1).图4 REM 输出波形Fig.4 REM output waveform产生红外发射码的时序仿真图形见图5.图中的REM 输出为加载载频信号之后的输出.图5 REM 输出时序仿真Fig.5 Simulation of REM output4 结 论采用VHDL 语言设计的红外遥控器的控制系统,通过下载到FPG A,外加红外驱动和放大电路可以实现红外遥控功能.用此种方法设计硬件电路,将有助于提高开发的效率,增加已有开发成果的可继承性以及缩短开发时间.参考文献:[1] 侯伯亨,顾新.VHDL 硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,1998,4~7.[2] [美]Skahill K.可编程逻辑系统的VHDL 设计技术[M].朱明程,孙普译.南京:东南大学出版社,1998,5~8.[3] 李建华.实用遥控器原理与制作[M].北京:人民邮电出版社,1996,64~67.192上海理工大学学报2004年第26卷。