FPGA设计中关键问题的研究

FPGA设计课程教学方法的研究

的首选。近年来 随着 F G C L P A/ P D等可编程器件 的广泛 应用,

社会对熟练掌握可编程器件 开发 的高素质大学 毕业生需 求量在

逐 年 增加 。为 了适应 社 会 需 求 ,很 多 高 校开 设 F G C L 等 P A/ P D

1硬 件描述 语言 的选择 .

匪 互

区互固

一 区囹

一 匝

一 I

—

代I 码

目前,国 际最流 行 的是 成 为 I E E E标准 的两 种 硬件 描 述 语 言 VHDL和 V rlg ei HD o L。两 种 HD L各 具 特 色,VHD L 的培 训才能 基本 掌握 设计 技术 ,多用于军 事及 航天 等领域 ;

硬件 描述语言设计之初是为了进 行硬件仿真 ,即其 中的一

与可编程逻辑 器件设计 相关的课程 。由于起步较 晚,目前该类 部 分语 句是可 以对 应生成相 应的硬件结 构,就是可综 合语 句 , 课程还 不够成 熟,但 总体上教学可 以分为两个 部分,即基础理 与之相对 ,不可综合的语 句并没有相 应的硬件 结构。作 为硬件 论部分和 实验 部分。笔者通 过总结近 年来的教学经验提 出了几 设计 的初学者区别 可综合语 句和不可综合 语句对于其进行有效

CP E E中国 电力教育

磊面

D I O 编码 : 03 6 / . s . 0 - 0 92 1.80 9 1 .9 9ji n 1 7 0 7 . 0 1 .5 s 0 0

FG P A设计课程教 学方法的研究

冯 柳

摘要 : P A设计课 程是- I实践性很 强的电 FG -' ] 子系专业课 ,包括 FG P A设计的理论课程和实验课程 两部

基于FPGA的嵌入式系统设计与开发研究

基于FPGA的嵌入式系统设计与开发研究嵌入式系统是指具有特定功能的计算机系统,被嵌入到其他设备中以完成特定任务。

嵌入式系统的设计与开发在现代技术领域中具有重要的地位,其中基于可编程逻辑器件(FPGA)的嵌入式系统尤为重要。

本文将探讨基于FPGA的嵌入式系统设计与开发的研究,并分析其在实际应用中的价值与挑战。

首先,我们需要了解FPGA是什么。

FPGA是一种基于可编程逻辑门阵列(PLA)的集成电路芯片,具有灵活性和可编程性,可以通过配置器件中的逻辑门和连接资源来实现各种硬件功能。

相比于传统的固定功能集成电路,FPGA具有更高的性能、灵活性和可靠性,因此广泛应用于嵌入式系统设计与开发中。

基于FPGA的嵌入式系统设计与开发的研究主要涉及以下几个方面:硬件设计、嵌入式软件开发、系统集成与验证。

在硬件设计方面,基于FPGA的嵌入式系统需要首先确定系统的需求和功能,然后进行硬件结构设计。

硬件设计主要包括逻辑设计、电路设计、时序设计等。

通过使用硬件描述语言(HDL)如VHDL或Verilog来描述系统的行为和结构,设计师可以实现各种硬件模块和接口,并通过逻辑综合工具生成对应的电路网表。

随后,通过布局布线工具将电路网表映射到FPGA的逻辑单元和资源中,最终生成比特流文件(Bitstream),供FPGA配置器件使用。

嵌入式软件开发是基于FPGA的嵌入式系统设计与开发中的另一个重要方面。

嵌入式软件开发主要涉及嵌入式处理器的选择与集成、固件编程、设备驱动程序的开发等。

在嵌入式系统设计中,使用处理器核心与FPGA逻辑单元进行协同工作,处理器核心负责控制和高层次算法处理,FPGA逻辑单元负责实时数据处理和硬件加速,使得系统具有较高的性能和吞吐量。

通过使用嵌入式软件开发工具如Eclipse等,设计师可以编写和调试嵌入式软件,并将其烧录到FPGA中。

系统集成与验证是保证基于FPGA的嵌入式系统正常运行的关键步骤。

系统集成主要涉及将各个硬件模块、嵌入式软件和外设等组合到一起,并实现合适的通信和数据交换机制。

基于FPGA嵌入式系统的研究与应用

半 导 体 工 业 和 嵌 入 式 领 域 所 面 临 的 主 要 课 题 之 一

1 P F GA 嵌 入 式 系统

1 1 基 本 原 理 .

就 是 设 计 片 上 系 统 。 上 系 统 可 以在 单 芯 片 上 集 成 嵌 入 片

式 C U、 S 、 储 器 和 其 他 控 制 功 能 , 而 可 大 大 降 低 P DP 存 从

产 品 的 开 发 周 期 。 高 产 品 的安 全 性 、 靠 性 , 小 产 品 提 可 缩

的 物 理 尺 寸 , 低 成 本【 。 片 上 系 统 :1可 以包 含 : 处 降 l 1 (1 微

F G 其 技 术 的关 键 在 于 用 户 可 编 程 性 , 用 F G PA 利 PA 作 为 高 度 并 行 处 理 器 件 来 设 计 嵌 入 式 系 统 可 以提 供 高 信 号 处 理 的 能 力 , 足 样 机 开 发 周 期 短 和 产 品 上 市 快 的 满

了 利 用 F G 实 现 嵌 入 式 系统 的 基 本 原 理 和 设 计 方 法 ,重 点 探 讨 了 其 结 构 的 转 换 难 点 。 通 过 具 体 应 PA

用 , 析 了乘 法 累加 驱 动 滤 波 器 的 实现 原 理 和 处 理 过 程 , 计 了 F G 嵌 入 式 系 统 的 具 体 实 现 方 式 。 分 设 PA

FPGA设计中的资源管理优化研究

FPGA设计中的资源管理优化研究随着数字电路的复杂度和功能需求的增加,数字系统设计的复杂性也在不断提高。

在数字系统设计中,FPGA(现场可编程门阵列)作为一种可编程硬件,为设计人员提供了灵活性和高性能。

然而,在 FPGA 设计过程中,资源管理一直是一个重要的问题。

资源的合理利用和优化对于 FPGA 设计的性能和功耀耗效率至关重要。

在 FPGA 设计中,资源主要包括逻辑资源、存储资源和时序资源。

逻辑资源指的是FPGA中的逻辑单元(Look-Up Table)、寄存器等,存储资源主要包括片上存储器(Block RAM)、分布式RAM等,而时序资源则指的是时钟分配、延迟等。

资源的合理管理和优化可以有效地提高设计的性能和节约资源开销。

一种常见的资源管理优化方法是通过资源共享和重用来减少资源占用。

资源共享包括逻辑资源的共享、存储资源的共享,以及时序资源的共享。

通过合理设计模块和调度算法,可以将多个模块中的共性部分抽取出来作为一个子模块,从而减少资源占用。

资源重用则是指在设计过程中尽可能重复利用同一种资源,例如将多个模块中相同的功能单元直接拷贝,避免重复实现相同功能。

另外,资源管理还需要考虑到设计的并行性和时序约束。

在 FPGA 设计中,设计的并行性会影响资源的分配和利用效率。

设计人员需要合理划分模块,并对模块进行并行调度,以提高设计的效率。

同时,时序约束也是资源管理的重要考量因素。

设计人员需要根据时序约束来调整资源的分配,保证设计的正确性和稳定性。

除了资源共享和重用,还可以通过优化算法和工具来实现资源管理优化。

例如,使用综合工具进行综合优化,可以帮助设计人员合理利用资源,并在性能和资源开销之间找到平衡点。

另外,基于约束优化的方法也可以用来优化资源管理,通过对设计的约束条件进行调整,达到资源最优化的目的。

总的来说,在 FPGA 设计中,资源管理的优化是一个复杂而关键的问题。

设计人员需要充分了解FPGA 架构和资源分配规则,同时结合设计的要求和约束条件,采用合适的资源管理方法和优化策略。

《基于FPGA的多核处理器系统的研究与设计》范文

《基于FPGA的多核处理器系统的研究与设计》篇一一、引言随着科技的快速发展,处理器性能的需求不断提升,传统单核处理器已经难以满足日益增长的计算需求。

因此,多核处理器系统成为了研究的热点。

本文以基于FPGA(现场可编程门阵列)的多核处理器系统为研究对象,对其进行了详细的研究与设计。

二、研究背景及意义FPGA作为一种可编程的硬件设备,具有高度的并行性、灵活性和可定制性,因此被广泛应用于高性能计算、信号处理等领域。

而多核处理器系统则通过集成多个处理器核心,实现了更高的计算性能和更快的处理速度。

将FPGA和多核处理器系统相结合,可以构建出高性能、高灵活性的多核处理器系统,对于提高计算性能、降低功耗、增强系统稳定性等方面具有重要的意义。

三、FPGA多核处理器系统的设计(一)系统架构设计基于FPGA的多核处理器系统主要由多个FPGA芯片组成,每个FPGA芯片上集成了多个处理器核心。

系统采用共享内存的方式,实现了各个处理器核心之间的数据交换和通信。

此外,系统还包含了控制模块、接口模块等部分,以实现系统的整体控制和外部接口的连接。

(二)处理器核心设计处理器核心是FPGA多核处理器系统的核心部分,其设计直接影响到整个系统的性能。

在处理器核心设计中,需要考虑指令集设计、数据通路设计、控制单元设计等方面。

指令集设计需要考虑到指令的兼容性、可扩展性和执行效率;数据通路设计需要考虑到数据的传输速度和带宽;控制单元设计则需要考虑到处理器的控制流程和时序。

(三)系统通信设计系统通信是FPGA多核处理器系统中非常重要的一部分,它涉及到各个处理器核心之间的数据交换和通信。

在系统通信设计中,需要考虑到通信协议的设计、通信接口的选择、通信速度和带宽等方面。

常用的通信协议包括总线协议、消息传递协议等,需要根据具体的应用场景进行选择和设计。

四、系统实现与测试(一)硬件实现在硬件实现阶段,需要根据设计要求选择合适的FPGA芯片和开发工具,完成电路设计和布局布线等工作。

FPGA设计中的时序优化与资源分配方法研究

FPGA设计中的时序优化与资源分配方法研究随着半导体技术的不断发展,可编程逻辑器件(FPGA)在数字电路的设计与实现中扮演着重要的角色。

然而,当设计复杂的电路时,时序约束与资源分配成为了一个具有挑战性的问题。

本文将重点介绍FPGA设计中的时序优化与资源分配方法的研究和应用。

一、时序优化方法时序优化是指通过改进电路中的逻辑路径的延迟以满足时序约束的要求。

下面介绍几种常见的时序优化方法:1. 管理时钟延迟:时钟信号在FPGA设计中起着至关重要的作用。

对于高性能电路设计来说,时钟信号的延迟是限制电路频率和性能的关键因素之一。

因此,通过对时钟网络进行优化,可以显著提高FPGA电路的性能。

一种常见的方法是通过合理地布局和路由时钟网络,减少时钟传播延迟并优化数据路径,从而改善电路的性能。

2. 优化数据路径延迟:数据路径是FPGA电路中数据传输的关键部分。

通过优化数据路径可以减少逻辑门延迟、寄存器延迟和布线延迟等因素对整体电路时序的影响。

一种常见的优化方法是在关键路径上引入流水线技术,将数据传输划分为多个阶段,从而增加并行计算能力和提高电路的工作频率。

3. 最小延迟布线:布线是指将逻辑电路中的门、寄存器和其他元件连接起来的过程。

最小延迟布线是为了最大限度地减少布线路径中的延迟,从而达到时序优化的目的。

在布线过程中采用合理的布线算法和技术,将关键路径正确地连接起来,并通过适当的电路拓扑结构和布线规则来优化电路性能。

二、资源分配方法资源分配是指将FPGA芯片上的资源合理地分配给电路中的各个功能模块,以满足设计需要。

下面介绍几种常见的资源分配方法:1. 确定资源需求:在进行资源分配之前,需要明确电路中各个模块的资源需求。

通过对电路的功能进行分析,确定所需的逻辑门、寄存器、DSP模块等资源数量,以便合理地分配FPGA芯片上的资源。

2. 资源共享:资源共享是一种常见的资源分配方法,通过将多个模块共享FPGA上的同一个资源,以提高资源的利用率。

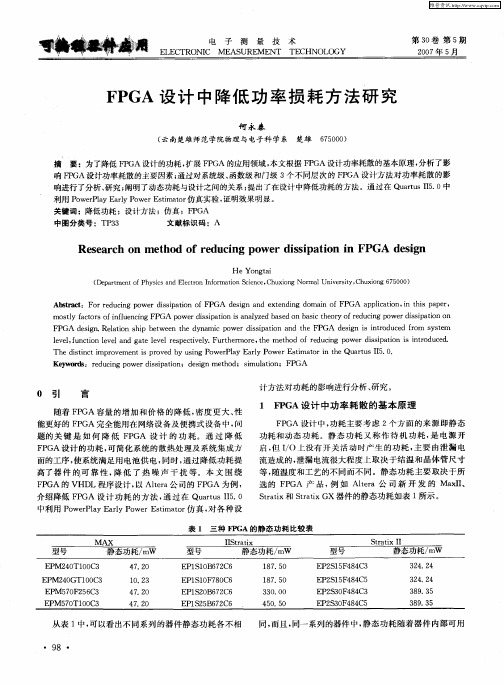

FPGA设计中降低功率损耗方法研究

Th it c mp o e n sp o e yu igPo r a ryP we t t ri h a ts15 0 edsi ti r v me ti r v db sn wePlyEa l o rEsi o n teQu ru 1 . . n ma

Ke wo d : r d cn o rd s i a i n d sg t o y r s e u i g p we isp t ; e in me h d; smu a in; FP o i lt o GA

1 FG P A设计 中功率耗散 的基本原理

F GA 设计 中 , P 功耗 主要 考 虑 2个 方 面 的来 源 即静 态

功耗 和动 态 功耗 。静 态 功 耗 又 称 作 待 机 功 耗 , 电 源 开 是

维普资讯

峭

ETN MS量T日N0 LRI 子 RE C0G E 0电E ENTHLY C CA M 测 技术 U

第7 月 2年5 0计 中降低 功 率 损 耗 方 法 研 究 P

何永 泰

( 云南楚雄 师范学院物理与 电子科 学 系 楚雄 650) 7 0 0

0 7 1

言

计方法对功耗的影响进行分析 、 研究。

随着 F G P A容 量 的增 加 和 价 格 的降 低 , 度 更 大 、 密 性 能更好 的 F G P A完 全能 用在 网络设 备 及便 携 式设 备 中 , 问 题 的 关 键 是 如 何 降 低 F GA 设 计 的 功 耗 。 通 过 降 低 P FG P A设 计 的功 耗 , 简 化 系统 的散 热处 理 及系 统集 成 方 可 面 的工序 , 系统 满足 用 电池 供 电 , 使 同时 , 通过 降低 功 耗 提 高 了器 件 的可 靠 性 , 低 了 热 噪 声 干 扰 等 。本 文 围 绕 降 FG P A的 V L程序 设计 , Al r 公 司 的 F G 为例 , HD 以 ta e P A 介 绍降低 F G 设 计 功耗 的 方 法 , 过 在 Q ats1 . P A 通 ur 5 0 u 1 中利用 P w r l al P w r sma r 真 , 各 种 设 o ePa E r o e E t t 仿 y y i o 对

基于Verilog的FPGA硬件加速算法优化研究

基于Verilog的FPGA硬件加速算法优化研究一、引言随着人工智能、大数据分析等领域的快速发展,对计算性能的需求也越来越高。

传统的软件算法在处理复杂任务时往往效率低下,为了提高计算速度和效率,硬件加速成为一种重要的解决方案。

而基于现场可编程门阵列(FPGA)的硬件加速方案因其灵活性和性能优势而备受关注。

本文将探讨基于Verilog的FPGA硬件加速算法优化研究。

二、FPGA硬件加速算法优化概述FPGA是一种可编程逻辑器件,通过在FPGA上实现特定的硬件电路,可以实现对特定任务的高效加速。

而Verilog作为一种硬件描述语言,被广泛应用于FPGA设计中。

在进行FPGA硬件加速算法优化研究时,需要深入理解算法原理,并结合Verilog语言进行硬件描述和优化。

三、算法分析与优化1. 算法分析在进行FPGA硬件加速算法优化之前,首先需要对待加速的算法进行深入分析。

通过分析算法的计算复杂度、数据依赖关系等因素,可以找到适合在FPGA上实现的部分,并确定需要进行优化的关键点。

2. 硬件加速设计基于Verilog语言,将经过分析和确定的部分算法转化为硬件电路描述。

在设计过程中,需要考虑如何利用FPGA资源最大化地实现算法功能,并保证电路的稳定性和性能。

3. 优化策略针对硬件加速电路中存在的性能瓶颈和资源占用较大等问题,可以采取一系列优化策略。

比如流水线技术、并行计算、资源共享等方法,来提高硬件加速算法的效率和性能。

四、案例研究以某一具体应用场景为例,展示基于Verilog的FPGA硬件加速算法优化过程。

通过对该案例的详细分析和实验结果展示,验证硬件加速算法优化在提升计算性能方面的有效性。

五、未来展望随着人工智能和大数据等领域的不断发展,对计算性能和效率的需求将会持续增长。

基于Verilog的FPGA硬件加速算法优化研究也将在未来得到更广泛的应用和深入探索。

未来可以进一步探讨更多复杂算法在FPGA上的实现方式,并结合新技术不断提升硬件加速算法的水平。

基于FPGA的硬件加速器设计与应用研究

基于FPGA的硬件加速器设计与应用研究FPGA(Field Programmable Gate Array)是一种可编程逻辑门阵列,广泛应用于数字电路设计和硬件加速器开发。

基于FPGA的硬件加速器能够提供高性能、低功耗的计算能力,为各种应用领域带来巨大的潜力。

本文将探讨基于FPGA的硬件加速器设计与应用研究。

一、硬件加速器的概念和原理硬件加速器是一种专用设备,用于加速特定的计算任务。

与传统的通用计算机相比,硬件加速器在特定应用领域的计算任务上能够提供更高的性能和更低的功耗。

硬件加速器的设计基于特定计算任务的需求,通过专门设计的硬件电路来完成计算任务,而不是通过软件算法来执行。

FPGA作为一种可编程硬件,能够通过重新配置逻辑门来实现不同的电路功能。

基于FPGA的硬件加速器利用FPGA的可编程特性,将特定计算任务的硬件电路转化为FPGA上的可编程逻辑电路,从而实现高性能的计算加速。

相比于专用的ASIC (Application Specific Integrated Circuit)设计,FPGA具有更灵活、更易开发的特点,使得硬件加速器的设计和开发更加迅速和便捷。

二、基于FPGA的硬件加速器设计流程基于FPGA的硬件加速器设计流程包括几个主要的步骤:需求分析、硬件设计、逻辑综合、约束设置、布局与布线、验证和测试。

下面将逐步介绍每个步骤的具体内容。

1. 需求分析:在设计硬件加速器之前,需要对特定计算任务的需求进行全面的分析和理解。

这包括数据流分析、算法分析和性能需求等。

通过深入了解需求,可以为硬件设计提供指导和选型的依据。

2. 硬件设计:在硬件设计阶段,需要根据需求分析的结果,使用硬件描述语言(例如VHDL或Verilog)进行电路设计。

电路设计包括功能模块的设计和连接方式的确定。

3. 逻辑综合:逻辑综合将硬件设计描述转换为基于目标FPGA 的逻辑电路网表。

这个步骤是将抽象的硬件描述转化为具体的逻辑电路的关键步骤。

FPGA的设计流程与关键问题以及解决方案分析

文章编号 : 1 0 0 6 — 4 3 1 1 ( 2 0 1 3 ) 1 8 — 0 1 9 6 — 0 2

0 引 言 ຫໍສະໝຸດ 计 的效 率 。 应用 F P G A设计数 字 电路是数 字 电路系统 领域 的主 要设计 方法之一 ,不 仅有助于 改善 电路 的稳定性 ,减小

1 F P G A设计流程 目前 ,大型工程 设计 中最常用的设计 方法是 H D L设

c o mmu n i c a t i o n s y s t e m w i t h i t s h i g h r e l i a b i l i t y , r e p e a t e d l y r e w r i t t e n f u n c t i o n , a n d l f e x i b l e f i e l d p r o g r a mmi n g . T h e p a p e r i f st r d e s c r i b e s t h e g e n e r a l d e s i g n f l o w o f F P G A d e s i g n ,a n d t h e n a n a l y z e s t h e k e y i s s u e i n d e s i g n ,i n c l u d i n g b u r r p h e n o me n a , c l o c k s k e w ,a n d p o o d y — d e l a y s i t u a t i o n , i f n a l l y g i v e s t h e a p p r o p r i a t e s o l u t i o n .

fpga的基础知识之资源的使用

在探讨FPGA(现场可编程门阵列)的基础知识之资源的使用时,我们首先需要了解FPGA的基本概念和结构。

FPGA是一种集成电路,可以通过在现场编程中重新配置实现特定的功能。

它包含了一系列的可编程逻辑单元和存储单元,可以根据特定的应用重新配置其功能。

在FPGA的设计和开发过程中,资源的使用是一个非常重要的方面,它直接影响到FPGA系统的性能和功耗。

1. FPGA资源的种类FPGA的资源主要包括逻辑单元、存储单元和数学运算单元。

逻辑单元主要用于实现逻辑功能和算术运算,而存储单元则用于存储数据和中间结果。

数学运算单元则是用于实现高速的数学运算和信号处理。

在设计FPGA系统时,我们需要充分了解各种资源的特性和限制,以便合理地配置和使用这些资源。

2. 资源的使用与分配在FPGA系统设计中,资源的使用与分配是一个需要特别注意的问题。

我们需要合理地分配逻辑单元、存储单元和数学运算单元,以满足特定应用的功能需求。

在进行资源分配时,我们需要考虑系统的性能和功耗,并根据应用的特点进行合理的权衡。

3. 优化资源的使用在设计FPGA系统时,我们需要考虑如何优化资源的使用,以提高系统的性能和降低功耗。

优化资源的使用可以通过合理的逻辑设计、存储器设计和算法优化来实现。

我们还可以通过合理的时序设计和流水线设计来进一步优化资源的使用。

4. 个人观点与总结在FPGA的基础知识之资源的使用过程中,我们需要充分了解资源的种类、使用与分配以及优化方法,并结合特定的应用需求进行合理的设计和配置。

资源的使用直接影响到FPGA系统的性能和功耗,因此在设计过程中需要特别注意。

通过合理地配置和优化资源的使用,我们可以实现更高性能和更低功耗的FPGA系统。

FPGA的资源的使用是一个非常重要的问题,它直接关系到系统的性能和功耗。

在设计FPGA系统时,我们需要充分了解各种资源的特性和限制,并根据特定的应用需求进行合理的配置和优化。

只有这样,我们才能实现更高性能和更低功耗的FPGA系统。

基于FPGA的数字信号处理技术研究与设计

基于FPGA的数字信号处理技术研究与设计数字信号处理技术的发展日益深入,随着FPGA(Field Programmable Gate Array)的出现,数字信号处理技术的应用也得以不断拓展,因此,我们将基于FPGA探讨数字信号处理技术的相关研究与设计。

1. 基于FPGA的数字信号处理技术简介FPGA是一种可编程的集成电路。

它具有现场可编程性和高度灵活性,可以承担任何数字电路的任务。

数字信号处理技术是指将信号处理数字化,以实现信号的处理和传输。

它广泛应用于通讯、医疗、工控和汽车等领域。

2. 应用FPGA实现数字信号处理技术的优势2.1 高速度FPGA的可编程性可以使其在实现数字信号处理技术时具有很高的运行速度,适用于高速数据的处理。

2.2 灵活性强FPGA在设计时灵活性较强,可以根据不同的需求,不同的任务进行编程,使得其在数字信号处理的各个领域都可以得到广泛的应用。

2.3 可重构性强FPGA在设计过程中均为可编程电路。

根据不同的需要和电路的修改,FPGA 可以通过简单的修改程序或重构电路来重新配置。

3. 基于FPGA的数字信号处理技术研究与设计案例3.1 旋转速度计旋转速度计是一种普遍应用的传感器器件,可以用来测量液体、气体等的旋转速度或流量。

过去的旋转速度计大多利用着串行外设接口(SPI)进行通讯,外设接口在通讯时速度、带宽比较低,限制了旋转速度计测量速度。

基于FPGA的数字信号处理技术,可以实现高速率的旋转速度测量。

在这个案例中,一个基于FPGA的旋转速度计被设计出来,通过FPGA芯片的内部收发器(SERDES)实现高速并行通讯,从而提高了数字信号处理速度。

3.2自适应滤波器自适应滤波器是一种使用在信号处理中的数字滤波器。

在过去的自适应滤波器设计中,常常需要使用优化算法进行复杂的配置,这种滤波器应用在实时系统中需要耗费大量的时间,效率并不高。

所以,基于FPGA的数字信号处理技术,可以更好的解决这个问题。

基于FPGA的嵌入式系统的研究及设计的开题报告

基于FPGA的嵌入式系统的研究及设计的开题报告一、研究背景及意义随着信息技术的发展,嵌入式系统在社会生产、科学技术等各个领域中得到了广泛应用,其中基于FPGA(Field-Programmable Gate Array)的嵌入式系统在高性能、低功耗、可重构性等方面具有独特的优势,日益成为研究的热点和应用的重要方向。

本课题旨在研究基于FPGA的嵌入式系统的设计及其应用,在对现有相关技术和理论进行深入分析的基础上,结合具体应用场景进行相关系统设计与实践开发,探索FPGA嵌入式系统的优化设计和功能实现,推动信息技术的发展与应用。

二、研究内容及目标本课题的主要研究内容包括以下几个方面:1、基于FPGA的嵌入式系统设计理论研究,包括FPGA基础概念、数字电路设计、EDA工具等相关理论技术的研究。

2、基于ARM处理器的FPGA嵌入式系统架构设计与优化,主要涉及ARM处理器架构、信号处理、寄存器设计等。

3、基于FPGA的嵌入式系统开发及应用实践,实现各类控制、通信、图像处理等应用场景。

本课题的主要研究目标包括以下几个方面:1、深入掌握基于FPGA的嵌入式系统的设计原理和关键技术,具备开发和应用FPGA嵌入式系统的能力。

2、基于ARM处理器的FPGA嵌入式系统架构设计与优化,在提高系统性能和功耗效率的同时,实现系统的实时控制和数据处理等功能。

3、基于FPGA的嵌入式系统开发及应用实践,实现控制、通信、图像处理等应用场景,验证系统性能和可靠性。

三、研究方法和技术路线本课题采用文献研究法、实验研究法和案例研究法相结合的方式进行研究,具体技术路线如下:1、文献研究法。

通过查阅相关文献资料和参考书籍,深入研究FPGA的基础理论、数字电路设计和ARM处理器的嵌入式系统架构等领域的最新研究成果,了解国内外相关领域的发展动态及趋势。

2、实验研究法。

基于FPGA平台,搭建实验环境并进行算法实现、实际调试和性能测试,对系统进行不断优化和完善,验证系统设计的可行性和有效性。

FPGA设计流程关键问题以及解决方案分析

FPGA的设计流程与关键问题以及解决方案分析摘要: fgpa的性能随着半导体技术的发展不断提高,并凭借高可靠性、方便的反复改写功能、灵活的用户现场编程功能等优点成为现代数字通信系统中的新宠。

本文首先介绍了fpga设计的一般设计流程,然后分析了设计中的关键问题产生的原因与影响,主要包括毛刺现象、时钟歪斜以及延迟效果不佳的现状三大点,最后对相应的问题提出解决方案。

abstract: fgpa performance is higher with the development of semiconductor technology. it is popular in the modern digital communication system with its high reliability,repeatedly rewritten function, and flexible field programming. the paper first describes the general design flow of fpga design, and then analyzes the key issue in design, including burr phenomena, clock skew, and poorly-delay situation, finally gives the appropriate solution.关键词: fpga设计流程;关键问题;解决方案key words: fpga design flow;key issues;solutions中图分类号:tn302 文献标识码:a 文章编号:1006-4311(2013)18-0196-020 引言应用fpga设计数字电路是数字电路系统领域的主要设计方法之一,不仅有助于改善电路的稳定性,减小pcb的面积,而且能缩短整个系统的设计调试周期。

基于FPGA硬件设计和仿真方法探索与研究的开题报告

基于FPGA硬件设计和仿真方法探索与研究的开题报告一、研究背景FPGA是一种可编程逻辑器件,它可以通过配置其内部的可编程逻辑单元,实现任何数字电路的功能。

因此,FPGA通常被用于数字集成电路的设计和实现。

随着FPGA技术的发展和进步,FPGA已经成为了一种非常重要的数字集成电路设计工具,广泛应用于计算机硬件设计、信号处理、图像处理、通信系统等领域。

本课题基于FPGA硬件设计和仿真方法,探索研究数字电路的设计和实现。

本课题通过研究FPGA的内部结构和原理,掌握FPGA的硬件设计和仿真方法,实现数字电路的设计和实现。

本课题主要研究内容包括:1. FPGA的内部结构和原理的研究。

2. FPGA的硬件设计和仿真方法的探索和研究。

3. 数字电路的设计和实现。

二、研究目的本课题旨在通过研究FPGA的硬件设计和仿真方法,探索数字电路的设计和实现,达到以下目的:1. 掌握FPGA的内部结构和原理,深入了解FPGA的工作原理。

2. 了解FPGA的硬件设计和仿真方法,提高数字电路设计和仿真的效率。

3. 实现数字电路的设计和实现,研究其在计算机硬件设计、信号处理、图像处理、通信系统等领域的应用。

三、研究内容和方法3.1 研究内容本课题主要研究内容包括FPGA的内部结构和原理、FPGA的硬件设计和仿真方法探索和研究以及数字电路的设计和实现。

1. FPGA的内部结构和原理的研究(1)FPGA的基本结构和功能。

(2)FPGA的逻辑单元和寄存器的结构和功能。

(3)FPGA的编程方式和存储器的工作原理。

2. FPGA的硬件设计和仿真方法的探索和研究(1)FPGA硬件设计开发工具的使用。

(2)FPGA硬件仿真开发工具的使用。

(3)FPGA的RTL设计和Verilog语言的掌握。

3. 数字电路的设计和实现(1)数字电路的基本原理和数电基础知识。

(2)数字电路的设计方法和流程。

(3)数字电路的实现和调试方法。

3.2 研究方法本课题的研究方法主要包括文献资料查阅和实验研究。

基于FPGA智能家居控制系统的设计与研究

基于FPGA智能家居控制系统的设计与研究基于FPGA智能家居控制系统的设计与研究1. 引言随着人工智能和物联网技术的不断发展,智能家居成为人们生活中的一种新趋势。

智能家居控制系统可以实现对家庭中各种设备的智能控制和自动化管理,提供便利和舒适的家居生活体验。

本文旨在通过设计和研究基于FPGA的智能家居控制系统,探索其在智能家庭中的应用。

2. FPGA技术简介FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,具备并行处理和高度可定制化的特点。

它可以根据用户的需求进行编程,实现不同的功能和算法。

FPGA在智能家居系统中具有灵活性高、可扩展性强、功耗低等优点,因此被广泛应用于智能家居领域。

3. 智能家居控制系统设计基于FPGA的智能家居控制系统主要包括三个模块:传感器模块、控制模块和通信模块。

3.1 传感器模块传感器模块用于采集家庭中的各种环境信息,如温度、湿度、光照等。

常用的传感器有温度传感器、湿度传感器和光敏传感器等。

传感器模块将采集到的信息通过FPGA进行处理和分析,并传递给控制模块。

3.2 控制模块控制模块是智能家居控制系统的核心部分,通过识别传感器传递过来的数据,实现对家庭设备的智能控制。

控制模块根据不同的需求,设计相应的算法和逻辑,将其烧录到FPGA中进行运行。

控制模块可以实现对灯光、空调、窗帘等设备的控制,提高家居的智能化程度。

3.3 通信模块通信模块用于实现智能家居控制系统与用户之间的交互和远程控制。

通信模块可以采用无线通信技术,如Wi-Fi或蓝牙,将用户的指令传递给FPGA控制模块,并接收来自控制模块的状态反馈,实现智能家居的远程监控和控制。

4. 系统性能与功能实现4.1 系统性能基于FPGA的智能家居控制系统具备以下性能特点:- 实时性:由于FPGA的并行处理能力和高速时钟频率,系统能够快速响应各种控制指令,确保智能家居的实时性。

- 稳定性:FPGA具备抗干扰能力强、可靠性高等特点,系统能够稳定运行,避免出现故障和中断。

基于fpga的视频图像阴影校正关键算法的研究与实现

华中科技大学硕士学位论文基于FPGA的视频图像阴影校正关键算法的研究与实现姓名:***申请学位级别:硕士专业:机械电子工程指导教师:陈冰;陈幼平20080521摘要随着视频图像数据的带宽大幅度增加,基于FPGA的视频图象处理方法则日益显示出其优越性。

由于FPGA并行执行的机制,使得它可以在较低的时钟频率下也可以很好的实现实时视频图像处理。

本文研究了基于FPGA的医疗图像阴影校正算法的设计与实现。

首先,本文分析了图像阴影产生的原因,然后讨论了几种阴影校正算法的原理,并选择基于参数的阴影校正算法用于X光医疗图像处理。

为在FPGA上实现该算法,必须解决平方根算法在FPGA上的实现问题。

接着,本文介绍了三种主要的平方根算法:数字循环算法(包括restoring算法、non-redundant算法和SRT算法)、Newton-Raphson算法和查表法。

重点讨论了数字循环算法的原理,并对各种算法的性能进行比较。

然后,本文研究了2基SRT算法的FPGA实现问题,给出了算法中几个关键问题的解决方法,包括:基数的选择,平方根结果的表示形式,部分余数的表示形式,平方根结果的转换,选择函数表的规则,迭代的初始化及终止条件和平方根结果的修正等。

并用Verilog硬件描述语言实现了该算法。

最后,本文对平方根算法的Verilog代码进行综合与验证仿真,并对仿真结果进行分析。

总结了论文的主要工作,并展望了下一步的研究工作。

关键词:视频图像处理阴影校正平方根算法数字循环算法SRT算法FPGAAbstractWith substantial increase of video image data bandwidth, FPGA-based video image processing method is increasingly demonstrated its high-performance. Because of the parallel mechanism, it is good at processing real-time video image at a lower clock frequency based on FPGA. This paper studies the design and implementation of medical image shadow correction algorithm based on FPGA.Firstly, this paper analyzes the cause of image shadow, discuss the principles of several correction algorithms, and choose the parametric shadow correction for medical X-ray image processing. In order to implement the algorithm in FPGA, the implementation of square root algorithm must be solved.Secondly, this paper introduces three major square root algorithms: digital recurrence algorithm (including restoring algorithm, non-redundant algorithm and SRT algorithm), Newton-Raphson algorithm and look-up table algorithm. The paper focuses on the principle of digital recurrence algorithm, and compares the performance of several algorithms.Thirdly, this paper studies the implementation of SRT algorithm in FPGA, and presents resolutions to several key problems encountered, including the choice of radix, the form of square root, the form of partial remainder, the conversion of square root, the digital selection rules, the initialization and termination conditions, and the results amendment. Then the algorithm is described in Verilog HDL.Finally, the paper synthesizes and simulates the codes of square root algorithm, and analyzes the simulation results. Then, the paper summarizes the major work and suggests the future work.Keywords:Video Image Processing Shadow Correction Square-Root Algorithm Digit Recurrence Algorithm SRT Algorithm FPGA独创性声明本人声明所呈交的学位论文是我个人在导师指导下进行的研究工作及取得的研究成果。

硬件描述语言在FPGA设计中的应用研究

硬件描述语言在FPGA设计中的应用研究随着科技的快速发展,计算机行业也得到了很大的发展和变革。

其中,FPGA是一种新兴的计算机工具,被广泛应用在数字电路设计和计算资源优化等领域。

而硬件描述语言,作为一种重要的工具,为FPGA的设计和实现提供了重要的支持。

本文将就硬件描述语言在FPGA设计中的应用做一些探讨。

一、 FPGA的应用FPGA的应用广泛,目前已经涵盖了比较多的领域,如数据中心、通信、安全、交通、工业控制等,其中以数据中心应用最为广泛。

在数据中心中,FPGA通过提供可编程逻辑单元和高速IO等功能,将大量的数据处理功能集成到芯片内部,以提升服务器的处理能力和效率。

同时,FPGA的灵活性和可编程性,使其能够进行各种自定义操作,满足不同用户的需求。

在其它领域,FPGA也得到了广泛应用,如在通信领域,FPGA 可以嵌入各种协议和加解密算法,为信息传输和安全保障提供优质的服务;在工业控制领域,FPGA可用于实时数据处理和精密控制等操作;在安全领域中,FPGA可以用于加密解密操作,确保安全传输和保密。

二、硬件描述语言硬件描述语言,即Hardware Description Language,简称HDL,是用来描述数字电路的一种语言。

其能够将数字电路中的逻辑功能、时序关系以及电路元件等描述出来,使之能够被计算机进行仿真、分析和综合等操作。

常见的HDL语言有Verilog和VHDL,其中Verilog语言是一种硬件描述语言,由美国的Phil Moorby所发明。

VHDL是一种硬件描述语言,由U.S. Department of Defense所发明。

通过HDL语言的描述,程序员可以将逻辑电路上的各种元器件,如门电路、寄存器、时序电路等逻辑元器件呈现出来,从而实现不同功能之间的匹配和协调。

在数字电路的设计工作中,硬件描述语言占据着非常重要的地位,可以提高设计者的工作效率和设计质量。

三、硬件描述语言在FPGA设计中的应用FPGA的设计过程,主要包括芯片规划、元器件选择、电路设计、仿真和综合等环节,而硬件描述语言可以对这些环节进行支持和优化。

fpga中的空间辐射效应及加固技术

fpga中的空间辐射效应及加固技术随着FPGA制造技术的不断提升和应用范围的扩大,FPGA在很多领域都得到了广泛的应用。

然而,FPGA在高剂量辐射环境中所面临的问题也逐渐凸显,特别是宇航、核电等领域。

辐射影响会对硅片、封装材料等引起损害,干扰器件高速运转。

其中,空间辐射环境对FPGA的影响更为突出。

如何加固FPGA以提高其抗辐射能力,是当前研究热点。

一、空间辐射效应的原因空间辐射效应是由太阳辐射、地球电离层等天然辐射和宇宙线等高能离子辐射共同作用引起的。

这些辐射会使物质受到电离、激发、击碎等作用,对电子器件严重影响。

二、空间辐射对FPGA的影响1、空间辐射效应可产生静电放电,使FPGA内部电荷积累,电压降低,甚至出现电压反向,导致FPGA完全失效。

2、空间辐射效应可使FPGA内部发生单粒子反应(SEU),导致FPGA芯片内的信息存储单元的状态随机变化,从而导致控制逻辑失效、功能失效、板载软件崩溃等问题。

3、时间相关位错(TID)是指由于电子器件长时间在辐射环境下工作而引起的误码率增加的现象。

空间辐射效应可引起FPGA的逻辑门、寄存器等单元被电离,改变电路工作时钟,导致TID、延迟误差等问题。

三、FPGA抗辐射加固技术为提高FPGA抗辐射能力,采取以下措施:1、FPGA电路设计应充分考虑辐射环境,采用可靠的纠错码、容错设计、逻辑复杂度降低等策略降低FPGA的易损度。

2、FPGA硅片封装时应选择抗辐射性能好的载体材料,防止板卡封装材料在高剂量辐射环境下损坏,并采用光阴老化测试方法评估载体材料抗辐射性能。

3、采用硬件加固方法(如隔离层技术、标准单元和重复块等)提高FPGA抗辐射能力。

硬件隔离层技术是指将FPGA内的单元、通道和系统内部元素隔离开,以减小系统内部的电荷积累和电离效应;硬件重复块技术是将多个相同的FPGA硬件单元集成在一起,实现系统工作,并可以通过故障容错的方式实现系统可靠性提高。

四、结语FPGA在空间辐射下工作时,会受到辐射效应的影响,进而导致系统失效。

RRAM及其在FPGA设计中的应用研究开题报告

RRAM及其在FPGA设计中的应用研究开题报告题目:RRAM及其在FPGA设计中的应用研究摘要:随着芯片技术的不断发展,各种新型存储器技术逐渐出现,其中基于阻变效应的抗褪色存储器(RRAM)具有极高的集成度、低功耗、高速度等优点,正逐渐成为替代闪存和DRAM的新兴存储器技术。

本文首先介绍了RRAM的基本原理及其优缺点,然后重点探讨了RRAM在FPGA设计中的应用,包括FPGA中各种存储器单元的设计和优化、逻辑单元的实现以及硬件加速等方面。

通过对比不同存储器单元的性能、功耗和面积等指标,支持基于RRAM的存储器单元设计。

关键词:RRAM;FPGA;存储器单元;逻辑设计;硬件加速1. 研究背景和意义FPGA作为一种可编程硬件平台,具有广泛的应用,其中存储器单元是FPGA设计中最常用的功能单元之一。

随着FPGA设计中存储器容量和速度等需求的不断提高,各种新型存储器技术也应运而生。

基于阻变效应的抗褪色存储器(RRAM)是一种新兴存储器技术,其具有读写速度快、能耗低、可重置等特点,在FPGA设计中应用前景广阔。

因此,对RRAM 技术及其在FPGA设计中的应用研究具有重要的意义。

2. 研究内容及方案(1)RRAM的基本原理及其优缺点本文将介绍RRAM的基本原理,包括其存储机制、写入与读出方式等方面,同时讨论其特点、优缺点以及与其他存储器技术的比较。

(2)RRAM在FPGA设计中的应用本文将着重探讨RRAM在FPGA设计中的应用,包括存储器单元、逻辑单元和硬件加速三个方面。

存储器单元的设计和优化:本文将介绍基于RRAM的存储器单元的设计,包括基本读写操作、数据保护与纠错等问题。

对比不同存储器单元的性能、功耗和面积等指标,并提出优化措施。

逻辑单元的实现:本文将介绍通过基于RRAM的逻辑单元的实现,提高FPGA的整体性能和可重构性。

主要包括基本逻辑单元(与、或、非等)和复杂逻辑单元(寄存器、计数器等)的设计。

硬件加速:本文将介绍如何利用RRAM实现硬件加速,如基于RRAM的加速器设计和自适应加速等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(3)同步电路能简化两个模块之间的接口,而异步电路需要握手信号或令牌标记才能确保信号的完整性。

(4)用D触发器或寄存器设计同步电路,可以消除毛刺和同步内部歪斜的数据。而异步电路就没有这个优点,且很难进行模拟和排错,也不能得到很好的综合。

同步电路也有缺点,因为需要时序器件,它与异步电路相比将会消耗更多的逻辑门资源。虽然异步电路速度较快且电源消耗较少,但由于现在的FPGA芯片已做到几百万门,故不必太在意这一点。笔者建议尽量避免用异步电路而采用同步电路进行设计。

FPGA(Field Programmable Gate Array)容量、功能以及可靠性的提高,其在现代数字通信系统中的应用日渐广泛。采用FPGA设计数字电路已经成为数字电路系统领域的主要设计方式之一[1]。在信号的处理和整个系统的控制中,FPGA不但能大大缩减电路的体积,提高电路的稳定性,而且其先进的开发工具使整个系统的设计调试周期大大缩短[2~3]。本文结合作者的经验和体会,指出FPGA设计中的一些难点问题,分析问题产生的原因并给出解决方案,有利于FPGA设计者少走弯路,在较短的时间内掌握FPGA设计技术。

2.2 毛刺信号及其消除

在组合逻辑电路中,信号要经过一系列的门电路和信号变换。由于延迟的作用使得当输入信号发生变化时,其输出信号不能同步地跟随输入信号变化,而是经过一段过渡时间后才能达到原先所期望的状态。这时会产生小的寄生毛刺信号,使电路产生瞬间的错误输出,造成逻辑功能的瞬时紊乱。在FPGA内部没有分布电感和电容,无法预见的毛刺信号可通过设计电路传播,从而使电路出现错误的逻辑输出。

2.1.1 全局时钟

全局时钟或同步时钟是最简单、可靠的时钟。在FPGA设计中时钟的最好解决方案是:由专用的全局时钟输入引脚驱动的单个主时钟去钟控设计中的每一个时序器件,只要有可能就应尽量在设计项目中采用全局时钟。FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。在器件中,这种全局时钟能提供最短的时钟延时(数据输入到数据到达输出的时间)。图2是全局时钟的一个实例。

(5)锁存办法

当计数器的输出进行相"与"或相"或"时会产生毛刺。随着计数器位数的增加,毛刺的数量和毛刺的种类也会越来越复杂。毛刺在计数器电路输出中的仿真结果如图4所示,从图中可发现有毛刺出现。此时,可通过在输出端加D触发器加以消除。接D触发器后仿真结果如图5所示。

从图5可以看到,数据中的毛刺被明显消除。当FPGA输出有系统内其它部分的边沿或电平敏感信号时,应在输出端寄存那些对险象敏感的组合输出。对于异步输入,可通过增加输入寄存器确保满足状态机所要求的建立和保持时间。对于一般情况下产生的毛刺,可以尝试用D触发器来消除。但用D触发器消除时,有时会影响到时序,需要考虑很多问题。所以要仔细地分析毛刺产生的来源和毛刺的性质,采用修改电路或其它办法来彻底消除。

例如,从D触发器的Q输出端直接馈给另一触发器的D输入端时,第一个D触发器能满足建立保持时间,但是到第二个D触发器的延迟就可能不足以满足第二个触发器对保持时间的要求,此时就会出现逻辑错误,当时钟出现歪斜时错误更加严重。解决办法是在第一个触发器Q端加一缓冲器,如图7所示。这样就能满足第二个触发器的时序要求。另外还可采用一个低驱动强度的源D型触发器而不加缓冲来解决,高的相对扇出有助于改进保持时间。

(1)利用冗余项消除毛刺

函数式和真值表所描述的是静态逻辑,而竞争则是从一种稳态到另一种稳态的过程。因此竞争是动态过程,它发生在输入变量变化时。此时,修改卡诺图,增加多余项,在卡诺图的两圆相切处增加一个圆,可以消除逻辑冒险。但该法对于计数器型产生的毛刺是无法消除的。

(2)取样法

由于冒险出现在变量发生变化的时刻,如果待信号稳定之后加入取样脉冲,那么就只有在取样脉冲作用期间输出的信号才能有效。这样可以避免产生的毛刺影响输出波形。

任何组合电路、反馈电路和计数器都可能是潜在的毛刺信号发生器。毛刺并不是对所有输入都有危害,如触发器的D输入端,只要毛刺不出现在时钟的上升沿并满足数据的建立保持时间,就不会对系统造成危害。而当毛刺信号成为系统的启动信号、控制信号、握手信号,触发器的清零信号(CLEAR)、预置信号 (PRESET)、时钟输入信号(CLK)或锁存器的输入信号就会产生逻辑错误。任何一点毛刺都可能使系统出错,因此消除毛刺信号是FPGA设计中的一个重要问题。毛刺问题在电路连线上是找不出原因的,只能从逻辑设计上采取措施加以解决。消除毛刺的一般方法有以下几种:

2.4.2 用流水线技术提高同步电路的速度

同步电路的速度是指同步系统时钟的速度,同步时钟愈快,电路处理数据的时间间隔越短,电路在单位时间内处理的数据量就愈大。在讨论同步电路的运行速度之前,先看看电路的数据传输模型,如图8所示。

Tco是触发器的输入数据被时钟打入到触发器到数据到达触发器输出端的延时时间;Tdelay是组合逻辑的延时;Tsetup是D触发器的建立时间。假设数据已被时钟打入D触发器,那么数据到达第一个触发器的Q输出端需要的延时时间是Tco,经过组合逻辑的延时时间为Tdelay,然后到达第二个触发器的D端,要希望时钟能在第二个触发器再次被稳定地打入触发器,则时钟的延迟必须大于Tco+Tdelay+Tsetup,也就是说最小的时钟周期Tmin=Tco+Tdelay+Tsetup,即最快的时钟频率Fmax=1/Tmin。FPGA开发软件也是通过这种方法来计算系统最高运行速度Fmax。因为Tco和Tsetup是由具体的器件工艺决定的,故设计电路时只能改变组合逻辑的延时时间Tdelay,所以说缩短触发器间组合逻辑的延时时间是提高同步电路速度的关键所在。由于一般同步电路都大于一级锁存,而要使电路稳定工作,时钟周期必须满足最大延时要求。故只有缩短最长延时路径,才能提高电路的工作频率。可以将较大的组合逻辑分解为较小的N块,通过适当的方法平均分配组合逻辑,然后在中间插入触发器,并和原触发器使用相同的时钟,就可以避免在两个触发器之间出现过大的延时,消除速度瓶颈,这样可以提高电路的工作频率。这就是所谓"流水线"技术的基本设计思想,即原设计速度受限部分用一个时钟周期实现,采用流水线技术插入触发器后,可用N个时钟周期实现,因此系统的工作速度可以加快,吞吐量加大。注意,流水线设计会在原数据通路上加入延时,另外硬件面积也会稍有增加。

(3)吸收法

增加输出滤波,在输出端接上小电容C可以滤除毛刺,如图3所示。但输出波形的前后沿将变坏,在对波形要求较严格时,应再加整形电路,该方法不宜在中间级使用。

4)延迟办法

因为毛刺最终是由于延迟造成的,所以可以找出产生延迟的支路。对于相对延迟小的支路,加上毛刺宽度的延迟可以消除毛刺。但有时随着负载增加,毛刺会继续出现,因而这种方法也是有局限性的。而且采用延迟线的方法产生延迟更会由于环境温度的变化而使系统变不可靠。

2.1.4 时钟歪斜

时钟歪斜是FPGA设计中最严重的问题之一。电路中控制各元件同步运行的时钟源到各元件的距离相差很大,时钟歪斜就是在系统内不同元件处检测到有效的时钟跳变沿所需的时间差异。为了保证各个元件的建立保持时间,歪斜必须足够小。若歪斜的程度大于从一边缘敏感存储器的输出到下一级输入的延迟时间,就能使移位寄存器的数据丢失,使同步计数器输出发生错误,故必须设法消除时钟歪斜。减少时钟歪斜的方法有以下几种:(1)采用适当的时钟缓冲器,或者在边缘敏感器件的输出与其馈给的任何边缘敏感器件输入端之间加入一定的延迟以减小歪斜。(2)严重的时钟歪斜往往是由于在FPGA内的时钟及其它全局控制线(如复位线)使负载过重造成的,在信号线上接一串线形缓冲器,使驱动强度逐步增大,可以消除时钟歪斜。(3)在受时钟控制的部件之后分别接入缓冲器,并在两个缓冲器输出端之间接一平衡网络。(4)采用FPGA内的PLL模块可以对输入时钟进行很好的分频和倍频,从而使时钟歪斜减到最低程度。

1 FPGA设计流程

FPGA设计大都采用自顶向下的设计流程,大体上分为设计说明书、设计输入、综合、功能仿真(前仿真)、逻辑实现、时序仿真(后仿真)、配置下载等七个

2.1 时钟设计

在任何数字电路设计中,可靠的时钟是非常关键的。时钟一般可分为全局时钟、门控时钟和多级逻辑时钟等几种类型。

同步数字电路系统在当今是占绝对优势的,工程师常用它设计所有能想象到的数字电路,其频率可以从直流到几GHz。同步电路与异步电路相比有以下优点:

(1)同步电路能在温度、电压、过程等参数变化的情况下保持正常的工作,而异步电路的性能通常和环境温度、工作电压以及生产过程有关。

(2)同步电路具有可移植性,易于采用新技术或更先进的技术,而异步电路很难重用和维护。

2.1.2 门控时钟

在许多应用中,都采用外部的全局时钟是不实际的,通常要用阵列时钟构成门控时钟。门控时钟常常同微处理器接口有关,每当用组合函数钟控触发器时,通常都存在着门控时钟。如果符合下述条件,门控时钟可以象全局时钟一样可靠地工作:(1)驱动时钟的逻辑必须只包含一个"与"门或"或"门;(2)逻辑门的一个输入是实际的时钟,而该逻辑门的所有其它输入必须是地址或控制线,它们约束时钟的建立和保持时间。当然也可以将门控时钟转换成全局时钟以改善设计项目的可靠性。

2.1.3 多时钟系统

许多应用要求在同一个FPGA内采用多个时钟,比如两个异步微处理器之间的接口或微处理器和异步通信通道的接口。由于两个时钟信号之间要求一定的建立和保持时间,所以引进了附加的定时约束条件,将某些异步信号同步化。在许多系统中只将异步信号同步化是不够的,当系统中有两个或两个以上非同源时钟的时候,数据的建立和保持时间很难得到保证,最好的解决办法是将所有非同源时钟同步化。使用FPGA内部的锁相环(PLL)模块是一个很好的方法。如果不用PLL,当两个时钟的频率比是整数时,同步的方法比较简单;当两个时钟的频率比不为整数时,处理方法要复杂得多。这时需要使用带使能端的D触发器,并引入一个高频时钟来实现。

2.4 FPGA中的同步电路设计