采用PLL(锁相环)IC的频率N(1~10)倍增电路

PLL技术与应用考核试卷

B.增加环路滤波器的阶数

C.减小环路带宽

D.提高VCO的切换速度

20.在PLL的设计过程中,如何判断PLL是否锁定?()

A.通过观察VCO的输出频率是否稳定

B.通过观察鉴相器的输出是否为零

C.通过观察环路滤波器的输出是否稳定

D.以上都是

二、多选题(本题共20小题,每小题1.5分,共30分,在每小题给出的四个选项中,至少有一项是符合题目要求的)

A. 10

B. 5

C. 1

D. 50

14.下列哪种因素不会影响PLL的性能?()

A.噪声

B.环境温度

C.电源电压

D.信号幅度

15.在PLL中,当输入信号频率变化时,为了维持锁定状态,VCO的输出频率会如何变化?()

A.保持不变

B.成比例增加

C.成比例减少

D.无规律变化

16. PLL的哪一部分负责产生控制VCO的电压?()

3.调整PLL参数改善相位噪声的方法包括使用低相位噪声的VCO、增加环路滤波器的阶数、选择合适的环路带宽等。

4.设计PLL频率合成器时,关键因素包括VCO的频率范围和相位噪声、环路滤波器的设计、鉴相器的性能等。这些因素影响PLL的锁定速度、稳定性、相位噪声和频率分辨率,对通信系统的性能至关重要。

4.下列哪种应用场合不适合使用PLL技术?()

A.无线通信中的频率合成

B.时钟信号的恢复

C.音频信号的放大

D.视频信号的同步

5.在PLL系统中,什么是鉴相器的作用?()

A.比较输入信号和压控振荡器输出信号的相位差

B.产生一个与输入信号频率相同的信号

C.用来放大压控振荡器的输出信号

D.用来减小噪声的影响

MCF_ColdFire52259时钟模块中文翻译

时钟模块1,时钟模块简要介绍时钟模块允许设备配置多个时钟模式中的一个。

时钟模式,包括内部相位锁相环(PLL )时钟与外部参考时钟或内部晶体放大器支持外部晶振参考时钟。

PLL 也可以被禁用,并且一个设备可以直接使用外部振荡器的时钟。

时钟模块包含以下内容:(1)晶体放大器和振荡器(OSC ); (2)锁相环(PLL );(3)分频器(RFD ); (4)状态和控制寄存器; (5)状态和控制寄存器; (6)控制逻辑;(7)实时时钟(RTC )振荡器。

2,特点时钟模块的功能包括以下内容:(1)晶体的张弛振荡器,或外部振荡器的参考选项; (2)修整松弛振荡器;(3)通过PLL 的与分频功能可以划分时钟源的频率范围; (4)外部RTC/备份振荡器(标称频率32.768千赫);(5)系统时钟可以由PLL 或直接由晶体振荡器或弛张振荡器决定; (6)支持低功耗模式; (7)独立的时钟输出信号; (8))150(2<=<=n n超低频运行的低功率分配器。

3,操作模式时钟模块可以运行在看门狗定时器模式下,RTC 模式下,正常PLL 模式(默认)或外部时钟模式下(锁相环禁用)。

3.1看门狗定时器模式在这种模式下,在POR (上电复位)后,看门狗定时器被禁用,这时定时器的时钟输入是系统时钟。

辅助看门狗定时器模块的时钟源的选用,能够仅出现一次的POR 。

因此,如果松弛振荡器作为定时器的输入源选择,随后尝试选择张弛振荡器作为系统时钟源被封锁,直到未来POR 。

如果已经选定的张弛振荡器作为系统时钟源,随后被选中作为定时器的输入源,系统和定时器可以使用的振荡器源。

3.2RTC模式一个专用的RTC振荡器可以选择运行RTC电路。

在正常运作,此振荡器是由VDDPLL和VSSPLL引脚控制的。

当部分关闭,这个振荡器供电由VSTBY针。

预计名义RTC振荡器的频率是32.768千赫,但范围可以从32千赫到40千赫。

3.3普通PLL模式在正常的PLL模式下,PLL是完全可编程的,它可以从1X到18X参考频率合成频率范围,并有一个辅助分频器,在没有扰乱PLL频率合成的情况下降低干扰。

锁相环倍频

锁相环倍频锁相环倍频是一种常用的电路技术,用于产生高频时钟信号或频率合成。

它是利用锁相环(Phase-Locked Loop,简称PLL)的特性来实现的。

锁相环倍频的原理是通过反馈的方式,将输入信号与本地时钟信号进行比较,并将误差信号通过滤波、放大等环节处理后,再输入到VCO(Voltage-Controlled Oscillator)中,通过调节VCO的频率,使其与输入信号的频率同步。

这种方式可以实现输入信号与本地时钟信号的频率倍增,从而达到倍频的目的。

锁相环倍频的基本结构包括相平衡器(Phase Detector)、环形滤波器(Loop Filter)、控制电压产生器(Control Voltage Generator)和VCO等组成。

其工作过程如下:1. 相平衡器将输入信号与本地时钟信号进行比较,产生误差信号。

2. 误差信号经过环形滤波器,滤除高频噪声,得到平稳的控制电压。

3. 控制电压通过控制电压产生器转换成电流信号,进一步输入到VCO 中。

4. VCO根据控制电流信号的大小,调节自身的频率,使其与输入信号的频率同步。

5. 经过一段时间后,锁相环达到稳定状态,输出的时钟信号的频率是输入信号频率的倍数。

锁相环倍频技术有许多应用,其中包括:1. 高速通信系统:在光纤通信和无线通信中,为了实现高速数据传输,需要产生高精度的时钟信号。

锁相环倍频可以通过将低频的参考时钟倍频到高频,从而满足高速通信系统对时钟信号精度和稳定性的要求。

2. 数字信号处理(DSP):在数字信号处理中,需要对输入信号进行采样和处理。

锁相环倍频可以用来产生高速的采样时钟信号,从而实现高速、高精度的信号处理。

3. 电源管理:在电子设备中,为了提高能源利用效率和延长电池寿命,通常会使用功率管理芯片来控制电源的供电。

锁相环倍频可以用于产生稳定的时钟信号,从而精确控制供电频率,实现电源管理的功能。

4. 音频频率合成:在音频设备中,为了产生不同频率的音频信号,通常使用频率合成器。

锁相环原理以及倍频分频实现

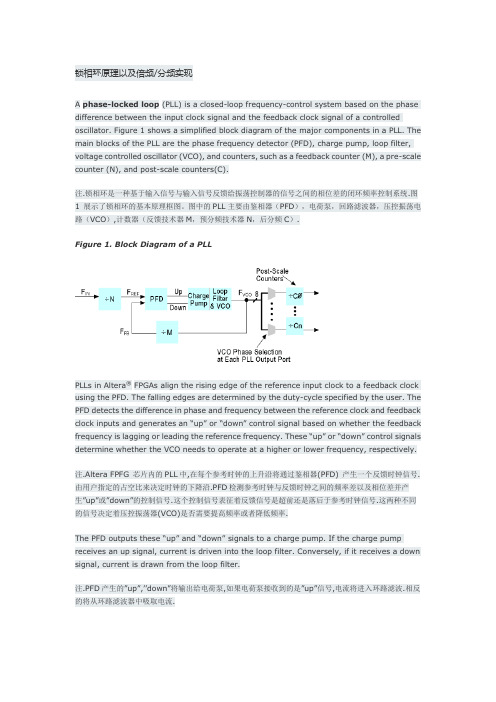

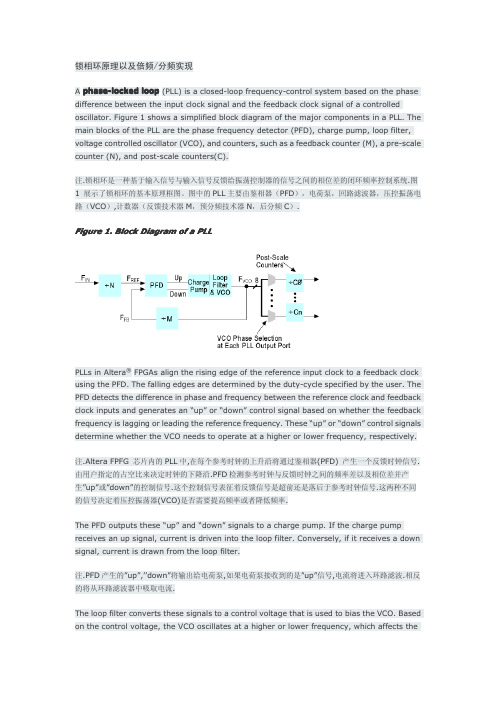

锁相环原理以及倍频/分频实现A phase-locked loop (PLL) is a closed-loop frequency-control system based on the phase difference between the input clock signal and the feedback clock signal of a controlled oscillator. Figure 1 shows a simplified block diagram of the major components in a PLL. The main blocks of the PLL are the phase frequency detector (PFD), charge pump, loop filter, voltage controlled oscillator (VCO), and counters, such as a feedback counter (M), a pre-scale counter (N), and post-scale counters(C).注.锁相环是一种基于输入信号与输入信号反馈给振荡控制器的信号之间的相位差的闭环频率控制系统.图1 展示了锁相环的基本原理框图。

图中的PLL主要由鉴相器(PFD),电荷泵,回路滤波器,压控振荡电路(VCO),计数器(反馈技术器M,预分频技术器N,后分频C).Figure 1. Block Diagram of a PLLPLLs in Altera® FPGAs align the rising edge of the reference input clock to a feedback clock using the PFD. The falling edges are determined by the duty-cycle specified by the user. The PFD detects the difference in phase and frequency between the reference clock and feedback clock inputs and generates an “up” or “down” control signal based on whether the feedback frequency is lagging or leading the reference frequency. These “up” or “down” control signals determine whether the VCO needs to operate at a higher or lower frequency, respectively.注.Altera FPFG 芯片内的PLL中,在每个参考时钟的上升沿将通过鉴相器(PFD) 产生一个反馈时钟信号.由用户指定的占空比来决定时钟的下降沿.PFD检测参考时钟与反馈时钟之间的频率差以及相位差并产生”up”或”down”的控制信号.这个控制信号表征着反馈信号是超前还是落后于参考时钟信号.这两种不同的信号决定着压控振荡器(VCO)是否需要提高频率或者降低频率.The PFD outputs these “up” and “down” signals to a charge pump. If the charge pump receives an up signal, current is driven into the loop filter. Conversely, if it receives a down signal, current is drawn from the loop filter.注.PFD产生的”up”,’’down”将输出给电荷泵,如果电荷泵接收到的是”up”信号,电流将进入环路滤波.相反的将从环路滤波器中吸取电流.The loop filter converts these signals to a control voltage that is used to bias the VCO. Based on the control voltage, the VCO oscillates at a higher or lower frequency, which affects the phase and frequency of the feedback clock. If the PFD produces an up signal, then the VCO frequency increases. A down signal decreases the VCO frequency. The VCO stabilizes once the reference clock and the feedback clock have the same phase and frequency. The loop filter filters out jitter by removing glitches from the charge pump and preventing voltage over-shoot.注.环路滤波将”up””down”信号准换为压控信号传递给压控振荡器.并控制压控振荡器的振荡频率.如果PFD产生的是”up”信号,VCO将提高振荡频率,相反减少振荡频率.直到参考时钟信号与反馈时钟信号具有相同的振荡频率以及相位. 环路滤波器将滤除电荷泵产生的噪声振荡并且防止电压过载.When the reference clock and the feedback clock are aligned, the PLL is considered locked. To注.当参考频率与反馈频率一致的时候,PLL被称为锁定.A divide counter (M) is inserted in the feedback loop to increase the VCO frequency above the input reference frequency. VCO frequency (F VCO) is equal to (M) times the input reference clock (F REF). The PFD input reference clock (F REF) is equal to the input clock (F IN) divided by the pre-scale counter (N). Therefore, the feedback clock (F FB) applied to one input of the PFD is locked to the F REF that is applied to the other input of the PFD. The VCO output feeds post-scale counters which allow a number of harmonically related frequencies to be produced within the PLL.注.反馈回路上插入一个除法器(M)可以在参考时钟频率的基础上实现M倍频.PFD的输入频率等于输入频率/N.The output frequency of the PLL is equal to the VCO frequency (F VCO) divided by thepost-scale counter (C).In the form of equations:∙F REF = F IN / N∙F VCO = F REF × M = F IN × M/N∙F OUT = F VCO / C = (F REF × M) / C = (F IN × M) / (N × C)where:∙F VCO = VCO frequency∙F IN = input frequency∙F REF = reference frequency∙F OUT = output frequency∙M = counter (multiplier), part of the clock feedback path∙N = counter (divider), part of the input clock reference pathC = post-scale counter (divider)。

锁相环(PLL)的工作原理

锁相环(PLL)的工作原理1.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

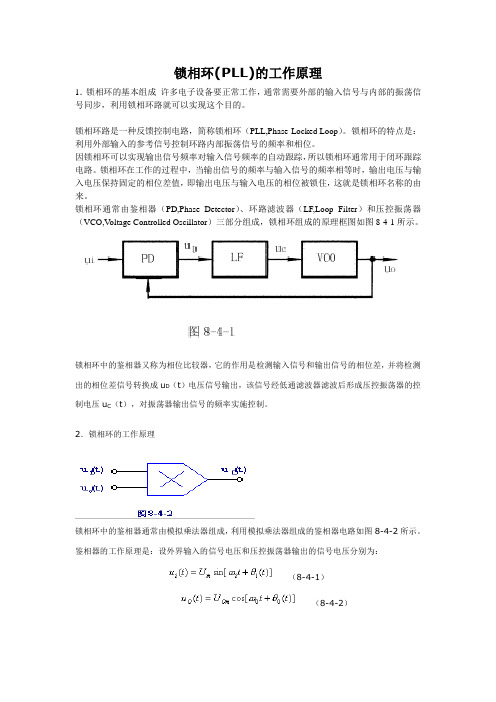

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。

2.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压u D为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t)。

即u C(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为:(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,u c(t)为恒定值。

pll数字锁相环原理

1引言锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数。

传统的锁相环各个部件都是由模拟电路实现的,一般包括鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)三个环路基本部件。

随着数字技术的发展,全数字锁相环ADPLL(AllDigital Phase-Locked Loop)逐步发展起来。

所谓全数字锁相环,就是环路部件全部数字化,采用数字鉴相器、数字环路滤波器、数控振荡器构成锁相环路,并且系统中的信号全是数字信号。

与传统的模拟电路实现的锁相环相比,由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点,从而具备可靠性高、工作稳定、调节方便等优点。

全数字锁相环的环路带宽和中心频率编程可调,易于构建高阶锁相环,并且应用在数字系统中时,不需A/D及D/A转换。

在调制解调、频率合成、FM立体声解码、图像处理等各个方面得到广泛的应用。

随着电子设计自动化(EDA)技术的发展,可以采用大规模可编程逻辑器件(如CPLD或FPGA)和VHDL语言来设计专用芯片ASIC和数字系统。

本文完成了全数字锁相环的设计,而且可以把整个系统嵌入SoC,构成片内锁相环。

2全数字锁相环的体系结构和工作原理74XX297是出现最早,应用最为广泛的一款全数字锁相环,在本文中以该芯片为参考进行设计、分析。

ADPLL基本结构如图1所示,主要由鉴相器、K变模可逆计数器、脉冲加减电路和除N计数器4部分构成。

K变模计数器和脉冲加减电路的时钟分别为M fc和2Nfc。

这里fc是环路中心频率,一般情况下M和N都是2的整数幂。

2.1鉴相器常用的鉴相器有两种类型:异或门(XOR)鉴相器和边沿控制鉴相器(ECPD)。

异或门鉴相器比较输入信号Fin相位和输出信号Fout相位之间的相位差θe,并输出误差信号Se作为K变模可逆计数器的计数方向信号。

射频电路期末试题及答案

射频电路期末试题及答案一、选择题(每题2分,共40分)1. 射频电路意味着信号频率高于多少kHz?A. 10B. 100C. 1D. 10002. 射频放大器主要用于增加哪种信号的幅度?A. 音频信号B. 射频信号C. 直流信号D. 时钟信号3. 射频滤波器的作用是什么?A. 抑制射频信号B. 放大射频信号C. 滤除杂散信号D. 改变信号的频率4. 射频混频器主要用于进行什么操作?A. 将射频信号转换为中频信号B. 将射频信号转换为直流信号C. 将射频信号转换为音频信号D. 将射频信号进行放大5. 射频电路中的天线主要用于什么目的?A. 发送射频信号B. 接收射频信号C. 进行信号混频D. 进行信号放大6. 射频锁相环(PLL)是用来解决什么问题的?A. 抑制射频信号的干扰B. 放大射频信号的幅度C. 实现射频信号的调频D. 实现射频信号的频率合成7. 射频功率放大器的主要特点是什么?A. 高增益B. 高效率C. 高线性度D. 低失真度8. 射频开关的作用是什么?A. 分离不同频段的信号B. 改变信号的频率C. 进行信号的开关控制D. 减小信号的幅度9. 射频电路中的衰减器的作用是什么?A. 减小射频信号的幅度B. 增加射频信号的幅度C. 对射频信号进行调频D. 对射频信号进行解调10. 射频电路的最主要应用领域是什么?A. 通信系统B. 音频系统C. 汽车电子系统D. 计算机系统11. 射频电路中的谐振器主要用于什么目的?A. 进行信号放大B. 改变信号的频率C. 压制杂散信号D. 过滤不需要的频率成分12. 射频电路中的偏置电路的作用是什么?A. 稳定射频信号的幅度B. 改变射频信号的频率C. 分离射频信号和其他信号D. 进行信号放大13. 射频放大器的增益一般指的是什么?A. 电流增益B. 电压增益C. 功率增益D. 带宽增益14. 射频电路中的衰减器通常采用什么原理实现?A. 脉冲宽度调制B. 变压器耦合C. 电阻耦合D. 反馈耦合15. 射频电路中的功率分配器的作用是什么?A. 将射频信号分配到不同的电路中B. 改变射频信号的频率C. 增强射频信号的幅度D. 减小射频信号的幅度二、填空题(每题4分,共40分)1. 射频电路是用于处理频率高于_________的信号。

stm32f103中文手册[10]

![stm32f103中文手册[10]](https://img.taocdn.com/s3/m/5c2a8ad080c758f5f61fb7360b4c2e3f5627256b.png)

stm32f103中文手册一、概述stm32f103c8/cb:64KB或128KB闪存,20KBSRAM,48引脚或64引脚LQFP封装。

stm32f103r8/rb:64KB或128KB闪存,20KBSRAM,64引脚LQFP封装。

stm32f103v8/vb:64KB或128KB闪存,20KBSRAM,100引脚LQFP封装。

stm32f103rc/rd/re:256KB或384KB或512KB闪存,48KB或64KB SRAM,64引脚或100引脚或144引脚LQFP封装。

stm32f103vc/vd/ve:256KB或384KB或512KB闪存,48KB或64KB SRAM,100引脚或144引脚LQFP封装。

stm32f103zc/zd/ze:256KB或384KB或512KB闪存,48KB或64KB SRAM,144引脚LQFP封装。

stm32f103的主要特性如下:基于ARM Cortex-M3内核,主频可达72MHz。

内置嵌套向量中断控制器(NVIC),支持多达60个中断源和4个优先级。

内置多种存储器资源,包括闪存、SRAM、备份寄存器和选项字节。

内置多种外设资源,包括GPIO、ADC、DAC、定时器、PWM、I2C、S PI、USART、CAN、USB等。

支持多种时钟源和时钟控制模式,包括内部RC振荡器、外部晶振、PLL等。

支持多种低功耗模式和唤醒机制,包括待机模式、停止模式、睡眠模式等。

支持多种调试和编程接口,包括JTAG/SWD、串口引导加载等。

支持多种电源管理功能,包括电压监测、温度传感器、复位控制等。

二、系统架构stm32f103的系统架构如图1所示¹。

其主要组成部分包括:ARM Cortex-M3内核:负责执行指令和处理数据。

NVIC:负责管理中断请求和中断服务程序。

存储器总线:负责连接内核和存储器资源。

AHB总线:负责连接内核和高速外设资源。

APB1总线:负责连接内核和低速外设资源1。

fod8342 典型应用电路

fod8342 典型应用电路在典型应用电路中,以下是一些常见的电路和相关参考内容:1. 电源电路- 直流电源电路:由变压器、整流电路和滤波电路组成,用来提供恒定的直流电源。

其中,变压器将交流电压转换为合适的电压、整流电路将交流电转换为直流电、滤波电路去除输出中的纹波。

- 开关电源:由输入滤波电路、功率因数校正电路、变换器和输出整流滤波电路组成,主要用于电子设备的变压、变频和直流电源转换。

2. 放大电路- 信号放大电路:包括放大器、差分放大电路和运算放大器等。

放大器可以将小信号放大到一定的幅度以供后续处理,例如声音放大器。

- 电源放大电路:将小信号放大到功率级别的电路,如功放电路,常用于音响设备或电视机中。

3. 滤波电路- 无源滤波器:由电容、电感和电阻组成,常见的类型有低通滤波器、高通滤波器和带通滤波器。

无源滤波器主要用于对信号进行频率的选择性放大或削弱。

- 主动滤波器:主要由放大器、运算放大器和电容等元件组成,能够对信号进行放大和选择性滤波。

4. 比较电路- 比较器电路:将两个电压进行比较,输出一个高电平或低电平的电路。

常用于数字电路的门电路或电压控制器中。

- 正弦波比较器电路:将输入正弦波与参考正弦波进行比较,输出一个脉冲的电路。

在调制解调器和数码通信中常用。

5. 倍压电路- 电压倍增电路:通过电感和电容的阻抗性质,将输入电压放大到两倍或更高的倍数。

- 电荷泵电路:通过二极管、电容和开关,将输入电压提升到更高的电压。

6. 时序电路- 时钟电路:根据时钟信号的计时方式,可以分为同步时钟和异步时钟等,用于同步各个电子元件之间的动作。

- 计数器电路:能够对输入信号的频率进行计数,常见的有二进制计数器、BCD计数器等。

7. 可调电路- 电压调节器:能够提供稳定的输出电压,例如线性稳压器和开关稳压器。

- 频率调节器:能够调节输入信号的频率,例如VCO(电压控制振荡器)和PLL(锁相环)等。

8. 信号转换电路- 模数转换电路:将模拟信号转换为数字信号的电路,例如ADC(模数转换器)。

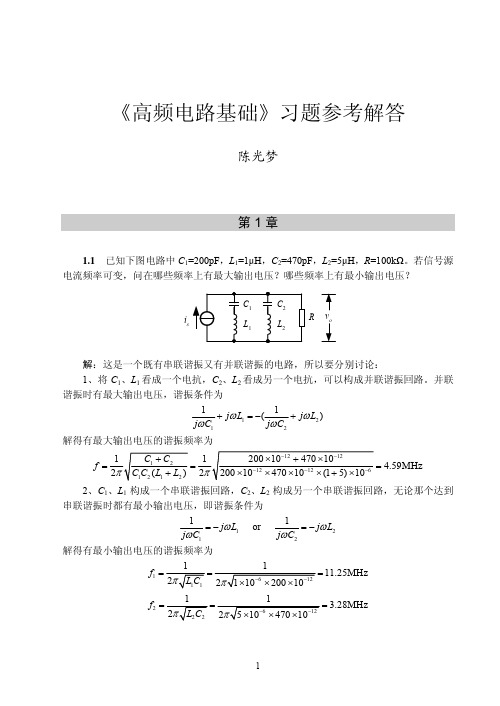

习题参考解答

按:现在很流行的无接触 IC 卡(如公交卡)的工作原理就是利用这个现象:读卡器 产生一定频率的高频电流流过读卡器内的线圈;IC 卡靠近读卡器后,卡内的线圈感应出电 流;此电流首先给卡内的电容充电,作为卡内电路的电源,然后按照一定的规律短路卡内

的线圈;最后读卡器根据初级线圈中阻抗的变化获知卡内的信息。

1 jωC1

+

jω L1

= −(

1 jωC2

+

jωL2 )

解得有最大输出电压的谐振频率为

f= 1 2π

C1 + C2 = 1 C1C2 (L1 + L2 ) 2π

200 ×10−12 + 470 ×10−12 200 ×10−12 × 470 ×10−12 × (1 + 5) ×10−6

= 4.59MHz

解:设电感值为 L,并联之电容值为 C2。已知 C1=12pF~360pF,f=535kHz~1605kHz, 所以有

⎧⎪535 ×103 ⎪

=

2π

1 L(360 ×10−12 + C2

⎨

⎪⎪⎩1605 ×103 = 2π

1 L(12 ×10−12 + C2

解之,得 C2=31.5pF,L=226μH。

BW0.1 = 2.47 BW0.7

1.9 试应用互感耦合的反射阻抗公式(1.61)式或(1.62)式,定性讨论互感耦合双调谐回 路的幅频特性曲线中出现的双峰值现象。

解:由于互感耦合双调谐回路次级的感生电势与电感串联,所以次级回路可以看作串 联谐振回路。根据(1.61)式或(1.62)式都可以计算互感耦合的反射阻抗,下面以(1.61)式进行 计算。

,Z12

将呈容性。若不考虑次级的反射阻抗,此时初级并联谐振回路将由于容抗减小、感抗增加

锁相环倍频

锁相环倍频

锁相环倍频(PLL)是一种常见的用于振荡信号放大和同步的电子电路。

它有助于把一个参考振荡器的频率转换成另一个频率,特别是在电视、广播、雷达和通信系统中,用于传输或接收信号。

它具有灵活性、简单的操作、易于维护的特点,在很多领域得到了广泛的应用。

锁相环倍频是一种基于振荡器的控制系统,主要由一个信号检测器(检测信号频率、相位等)、一个比较器(生成检测器输出信号的差异)、一个控制器(根据比较器输出信号作出反应)、一个调节器(调整振荡器的频率,以达到原有参考频率)和一个振荡器(按照控制器控制的频率工作)组成。

当一个参考信号的频率由振荡器产生时,检测器将检测它的频率和相位,并将该信号输出给比较器。

随后,比较器将检测器的输出与参考信号比较,并将不同之处输出给控制器。

最后,控制器将根据差异来控制调节器以调节振荡器的频率,直到检测器输出和参考信号完全一致为止。

由于锁相环倍频能够快速有效地将参考信号的频率转换成另一个频率,因此在很多领域得到了广泛的应用,包括电视、广播、雷达和无线通信系统等。

它可以帮助系统提高信号的质量,使接收到的信号易于识别。

此外,它还可以提高系统避免出现谐振现象,从而提高系统的稳定性。

pll锁相环的公式

pll锁相环的公式PLL锁相环是一种广泛应用于通信、计算机、控制等领域的电子设备,它的作用是将输入信号的频率锁定到参考信号频率上。

在PLL锁相环的设计中,计算PLL锁相环的公式是非常重要的,因为它能够推导出PLL锁相环的相关参数,从而影响其性能和稳定性。

本文将详细介绍PLL 锁相环的公式及其应用。

一、 PLL锁相环基本原理PLL锁相环是一种基于反馈的电子电路,可以将不同频率的信号锁定在一个稳定的参考信号上。

PL锁相环由三部分组成:比较器、低通滤波器和可变频率振荡器(VCO)。

比较器将输入信号和参考信号进行比较,输出的误差信号经过低通滤波器滤波后控制VCO的频率,以使得VCO的输出频率与参考信号的频率同步。

二、PLL锁相环的公式在PLL锁相环中,有以下基本参数:1. 相位差(Phase difference),用$\Delta\phi$ 表示。

它表示输入信号和参考信号的相位差,即两个信号的相位差。

2. 频率差(Frequency difference),用 $\Delta f$ 表示。

它表示输入信号和参考信号的频率差,即两个信号的频率之差。

3. 循环误差(Loop error),用 $\delta$ 表示。

它表示输出信号的相位与参考信号的相位差。

根据上述参数,PLL锁相环的公式如下:$$\delta = K_v\Delta f$$其中$K_v$是VCO的增益,即输出频率随输入电压的变化率。

它通常用Hz/Volts或MHz/Volts表示。

需要注意的是,上述公式中的单位应该保持一致。

例如,如果频率单位是kHz,那么增益单位应该是kHz/Volts。

三、PLL锁相环的应用PLL锁相环在通信、计算机、控制等领域都有广泛的应用。

例如:1. 频率合成器:通过PLL锁相环将输入信号锁定到参考信号的频率上,然后使用倍频器或分频器将输出信号的频率调整到所需要的频率,从而实现频率合成。

2. 时钟恢复:在数据传输中,使用PLL锁相环将接收到的数据中的时钟与本地时钟进行同步,以便正确接收数据。

锁相环原理以及倍频分频实现

锁相环原理以及倍频/分频实现A phase-locked loop(PLL)is a closed-loop frequency-control system based on the phase difference between the input clock signal and the feedback clock signal of a controlled oscillator.Figure1shows a simplified block diagram of the major components in a PLL.The main blocks of the PLL are the phase frequency detector(PFD),charge pump,loop filter, voltage controlled oscillator(VCO),and counters,such as a feedback counter(M),a pre-scale counter(N),and post-scale counters(C).注.锁相环是一种基于输入信号与输入信号反馈给振荡控制器的信号之间的相位差的闭环频率控制系统.图1展示了锁相环的基本原理框图。

图中的PLL主要由鉴相器(PFD),电荷泵,回路滤波器,压控振荡电路(VCO),计数器(反馈技术器M,预分频技术器N,后分频C).Figure1.Block Diagram of a PLLPLLs in Altera®FPGAs align the rising edge of the reference input clock to a feedback clock using the PFD.The falling edges are determined by the duty-cycle specified by the user.The PFD detects the difference in phase and frequency between the reference clock and feedback clock inputs and generates an“up”or“down”control signal based on whether the feedback frequency is lagging or leading the reference frequency.These“up”or“down”control signals determine whether the VCO needs to operate at a higher or lower frequency,respectively.注.Altera FPFG芯片内的PLL中,在每个参考时钟的上升沿将通过鉴相器(PFD)产生一个反馈时钟信号.由用户指定的占空比来决定时钟的下降沿.PFD检测参考时钟与反馈时钟之间的频率差以及相位差并产生”up”或”down”的控制信号.这个控制信号表征着反馈信号是超前还是落后于参考时钟信号.这两种不同的信号决定着压控振荡器(VCO)是否需要提高频率或者降低频率.The PFD outputs these“up”and“down”signals to a charge pump.If the charge pump receives an up signal,current is driven into the loop filter.Conversely,if it receives a down signal,current is drawn from the loop filter.注.PFD产生的”up”,’’down”将输出给电荷泵,如果电荷泵接收到的是”up”信号,电流将进入环路滤波.相反的将从环路滤波器中吸取电流.The loop filter converts these signals to a control voltage that is used to bias the VCO.Based on the control voltage,the VCO oscillates at a higher or lower frequency,which affects thephase and frequency of the feedback clock.If the PFD produces an up signal,then the VCO frequency increases.A down signal decreases the VCO frequency.The VCO stabilizes once the reference clock and the feedback clock have the same phase and frequency.The loop filter filters out jitter by removing glitches from the charge pump and preventing voltage over-shoot.注.环路滤波将”up””down”信号准换为压控信号传递给压控振荡器.并控制压控振荡器的振荡频率.如果PFD产生的是”up”信号,VCO将提高振荡频率,相反减少振荡频率.直到参考时钟信号与反馈时钟信号具有相同的振荡频率以及相位.环路滤波器将滤除电荷泵产生的噪声振荡并且防止电压过载.When the reference clock and the feedback clock are aligned,the PLL is considered locked.To注.当参考频率与反馈频率一致的时候,PLL被称为锁定.A divide counter(M)is inserted in the feedback loop to increase the VCO frequency above the input reference frequency.VCO frequency(F VCO)is equal to(M)times the input reference clock(F REF).The PFD input reference clock(F REF)is equal to the input clock(F IN)divided by the pre-scale counter(N).Therefore,the feedback clock(F FB)applied to one input of the PFD is locked to the F REF that is applied to the other input of the PFD.The VCO output feeds post-scale counters which allow a number of harmonically related frequencies to be produced within the PLL.注.反馈回路上插入一个除法器(M)可以在参考时钟频率的基础上实现M倍频.PFD的输入频率等于输入频率/N.The output frequency of the PLL is equal to the VCO frequency(F VCO)divided by thepost-scale counter(C).In the form of equations:•F REF=F IN/N•F VCO=F REF×M=F IN×M/N•F OUT=F VCO/C=(F REF×M)/C=(F IN×M)/(N×C)where:•F VCO=VCO frequency•F IN=input frequency•F REF=reference frequency•F OUT=output frequency•M=counter(multiplier),part of the clock feedback path•N=counter(divider),part of the input clock reference path•C=post-scale counter(divider)。

pt4455工作原理

pt4455工作原理

PT4455是一款超外差无线发射IC,主要应用于315MHz至433MHz或250MHz至450MHz的UHF频段,支持OOK(开关键控)和ASK(幅度键控)调制方式。

以下是对PT4455工作原理的简要概述:

1. 频率合成:

PT4455基于PLL(锁相环路)技术来实现频率合成,通过外部晶振提供稳定的基准频率信号,PLL会按照预设分频比将基准频率倍增到目标工作频率。

2. 射频调制:

输入的数据信号控制射频载波的幅度变化(ASK),或者通过开关载波的“开”与“关”状态来传输信息(OOK)。

数据信号经过内部电路处理后,对产生的射频信号进行幅度或占空比调制。

3. 低电压操作:

IC设计为低电压工作模式,能够在2.2V至3.6V的电源电压范围内稳定运行,适应低功耗、电池供电的应用场景。

4. 输出匹配与功率放大:

PT4455的PA(功率放大器)部分采用开漏结构,并需要在输出端连接适当的扼流电感和直流阻隔电容器构成π型滤波网络,以匹配天线负载,提高效率

并确保合规的射频输出功率(例如+10dBm)。

5. 单稳态电路:

芯片上集成有单稳态电路,这有助于维持信号质量,减少噪声干扰,并可能用于信号整形或脉冲展宽等目的。

综上所述,PT4455通过集成PLL、射频调制模块以及功率放大器等功能组件,在简化外围元件数量的同时实现了高效的UHF无线发射功能。

在实际应用中,工程师需根据芯片数据手册提供的指导,正确设计电路布局和参数配置,以确保发射器能够正常工作且符合相应的法规要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

采用PLL(锁相环)IC的频率N(1~10)倍增电路

电路的功能

很多电路都要求把频率准确地倍增,使用PLL电路可很容易组成满足这种要求的电路。

例如主振频率为1KHZ,若使用倍增器内插10个脉冲,可变成

10KHZ的脉冲信号。

在VCO中,即使主振频率发生变化,也能获得跟踪主振荡频率的倍增频率N.F0,这是本电路的一大特点。

电路工作原理

具有PLL主要功能的C-MOSIC4046是一种最高工作频率为1MHZ的集成电路,将其与可编程除法器连接,便可构成把输入频率递增N倍的电路。

相位比较器PC2是检查FIN与N分步器输出的频率、相位是否相等的电路,它输出0~VP-P的信号,经环跑滤波器滤波后对VCO的振荡频率进行控制,VCO的可变范围FMAX~FMJA就是从输入频率FIN到N.FIN。

考虑到电路的误差和

长期稳定性实际上增加了若干安全余量。

在实际应该中不一定局限限于本电路。

下面介绍一下设计顺序:

如果N=1~10,VCO的振荡频率为1KHZ~10KHZ,若C3=0.01UF,则:

按此计算,VCO的控制电压范围没有余量,不能进行正常工作。

为此,决定FMIN值的RS应具有20%的安全余量,基计算值为8.8K现取9.1K,因为VCO的控制电压很小,所以FMTN应有50~100%的安全余量,并把最小控制电压设计得稍高一点,R4取180~220K,环路滤波器决定PLL电路的频响,用由R1和C2确定的时间常数分段,N=10时。

因为C2为1UF,所以R2=5.8*10的次方/10的次方=5.8K。

PC2的输入电阻为1M,即使FC=100HZ,输入电容器C1的容量也可取1600PF以上,这里取0.01UF,上述计算结果是大概的。