基于FPGA的通用异步收发机的设计

基于FPGA/CPLD的通用异步通信接口UART的设计

2 整体与各部分 功能详述

U R 处理的是并行数据转为串行信号和串行转为并行, AT

但并不是简单地转换 。分析 U R A T的结构 , 以看 出 U R 可 A T主 要 由数据总线 接 口、 制逻 辑和状态 接 口、 控 波特率发生 器 、 发 送逻辑和接 收逻辑等 部分组成 , 各部分间关系如 图 2 。 .

维普资讯

僵J拄木 与僵J佑 I I

基 于 F G / P D的 通 用 异 通 信 接 口 U R P A CL 步 A T的 设 计

TeD s no U R ( n e a A ycr os ee e Tas ie) a do P MC L h e g f A T U i r l s h nu ci r r m tr bs nF G P D i v s n o R v n t e

GA C L , P D,ii eat b t f e —u tm tgaeC rut o iigE i tSt tiueo micso I ert i i。c mbnn DA wt nB C L i o s u th ii h r s n c h P Dw lc nt c edg l r t t yt q iMya dep de t . sat l nrd csameh d t ei at ae ntepo rmma l gcd - a ss m ue n x einl r ceit ue to odsg u r b sdo h rga l e y i o n bel i e o vc i e矸, , P .T ecr u c o fUA T i n gae nF矗 CP D.T l d inicu e h rnmie L gc GA C I h oefn t no i R sit rtdi 1 e L ns e g n ldsteTa s t r o i、 s t t c ie o i a dteB u rt n rtr lfn t naegv nb HD rei lme tt no ei 、i la h Reev rL gcn a daeGe eao .Al u ci r ie yV L. h e h o mpe na o f sg s i d n mu -

基于FPGA的串口通信设计与实现

置和输人数据计算出响应

的奇偶校验位,它是通过

纯组合逻辑来实现的。

2.6总线选择模块

总线选择模块用于

选择奇偶校验器的输入是

数据发送总线还是数据接

收总线。

2.7计数器模块

计数器模块的功能

是记录串行数据发送或者

接收的数日,在计数到某

数值时通知UART内核模

块。 3 UART程序设计 UART完整的工作流程可以分为接收过程

关键词:FPGA:UART:RS232

引言 串行接口的应用非常广泛,为实现串口通 信功能一般使用专用串行接口芯片,但是这种 接口芯片存在体积较大、接口复杂以及成本较 高的缺点,使得硬件设计更加复杂,并且结构与 功能相对固定,无法根据设计的需要对其逻辑 控制进行灵活的修改。介绍了一种采用FPGA 实现串口通信的方法。 1串口通信协议 对一个设备的处理器来说,要接收和发送 串行通信的数据,需要一个器件将串行的数据 转换为并行的数据以便于处理器进行处理,这 种器件就是UART(Universal Asynchronous Re— ceiver/Transmitter)通用异步收发器。作为接iSl的 一部分,UART提供以下功能: 1.1将由计算机内部传送过来的并行数据 转换为输出的串行数据流; 1.2将计算机外部来的串行数据转换为字 节,供计算机内部使用并行数据的器件使用; 1.3在输出的串行数据流中加入奇偶校验 位,并对从外部接收的数据流进行奇偶校验: 1.4在输出数据流中加入启停标记,并从 接收数据流中删除启停标记。 2 UART模块设计 UART主要由UART内核、信号检测器、移 位寄存器、波特率发生器、计数器、总线选择器 和奇偶校验器7个模块组成。(见图1) 2.1 UART内核模块 UART内核模块是整个设计的核心。在数 据接收时,UART内核模块负责控制波特率发 生器和移位寄存器同步的接收并且保存 RS一232接收端口上的串行数据。在数据发送 时,UART内核模块首先产生完整的发送序列, 之后控制移位寄存器将序列加载到移位寄存器 的内部寄存器里,最后再控制波特率发生器驱 动移位寄存器将数据串行输出。 2_2信号检测模块 信号检测器用于对RS一232的输入信号进 行实时检测,一旦发现新的数据则立即通知 UART内核。需要注意的是,这里所说的 RS一232输入输出信号都指经过电平转换后的 逻辑信号,而不是RS一232总线上的电平信号。 2_3移位寄存器模块 移位寄存器的作用是存储输入或者输出 的数据。 2.4波特率发生器模块 由于RS一232传输必定是工作在某种波特 率下,比如9600,为了便于和RS一232总线进行 同步,需要产生符合RS一232传输波特率的时 钟。 2.5奇偶校验器模块 奇偶校验器的功能是根据奇偶校验的设

fpga中异步信号处理

fpga中异步信号处理

在FPGA中进行异步信号处理是一项重要的任务,因为许多

输入信号可能以不同的时钟信号、频率或相位到达FPGA。

处

理这些异步信号需要特殊的技术和电路设计。

以下是一些常用的异步信号处理方法:

1. 异步复位器:在FPGA中,可以使用异步复位器来处理异

步复位信号。

异步复位器可确保在输入复位信号到达时立即将FPGA重置为初始状态,而不需要等待时钟信号。

2. 异步触发器:通过使用异步触发器,可以将异步输入信号转换为同步的信号。

异步触发器具有单独的时钟信号和数据输入,当触发信号到达时,会将数据输入传递到输出。

这样,异步信号就可以与FPGA中的同步逻辑一起使用。

3. FIFO缓冲器:FIFO(First-In-First-Out)缓冲器用于将异步

信号转换为同步信号,并进行缓冲。

当异步输入信号到达时,它会存储在FIFO中,然后由同步时钟信号按顺序输出。

这样

可以确保异步信号按照正确的顺序被处理。

4. 时序分析和约束:在设计FPGA中的异步信号处理电路时,需要进行时序分析和约束。

时序分析可以帮助确定异步信号到达的时机、时钟边沿等。

时序约束可以确保异步信号处理电路能够按照预期的时序工作。

需要注意的是,异步信号处理在FPGA设计中需要特别小心,

因为异步信号可能导致不稳定的或不确定的行为。

因此,正确设计和验证异步信号处理电路是至关重要的。

基于FPGA的UART设计综述

四川师范大学本科毕业设计基于FPGA的UART设计学生姓名院系名称专业名称班级学号指导教师完成时间基于FPGA的UART设计电子信息工程专业摘要:UART(通用异步收发器)是一种应用广泛,协议简单,易于调试的串行传输接口。

FPGA是能高密度,低消耗完成所需要的逻辑功能的一种在线可编程器件,是现在业内提高系统集成度最佳技术之一,其可反复配置,且使用灵活。

VHDL 是描述电路功能或行为的一种硬件语言。

本文首先阐述了运用FPGA实现UART接口的意义。

接着介绍了UART的波特率发生器,发送功能和接收三大核心功能的理论知识。

FPGA的工作原理,配置模式以及VHDL语言实现状态机的相关理论基础。

给出了运用VHDL语言将UART三大功能嵌入在FPGA上的模块化设计方法。

设计包括四大模块:顶层模块,波特率发生器,UART接收器,UART发生器。

在FPGA片上集成UART主要功能,减少了电路板体积,同时电路也增加了可移植和反复配置功能,有效提高了电路的集成度和灵活性。

最后运用Quartus ii 9.1实现了其功能仿真。

关键词:FPGA UART VHDL 有限状态机The Design of Universal Asynchronous Receiver Transmitter Based on FPGAAbstract:UART (Universal Asynchronous Receiver Transmitter) is a widely used, simple protocol, easy to debug serial transmission interface. FPGA is capable of high-density, low-cost needed to complete a line of programmable logic devices, is now one of the industry's best technologies to improve system integration, which can be repeated to configure and use and flexible. VHDL description of the circuit function or behavior is a hardware language. This paper first describes the use of FPGA to realize the significance of the UART interface. Then introduced the theory of knowledge UART baud rate generator, sending and receiving three core functions. FPGA works, configuration mode and the VHDL-based state machine theory. Gives the UART using VHDL language to three functions embedded in the FPGA design. Design includes four modules: the top-level module, baud rate generator, UART receivers, UART generator. Integrated on-chip UART FPGA basic functions, reducing board space, the circuit also increases the portability and repeated configuration capabilities, improve the integration and flexibility of the circuit. Finally, the use of Quartus ii 9.1 implements its functional simulation.Key Words:FPGA ;UART ;VHDL;FSM目录摘要: (I)Abstract: (II)1 绪论 (1)1.1 课题背景 (1)1.2 课题研究现状 (2)1.3 课题研究内容与主要工作 (3)1.4 课题内容结构 (3)2 UART理论基础 (4)2.1 接口技术简介 (4)2.2 UART基本结构 (4)2.3 UART数据帧格式 (5)2.4 涉及到的理论计算 (6)3 设计工具 (7)3.1 课题硬件平台——FPGA (7)3.2 设计工具QuartusII简介与使用 (7)3.3 VHDL语言简介 (7)4 UART实现方案 (8)4.1 系统总体结构 (8)4.2 顶层模块设计 (8)4.3 波特率发生模块设计 (9)4.4 接收模块 (10)4.5 发送模块设计 (12)5 UART设计的仿真与验证 (15)5.1波特率发生模块仿真 (15)5.2 接收模块仿真 (15)5.3 发送模块仿真 (16)6 总结 (17)参考文献 (18)致谢 (19)附录 (20)基于FPGA的UART设计1 绪论在计算机的数据通信中,外设一般不能与计算机直接相连,它们之间的信息交换主要存在以下问题:(1)速度不匹配。

基于FPGA的通用异步收发器设计

龙源期刊网

基于FPGA的通用异步收发器设计

作者:林爱英胡惠敏贾树恒

来源:《现代电子技术》2011年第15期

摘要:采用Verilog HDL语言作为硬件功能的描述,运用模块化设计方法分别设计了通用异步收发器(UART)的发送模块、接收模块和波特率发生器,并结合现场可编程门阵列(FPGA)的特点,实现了一个可移植的UART模块。

该设计不仅实现了串行异步通信的主要功能,而

且电路简单,工作稳定、可靠,可以将其灵活地嵌入到各个通信系统中。

关键词:通用异步收发器;现场可编程门阵列;Verilog HDL;串行通信

中图分类号:TN915.04-34; TN402 文献标识码:A 文章编号:1004-373X(2011)15-0121-03。

基于FPGA的通用异步收发传输器控镦FLASH存储系统设计

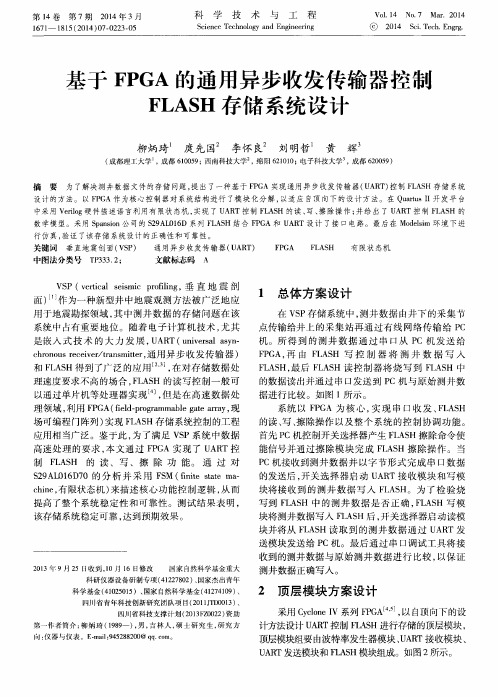

1 总体 方案 设 计

在V S P存储 系统 中 , 测井 数 据 由井 下 的采 集 节 点传输给井上的采集站再通过有线 网络传 输给 P c 机 。所 得 到 的 测 井 数 据 通 过 串 口从 P C机 发 送 给 F P G A, 再由 F L A S H 写 控 制 器 将 测 井 数 据 写 入 F L A S H, 最后 F L A S H读控制器将烧写到 F L A S H 中 的数据 读 出并通 过 串 口发 送 到 P c机 与 原 始测 井 数 据进 行 比较 。如图 1所示 。 系统 以 F P G A为 核心 , 实现 串 口收发、 F L A S H 的读 、 写、 擦 除操 作 以及 整个 系 统 的控 制 协 调 功 能 。 首先 P c机 控制 开关 选择器 产生 F L A S H擦 除命令 使 能信 号并通 过 擦 除模 块 完 成 F L A S H 擦 除 操作 。 当 P c机 接 收到测 井 数 据并 以字 节 形式 完 成 串 口数 据 的发送 后 , 开关 选 择 器启 动 U A R T接 收模 块 和 写 模 块将 接 收 到 的测 井 数 据 写 入 F L A S H。为 了检 验 烧 写到 F L A S H 中 的测 井 数 据 是 否 正 确 , F L A S H 写 模 块将 测井 数据 写入 F L A S H后 , 开关 选择器 启 动读 模 块并将 从 F L A S H 读 取 到 的测 井 数 据 通 过 U A R T发 送模块 发送 给 P c机 。最后 通 过 串 口调 试 工具 将 接 收到 的测井 数据 与 原始 测 井 数 据 进行 比较 , 以保 证 测井 数据 正确 写入 。

⑥

2 0 1 4 S c i . T e c h . E n g r g .

CPLDFPGA的UART接口设计之系统时钟(晶振)和波特率关系探讨

CPLD/FPGA的UART接口设计之系统时钟(晶振)和波特率关系探讨UART(Universal Asynchronous Receiver Transmitter,通用异步收发器)是一种广泛使用的异步串行数据通信协议。

目前各种MCU、串口通信IC等芯片或模块均支持UART通信,随着CPLD/FPGA应用得越来越广泛,用CPLD/FPGA 来设计UART等接口已是数字电路设计的常见应用之一。

由于UART是异步传输,没有传输同步时钟。

在CPLD/FPGA的UART接口设计中,为了能保证数据接收的正确性,数据帧接收时需采用比数据波特率至少高2倍的采样时钟对数据进行采样,才能保证对数据采样不失真或误码,实际波特率时钟采样比最好大于10倍。

简单起见,可以取中间时钟的采样值作为数据真实值,采样时钟从系统时钟(晶振)分频得到。

虽然理论上照此设计便可保证UART数据传送和接收时不发生误码,但由于在实际设计UART数据通信时,存在采样时钟偏差、数据帧格式、传输波特率及设计的舍入误差等因素的影响,对确定数据波特率传输的UART数据收发器,如何选择恰当的系统时钟(晶振)来保证UART通信的正常或者换句话说,对确定系统时钟(晶振)的UART数据收发器能支持多大的数据通信波特率?这是一个值得探讨的问题。

本文对采用CPLD或FPGA进行UART数据收发器设计时,上述提到的问题作个简单的讨论,错误之处还请大家包涵。

下面简单介绍一下UART时序及其发送接收过程。

发送数据帧过程:空闲状态,线路处于高电平。

当开始发送时,先发送起始位(线路保持1个数据位的低电平时间),接着按低位到高位的顺序发送数据位、奇偶校验位(如果需要校验的话)及停止位(停止位为高电平)。

接收数据帧过程:空闲状态,线路处于高电平。

当检测到线路的下降沿(线路电平由高变低)时说明线路接收到数据传输的起始位,这时可按照指定的波特率从低位到高位接收数据位、奇偶校验位(如果需要校验的话)及停止位,并完成数据校验,根据校验情况决定数据的处理。

基于FPGA的异步FIFO设计与实现

基于FPGA的异步FIFO设计与实现王伟国;张振东【摘要】随着现代数字电路系统密度和规模的不断扩大,一个系统中通常会包含多个时钟,因此不同时钟之间的数据传输成为亟待解决的问题.而一种可靠易行的解决方案就是异步FIFO.异步FIFO需要非常严格的多时钟技术,难以作出正确的设计合成和分析.本文提出了一种利用格雷码作为读写地址计数器的异步FIFO的设计方法,有效的避免了数据在不同时钟时间传输时遇到的亚稳态问题.并给出了综合仿真结果.%With the expanding of the density and scale of modern digital circuitry,a system will contain multiple clock.Therefore,the transfer of data between different clock becomes a serious problem needs to be solved.A reliable and feasible solution is asynchronous FIFO.Asynchronous FIFO require very strict clock technology,it is difficult to make the correct design of synthesis and analysis.This paper presents a design method of asynchronous FIFO which based on read/write counter in terms of gray code.This method effectively avoid the metastable state in the data transmission between different clock and given a comprehensive simulation results.【期刊名称】《聊城大学学报(自然科学版)》【年(卷),期】2012(025)003【总页数】6页(P79-84)【关键词】多时钟;异步fifo;verilog;HDL;格雷码【作者】王伟国;张振东【作者单位】中国科学院长春光学精密机械与物理研究所,吉林长春130033;中国科学院长春光学精密机械与物理研究所,吉林长春130033/中国科学院研究生院,北京100039【正文语种】中文【中图分类】TN4330 引言随着现代数字电路系统的实时数据处理能力的不断提高,逻辑电路的复杂程度和内核处理器的运算速度也快速增长,在使得一些复杂算法得以实现的同时也加剧了快速CPU与慢速外设之间的冲突.异步FIFO大量数据缓存的能力成功的解决了这一问题,但专用的高速异步FIFO芯片价格昂贵,且容量受限,随着现场可编程逻辑器件容量和速度的不断提高,利用现场可编程逻辑器件设计异步FIFO成为可行的方法.本文首先讨论了异步FIFO设计中经常出现的亚稳态问题和二进制计数器多位同时改变的问题,并给出解决办法,然后讨论了两种格雷码计数器的形式并作出比较,最后给出一种以格雷码为读写地址计数器的异步FIFO的设计方法和在设计异步FIFO时必须要注意的细节.1 多时钟电路中的亚稳态问题在一个时序电路中,合理的建立时间和保持时间是触发器正常工作的前提条件.对于下降沿触发的触发器而言,下降沿触发之前输入数据持续的最短时间是建立时间(setup time),下降沿触发之后输入数据持续的最短时间是保持时间(hold time).当电路时序不能满足setup time/hold time的要求时,系统时序就会出现混乱.在异步时序电路中,不同时钟之间是不存在任何关系的,必然会产生建立时间和保持时间冲突.解决系统时序问题常用双锁存器法如下图1所示,即在不同时钟之间传输数据时连续锁存两次.但是这种方法只是保证了电平的稳定,而在实际的系统中还需要FIFO作为不同时钟之间传输多位数据的接口.图1 避免亚稳态出现的双锁存器法2 异步FIFO指针对于同步FIFO来说,使用一个计数器计算读出和写入到FIFO缓存器中的数据量,计数器在只有写没读是递增,只读没写是递减,既读又写和没读也没写时保持不变.当计数器到达设定值时FIFO满信号置位,为零时空信号置位.在异步FIFO中,由于这种计算数据个数增减的计数器会被两个不同的时钟控制,因此这种计数器不能使用.所以,为了决定FIFO“空”和“满”状态,读指针和写指针必须相互比较.设计FIFO最主要的困难是生成FIFO指针和找到一个决定FIFO“空”和“满”状态的可靠方法.在FIFO设计中,读指针和写指针总是指向下一个要读和写的地址空间.当读或写操作完成后指针自动递增,当FIFO是空时读指针和写指针相等,当FIFO满时读指针和写指针也是相等.一种解决的方法是增加一个多余的MSB位来区分两种状态,当写指针递增超过地址范围时,写指针会递增MSB位,其他位清零,读指针同样也是.当读指针和写指针的MSB位不同时,意味着写指针比读指针多走了一圈,当MSB位相同时意味着走的圈数相等(如图2所示)图2 增加多余MSB后区分FIFO空和FIFO满的方法示意图当FIFO存储缓冲区需要(n-1)位地址时,地址指针用n位,当指针相等(包括MSB位)时空标志置位,当指针低(n-1)位相等且MSB位不等时满标志置位.2.1 二进制FIFO指针的情况二进制地址计数量会有多个位同时变化,因此在把二进制量在不同时钟域之间同步时会出现问题.一个解决的方法是取样并把周期计数量寄存在一个保持寄存器中,并发出一个ready信号,新时钟域收到信号并发出确认信号,这样变化的计数量就安全的传送到新时钟域.用这种方法不会产生上溢和下溢,因为当读指针递增到与写指针相等时,空信号置位,取样的写指针不反映当前写指针的值,而是小于当前值,故永远不能产生下溢,满信号也是如此.最常用的解决方法是用格雷码计数器,格雷码在每个时钟只有一位变换可以极大的减少在同步计数时错误的发生.3 格雷码计数器设计格雷码计数器的方法有很多,这里介绍二种简单直接的方法.下面详细介绍两种方法.3.1 格雷码计数器中的问题为了更好的理解把n-bit计数器转换成(n-1)-bit计数器时出现的问题,先考虑一下一个双重4-bit和3-bit格雷码计数器的例子如图3.图3 4-bit格雷码计数器示例及转换成3-bit格雷码时出现的问题在4-bit计数器中除了MSB位其余位关于中间对称,我们把2nd MSB位反相后,上半部分与下半部分的LSBs便相等.但是经过反相操作后整体便不是格雷码了,例如15(1100)到0(0000)的转变过程有两个bits变化,在下面的第一种格雷码计数器中会有解决方法.3.2 第一种格雷码计数器图4是第一种计数器的框图并是双重格雷码计数器中两个bits同时跳变的解决方法.其中假设输出寄存器的值是格雷码(ptr),此格雷码被输出到格雷码到二进制的转换器中,然后通过一个有条件递增的加法器并输出下一个格雷码值(gnext),连接到输出寄存器的输入端,如框图上半部分所示.(n-1)-bit格雷码简单地通过n-bit格雷码的2个MSBs的异或操作产生,(n-2)个LSBs不变.图4 第一种格雷码计数器示意图及其如何避免了两位同时跳变问题3.3 第二种格雷码计数器此种风格的格雷计数器(如图5所示)用了两组寄存器避免了把格雷码转换成二进制数的步骤.而且第二组寄存器也可以直接用来寻址FIFO存储器.n-bit格雷码指针仍然需要同步到不同的时钟域中.二进制指针可以更容易的通过计算产生“几乎满”和“几乎空”信号.因此在本论文的设计中用此种风格的格雷码计数器.图5 第二种格雷码计数器工作示意图4 总体设计及“空”和“满”信号的产生总体设计如图6所示,本设计方案共有四个模块,双口RAM模块,读控制模块,写控制模块,格雷码同步模块.写控制模块主要是当写使能信号有效且写满信号无效时产生写地址并实行地址递增功能,读控制模块实现相似功能,双口RAM模块用来使缓冲数据其读写动作可同时进行.4.1 “空”和“满”信号的产生“空”信号的产生比较简单,只需同步到读时钟域的写地址格雷码与n-bit的读指针的格雷码完全相等即可代码如下图6 异步FIFO总体设计框图及其信号说明但是,“满”信号的产生就没那么容易,简单地用n-bit格雷码作比较判断“满”信号是不可靠的.因为格雷码除了MSB位外是对称的如图3所示.在图3中假如写指针和读指针都指向地址7,此时写指针递增一次后,写指针指向地址8,读指针和写指针相比较,除了MSB位不同外其余各位均相等,满信号此时有效,但这是不符合实际情况的,错误的.这也是为什么在图4中应用双重n-bit格雷码计数器的一个原因.正确判断满信号的条件是:读写指针的n-bit格雷码的前两个MSBs都不相等,其余的写指针和同步读针相等.代码如下4.2 不同时钟速度因为异步FIFO被两个不同的时钟控制,很明显两个时钟运行在不同的速度下.当把较快的时钟同步到较慢的时钟时,会有一些计数值被跳过.当被同步的格雷码递增两次只被取样一次时也不会出现亚稳态问题,因为亚稳态出现在同步时钟上升沿附近有多位同时跳变时,而在两个同步时钟沿之间有格雷码跳变两次,第一次跳变距离同步时钟条边沿较远,只有第二次跳变在同步时钟沿附近,故不会产生亚稳态.当较快的格雷码计数器在较慢时钟沿之间递增多于一次,不会出现已经溢出却没有检测到的现象,因为同步到写时钟域的读指针滞后于当前的读指针,而写指针只会小于或等于同步读指针,故不会出现溢出.5 设计仿真及总结本设计采用Xilinx公司Spartan3A系列的XC3S1400A,封装时PG484,速度是-4,仿真器是ISE Simulator(VHDL/Verilog),硬件描述语言是Verilog,开发工具是ISE.最后对电路进行时序分析,结果为该FIFO运行速度可达到90.63MHz.wclk、rclk时钟周期分别为:75MHz、80MHz.先向FIFO中写入18个数据,当第16个数据被读入后wfull立即被置位如下图7.图7 写满仿真结果同时向FIFO中写入和读出数据,由于wptr要经过两个读周期才能同步到读时钟域,故在waddr递增后的第二个rclk的上升沿rempty才清零如下图8所示.本文对异步FIFO的结构和重要时序问题给予了详细的阐述,并得到了可靠的仿真结果.在高速数据采集系统中,采用高性能FPGA作为数据预处理和高速异步FIFO 作为数据采集缓存的应用都十分广泛.把FIFO集成在FPGA中简化了电路设计的复杂程度,增加了电路的集成化程度和可靠性,是未来高速数据采集系统的重要发展方向.图8 同时写入读出时的仿真结果参考文献【相关文献】[1] Clifford E.Cummings,Synthesis and Scrip ting Techniques for De signing Multi-Asynchronous Clock Designs[A].SNUG-2001,2001(3):2-8.[2]吴自信,张嗣忠.异步FIFO结构及FPGA设计[J].单片机及嵌入式系统应用,2000,22(3):1.[3]赵雅兴.FPGA原理、设计与应用[M].天津:天津大学出版社,1999.[4]夏宇闻.数字系统设计-Verilog实现[M].北京:高等教育出版社,2006.[5]王金明.Verilog HDL程序设计教程[M].北京:人民邮电出版社,2004.。

基于DSP+FPGA的UART设计与实现

基于DSP+FPGA的UART设计与实现摘要:UART作为RS232协议的控制接口得到广泛的应用,将UART功能集成在DSP和FPGA芯片组成的系统中,可使整个系统更为灵活、紧凑,减小电路体积,提高系统的可靠性和稳定性。

本文提出了一种基于DSP和FPGA 系统的UART 实现方法。

关键词:通用异步收发器;DSP;FPGA1 引言通用异步收发器(Universal Asynchronous Receiver/Transmitter,通常称作UART)是一种串行异步收发协议,应用十分广泛。

UART可以和各种标准串行接口,如RS232、RS485等进行全双工异步通信,具有传输距离远、成本低、可靠性高等优点。

一般UART 由专用芯片来实现,但专用芯片引脚较多,内含许多辅助功能,在实际使用时往往只需要用到UART 的基本功能,使用专用芯片会造成资源浪费和成本提高[1]。

在DSP和FPGA组成的系统中,利用DSP芯片完成UART数据收发控制,FPGA完成UART数据具体的收发时序,二者利用EMIF接口配合,即可实现UART通信功能。

这样设计可以大大减少电路体积、简化电路,也提高了系统的灵活性,使整个系统更加紧凑、稳定且可靠。

2 UART原理UART是一种串行数据总线,用于全双工异步通信。

工作原理是将数据的二进制位按位进行传输。

基本的UART 只需要两条信号线(收、发)和一条地线就可以完成数据的互通,接收和发送互不干扰。

在UART通信协议中,信号线上的状态位高电平代表“1”,低电平代表“0”。

图1 UART数据传输格式UART 数据传输格式如图1所示,一个字符由起始位、数据位、校验位和停止位组成(其中校验位可选)。

其中各位的含义如下:起始位:一位逻辑“0”信号,表示字符数据传输的开始;数据位:5~8位可选的逻辑“0”或“1”。

数据位的发送顺序为:先发送数据的最低位,最后发送最高位;校验位:包括奇校验或偶校验两种方式,即数据位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验)。

基于FPGA的异步收发器模块设计

相 与 , 产 生 用 来 启 动 数 据 流 发 生 器 工 作 的 时 钟 0T 1 xc k, 0 c1 tx k

时 钟 只 在 发 送 器 状 态 机 处 于 移 位

状 态 时 有 效 , 其 他 状 态 时 Ot c k x 1

●

●

:

:

状 态 结 束 时 , 状 态 机 切 换 到 奇 偶 校 验 状 态 , 状 态 机 将 奇 偶 校 验 位 插 入 , 然 后 状 态 机 切 换 到 停 止 位

状态 。

奇 偶 校 验 出 错 是 U T 采 集 数 据 AR 在 位 时 同 时 进 行 奇 偶 校 验 , 然 后 把 奇 偶 校 验 值 和 采 集 到 的 的 奇 偶 位

维普资讯

维普资讯

Test T c 3oI gY e h1 o

测 试 技 术 卷

一 ~

… ・ ・ ●● ● ● ・・

对 于 配 置 为 1比 特 停 止 位 长 度 ,

的 开 始 位 变 得 十 分 重 要 , 在 设 计 中 认 为 输 入 的 信 号 由 高 到 低 变 化 时 被 认 为 是 帧 的 开 始 位 。 然 而 为 了 避 免 输 入 信 号 噪 声 影 响 而 造 成 接 收 错 误 数 据 , 在 本 设 计 中 开 始 位 检 测 是 在 时 钟 波 特 率 50%之 前 为 低 。 由于 内部 时钟 c LK16 x是 发 送 接 收 数据 速 率 的 1 6倍 , 至 少 在 连 续 8个 CLK16x时 钟 周 期 内 检 测 到 开 始 位 为 低 则 认 为 开 始 位 是 有

时钟被 c k r 号 屏 蔽 。 1 t 信

基于FPGA的异步串行总线设计

如 果 接 收 方 收 到 的题 头 或 者 题 尾 任 意 一 个 有 误 . 就判 本 包数 据传 输 有 误 。并 且 在 本 包 数 据 末 端 增

加 了C C 8 验 码 ,对 发 送 的 整 个 串行Байду номын сангаас码 流 进 行 R 一校

校验 。具 体传 输协 议如 下 : … 串行 传输 格式 : 1 起 始 位 一 题 头 一 命 令 字 一 信 息 一 题 尾 一

等 。这 些 都 给 串行 总 线 的发 展 和应 用 提 供 了客 观

动 力 。 串行 总 线 按 传输 模 式 可分 为 同步 串行 总 线 和异 步 串行 总 线 两 类 ;同 步 串行 总线 在 传 输 过 程

可靠 、级联 简洁 ,系统性 能 升级方 便等 。通 过对 系

统要求 研究 分析 ,采用 高速 异步 串行 总线实 现模 块

通用元器件

d i 0 9 9 .s .5 3 4 9 .0 20 .0 o: . 6 /i n1 6 — 7 52 1 .2 7 1 3 js 0

基于F G 的异步 串行总线设计 PA

黄 振 . 郭 日峰

( 中国电子科技 集 团公 司第 二十研 究 所 ,陕西 西安 7 0 6 ) 10 8

一

间通 信 比较 符合要 求 。系统框 图如 图1 所示 。

瑶

F GA P 上位 机

种 是 采 用 专 用 串行 总 线 接 口芯 片 实现 ,实 现 方

便 简 单 ,但 二 次开 发性 差 ,不 利 于 系统升 级 维 护 ;

另一 种 是基 于 F G 等 可 编 程逻 辑 芯 片实 现 。后 者 PA 设 计 灵 活 ,二 次 开 发 型 良好 ,参 数 配 置便 捷 ,利

基于FPGA的UART模块的设计

基于FPGA的UART模块的设计作者:杨宗国李艳萍来源:《现代电子技术》2009年第02期摘要:为了实现计算机与基于FPGA图像处理系统的数据通信,这里用FPGA设计了一款简易通用异步收发器(UART)模块。

UART的主要功能是实现数据处理模块与RS 232串行数据接口之间的数据转换,即将送过来的并行数据转换为输出的串行数据流,由数据处理模块传送给计算机,还可以将串行数据转换为并行数据,供数据处理模块使用。

为了简化电路设计,减少电路面积,这里省略了UART系统中的奇偶检验模块。

关键词:FPGA;VHDL;串/并转换;并/串转换;UART中图分类号:TN971文献标识码:B文章编号:1004 373X(2009)02 019 04Design of UART Module Based on FPGAYANG Zongguo,LI Yanping(College of Information Engineering,Taiyuan University of Technology,Taiyuan,030024,China)Abstract:To realize data communication between computer and FPGA-based image processing system,a simple Universal Asynchronous Receiver Transmitter(UART)is designed by FPGA.The main function of UART is to realize data conversion between data disposal module and RS 232 serial port,that is to say,parallel data trinsmitted by data disposal module is converted into serial data flow,then it is transmitted into computer,the serial data is converted into parallel data for the usage of data disposal module.For predigesting circuit design and reducing electrocircuit proportion,parity check module is not needed.Keywords:FPGA;VHDL;S/P conversion;P/S conversion;UART0 引言在计算机的数据通信中,外设一般不能与计算机直接相连,它们之间的信息交换主要存在以下问题:(1)速度不匹配。

基于FPGA的UART16550的设计

基于FPGA 的UART16550的设计王建伟,王厚军,王 毅(电子科技大学自动化工程学院 四川成都 610054)摘 要:串行通信在数字信息系统以及控制系统中得到了广泛的应用。

针对传统UAR T 传输速率低、稳定性相对较差的状况,介绍了高速异步串口UAR T16550的工作原理与设计实现,并且给出在现场可编程门阵列FP GA 上的实现与验证仿真。

这项设计对于片上系统之间以及与PC 机之间的串行数据传输有了很大程度的改善。

关键词:UAR T16550;串口;FIFO ;FP GA中图分类号:TN919 文献标识码:B 文章编号:1004-373X (2007)09-054-02Design of UART16550B ased on FPG AWAN G Jianwei ,WAN G Houjun ,WAN G Y i(School of Automation ,University of Electronic Science &Techonolgy of China ,Chengdu ,610054,China )Abstract :Serial communication is widely used in digital information systems and control systems.The traditional UAR T transfers data at a low speed and is not so stable.This paper introduces a higher performance UAR T16550which is designed on a FP GA.The simulation shows it works well on the FP GA.It will greatly improve the efficiency of data transmission be 2tween SoC and PC.K eywords :UAR T 16550;serial port ;FIFO ;FP GA收稿日期:2006-09-061 引 言UAR T (Universal Asynchronous Receiver/Transmit 2ter ,通用异步收发器)是用于控制CPU 与串行设备通信的芯片,将由CPU 传送过来的并行数据转换为输出的串行数据流。

基于FPGA的异步FIFO的设计

基于FPGA的异步FIFO的设计作者:王小娟来源:《中国新通信》2016年第23期【摘要】简单的介绍了FPGA和异步FIFO的特点,针对在跨时钟域传递数据的系统中亚稳态的产生,采用异步FIFO(First In First Out,先进先出队列)口来缓冲传输的数据,以克服亚稳态,保证数据的正确传输。

由于常规异步FIFO模块中的RAM存储器读写寻址指针常采用格雷码计数器以及“空满”控制逻辑的存在,将使通过这两个模块的信号通路延时对整个模块的工作频率造成制约。

提出了一种在FPGA内实现高速异步FIFO的方法.使模块的工作频率得到一定提高。

【关键字】 FPGA FIFO一、FPGA简介FPGA(Field-Programmable Gate Array)[1],即现场可编程门阵列,是专用集成电路(ASIC)中集成度最高的一种,用户可对FPGA内部的逻辑模块和I/O模块重新配置,以实现用户的逻辑,因而也被用于对CPU的模拟。

用户对FPGA的编程数据放在Flash芯片中,通过上电加载到FPGA中,对其进行初始化。

也可在线对其编程,实现系统在线重构,这一特性可以构建一个根据计算任务不同而实时定制的CPU,这是当今研究的热门领域。

既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

二、异步FIFO简介FIFO ( First In FirstOut)[2],使用在需要产时数据接口的部分,用来存储、缓冲在两个异步时钟之间的数据传输在现代的集成电路芯片中,随着设计规模的不断扩大,一个系统中往往含有数个时钟,因而出现了跨不同时钟区域进行异步数据传输的要求。

异步FIFO ( First In FirstOut)是解决这个问题一种简便、快捷的解决方案。

根据FIFO的工作时钟,可将FIFO分为同步FIFO和异步FIFO。

同步FIFO是指读时钟和写时钟为同一个时钟,在时钟沿来临时同时进行读写操作;异步FIFO是指读写时钟不是同一个时钟,而是相互独立的。

基于FPGA的UART 16倍频采样的VHDL设计

基于FPGA 的UART 16 倍频采样的VHDL 设计概述随着电子设计自动化(EDA)技术的发展,可编程逻辑器件FPGA/CPLD 已经在许多方面得到了广泛应用,而UART(通用异步收发器) 是在数字通信和控制系统中广泛使用的串行数据传输协议。

因此越来越多用户根据自己的需要,以EDA 技术作为开发手段,用一块FPGA/CPLD 设计出符合自己需要的UART 芯片。

基于FPGA/ CPLD 的UART 设计在诸多文献中都有论述,在此不再对UART 整个功能模块实现做太多的论述。

本文着重分析UART 接收器起始位的检测。

3 倍频采样的缺陷首先,串行异步通信规定了字符数据的传送格式。

每一帧数据由起始位、数据位、奇偶校验位、停止位和线路空闲状态组成,格式如图1 所示。

一般情况起始位为1 位,数据位为5、6、7 或8 位、奇偶校验位为1 位,停止位为1、1.5 或2 位。

其中的起始位和停止位就是用来实现字符的同步。

在空闲状态,传送线为逻辑1 状态。

数据的传送总是以一个起始位开始的,接着是要传送的若干数据位,低位先行,最后是一个1 状态的停止位;那么,当接收器检测到一个1 向0 的跳变时,便视为可能的起始位。

起始位被确认后,就知道发送器已开始发送,当接收了已协议好的位数后并接收到字符帧中停止位就是一帧字符数据已发送完毕。

这样,接收器就知道发送器何时开始发送数据和何时结束发送数据。

要提高接收器的接收准确性,减少误码率,必须要用比数据波特率高n 倍(n≥1)的速率对数据进行采样。

文献2 中采用了非常规的3 倍频采样方法:用3 倍频的波特率对每一位数据进行采样(如图2 所示),然后对3 次采样结果进行判决。

如果3 次采样中至少有2 次为高电平,则接收这一位数据被判决为。

基于FPGA的UART设计与实现

基于FPGA的UART设计与实现作者:何勇来源:《现代电子技术》2010年第11期摘要:介绍了应用现场可编程门阵列(FPGA)设计和实现通用异步收发器UART的方法。

采用有限状态机模型形式化描述了UART的功能,在此基础上用硬件描述语言VHDL编程实现了UART,并使用Quartus Ⅱ软件中的嵌入式逻辑分析仪SignalTapⅡ对数据传输进行了检测,验证了设计的正确性。

关键词:FPGA; UART; 有限状态机; SignalTapⅡ中图分类号:TP332 文献标识码:A文章编号:1004-373X(2010)11-0154-03Design and Realization of UART Based on FPGAHE Yong(College of Computer Science & Information, Guizhou University, Guiyang 550025, China)Abstract: A method to design and realize the universal asynchronous receiver/transmitter(UART) based on the field programmable gate array(FPGA) is introduced.The functions of UART are described formally by using the finite state machine model, by the way, UART is realized on the basis of VHDL. Moreover, the data transmission is detected with SignalTapⅡ which is an embedded logic analyzer in Quartus Ⅱ. The result proves the validity of the design.Keywords: FPGA; UART; finite state machine; SignalTapⅡ0 引言通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART)可以和各种标准串行接口,如RS 232和RS 485等进行全双工异步通信,具有传输距离远、成本低、可靠性高等优点[1]。

基于FPGA的异步FIFO设计

万方数据 为) 贺占庄, 研究员, 硕士生导师, 研究方向为计算机控制技术。 * +;

第 G期

张维旭等: 基于 : ; < 的异步 . / 设计

・* F E・

个没有关系的时钟域之间传递信号, 也会出现 ! / " # $ & ’ ( ) % 冲突。虽然亚稳状态是不可避免的, 但是, 可以通过下面

[ ] * 。 的方法将其降低到一个能够接受的范围之内

会产生向上溢出 (’ . / 如果 进 行 一 个 写 入 动 作, 5 " 1 2 , 一个有用的数据会被新写入的数据覆盖。为了避 3 ( ’ 4) 免这种错误的产生, 应该对 . / 设置满和空两个信号。 对满信号置位表示 不能再执行写 . / 已经处于满状态, 入动作; 对满信号复位表示 还可以执行写入 . / 非满, 动作; 对空信号置位表示 这时没有有 . / 处于空状态, 效数据可以读出; 对空信号复位说明 这时可 . / 非空, 以进行读操作。 当读指针和写指针相等时, . / 可能处于满状态或 空状态。可以用不同的方法判断 . / 究竟处于什么样 的状态, 也就是说究竟是写指针从后面追上了读指针还是 读指针从后面追上了写指针。文中采用设置一个额外状 态位的方法来区分两种状态。读写指针由它的地址位和 状态位组成。地址位随着相应的操作递增, 指针由最后位 置返回初始位置时状态位取反。当读写指针的状态位和 地址位全部吻合的时候, 读写指针经历了相同次数的循环 如果读写指针的地址位相 移动, 这时 . / 处于空状态; 同而状态 位 相 反, 说 明 写 指 针 多 经 过 了 一 次 循 环, 这时 . / 处于满状态。使用下面的公式来判断空满状态: (读指针88写指针) " 6 # 8 % 7 (读地址88写地址 99 读指针状态位! 88 3 $ ( ( 8 写指针状态位)

基于FPGA的UART设计与实现

基于FPGA的UART设计与实现

董秀洁;付凯

【期刊名称】《中原工学院学报》

【年(卷),期】2012(023)002

【摘要】提出了一种基于FPGA的UART的实现方法.利用有限状态机和硬件描述语言VHDL实现了通用异步收发器UART IP核的设计,给出了用VHDL实现UART 的数学模型,并进行了仿真分析.结果表明,各项通信指标均满足要求,并可提高系统的可靠性和稳定性.

【总页数】4页(P66-69)

【作者】董秀洁;付凯

【作者单位】中原工学院,郑州450007;中原工学院,郑州450007

【正文语种】中文

【中图分类】TN402

【相关文献】

1.基于FPGA的UART设计与实现 [J], 于志翔

2.基于FPGA的UART模块设计与实现 [J], 刘博

3.基于FPGA的UART设计与实现 [J], 刘宝军;王中训;娄阳;张珉;钟强

4.基于FPGA的UART抗干扰接收装置设计与实现 [J], 张名淑;张雅迪;王旭;陈飞;钱祥利

5.基于FPGA的UART串行通信参数自适应设计与实现 [J], 杨洋;和蕾;王旭;钱祥利;陈飞;李静

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Jan.2008

53

基于FPGA的通用异步收发机的设计

赵权, 刘翠玲

(北京工商大学信息.r-希2学院,北京 100037)

摘 要:阐述了通用异步收发机(UART)异步串行通信原理,介绍了实现UART异步串行通信的 硬件接口电路及各部分硬件模块,同时还介绍了用硬件描述语言Verilog来开发UART通信接口 电路模块的方法.研究基于Verilog语言,结合有限状态机的设计方法来实现UART,将其核心功 能集成到现场可编程门阵列(FPGA)_L,使其整体设计紧凑、小巧,实现的UART功能稳定、可靠; 同时,与其他设计方法相比较,利用有限状态机的方法具有结构模式直观简单,设计流程短,程序层 次分明,易综合,可靠性高等优点,这种方法必将在电子设计自动化(EDA)技术申发挥重要作用.

可运用在中低端的异步通信系统中

参考文献:

n 1J 巴斯克尔.Verilog HDL综合实用教程[M].孙海平, 译.北京:清华大学出版社,2004.

眩 1J 王伟.Verilog HDL程序设计与应用[M].北京:人民 邮电出版社,2005.

B 1J 董长富,郭超平,宋渝.基于FPGA的多串口模块的设 计和实现[J].电子元器件应用,2006,11(8):43—

读8位并行数据‘——,』输出逻辑高电平

跏J广I氘撼

图7发送端信号模块

率进行,波特率可以通过接口模块的总线接口进行 设置.UART收发的每一个数据宽度都是波特率发

生器输出的时钟周期的16倍,即假定当前按照

9 600 b/s进行收发,那么波特率发生器的输出时钟

频率应该为9 600 x 16 Hz.假定提供的外部时钟为

收稿日期:2007—09—27 作者简介:赵权(1982一)。男。河南信阳人,硕士研究生,研究方向为仪器仪表及其自动化;

刘翠玲(1965一),女,黑龙江大庆人.教授。博士,主要从事模式识别与智能控制系统研究

万方数据

北京工商大学学报(自然科学版)

2008年1月

一个下降沿.如图1,方案中采用1位起始位,8位 数据位,不设奇偶校验位,2位停止位,波特率可调 的数据传输方式[2J.

:inst一一一一一一一一一一一一一一一一一一一一一j 图4接收端信号模块

2.2发送模块 发送器实现的功能是将输入的8位并行数据变

为串行数据,同时在数据头部加起始位,在数据位尾 部加奇偶校验位和停止位.相对于接收部分来说,

万方数据

第26卷第1期

赵权等:基于FPGA的通用异步收发机的设计

55

^丽试雨f一一一一一一一一一一一一一一一:

state5状态:输出停止位. 利用Quartus生成的发送系统信号端口模块如 图7,利用ModelSim对设计文件进行Verilog仿真 的波形如图814-5]. 2.3波特率发生器 设计的UART的接收和发送按照相同的波特

万方数据

图8发送系统端口Verilog仿真波形

如果希望输出10 000 Hz的波特率,可以得出从 总线写入的数值为

图5接收系统端口Verilog仿真波形

当电路复位以后,控制器首先进入开始状态,当检测 到缓冲器THR不空时,转入到移位状态,控制发送 器发送低电平开始位和有效数据位.当计数器计数 满一个波特时钟后,发出移位信号,发送下一位数据 位;当8位有效位发送完之后,进入校验状态,发送 奇偶校验位;最后转入停止状态,发送停止位;这样 就完成了数据的发送.发送系统的有限状态图机 FSM如图6.

由于串行数据帧与接收数据时钟是异步的,接 收器功能实现的关键是接收器的时钟与每个接收字 符的时钟同步.一个有效的办法是接收器采用高速 率的时钟对串行的数据采样,如果采样频率是位时 钟频率的整数倍,就比较容易实现.理论上倍数越 高,接收数据各位的分辨率越高.在实际设计中,一 般最大选择16倍.

要保证异步通信的双方准确无误地交换信息, 必须有效控制采集通信线路上电平信号的时机.根 据实际选择恰当的时机能够使系统准确稳定.如图 2所示的D点是每一数据位周期的中心点,所以一 般系统中的D点是最佳采集时机.当所用的开发系

统的时钟频率和波特率不匹配时就容易产生固定的 频差.采用高稳定度的时钟可以将误差缩小,只要 留出比较小的余度就可以.因此,稍微靠近A点的 B点和C点是最佳采集时期[3J.

起始位

数据DO 数据D1

B CDE F

启动检测A

G

图2采样过程分析

在异步串口接收中,帧结构起了至关重要的作 用.如果在数据帧的结尾第一个停止位的位置抽取 到了低电平,说明发生了帧错误,应该进行帧数据的 滑动,直至找到帧头和帧尾.用Verilog实现上述各 功能的有限状态图机FSM(finite state machine)流 程如图3.

I 600 000÷(16 x 10 000)一1=9(09H). (2) 2.4综合实现

在ModelSim中进行前段仿真,然后利用Quar— tus生成的.Vo文件在ModelSim中进行后端仿真, 将两次仿真结果进行对比,发现后端仿真中的输出 波形有轻度延迟,仿真结果符合实际.

利用革新实验平台,在QuatusⅡ6环境中进行

statel状态:输出起始位之前的一位逻辑1,然 后转入到state2.

state2状态:输出起始位0.综合statel和 state2可知,在第一位数据位之前,有一个从1到0 的下跳变.

state3状态:根据8位数据,检验校验位为逻辑 1还是逻辑0,校验位在state4状态输出.

state4状态:该状态机的功能在state3中已经讲 过.

北京工商大学学报(自然科学版)

2008年1月

编译、综合,以及时序仿真,利用Altera Programmer 通过Jtag电缆下载到相应的可编程器件中.

3 结束语

利用Verilog设计的灵活性实现了UART通信 功能。可以实现对数据的接收和发送,并可以在接收 数据时对其校验位、停止位进行判断,在发送数据时 可以形成完整的一帧数据格式.其接收和发送数据 的时钟有内部波特率发生器产生,根据预置的分频 系数。对外部时钟进行分频,产生需要的接收或发送 时钟.将该UART设计作为一功能块嵌入到一个 FPGA/CPLD实现的数据采集与处理系统中,可以 成功地实现和远端的PC机进行异步串行通信.实 验证明该UART设计占用资源少,工作稳定可靠,

1 UART的通信原理

UART即通用异步收发器,是一种串行通信方 式.数据在传输过程中是通过一位一位地进行传输 来实现通信的.串行通信具有传输线少、成本低等 优点,缺点是速度慢.

串行通信分为两种类型:同步通信方式和异步 通信方式.方案采用的是异步通信方式,其特点是: 通信的发送方和接收方各自具有独立的时钟,传输 的速率由双方约定.国际上规定的一个串行通信波 特率标准系列是:110、300、600、1 200、1 800、2 400、 4 800、9 600、19 200.方案采用的波特率是 9 600 Hz【1].

2 UART的Verilog HDL实现

2.1接收模块 在异步串行通信中,需要采取有效的措施来避

免错误的出现:找准帧头起始位;选择比较可靠的采 集点,确保数据判断正确;采取有效的方法判断帧格 式,纠正帧错误.

接收端不断检测线路的状态,若连续为1后又 检测到一个0。就知道发来一个新字符,应马上准备 接收.所以只需要每个时钟周期都循环检测数据 线,当发现数据线为低电平时就认为找到了起始位, 显然这个时刻落后于起始位跃变沿的时间.

一

起始位

停止位 I

l,LjET’I' 8位数据

停止位

叭I l 1

0/1 o/l 0/1 0/1 0/1 0/1 0/1 0/l l

l

I}

I

.氐位

高位

位宽取决于波特率

5日

位

空闲位 1

ll 10

下降沿指 玎≮一 字符的开始

图1异步串行通信的字符格式

采用/kitera公司的Quartus II为设计平台,设计 采用的(hardware description language,HDL)语言为 Verilog,作为本系统逻辑描述程序的唯一表达语言, 采用自顶向下的设计原则,对异步接收发送器 (uART)进行设计.同时选用Altera公司的ACEX 1K系列器件EPlKl00QC208—3来实现最终的 UART电路.没有检到起始位V空闲 \状态

\ ▲

存人数据l

寄存器I

,,工

,,数据

k正确

虚假起始位

检测到起始位

\

停止位错误 放弃数据

停止位有效

,起始位、

\确认/, \/

采样|起始位 数据l有效

I

y7—、 /停止位\ \确认/

图3接收系统状态转换示意

接收系统信号端口模块如图4,利用Quartus进 行Verilog仿真的波形如图5.

1.6 MHz,可以很简单地通过总线写入不同的数值

到波特率发生器保持寄存器,然后用计数器的方式 生成所需要的各种波特率,即分频器[5】.计算公式

如下,RS为所期望的波特率:

!鱼QQ QQQ一,“ (16×Rs)

,1、 、1 7

输出奇偶校验位’:::二)判断奇偶校验位

图6发送系统状态转换示意

state0状态:当UART被复位信号复位以后。 状态机将立刻进入这一状态,在该状态下读8位并 行数据,并转到statel.

第26卷第1期 2008年1月

北京工商大学学报(自然科学版) Journal of Beijing Technology and Business University(Natural Science Edition)

文章编号:1671—1513(2008)01—0053—04

V01.26 No.1

46.

-!l 1J 常晓明.Verilog HDL实践与应用系统设计[M].北 京:北京航空航天大学出版社,2004.