C8051F单片机

C8051F单片机使用注意事项

C8051F单片机使用注意事项C8051F单片机使用注意事项由于C8051F单片机是3.3V低功耗、高速单片机,与大家过去应用传统的5V供电低速单片机在引脚处理与PCB布板方面会有一些区别,我们总结了这方面的经验,提供给大家,以避免在应用设计上走弯路。

一、电源和地线方面的处理1、模拟电源和数字电源要分别供电,可以使用两个稳压源分别供电,但是两个电源之间的电压差必须满足数据手册中的规定(<0.5V,小于0.3V是比较理想的)。

实际应用中模拟电源和数字电源可以来自同一个稳压器的输出,只在AV+与VDD之间接简单的滤波器也是很有效的。

这里要加一个小电感,也可以用低阻值的电阻(通常2欧姆,电阻要有足够的寄生电感。

) 这种方式既能降低成本又能减少体积。

(关于这一点可以参考C8051F各种目标板的原理图的电源部分)。

2、在地线方面,模拟地和数字地要分开布线,然后在一点通过磁珠连接,在实际应用中也可以使用0欧姆绕线电阻连接的。

该绕线电阻要有寄生电感,另外,在布线时一定要注意地线应该尽可能的粗,或者采用大面积覆地,电源线也要尽量粗,并且在单片机所有电源和地之间以及每个外围集成电路的VDD和GND间加去耦合电容。

3、如果所使用的器件上有模拟电源,模拟地,数字电源和数字地,所有这些引脚不可以悬空,必须连接。

二、在严酷环境下使用C8051F器件时,在PCB设计时应注意那些问题?在严酷条件下使用C8051F器件时,我们提供给您的一般性建议如下:1) 在器件的每个电源引脚处放置0.1μF和1.0μF的去耦电容,而且要尽可能地靠近芯片。

这一点适用于板上所有的IC(集成电路)。

*2) 尽可能将板上不使用的空间接地,即所谓的大面积覆铜。

3) 在靠近器件外部振荡器引脚处放置外部晶体和其他振荡器元件(如果可行的话)。

4) 使用最短的连线以避免产生“天线”,尤其在下列引脚处:/RST,MONEN,XTAL1,XTAL2,TMS,TCK,TDI和TDO。

C8051F单片机常见问题及解决方案

C8051F单片机常见问题及解决方案1000字C8051F单片机常见问题及解决方案C8051F系列单片机是一款常用的32位微型控制器。

在使用中,常常会遇到各种问题,以下列出了一些常见问题及解决方案,供大家参考。

1.如何选择晶振?C8051F单片机的内部时钟频率有两种选择:内部振荡器(24MHz)和外部晶振(最高可达25MHz,具体要看选用的晶振规格)。

选择晶振时,可以考虑系统时钟的需求量,以及对系统稳定性的要求。

2.如何处理硬件复位?硬件复位是指在单片机系统上电时,自动执行初始化操作的过程。

C8051F单片机实现硬件复位的方法有两种:使用复位电路(RST#复位)、通过预编程的复位向量(从C2寄存器获取程序计数器初始值)。

通常情况下,我们可以使用预编程的复位向量,以方便地重新启动程序。

3.如何处理软件复位?软件复位是指通过程序代码实现的复位。

在C8051F单片机中,软件复位可以通过配置系统管理单元(SMU)来实现。

这个过程通常包括设置复位源、配置访问时间窗口、启用复位源、复位等操作。

在进行软件复位之前,我们需要仔细查看数据手册中的相关章节,并根据实际需求进行配置。

4.如何配置GPIO口?GPIO(通用输入输出)口是单片机系统中的基本输入输出接口,用于实现I/O操作和外设控制等功能。

在C8051F单片机中,GPIO口的配置可以通过专用寄存器(P0、P1、P2、P3等)来实现。

具体的配置包括:指定口线方向、设置上下拉电阻、确定端口中断引脚等。

5.如何编写中断服务程序?中断服务程序是用于响应中断请求、处理相应事件的程序代码实现。

在C8051F单片机中,编写中断服务程序包括两个步骤,一是将中断请求源打开(或禁止),二是编写相应的中断处理程序。

具体的实现方法会有一些细微的差别,需要仔细查看数据手册中的相关章节。

6.如何使用定时器?定时器是单片机中常用的计时器件,用于实现时间处理、调度和控制等功能。

在C8051F单片机中,使用定时器需要涉及一些内容,包括:设置定时器的工作模式、配置计数器时钟源和初始化计数器等。

《C8051F单片机》课件

发效率。

3

常见应用案例

了解C8051F单片机的常见应用案例可以 帮助您更好地理解实际应用场景。

实验操作

实验材料准备

实验步骤

在进行实验操作前,您需要购买 一些电路测试仪器,例如万用表、 示波器等。

您需要按照实验步骤进行实验。 请务必仔细阅读实验说明,以确 保实验的顺利进行。

实验结果分析

在实验结束后,您需要对实验结 果进行分析和总结。这可以帮助 您更好地理解C8051F单片机的工 作原理和应用场景。

C8051F单片机课件

这份PPT课件是针对C8051F单片机开发而制作的。本课程会涵盖硬件设计、接 口设计、软件开发和实验操作等各个方面。通过学习本课程,您将学会如何 使用C8051F芯片,开发出各种电子设备。

C8051F单片机概述

什么是C8051F单片 机?

C8051F单片机是一种集成了 微处理器、存储器和各种输 入输出接口的电路芯片。

基本特性

C8051F单片机有着低功耗、 高速度、高精度、低体积的 基本特性。

应用领域

C8051F单片机应用广泛,包 括汽车电子、医疗设备、智 能家居、工业自动化等各种 领域。

硬件设计

电路原理

了解C8051F单片机的电路结构和 原理非常重要。掌握这些知识可 以帮助您更好地设计硬件电路。

接口设计

单片机的接口设计是硬件设计的 重要部分。不同的接口设计会影 响到整个电路的稳定性和性能。

Q& A

1 常见问题解答

在学习C8051F单片机的过程中,您可能会遇 到一些问题。我们为您准备了一些常见论与交流

与其他学习者进行讨论和交流,可以帮助您 更好地理解C8051F单片机的应用和工作原理。

总结

第2章 C8051F单片机的结构与原理

常用的特殊功能寄存器

ACC (Accumulator)累加器:存放运算操作数和结果。 B (B Register)寄存器:乘除法中与ACC配合使用。 SP(Stack Pointer)8位堆栈指针:复位值为0x07,使用时根 据需要可重新赋值。数据入栈,SP加1,与80X86相反。

DPTR (Data Pointer)16位数据指针:访问外部存储器的地址指

复位值

00000000

SFR地址:0xD0

位7 位6 位5 位4 位3 位2 位1

位7( CY):进位标志

• 有进/借位(减法)时,臵1。

位6( AC):辅助进位标志

• 向高半字节有进/借位时,臵1。

位5、1( F0、F1):用户标志

•可供用户编程使用的通用标志位。 21

PSW的各位定义 (2)

24

1.XRAM存储器空间的访问

16位形式的MOVX指令,访问DPTR 指向的存储器 单元。 如:

MOV DPTR,#1234h

MOVX A,@DPTR

;立即数0x1234 → DPTR

;(0x1234)→ A

8位形式的MOVX指令,用EMIOCN存放待访问地址 的高8位,由R0或R1给出待访问地址的低8位。如:

寻址方式和对PSW标志的影响。

指令时序与标准8051不同, CIP-51中机器周期与时

钟周期相等,MCS-51中机器周期=12×时钟周期。

采用流水线结构,大多数指令执行所需的时钟周期数 与指令的字节数一致。 条件转移指令,不发生转移时 比发生转移时少一个时钟周期。

35

2.3.1 寻址方式 (1)

PRTSEL EMD2 EMD1 EMD0 EALE1 EALE2

C8051F系列单片机的初始化

C8051F系列单片机的初始化C8051F系列单片机是由美国Silicon Laboratories公司研发的一款8位微控制器,它具有强大的功能和灵活的性能,是一种广泛应用于各种电子设备中的微控制器。

在使用C8051F系列单片机之前,需要进行初始化操作,以确保单片机能够正常工作。

下面将介绍C8051F系列单片机的初始化过程。

1. 系统时钟初始化在初始化单片机之前,需要先配置它的系统时钟。

C8051F系列单片机的系统时钟可从外部晶体振荡器或内部RC振荡器提供。

通过设置相关的寄存器,可以选择使用哪一种时钟源,并配置其频率。

2. 系统时钟分频器初始化对于大多数应用程序而言,操作系统时钟的速度往往太快,因此需要对其进行分频,减少操作速度。

C8051F系列单片机提供了一个系统时钟分频器,通过设置相关的寄存器,可以选择分频比例,将操作速度减慢。

3. I/O端口初始化C8051F系列单片机具有多个I/O端口,用于输入和输出数据。

在初始化单片机时,需要设置每个I/O端口的输入和输出模式,以及电平状态和电流限制等参数。

4. 中断初始化C8051F系列单片机支持多种中断模式,可以在程序执行期间随时中断当前任务,处理新的事件。

在初始化单片机时,需要配置中断引脚和中断向量表等参数。

5. 定时器初始化C8051F系列单片机具有多个定时器,用于计时和延时等功能。

在初始化单片机时,需要设置每个定时器的计数模式、频率、触发条件和计时范围等参数。

6. 串口初始化C8051F系列单片机支持串口通信,可以与其他设备进行数据交换。

在初始化单片机时,需要设置串口的通信协议、波特率和数据格式等参数。

7. ADC/DAC初始化C8051F系列单片机具有模拟转换模块,可以对模拟信号进行采样和变换。

在初始化单片机时,需要设置ADC/DAC的采样率、分辨率和参考电压等参数。

通过以上步骤,就可以完成C8051F系列单片机的初始化。

在开发具体应用程序时,还需要根据实际需求对各个模块进行进一步配置和编程。

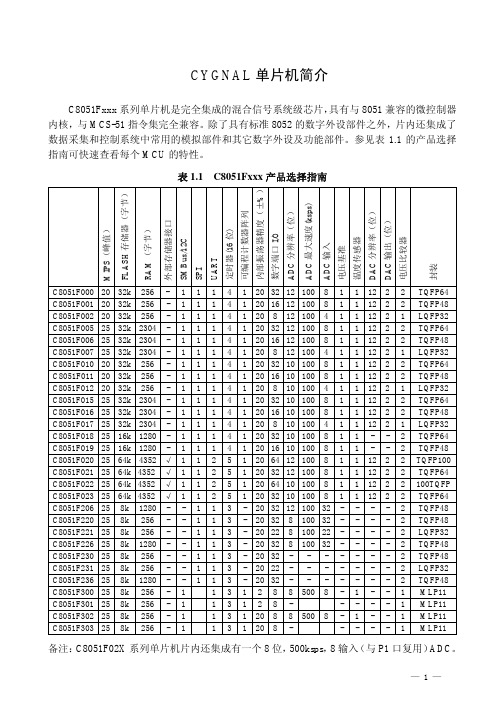

C8051F单片机简介

C8051F021 25 64k 4352 √ 1 1 2 5 1 20 32 12 100 8 1 1 12 2 2 TQFP64

C8051F022 25 64k 4352 √ 1 1 2 5 1 20 64 10 100 8 1 1 12 2 2 100TQFP C8051F023 25 64k 4352 √ 1 1 2 5 1 20 32 10 100 8 1 1 12 2 2 TQFP64

C8051F005 25 32k 2304 - 1 1 1 4 1 20 32 12 100 8 1 1 12 2 2 TQFP64

C8051F006 25 32k 2304 - 1 1 1 4 1 20 16 12 100 8 1 1 12 2 2 TQFP48

C8051F007 25 32k 2304 - 1 1 1 4 1 20 8 12 100 4 1 1 12 2 1 LQFP32

C8051F226 25 8k 1280 - - 1 1 3 - 20 32 8 100 32 - - - - 2 TQFP48

C8051F230 25 8k 256 - - 1 1 3 - 20 32 - - - - - - - 2 TQFP48

C8051F231 25 8k 256 - - 1 1 3 - 20 22 - - - - - - - 2 LQFP32

C8051单片机基础C8051F单片机结构及原理详解

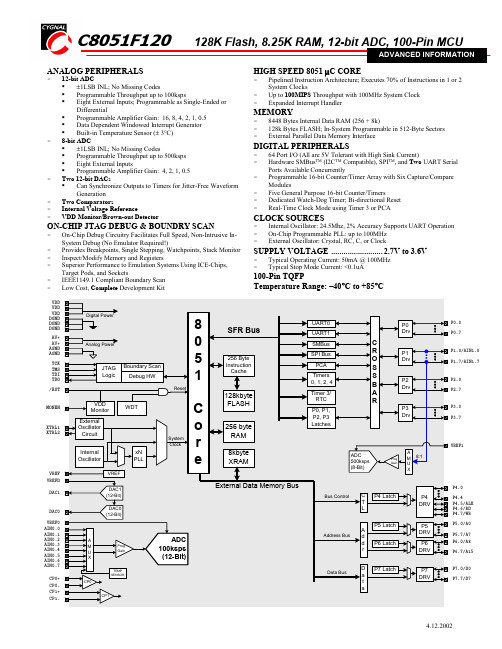

2.2 C805lF单片机的结构与原理

2.2.1 C8051F02x单片机的组成与结构 C8051F020单片机以8051内核为中心,

通过SFR总线、外部数据存储器总线、系 统时钟线、复位线等与64KB闪存、4KB XRAM、数字功能模块(UART、SPI、定时器 等)、模拟功能模块(比较器、A/D、D/A 等)、片上时钟系统和JTAG逻辑电路等相 连。是一个完整的单片机片上系统,可以 用作为一个闭环测量控制系统。

2.1 C8051F的CIP-51内核

2.1.3 CIP-51内核的基本部件

5.流水线结构 CIP-51采用了流水线处理结构,用

于控制和管理取指令和执行指令的过程。 其已经没有机器周期时序,指令执行的最 小时序单位为系统时钟,大部分指令只要 1个~2个系统时钟即可完成。在流水线结 构中包括指令寄存器和指令译码器。

2.1 C8051F的CIP-51内核

2.1.3 CIP-51内核的基本部件

6.中断系统 中断系统的主要作用是对外部或内

部的中断请求进行管理与处理。C8051F系 列单片机的中断系统可以满足一般控制应 用的需要,C8051F系列单片机的中断源最 多可达22个。

2.1 C8051F的CIP-51内核

2.2 C805lF单片机的结构与原理

2.2.2 引脚定义及功能

下面对部分专用引脚的功能进一步说明。 (1)VDD和GND各为3个引脚,使用时建议全部

接上,这样可提高抗干扰能力。 (2)如果在系统中没有使用模拟部分,芯片的

模拟电源V+和模拟地AGND也要连接。 (3)VREF端也可以作为带隙电压基准输出驱动

改良创新后的51单片机-----C8051F

改良创新后的51单片机-----C8051FMCS-51单片机及其衍生产品在我国乃至世界范围获得了非常广泛的应用,尤其在我国,大部分大专院校都采用MCS-51单片机作为教学机型,大部分单片机系统工程师都熟悉MCS-51单片机。

随着一些髙集成度、髙性能的8位和16位RISC单片机的推出,基于8051内核的单片机正面临着退出市场的境地。

因此一些半导体公司开始对传统8051内核进行大的改造,主要是提高速度和增加片内模拟和数字外设,以期大幅度提高单片机的整体性能.Silabs集成产品公司推出的C8051F单片机是这类MCS-51单片机的典型代表,也是目前功能最全,速度最快的8051衍生单片机。

C8051F单片机的出现令业界人士耳目一新,使广大单片机系统设计人员看到了MCS-51单片机的曙光。

C8051F单片机简介C8051F单片机是完全集成混合信号系统级芯片(SoC),具有与8051兼容的高速CIP-51内核,于MCS-51指令集完全兼容,可以使用标准803×805X汇编器和编译器进行软件开发。

除了具有标准8051的数字外设部件之外,片内还集成了数据采集和控制系统中常用的模拟部件和其它数字外设及功能部件。

这些外设或功能部件包括模拟多路选择器、可编程增益放大器、ADC、DAC、电压比较器、电压基准、温度传感器、SMBUS、12C、UART、SPI、定时器、可编程计数器、定时器阵列(PCA) 、数字I/O端口、电源监视器、看门狗定时器(WDT)和时钟振荡器等。

所有器件都有内置的FLASH程序存储器和256字节的内部RAM,有些器件内部还有位于外部数据存储器空间的RAM,即XRAM。

C8051F单片机的主要特点C8051F单片机中有丰富的模拟和数字资源,并采用了一些在单片机中前所未有的新技术,在CPU内核的内部和外部有几项关键性的改进。

提高了整体性能,更易于在最终使用中使用。

下面对C8051F单片机的主要特点加以介绍。

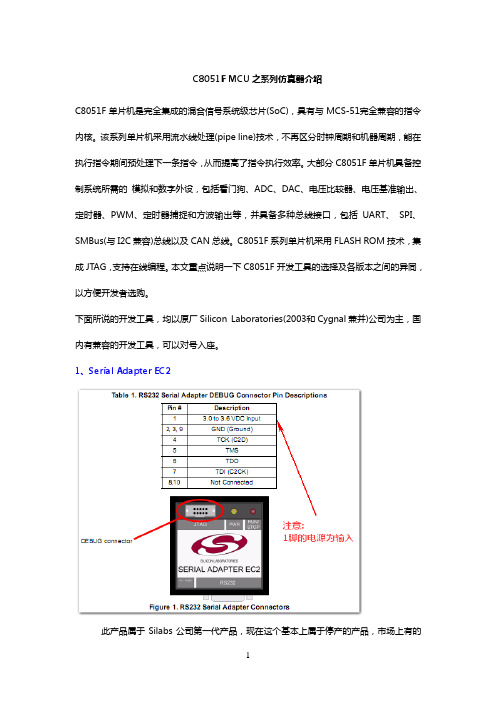

C8051F MCU之系列仿真器介绍

C8051F MCU之系列仿真器介绍C8051F单片机是完全集成的混合信号系统级芯片(SoC),具有与MCS-51完全兼容的指令内核。

该系列单片机采用流水线处理(pipe line)技术,不再区分时钟周期和机器周期,能在执行指令期间预处理下一条指令,从而提高了指令执行效率。

大部分C8051F单片机具备控制系统所需的模拟和数字外设,包括看门狗、ADC、DAC、电压比较器、电压基准输出、定时器、PWM、定时器捕捉和方波输出等,并具备多种总线接口,包括UART、SPI、SMBus(与I2C兼容)总线以及CAN总线。

C8051F系列单片机采用FLASH ROM技术,集成JTAG,支持在线编程。

本文重点说明一下C8051F开发工具的选择及各版本之间的异同,以方便开发者选购。

下面所说的开发工具,均以原厂Silicon Laboratories(2003和Cygnal兼并)公司为主,国内有兼容的开发工具,可以对号入座。

1、Serial Adapter EC2此产品属于Silabs公司第一代产品,现在这个基本上属于停产的产品,市场上有的话,价格也相对偏高。

不合适!还有一个值得提醒大家的是(也是好多朋友问本空间的开发器为什么1脚为NC,特做此声明),注意这个DEBUG的调试接口的关系,在第一脚3.0 to 3.6 VDC Input,搞过RS232接口的朋友都应该知道,串行口不能向设备提供大电流电源的(通常的窃电电路也只是小电流方式),所以在官方的开发板上都有如下有这个关系。

其实在这个脚上(1脚的+3VD)的电源不是向目标板提供的,而官方的开发板这种设计完全是为了兼容所有工具(原装EC2的供电问题)的开发,而不是一般朋友认为的这个脚是仿真器向目标板供电的。

注意这个脚的方向是目标板向仿真器输入,而不是输出!!!2、USB Debug Adapter for C8051F MCU这个开发工具是一个纯USB的开发工具,在PC上这个是免驱动的HID设备,所以很方便地应用在Windwos系统中,在产品内部带有TVS和过流保护,另外由于C8051F 个别单片机有VIO单独控制IO口的电源(如C8051F410的IO可以最大5.25V的输入),所以在这个产品中有一个根据目标板电压,自动调整电平级别来适应C8051F全系列,全电压范围单片机的开发测试工作。

C8051F单片机入门学习流程

C8051F单片机入门学习流程一. 准备硬件及软件1.C8051F任意一款开发板(以C8051F330ST为例)。

2.EC3仿真器。

3.Keil C51开发软件到下载二. 开发者具备基本知识1.对MCS51架构单片机有基本了解。

2.有基本C语言及汇编语言编程经验。

3.对单片机开发过程有基本了解。

三. 学习过程如下1.安装Keil C51软件。

(1)找到Keil uv3 (版本 V8.02)软件目录,并点击C51v802.exe安装(2)点击Next(3)选I agree…, 点击Next(4)默认目录(千万不要选择其它目录),点击Next(5)填写用户名等,点击Next(6)开始安装,等待….(7)安装完成,点击Finish(8)打开Keil C软件,选择File/License Management…(9)显示如下:(10)打开Keil_lic_v2.exe,并按如下设置,点击Generate(11)拷贝LIC0内的序列号:(12)粘贴序列号到Keil C软件的New License ID Code下,(13)点击Add LIC,添加序列号成功。

如果添加失败,请重启电脑并进入安全模式,重新安装序列号。

Keil C 软件安装完毕2.安装C8051F单片机针对Keil C51驱动程序。

(1)找到Keil C51驱动程序软件目录,并点击SiC8051F_uv3_v2.31.exe安装(如果前面安装的是Keil uv2, V7.02或V7.50,请点击SiC8051F_uv2_v2.31.exe安装驱动)(2)点击Next(3)点击Next(4)点击Next(5)选择I accept…, 点击Next(6)点击Next(7)点击Next(不要更改目录)(8)开始安装(9)点击Finish安装完成!3. EC3仿真器、开发板连接及开发软件Keil C软件配置(1)将EC3仿真器与开发板连接好,按1.2.3.4步连接(2) 将EC3仿真器与电脑连接好, 仿真器指示灯亮(3) 上述连接确认无误,将开发板电源线(USB接口)与电脑连接好,再连接到开发板上(4)打开Keil Vision3软件,新建一工程ML-Test(或者将学习板光盘上的测试程序拷贝到电脑硬盘上,用Keil Vision3打开,注意将文件属性更改为可读写):(5)选择C8051F330作为CPU:(6)选择配置如下图:(7)显示如下图:(8)选择Debug项,配置如下图:(9)选择Settings项,配置如下图:(10)点击确定,完成设置;(11)编译并下载程序即可调试了;4. 用Keil C51打开软件例程,编译下载程序并运行。

C8051F系列单片机资料

TCK TMS TDI TDO AV+AV+VDD VDD VDD DGND DGND DGND AGND AGND /RSTXTAL1XTAL2P2.0P2.7P1.0/AIN1.0P1.7/AIN1.7P0.0P0.7DAC1AIN0.0AIN0.1AIN0.2AIN0.3AIN0.4AIN0.5AIN0.6AIN0.7DAC0CP0+CP0-CP1+CP1-VREF P3.0P3.7MONENVREF1VREFD VREF0P7.0/D0P7.7/D7P5.0/A0P5.7/A7P6.0/A8P6.7/A15P4.5/ALE P4.6/RD P4.7/WR P4.0P4.4ANALOG PERIPHERALS-12-bit ADC±1LSB INL; No Missing CodesProgrammable Throughput up to 100kspsEight External Inputs; Programmable as Single-Ended orDifferentialProgrammable Amplifier Gain: 16, 8, 4, 2, 1, 0.5 Data Dependent Windowed Interrupt Generator Built-in Temperature Sensor (± 3°C) -8-bit ADC±1LSB INL; No Missing CodesProgrammable Throughput up to 500ksps Eight External InputsProgrammable Amplifier Gain: 4, 2, 1, 0.5 - Two 12-bit DACsCan Synchronize Outputs to Timers for Jitter-Free WaveformGeneration - Two Comparators- Internal Voltage Reference- VDD Monitor/Brown-out DetectorON-CHIP JTAG DEBUG & BOUNDRY SCAN- On-Chip Debug Circuitry Facilitates Full Speed, Non-Intrusive In-System Debug (No Emulator Required!)- Provides Breakpoints, Single Stepping, Watchpoints, Stack Monitor - Inspect/Modify Memory and Registers- Superior Performance to Emulation Systems Using ICE-Chips, Target Pods, and Sockets- IEEE1149.1 Compliant Boundary Scan -Low Cost, Complete Development KitHIGH SPEED 8051 µC CORE- Pipelined Instruction Architecture; Executes 70% of Instructions in 1 or 2 System Clocks- Up to 100MIPS Throughput with 100MHz System Clock - Expanded Interrupt HandlerMEMORY- 8448 Bytes Internal Data RAM (256 + 8k)- 128k Bytes FLASH; In-System Programmable in 512-Byte Sectors - External Parallel Data Memory InterfaceDIGITAL PERIPHERALS- 64 Port I/O (All are 5V Tolerant with High Sink Current)- Hardware SMBus TM (I2C TM Compatible), SPI TM , and Two UART Serial Ports Available Concurrently- Programmable 16-bit Counter/Timer Array with Six Capture/Compare Modules- Five General Purpose 16-bit Counter/Timers- Dedicated Watch-Dog Timer; Bi-directional Reset - Real-Time Clock Mode using Timer 3 or PCACLOCK SOURCES- Internal Oscillator: 24.5Mhz, 2% Accuracy Supports UART Operation - On-Chip Programmable PLL: up to 100MHz - External Oscillator: Crystal, RC, C, or Clock SUPPLY VOLTAGE .........................2.7V to 3.6V - Typical Operating Current: 50mA @ 100MHz -Typical Stop Mode Current: <0.1uA100-Pin TQFPTemperature Range: –40°C to +85°C4.12.2002SELECTED ELECTRICAL SPECIFICATIONS TA = -40°C to +85°C unless otherwise specified.PARAMETER CONDITIONS MIN TYP MAX UNITSGLOBAL CHARACTERISTICS Supply Voltage 2.7 3.6 V Supply Current (CPU active) Clock=100MHz Clock=1MHz Clock=32kHz 50 1 25 mAmA µASupply Current (shutdown) Oscillator off; VDD Monitor Enabled Oscillator off; VDD Monitor Disabled 10 <0.1 µAµAClock Frequency Range DC 100 MHz INTERNAL CLOCKS Oscillator Frequency 24.0 24.5 25.0 MHz PLL Frequency 96 98 100 MHz A/D CONVERTERResolution 12 bits Integral Nonlinearity ± 1 LSB Differential Nonlinearity Guaranteed Monotonic ± 1 LSB Signal-to-Noise Plus Distortion 66 69 dB Throughput Rate 100 kspsD/A CONVERTERSResolution 12 bits Differential Nonlinearity Guaranteed Monotonic ± 1 LSB Output Settling Time 10 µS COMPARATORS Supply Current (each Comparator) 1.5 µA Response Time (CP+) – (CP-) = 100mV 4.0 µSC8051F120DK DEVELOPMENT KITSMBus is a trademark of Intel Corp.; I2C is a trademark of Philips Semiconductors, Inc.; SPI is a trademark of Motorola, Inc.。

C8051F单片机常见问题及解决方案

答:正确步骤:

1、允许外部振荡器;

2、等待1ms;

3、查询XTLVLD '0'->'1'

4、切换到外部振荡器。

注意:振荡器频率的选择,即OSCXCN寄存器的配置(外部振荡器频率控制位的设置)。关于更多的信息以及源代码可以参看应用笔记AN002《配置内部和外部振荡器》。应用笔记可以从我公司网站下载:

答:推荐在VREF引脚接一个0.1μF的陶瓷电容器与一个大的电容(典型为4.7μF钽电容)。在VREF引脚加电容是为了降低VREF的噪声。因为VREF的噪声越小,ADC或DAC转换结果的噪声也就越小。且这两个电容在PCB板上应尽可能离VREF引脚近。

问:内部参考电平是否可以用于外部电路的参考?

答:可以,你可以用VREF信号作为输出驱动其它电路(像放大器的偏置电压等)。注意,VREF引脚只能提供源电流,也就是说,要有负载接地使电流流出C8051器件。例如,如果你将VREF连到OP运放的(+)节点,你要加一个下拉电阻对地(24K左右)将电流限制在100μA。

2、换别的通道转换看是否正常。

问:ADC的单端输入与差分输入的区别?

答答:在单端方式工作时;ADC转换的是单输入引脚对地的电压值;在增益为1时,测量的值就是输入的电压值;范围是0V到VREF;当增益增加时,输入的范围要相应的减小;

在差分方式工作时;ADC转换的是AIN+与AIN-两个引脚的差值;在增益为1时,测量的值等于(AIN+)-(AIN-),范围是-VREF到+VREF;当增益增加时,输入的范围要相应的减小。

第三、制板时,大面积覆铜。

第四、未使用到的模拟引脚要接地。

c8051f单片机原理及应用

c8051f单片机原理及应用C8051F单片机是由Silicon Laboratories公司推出的一款高性能、低功耗、集成度高的8位单片机系列,它采用了高速8051内核,具有快速的执行速度和高效的计算能力,适用于各种应用领域。

本文将详细介绍C8051F单片机的原理和应用。

一、C8051F单片机原理1.8051内核C8051F单片机采用了高速的8051内核,它包含了一个中央处理器(CPU)、存储器、输入/输出端口、定时器/计数器、串行接口等模块。

8051内核具有简单易学、易于控制和可靠性高等特点,被广泛应用于各种嵌入式系统中。

2.存储器C8051F单片机的存储器包括闪存、RAM和EEPROM。

其中,闪存用于存储程序代码,RAM用于存储数据,EEPROM用于存储非易失性数据。

C8051F单片机的存储器容量从4KB到128KB不等,可以满足不同应用的需求。

3.输入/输出端口C8051F单片机的输入/输出端口包括数字输入/输出端口和模拟输入/输出端口。

数字输入/输出端口用于连接数字设备,模拟输入/输出端口用于连接模拟设备。

C8051F单片机的输入/输出端口可以通过软件配置,实现各种功能。

4.定时器/计数器C8051F单片机的定时器/计数器包括多个独立的定时器和计数器,它们可以通过软件配置,实现各种计时和计数功能。

5.串行接口C8051F单片机的串行接口包括SPI接口、I2C接口和UART接口。

它们可以用于与外部设备进行通信,实现数据交换和控制。

二、C8051F单片机应用C8051F单片机广泛应用于各种嵌入式系统中,例如:工业控制、智能家居、医疗设备、电子仪器等。

1.工业控制C8051F单片机可以用于各种工业控制系统中,如温度控制、湿度控制、压力控制等。

它具有高速的运算能力和丰富的输入/输出端口,可以实现复杂的控制算法和实时控制。

2.智能家居C8051F单片机可以用于智能家居系统中,如智能灯光控制、智能窗帘控制、智能门锁控制等。

多功能单片机C8051F

智能检测与仪器研究所

C8051F系列单片机的特点 C8051F系列单片机的特点

1、指令运行速度高 、

由于C8051Fxxx单片机采用流水线结构,废除了机器周 单片机采用流水线结构,废除了机器周 由于 单片机采用流水线结构 的概念,指令以时钟周期为运行单位 由标准的12个系统 以时钟周期为运行单位, 期的概念,指令以时钟周期为运行单位,由标准的 个系统 个系统时钟周期,处理能力大大提高。 时钟周期降为 1 个系统时钟周期,处理能力大大提高。在相 同时钟下,指令运行速度比一般的80C51系列单片机提高大 同时钟下,指令运行速度比一般的 系列单片机提高大 个系统时钟周期, 约10倍。70%指令的执行时间为 1 个或 2 个系统时钟周期, 倍 % 只有4条指令的执行时间大于 个系统时钟周期。 条指令的执行时间大于4个系统时钟周期 只有 条指令的执行时间大于 个系统时钟周期。

智能检测与仪器研究所

C8051F系统单片机的组成 C8051F系统单片机的组成

4、模数和数模转换 、

大部分的C8051Fxxx单片机内部都有A/D转换模块,不 单片机内部都有 转换模块, 大部分的 单片机内部都 转换模块 同型号中的A/D转换位数、转换速度和输入通道数不完全相 转换位数、 同型号中的 转换位数 同。 部分的C8051Fxxx单片机内部有两个12位数模转换器, 单片机内部有两个 位数模转换器 部分的 单片机内部有两个 位数模转换器, MCA可将任何一个 可将任何一个DAC置于低功耗关断方式。 置于低功耗关断方式。 可将任何一个 置于低功耗关断方式

智能检测与仪器研究所

3、CIP-51内核的基本部件 、 内核的基本部件 1)中央处理器(CPU) )中央处理器( )

C8051F系列的 系列的CPU是单片机最核心的部分,主要 是单片机最核心的部分, 系列的 是单片机最核心的部分 完成运算和控制功能,只是它的控制功能比通用处理器 完成运算和控制功能, 更强。 位中央处理单元。 更强。CPU是8位中央处理单元。 是 位中央处理单元

C8051F系列单片机的初始化共5页文档

C8051F系列单片机的初始化Silicon Labs公司出品的C8051F系列单片机是高集成度的混合信号系统级(SoC)芯片,它具有基于增强的CIP-51内核,其指令集与MCS-51完全兼容,采用流水线结构,70%的指令执行时间为1到2个系统时钟周期,是标准8051指令执行速度的12倍,具有大量的中断源(可达22个),集成了丰富的资源和外部设备接口,能够满足绝大部分场合的复杂功能要求,在嵌入式领域的各个场合都得到了广泛的应用。

1、初始化的基本流程C8051F系列单片机系统时钟源多样且控制灵活,采用交叉开关配置方式实现了I/O端口的灵活配置,内部特殊功能寄存器SFR种类数量多且采用分页管理方式,因为这些特点C8051F系列单片机的初始化工作不同于标准8051单片机,其初始化工作流程基本如下:看门狗初始化配置→交叉开关初始化配置→I/O端口初始化配置→系统时钟初始化配置→功能模块初始化配置。

2、初始化的要点2.1 特殊功能寄存器(SFR)C8051F系列单片机具有标准8051中的全部SFR,还增加了一些用于配置和访问专有子系统的SFR,SFR采用分页机制,允许器件将很多SFR映射到0x80-0xFF存储器地址空间,最多可达256页。

在使用相应的特殊功能寄存器时,需先利用页选择寄存器(SFRPAGE)转换到相应的SFR页,再对其进行操作。

当中断发生时,SFR页寄存器会自动切换到引起中断的标志位所在页,这减轻了从中断服务程序切换SFR页的负担,在执行RETI指令时,中断前使用的SFR页会被自动恢复。

SFR结构如图1所示:2.2 可编程数字I/O和交叉开关C8051F系列单片机使用优先权交叉开关译码器实现了I/O端口的灵活配置,允许将内部系统资源映射到P0-P3的端口,用户根据自己的特定应用选择通用端口I/O和所需资源的组合。

优先权交叉开关译码器是通过交叉开关配置寄存器XBR0、XBR1、XBR2 和XBR3(复位后均为0)来进行配置的,当外设对应使能位被置为1时,外设可以通过端口进行访问,反之则不能。

c8051f单片机使用小结

1. c8051f单片机速度快,时钟频率可达到25,50甚至100Mhz!2. 电源用计算机的USB接口5伏电源,然后串接3个1N4007或1N4148二极管可以得到3伏左右的电压!!!如果要使用片内ad功能,电源电压需要更好些,可以使用三极管、稳压管等构成串联稳压电路,效果还是很好的!!!3. 串口通信转换芯片可以不用max3232或max232,只需要2个三极管和4个电阻就可以了!8.c8051f单片机和at89c5x,at89s5x单片机的不同之处。

第一,c8051f单片机没有采用时钟12分频,因此运行速度快了一个数量级;第二,c8051f单片机采用低电平复位,而at89x5x采用高电平复位;第三,c8051f单片机内部带有晶振,其中不少的精度高,可以和外部的晶振切换工作;第四,c8051f单片机的看门狗上电复位后已打开(所以通常要关掉),而at89s5x单片机的看门狗上电复位后关闭;第五,c8051f单片机的flash至少可以擦除编程20000次,而且可以当e2prom数据寄存器使用,而at89x5x单片机的flash最多擦除编程1000次;第六,at89x5x采用5伏供电,c8051f单片机虽然采用3伏供电,但i/o口可以承受5伏电压;第七,at89s5x单片机的一个i/o口最多有两种功能,而c8051f单片机的i/o口可以达到3种以上的功能,这是通过内部的交叉开关实现的;最后要说的是开发工具不一样。

与8051相比,在相同时钟下单周期指令运行速度为原来的12倍.2,I/O从固定方式到交叉开关配置迄今为止,I/O端口大都是固定为某个特殊功能的输入/输出口,可以是单功能或多功能,I/O端口可编程选择为单向/双向以及上拉、开漏等。

固定方式的I/O端口,既占用引脚多,配置又不够灵活。

在C8051F中,则采用开关网络以硬件方式实现I/O端口的灵活配置,在这种通过交叉开关配置的I/O端口系统中,单片机外部为通用I/O口,如P0口、P1口和P2口。

C8051F单片机

13

2、IO口

推挽输出方式

1 0 1 0 1 0 1 DGND VDD

0

1

14

2、IO口

漏极开路输出

0 0 1 0 1 DGND

0

1

高阻

15

2、IO口

数字输入

0 1 1 1

0

16

3、优先权交叉开关配置

1. C8051F单片机有大量的数字资源需要通过4个 低端I/O端口P0、P1、P2和P3才能使用。 2. P0、P1、P2和P3中的每个引脚既可定义为通用 的端口I/O(GPIO)引脚,又可以分配给一个 数字外设或功能(例如:UART0 或/INT1)。 3. 资源分配的灵活性是通过使用优先权交叉开关 译码器实现的。

执行周期数 1 2 2/3 3 3/4 4 4/5 5 8

指令数

26

50

5

16

7

3

1

2

1

8

1、概述 微控制器内核峰值执行速度比较

9

1、概述

3、增加的功能 C8051F31x 系列MCU 在CIP-51 内核和外设方面 有几项关键性的改进,提高了整体性能,更易于在最 终应用中使用。 1)扩展的中断系统 提供14 个中断源(标准8051 只有5个中断源), 允许大量的模拟和数字外设中断微控制器。 一个中断驱动的系统需要较少的MCU 干预,因而 有更高的执行效率。 在设计一个多任务实时系统时,这些增加的中断源 是非常有用的。

22

4、系统时钟源

当外部晶体振荡器稳定运行时,晶体振荡器有效标志 OSCXCN 寄存器中的XTLVLD被硬件置‘1’。 XTLVLD 检测电路要求在使能振荡器工作和检测XTLVLD之 间至少有1 ms的启动时间。 如果需要使用晶体或陶瓷谐振器作为MCU 的外部振荡器源 建议的过程为 1) 通过向端口寄存器的对应位写0 使XTAL1 和XTAL2 引脚 为低电平。 2) 将XTAL1 和XTAL2 配置为模拟输入。 3)使能外部振荡器 4)等待至少1ms 5)查询XTLVLD => ’1’ 6)将系统时钟切换到外部振荡器 23

C8051F单片机原理及应用课程设计

C8051F单片机原理及应用课程设计

一、设计背景及意义

C8051F单片机具有结构简单、易于编程、使用灵活等特点,在嵌入

式行业越来越受到重视。

设计这门课程的主要目的是向学生介绍

C8051F单片机的基本结构、编程技巧和应用场景,培养学生的嵌入式

系统管理和开发能力,从而满足市场对嵌入式人才的需求。

二、教学内容与目标

1. 教学内容

•C8051F单片机的硬件介绍:内部结构、各部件功能、寄存器、引脚说明等;

•C8051F单片机的编程技巧:汇编语言、C语言、应用程序设计;

•C8051F单片机的应用场景:实时控制、AD转换、PWM控制、串口通信等。

2. 教学目标

•了解C8051F单片机的内部结构和工作原理;

•掌握C8051F单片机的编程技巧;

•能够运用C8051F单片机进行嵌入式系统开发。

1。

C8051F学习笔记1:C8051F最小系统

C8051F学习笔记1:C8051F最小系统C8051F是Silicon Laboratories公司推出的增强型51单片机,当然功能很强大,我觉得最吸引人的要算峰值能指令运行达到25MIPS(Million Instruction s Per Second(每秒百万条指令)),即与8051相比,在相同时钟下单周期指令运行速度为原来的12倍;整个指令集平均运行速度为原来8051的9.5倍,使8051兼容机系列进入了8位高速单片机行列。

哈哈,下面开始一步步教你制作C8051F的最小系统:要进行C8051F开发无非要有这些东西:下载线+最小系统开发板+编译软件。

下载线:这个可以自己制作,网上也有这方面的电路图,为了省事,我是在淘宝上买的,卖家东西很好,是自己开发的USB口下载线,同时也是一个仿真器(C8051 F USB口的JTAG/C2下载线U-EC5仿真器)/microgo/blog/item/7ecfc86377bcb4dbe7113afa.html卖家还把教程、软件、例程和在官网下的应用笔记刻成光盘,这样就省去了我学习C8051F的很多时间C8051F最小系统我没有买开发板,是在万用板上焊接的。

C8051F有很多型号,有些还有1 00多个管脚,这很费事,所以我选用C8051F320,管脚少,LQFP32封装,只有32个管脚,管脚间距也大,1.27mm。

在中发买那种有贴片焊盘的万用板。

C8051F选型/xxzn/xxzn.aspC8051F开发板参考电路图/pcb/1.htmC8051F最小系统构成3.3V电源+低电平复位+JTAG/C2+(晶振)电源部分电源采用AMS1117-3.3V,AMS1117的好处是电压压降低,大于1.7V,所以输入用5V电源的话,也可以稳压到3.3V。

当然C8051F在2.7V~3.6V之间都能正常工作。

如果没有1117的话,也可以采用可调的稳压芯片LM317,不过对于LM337,在接入电路前最好把输出电压调节到3.3V左右。

第十部分C8051F系列SOC单片机教学课件

兆指令/秒,有的型号最高执行速度可达100 兆指令/秒; 4) 增加了流水线结构,70%指令的执行时间为 1~2个系统时钟周期;

5) 与模/数、数字外设有关的SFR移到核外,通 过SFR接口与CPU交换信息;

C8051F单片机大部分系列都有位于片上的核 外数据存储器空间RAM(XRAM),除此还可向 外扩展64KB RAM。存储器接口就是用于控制和 管理片上和片外的数据存储器,需要用MOVX访 问。

5)流水线结构 在CIP-51中采用流水线结构,使多条指令并

行执行,大大提高了单片机的执行速度。

6)中断系统 C8051F系列单片机的中断系统可以满足一般

1、指令运行速度高

由于C8051Fxxx单片机采用流水线结构,废 除了机器周期的概念,指令以时钟周期为运行 单位,由标准的12个系统时钟周期降为 1 个 系统时钟周期,处理能力大大提高。在相同时 钟下,指令运行速度比一般的80C51系列单片 机提高大约10倍。70%指令的执行时间为 1 个或 2 个系统时钟周期,只有4条指令的执行 时间大于4个系统时钟周期。

10.1 C8051F系列单片机简介

10.1.1 C8051F系列单片机的诞生

美国 Silabs 公司推出的C8051F系列单片机, 把 C8051F 系列单片机从微控制器(MCU)时代推 向片上系统( SOC )时代,使其以8051为内核的 单片机上了一个新的台阶。

SOC即 System On Chip 的缩写,即把计算机常 用的一些数字模拟设备全部都做在一块芯片上, 使之成为一个完整的模拟数据采集与控制系统。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

30

5、系统复位

5)看门狗定时器复位 可编程计数器阵列(PCA)的可编程看门狗定时 器(WDT)功能可用于在系统出现错误的情况下防止 软件运行失控。 如果因系统出错使用户软件不能更新WDT,则 WDT 将产生一次复位,WDTRSF 位(RSTSRC.5)被 置‘1’。/RST 引脚的状态不受该复位的影响。 可以通过软件使能或禁止PCA 的WDT 功能。

27

5、系统复位

2)掉电复位和VDD 监视器 当发生掉电或因电源波动导致VDD降到VRST以下 时,电源监视器将/RST引脚驱动为低电 平并使CIP-51 保持复位状态。 当VDD又回到高于VRST的电平时,CIP-51 将退出 复位状态。

在选择VDD 监视器作为复位源之前,必须使能VDD 监视器。 VDD 监视器被使能或稳定之前选其为复位源可能导致系统复位 将VDD 监视器配置为复位源的步骤如下: 1.使能VDD 监视器(VDM0CN 中的VDMEN 位 = 1); 2.等待VDD 监视器稳定; 3.选择VDD 监视器作为复位源(RSTSRC 中的PORSF 位 = 1) 28

32

6、JTAG接口的在系统调试

33

6、JTAG接口的在系统调试

C8051F31x器件具有片内Silicon Labs 2线(C2) 接口调试电路,支持使用安装在最终应用系统中的 产品器件进行非侵入式、全速的在系统调试。 Silicon Labs的调试系统支持观察和修改存储器 和寄存器,支持断点和单步执行。不需要额外的目 标RAM、程序存储器、定时器或通信通道。在调试 时所有的模拟和数字外设都正常工作。 当MCU单步执行或遇到断点而停止运行时,所 有的外设(ADC和SMBus除外)都停止运行,以保 持与指令执行同步。

◆16K 字节可在系统编程的FLASH 存储器

◆1280字节的片内RAM ◆可寻址64K字节地址空间的外部数据存储器接口

◆硬件实现的SPI、SMBus/ I2C 和两个UART 串行接口

◆4个通用的16位定时器 ◆具有5个捕捉/比较模块的可编程计数器/定时器阵列

◆片内看门狗定时器、VDD 监视器和温度传感器

13

1、概述

4、可编程数字I/O •C8051F310有29个I/O引脚(3个8位口和一个5位口) •C8051F31x端口的工作情况与标准8051相似,但有一些 改进。每个端口引脚都可以被配置为模拟输入或数字I/O 。 •被选择作为数字I/O的引脚还可以被配置为推挽或漏极 开路输出。 •在标准8051中固定的“弱上拉”可以被总体禁止,为低 功耗应用提供了进一步节电的能力。

4

1、概述

C8051F芯片示意图

5

1、概述

高速微控制器 内核

数字 IO

C8051F原理框图

模拟外设

6

1、概述

CIP-51系统控制器的指令集与标准MCS-51TM 指令集

完全兼容,可以使用标准8051的开发工具开发CIP-51

的软件。

所有的CIP-51指令共111条,在二进制码和功能上与 MCS-51 TM 产品完全等价,包括操作码、寻址方式和对 PSW标志的影响,但是指令时序与标准8051不同。 由于CIP-51采用了流水线结构,大多数指令执行所需

执行周期数 1 2 2/3 3 3/4 4 4/5 5 8

指令数

26

50

5

16

7

3

1

2

1

9

1、概述 微控制器内核峰值执行速度比较

10

1、概述

3、增加的功能 C8051F31x 系列MCU 在CIP-51 内核和外设方面 有几项关键性的改进,提高了整体性能,更易于在最 终应用中使用。 1)扩展的中断系统 提供14 个中断源(标准8051 只有5个中断源), 允许大量的模拟和数字外设中断微控制器。 一个中断驱动的系统需要较少的MCU 干预,因而 有更高的执行效率。 在设计一个多任务实时系统时,这些增加的中断源 是非常有用的。

31

5、系统复位

看门狗watchdog timer,是一个定时器电路。 一般 有一个输入,叫喂狗,一个输出到MCU的RST端。 MCU正常工作的时候,每隔一端时间输出一个信 号到喂狗端,给WDT 清零。如果超过规定的时间不喂 狗(一般在程序跑飞时),WDT 定时超过,就给出一个 复位信号到MCU,使得MCU复位,防止MCU死机 看门狗的作用就是防止程序发生死循环,或者说 程序跑飞。 工作原理:系统运行以后也就启动了看门狗的计 数器,看门狗就开始自动计数,如果到了一定的时间 还不去清看门狗,那么看门狗计数器就会溢出从而引 起看门狗中断,造成系统复位。

14

2、IO口

推挽输出方式

1 0 1 0 1 0 1 DGND VDD

0

1

15

2、IO口

漏极开路输出

0 0 1 0 1 DGND

0

1

高阻

16

2、IO口

数字输入

0 1 1 1

0

17

3、优先权交叉开关配置

1. C8051F单片机有大量的数字资源需要通过4个 低端I/O端口P0、P1、P2和P3才能使用。 2. P0、P1、P2和P3中的每个引脚既可定义为通用 的端口I/O(GPIO)引脚,又可以分配给一个 数字外设或功能(例如:UART0 或/INT1)。 3. 资源分配的灵活性是通过使用优先权交叉开关 译码器实现的。

8

1、概述

2、速度提高 CIP-51 采用流水线结构,与标准的8051 结构相比指令 执行速度有很大的提高。在一个标准的8051 中,除 MUL 和DIV 以外所有指令都需要12 或24 个系统时钟 周期,最大系统时钟频率为12-24MHz。而对于CIP-51 内核,70%的指令的执行时间为1 或2 个系统时钟周期 ,只有4 条指令的执行时间大于4 个系统时钟周期。

5、系统复位

3)外部复位 外部/RST 引脚提供了使用外部电路强制MCU 进 入复位状态的手段。 在/RST 引脚上加一个低电平有效信号将导致 MCU 进入复位状态。 尽管在内部有弱上拉,但最好能提供一个外部上 拉和/或对/RST 引脚去耦以防止强噪声引起复位。

29

5、系统复位

4)时钟丢失检测器复位 时钟丢失检测器(MCD)实际上是由系统时钟 触发的单稳态电路。 如果系统时钟保持在高电平或低电平的时间大 于100 微秒,单稳态电路将超时并产生复位。

19

3、优先权交叉开关配置

数字资源 对外引脚

端口IO 单元

20

3、交叉开关配置——优先权交叉开关译码表

高 UART0 SPI SMBus UART1 PCA

低

21

3、交叉开关配置——优先权交叉开关译码表

端口I/O 初始化

端口I/O 初始化包括以下步骤: 1.用端口输入方式寄存器(PnMDIN)选择所有端口引脚的 输入方式(模拟或数字)。 2.用端口输出方式寄存器(PnMDOUT)选择所有端口引脚 的输出方式(漏极开路或推挽)。 3.用端口跳过寄存器(PnSKIP)选择应被交叉开关跳过的 那些引脚。 4. 将引脚分配给要使用的外设。 5. 使能交叉开关(XBARE =‘1’)。

18

3、优先权交叉开关配置

也称为“交叉开关”,按优先权顺序将端口0 – 3 的 引脚分配给器件上的数字外设(UART、SMBus、 PCA、定时器等)。 端口引脚的分配顺序是从P0.0 开始,可以一直分配 到P3.7。为数字外设分配端口引脚的优先权顺序为 UART0具有最高优先权,而CNVSTR具有最低优先 权。 优先权交叉开关的配置是通过3个特殊功能寄存器 XBR0、XBR1、XBR2来实现的,对应使能位被设置 为逻辑‘1’时,交叉开关将端口引脚分配给外设。

的时钟周期数与指令的字节数一致。

7

1、概述

1、 与8051 完全兼容 •C8051F31x系列器件使用Silicon Labs的专利CIP-51 微控制器内核。 •CIP-51 与MCS-51TM指令集完全兼容,可以使用标 准803x/805x的汇编器和编译器进行软件开发。 •CIP-51 内核具有标准8052 的所有外设部件,包括4 个16 位计数器/定时器、一个具有增强波特率配置的 全双工UART、一个增强型SPI端口、1280 字节内部 RAM、128 字节特殊功能寄存器(SFR)地址空间及 29/25 个I/O端口。

5、系统复位

复位电路将控制器置于一个预定的缺省状态。 1)CIP-51 停止程序执行 2) 特殊功能寄存器(SFR)被初始化为所定义的复位值 3)外部端口引脚被置于一个已知状态 4)中断和定时器被禁止。 5)所有的SFR 都被初始化为预定值 6)I/O 端口锁存器的复位值为0xFF,全部为逻辑‘1’,内部 弱上拉有效,使外部I/O 引脚处于高电平状态。 7) MCU 使用内部振荡器运行在2MHz 作为默认的系统时钟。 8) 看门狗定时器被使能,使用其最长的超时时间。

23

4、系统时钟源

当外部晶体振荡器稳定运行时,晶体振荡器有效标志 OSCXCN 寄存器中的XTLVLD被硬件置‘1’。 XTLVLD 检测电路要求在使能振荡器工作和检测XTLVLD之 间至少有1 ms的启动时间。 如果需要使用晶体或陶瓷谐振器作为MCU 的外部振荡器源 建议的过程为 1) 通过向端口寄存器的对应位写0 使XTAL1 和XTAL2 引脚 为低电平。 2) 将XTAL1 和XTAL2 配置为模拟输入。 3)使能外部振荡器 4)等待至少1ms 5)查询XTLVLD => ’1’ 6)将系统时钟切换到外部振荡器 24

C8051F310单片机介绍

1

1、概述 2、IO口 3、交叉开关配置 4、系统时钟源 5、系统复位 6、JTAG接口的在系统调试 7、单片机的初始化设置

2

1、概述

C8051F系列单片机是集成的混合信号片上系统SOC (System on chip)。