第3章C28xDSP的CPU与指令系统共35页

DSP讲稿——第三章指令系统1

单片机和DSP延时程序的比较

单片机延时程序:

MOV AAA:MOV BBB:DJNZ DJNZ R1,#0FFH R2,#0FFH R2,BBB R1,AAA

DSP延时程序:

RPT #0FFFFH NOP

•参照单片机延时程序可 否用DSP另外的延时程序 完成?

#0FFFFH,AR1 #0FFFFH,AR2 BBB,*AR2AAA,*AR1-

16位立即数——数据存储器地址(0~65535) 16位立即数——程序存储器地址(0~65535) 16位立即数——I/O口地址(0~65535) 源累加器(A或B) 目的累加器(A或B) 16位长立即数

DSP技术与应用 第三章3.2

3.2.1 立即数寻址

DSP技术与应用 第三章3.2

支持立即数寻址的指令

DSP技术与应用 第三章3.1

3.1.1 汇编语言源程序格式

助记符指令一般包含4个部分,其一般组成 形式为: [标号][:] 助记符 [操作数] [;注释] 例如:start: LD #40,AR1 1.标号区 所有汇编指令和大多数汇编伪指令前面都可 以带有标号,标号可以长达32个字符,由 A~Z、a~z、0~9、_和$符号组成,且第 一个字符不能是数字,区分大小写。

DSP技术与应用 第三章3.2

请思考:若将下面两条语句用 一条程序存储器地址寻址指令 代替,应如何修改? LD #2000H,A READA 0060H

DSP技术与应用 第三章3.2

3.2.4 直接寻址

DSP技术与应用 第三章3.2

请思考

有如下指令: LD #0,DP LD @u,A 假定在上面指令中u变量分配的地 址已经超过了7位数,即如果u分配 了10E0h地址,那么实际装载到A 的数据的地址单元是多少?

DSP28335汇编教程

DSP28335汇编教程当硬件执行指令时,寻找指令所指定的参与运算飞操作数的方式——寻址方式。

根据程序的要求采用不同的寻址方式,可以有效地缩短程序的运行时间和提高代码执行效率。

汇编指令是可执行指令,每一条指令对应一条机器码,用来控制处理器仲的执行部分进行各种操作。

在本章节当中将主要以基于C28x的DSP芯片为例,为读者讲解DSP的寻址方式和汇编指令系统,其中大部分内容也可适用于其他Ti公司的DSP产品。

6.1汇编语言指令集概述在学习C28x系列DSP的寻址方式和汇编指令指令之前,先来对一些基础的知识进行讲解一下先,在汇编程序当中开发人员会常常使用到许多的特殊符号和标志,它们都具有特殊的含义,在学习汇编之前读者们必须先理解这些符号和标志含义,在这里会对其中最常用最重要的操作数符号和寄存器经行详细说明。

在进行汇编讲解之前先来了解一下开发的核心——CPU。

在TMS320C2000系列中,CPU 内核为:C20x/C24x/C240x:C2xLP:C27x/C28x:C27x、C28x这些CPU的硬件结构有一定差别,指令集也不相同,但是,在C28x芯片中可以通过选择兼容特性模式,使C28xCPU与C27xCPU及C2xLPCPU具有最佳兼容性。

可通过状寄存器STl的位OBJMODE和位AMODE的组合,选定模式。

C28x芯片具有3种操作模式:1.C28x模式:在该模式中,用户可以使用C28x的所有有效特性、寻址方式和指令系统,因此,一般应使C28x芯片工作于该种模式。

2.C27x目标——兼容模式:在复位时,C28x的CPU处于C27x目标-兼容模式。

在该模式下,目标码与C27xCPU完全兼容,且它的循环—计数也与C27xCPU兼容。

3.C2xLP源——兼容模式:该模式允许用户运行C2xLP的源代码,这些源代码是用C28x代码生成工具编译生成的。

在下面的讲解当中会牵涉到模式的转换,希望读者要搞清楚每一个模式的对应关系。

第3章C28xDSP的CPU与指令系统35页PPT

Fast & flexible interrupt management significantly reduce interrupt latency

28.05.2020

Code compatible with the TMS320C24x™ DSP family

CPU的信号主要包括4种: ① 存储器接口信号 ② 时钟和控制信号 ③ 复位和中断信号 ④ 仿真信号

28.05.2020

山东大学控制学院 张东亮

2

F281x DSP的CPU 单元结构框图

28.05.2020

山东大学控制学院 张东亮

3

C28x的CPU主要由总线、CPU寄存器、程序地址发 生器和控制逻辑、地址寄存器算术单元(ARAU)、算术逻 辑单元(ALU)、乘法器和移位器等逻辑部件组成,还包括 指令队列和指令译码单元、中断处理逻辑等。

28.05.2020

山东大学控制学院 张东亮

4

TMS320F2812 / TMS320F2810

Most Powerful - Most Integrated Dual Function Digital Signal Controller

Code security

128Kw Flash + 2Kw OTP

File

28.05.2020

Peripheral Bus

High-Performance CPU (C28xTM DSP Core)

Event Mgr A Event Mgr B 12-Bit ADC

Watchdog GPIO

150MIPS performance Single cycle 32 x32-bit MAC (or dual 16 x16 MAC) Very Fast Interrupt Response Single cycle read-modified-write F24x/LF240x Source Code Compatible

TMS320C28x系列DSP芯片结构及引脚功能

第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x 系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

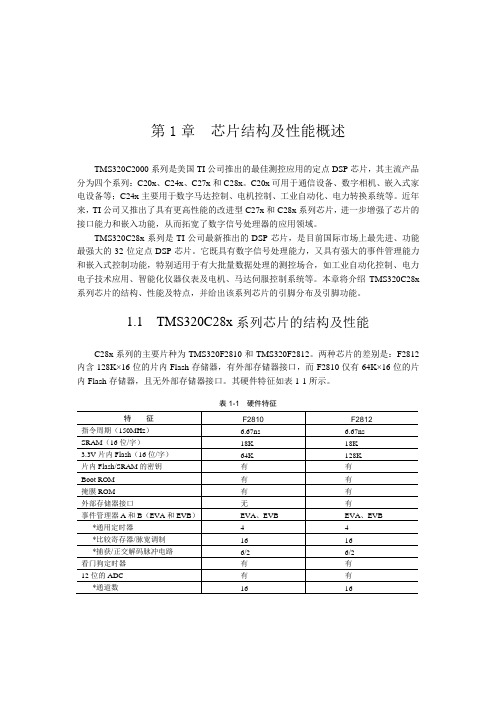

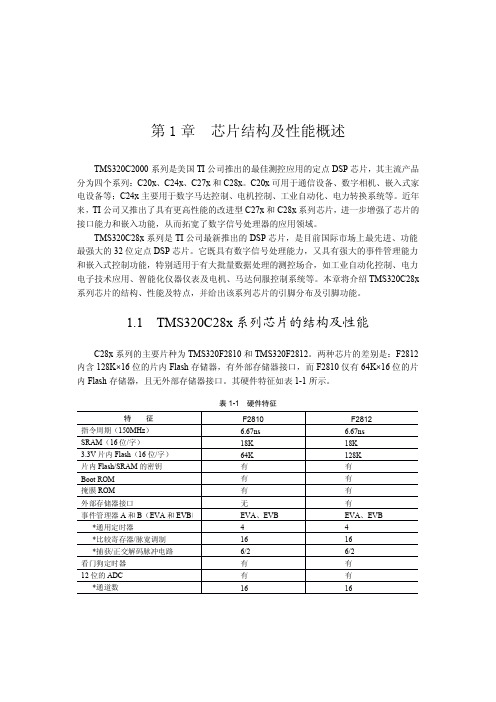

1.1 TMS320C28x系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征TMS320C28x系列DSP的CPU与外设(上)·2·注:‡“S”是温度选择(-40℃~ +125℃)的特征化数据,仅对TMS是适用的。

‡‡产品预览(PP):在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI):在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包括对所有参数的测试。

TMS320F2812中文手册

TMS320F2812中文手册第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x 系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征特征 F2810 F2812 指令周期(150MHz) 6.67ns 6.67ns SRAM(16位/字)18K 18K 3.3V片内Flash(16位/字) 64K 128K 片内Flash/SRAM的密钥有有有有 Boot ROM掩膜ROM 有有外部存储器接口无有事件管理器A和B(EVA和EVB)EVA、EVB EVA、EVB*通用定时器 4 4*比较寄存器/脉宽调制 16 16*捕获/正交解码脉冲电路 6/2 6/2 看门狗定时器有有 12位的ADC 有有*通道数 16 16TMS320C28x系列DSP的CPU与外设(上) ?2?续表特征 F2810 F2812 32位的CPU定时器 3 3 串行外围接口有有串行通信接口(SCI)A和B SCIA、SCIB SCIA、SCIB 控制器局域网络有有多通道缓冲串行接口有有数字输入/输出引脚(共享)有有外部中断源 3 3 核心电压1.8V 核心电压1.8V 供电电压 I/O电压3.3V I/O电压3.3V 封装128针PBK 179针GHH,176针PGF 温度选择‡ A:-40? ~ +85? PGF和GHH PBK S:-40? ~ +125? 仅适用于TMS 仅适用于TMS 产品状况‡‡产品预览(PP) AI AI 高级信息(AI)(TMP)‡‡‡ (TMP)‡‡‡ 产品数据(PD)注:‡ “S”是温度选择(-40? ~ +125?)的特征化数据,仅对TMS是适用的。

TMS320C28x DSP 的系统控制和中断

表 1 P I L模 式及 工作 时钟

表 1给出 了不 同 P 模 式下 的 CP 工作 时钟 S C OUT。 中 , C N是 外 接 晶体或 外部 时 钟 I I U YS I K 其 X I KI 源 的 固有 频率 , 时钟 信号 通 过 P 模 块 可 以产生 数 倍 于 X I N 的 C U 工 作 时钟 S C OUT。在 该 I I C KI P YS I K P 使 能 模式 下 , I I 配置 P 控制 寄 存器 P C 的低 4位 值 , I I I R I 即可 得到 倍频 系数 D V 值 , 时的 C U 工 作 I 此 P

( . o t r d aeTe m CE,PL 1 P sg a u t a 1I AUS T,Na j g 2 0 0 n i 1 0 7,Chn ; n ia

2 D e arm en e toni nf r a i gi e rng I . p t tofEl c r c I o m ton En n e i CE ,PLA U ST )

摘 要 : I T 公司新近推 出的 T 3 0 2 x系列 3 MS 2C 8 2位定点 D P芯片具有 丰富的系统资源 。 中介绍 了片内 S 文

各 部 分 配 置 及 其 特 点 : 钟 控 制 灵 活 , 供 了多 种 低 功 耗 模 式 以供 选 择 ; 达 5 时 提 多 6个 通 用 I O 引 脚 均 可 复 用 , 能 丰 / 功

路 以节省 功耗 。

1 3 低 功 耗 模 式 .

除 了可 以通 过关 闭不需 要 的外 设 时钟 以降 低芯 片功 耗外 , 8 C2 x芯 片还 提供 了低 功耗 模 式 以进 一 步 降 低 系 统 工 作 时 的功 耗 。C 8 2 x系列 D P的低 功 耗 模 式 与 2 0 S 4 x系 列 DS P相 类 似 。设 定 低 功 耗 控 制 寄 存 器 L MC P R0的低两 位 ( P 值 ) 执行 I I M 后 DI E指令 , 即可进 入 到 I M 值 所指 定 的低功 耗 模 式下 。表 2列 出 了 P

DSP常用汇编语言指令简介

5. 控制指令举例

Example1:BIT0h,15 ;(DP = 6)把内存地址=300h 单元内容的最低位(BIT0)送给TC。 Example2:LDP #0h;使用立即数方式装载 数据页,也可以采用直接寻址和间接寻址方式装 载。 Example3:PUSH ;把累加器的低16位压入堆 栈。 Example4:SETC C;置进位C=1,也可以设置 以下的控制位为1或者为0,例如:CNF、INTM、 OVM、SXM、TC和XF。类似的指令还有: CLRC。

2. 工作寄存器等指令举例

Example4:ADRK #80h ;把当前工作寄存器内容 加一个立即数80h(注意立即数范围:00~FFh)。类 似的指令还有SBRK。 Example5:BANZ指令使用举例。例: MAR *, AR0 ;当前ARP=AR0 LAR AR1, #03h ;AR1内容赋值为03h LAR AR0, #60h ;AR0内容赋值为60h ZAC ; 累加器ACC清零 loop: ADD *+, AR1 ;把当前工作寄存器AR0指向 的内存单元数值加到ACC,然后AR0内容加1,当前工 作寄存器指针指向AR1 BANZ loop, *-AR0 ;判断AR0是否为0,否则程序 转到loop,同时AR0的内容减1。 南航自动化学院DSP技术应用实验 返回到第10页 室

南航自动化学院DSP技术应用实验 室

1. 累加器等指令举例

Example 1:ADD 1,1;(假设DP = 6),把 第6个数据页的第一个内存单元内容左移一 位加到累加器 Example 2:LACC *,4; (与SXM有关) Example 3:ROL;把累加器内容循环左移 Example 4:SACL *,0,AR7 ;把当前工作寄 存器指示内容左移0位送入累加器的低8位 Example 5:RPT #15 SUBC * ;累加器减去当前寄存 器指的内容,连续减16次,结果存累加器

TMS320C28x系列芯片的结构及性能

—

I

PU 的操作完成且没有即将对 XINTF 进行访

问时,XINTF 释放总线。此信号是异步输

入并与 XTIMCLK 同步

XHOLDA

外部 DMA 保持确认信号。当 XINTF 响应 XHOLD 的请求时 XHOLDA 呈低电平,所

K10

82

有的 XINTF 总线 和 选 通 端 呈 高 阻 态 。

特征 指令周期(150MHz) SRAM(16 位/字) 3.3V 片内 Flash(16 位/字) 片内 Flash/SRAM 的密钥

Boot ROM 掩膜 ROM 外部存储器接口 事件管理器 A 和 B(EVA 和 EVB)

*通用定时器 *比较寄存器/脉宽调制 *捕获/正交解码脉冲电路 看门狗定时器 12 位的 ADC *通道数

·6·

TMS320C28x系列DSP的CPU与外设(上)

封装和 176 引脚 PGF 低剖面四芯线扁平 LQFP(Low-profile Quad)封装,其引脚分布分别 如图 1-2(BGA 封装底视图)和图 1-3(LQFP 封装顶视图)所示。TMS320F2810 芯片的封 装方式为 128 引脚 PBK LQFP 封装,其引脚分布情况如图 1-4(顶视图)所示。

DSP芯片应用系列讲座_二_第3讲TMS320C28x的指令系统与寻址方式

D SP 芯片应用系列讲座(二)第3讲 TM S 320C 28x 的指令系统与寻址方式Ξ郭国良1,闫佩君2,张雄伟3(1.解放军理工大学通信工程学院研究生1队,江苏南京210007;2.解放军理工大学通信工程学院研究生5队;3.解放军理工大学通信工程学院电子信息工程系)摘 要:文中分类介绍了T I 公司新近推出的TM S 320C 28x 系列32位定点D SP 芯片的指令系统和寻址方式。

TM S 320C 28x 系列D SP 芯片的指令系统和寻址方式可以对以前的C 2000系列D SP 兼容,又增加了不少新特性。

文中重点介绍了这些新增特性,并举例说明了每一类指令和寻址方式。

关键词:指令系统;寻址方式;数字信号处理器中图分类号:TN 911.72文献标识码:A 文章编号:CN 3221289(2005)022*******Ins truc tions a nd A dd re s s ing M ode s of T MS 320C 28x DS PGUO Guo 2liang 1,YA N P ei 2jun 2,ZH A N G X iong 2w ei 3(1.Po stgraduate T eam 1I CE ,PLAU ST ,N anjing 210007,Ch ina ;2.Po stgraduate T eam 5I CE ,PLAU ST ;3.D epartm ent of E lectronic Info r m ati on Engineering I CE ,PLAU ST )A bs tra c t :T h is paper in troduced the assem b ly language in structi on s and the addressingm odes of the TM S 320C 28x 322b it fixed 2po in t digital signal p rocesso r developed by T I recen tly .Com pared w ith the fo r m er C 2000series ,TM S 320C 28x series p rovides m any new featu res of the assem b ly language in structi on s and the addressing m odes w ith em phasis on the new featu res .Exam p les w ere p rovided fo r each k ind of in structi on s and the address m odes .Ke y w o rds :in structi on ;addressing m ode ;D SP在D SP 开发应用中,熟悉D SP 芯片的指令系统和寻址方式是进行D SP 开发的基础。

TI公司三大系列DSP芯片指令系统比较

TI公司三大系列DSP芯片指令系统比较摘要:DSP技术已成为目前电子工业领域发展最迅速的技术,在各行各业的应用越来越广泛。

DSP微处理器是以数字信号来处理大量信息的器件,已成为电子工业领域增长最迅速的产品之一。

TI公司作为最早从事DSP微处理器研究的厂商之一,已经形成了三大系列的DSP芯片,在电子行业各个领域占有很大的市场份额。

本文通过对TI公司三大系列DSP芯片的简要介绍,对这三大系列芯片的指令系统进行了比较。

关键词:TI DSP芯片指令系统比较一、前言在经历整整二十年的市场拓展之后,DSP所树立的高速处理器地位不仅不可动摇,而且业已成为数字信息时代的核心引擎。

与此同时,DSP的市场正在蓬勃发展。

从TI推出业界第一颗商用DSP开始,陆续有公司设计出适合于DSP处理技术的处理器,于是DSP开始成为一种高性能处理器的名称。

TI在1982年发表一款DSP处理器名为TMS32010,其出色的性能和特性倍受业界的关注,当努力使DSP处理器每MIPS成本也降到了适合于商用的低于$10美元范围时,DSP不仅在在军事,而且在工业和商业应用中不断获得成功。

1991年TI推出的DSP批量单价首次低于$5美元而可与16 位的微处理器相媲美,但所能提供的性能却是其5至10倍。

多家公司跻身于DSP领域与TI进行市场竞争。

TI首家提供可定制DSP,称作cDSP。

cDSP 基于内核DSP的设计可使DSP具有更高的系统集成度,大加速了产品的上市时间。

同时TI瞄准DSP 电子市场上成长速度最快的领域,适时地提供各种面向未来发展的解决方案。

到九十年代中期,这种可编程的DSP器件已广泛应用于数据通信、海量存储、语音处理、汽车电子、消费类音频和视频产品等等,其中最为辉煌的成就是在数字蜂窝电话中的成功,逐渐形成了现今TI三大系列主流DSP芯片。

TI通过不断革新,推陈出新,DSP业务也一跃成为TI的最大的业务,并始终处于全球DSP市场的领导地位。

最新LDX_DSP原理与应用_张卫宁_第3章(1)精品PPT课件

65

Sind

66

Smem

67

SP

堆栈指针寄存器

68

src

源累加器(A或B)

69

ST0,ST1

70

SXM

间接寻址的单数据存储器操作数

16位单数据存储器操作数

状态寄存器0,状态寄存器1

ST1中的符号扩展方式位

第十页,共115页。

第3章 汇编语言(huì biān yǔ yán)指令系统

3.1.1 指令系统中的符号(fúhào)、缩写及操作符

第3章 汇编语言(huì biān yǔ yán)指令系统

3.1.1 指令系统(zhǐ lìnɡ xì tǒnɡ)中的符号、缩写及

操作符

序号

符 号

含

义

61

RSA

块重复起始地址寄存器

62

SBIT

用于指定状态寄存器位的4位地址(0~15)

63

SHFT

4位移位值(0~15)

64

SHIFT

5位移位值(-16~15)

汇编语言(huì biān

biān yǔ

第3章

yǔyán)指令系统

yán)指令系统

3.2.2 绝对(juéduì)寻址

□ 绝对寻址是指指令中包含着操作数的地址。

□ 绝对寻址有下列4种类型 :

➢ 数据存储器(dmad)寻址

➢ 程序存储器(pmad)寻址

➢ I/O端口(PA)寻址

➢ *(lk)寻址 (16位长立即数)

址标号或符号

来指明该数据

存储器地址

相关(xiāngguān)指令如下表所示:

绝对寻址方式

相关指令

MVDK Smem, dmad

数据存储器

c28 栈 跳转指令

c28 栈跳转指令

C28是指C28x系列的TI DSP芯片,它具有丰富的指令集和功能。

在C28x系列中,栈是用来存储和管理函数调用、局部变量和其

他重要信息的关键数据结构。

栈指针(SP)是用来指示栈顶位置的寄

存器,而栈帧指针(FP)则用来指示当前函数的栈帧的起始位置。

当

函数调用时,参数、返回地址和其他相关信息会被压入栈中,当函

数返回时,这些信息会被弹出栈。

栈的正确使用对于函数调用和返

回至关重要,因为它确保了函数之间的正确交互和数据的正确保存。

跳转指令是用来改变程序执行流程的指令,C28x系列的指令集

中包含了丰富的跳转指令,比如条件跳转、无条件跳转、函数调用

和返回等。

这些指令可以实现程序的循环、条件分支、函数调用等

功能,从而实现复杂的控制流程。

在使用跳转指令时,需要考虑到

程序的逻辑正确性和性能优化,避免出现死循环、跳转错误等问题。

总的来说,C28x系列的栈和跳转指令在程序的执行和控制流程

中起着非常重要的作用,正确的使用和理解这些机制对于编写高效、稳定的程序至关重要。

希望这个回答能够满足你的要求。

第3章C24xDSP的CPU与指令系统

9

乘积定标移位器的乘积移位方式

PM 移位 00 无移位 01 左移1位

10 左移4位

11 右移6位

作用和意义

乘积送CALU或数据写总线,不移位 移去二进制补码乘法产生的额外符号

• OV 溢出标志位,为1时,有溢出。

• OVM 溢出模式位。 OVM=1, 溢出时,A中为最大或最小值。 OVM=0,按正常溢出。

• INTM中断模式位,可禁止(INTM=1)或使能可屏蔽中断

• DP 数据存储器页面指针(Data Page) 9位,用于直接寻址地 址的高9位,与指令中的低7位共同形成16位地址。

位,产生Q31格式的乘积 当与一个13位的常数相乘时,移去在 16☓13位(常数)二进制补码产生的 额外的4位符号位,产生Q31格式的乘积 对乘积结果定标,以使得运行128次的 乘积累加而累加器不会溢出

注:Q31格式是一种二进制小数格式,表示有31位二进制小数

10

3)中央算术逻辑单元 中央算术逻辑单元(CALU, Central ALU)实现大部分 算术和逻辑运算功能,大多数功能只需一个时钟周期,这 些运算功能包括:16位加、16位减、逻辑运算、位测试以 及移位和循环功能。 由于CALU可以执行布尔运算,因此使得控制器具有 位操作功能。CALU的移位和循环在累加器中完成。 CALU是一个独立的算术单元,它和辅助寄存器算术 单元(ARAU)在程序执行时,是完全不同的两个模块。

ARAU除可对数据存储器的寻址外,还可用作它用: (1) 通过CMPR比较指令,利用辅助寄存器支持条件

转移、调用和返回; (2) 利用辅助寄存器作为暂存单元; (3) 利用辅助寄存器进行软件计数。根据需要将其加1

第3章-X86指令系统

POP REG POP SREG POP MEM

将栈顶的数据送入一个寄存器中 将栈顶的数据送入一个段寄存器中 将栈顶的数据送入内存单元

两个操作都是以字为单位进行的

34

栈指令

PUSH AX的执行过程 (1)(SP)= (SP)2,SS:SP指 向当前栈顶前面的单元,以当 前栈顶上面的单元为新的栈顶; (2)将AX中的内容送入SS:SP 指向的内存单元处,此时SS:SP 指向新栈顶。

[DI+idata]/idata[DI] [BP+idata]/idata[BP]

EA=(BX)+idata,SA=(DS) EA=(SI)+idata,SA=(DS)

EA=(DI)+idata,SA=(DS) EA=(BP)+idata,SA=(SS)

16

寄存器相对寻址

MOV AL, [BX+5]

含义 EA=(BX)+(SI),SA=(DS) EA=(BX)+(DI),SA=(DS) EA=(BP)+(SI),SA=(SS) EA=(BP)+(DI),SA=(SS)

18

基址加变址寻址

MOV AX, [BX+SI]

19

相对基址变址寻址

操作数在存储器中 偏移地址:(基址寄存器)+(变址寄存器)+相对偏移量

NUIST

第3章 80X86微处理器指令系统

主要内容

寻址方式 8086/8088指令系统 32位处理器指令系统

2

NUIST

3.1 寻址方式

处理的数据在什么地方 ? 要处理的数据有多长 ? 隐含于 机器指令内 …… 操作数

指令的一般格式: 操作码 操作数

TMS320C28x系列DSP芯片结构及引脚功能

第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812含128K×16位的片Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征1 / 16注:‡“S”是温度选择(-40℃ ~ +125℃)的特征化数据,仅对TMS是适用的。

‡‡产品预览(PP):在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI):在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包括对所有参数的测试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Event Managers Ultra-Fast 12-bit ADC 12.5 MSPS throughput Dual sample&holds enable simultaneous sampling Auto Sequencer, up to 16 conversions w/o CPU

Real-time JTAG debug shortens development cycle

Fast & flexible interrupt management significantly reduce interrupt latency

Code compatible with the TMS320C24x™ DSP family

3.1 中央处理器

1. CPU结构

C28x DSP的中央处理器(CPU)结构包括三个部分: CPU内核、仿真逻辑单元和CPU信号 。

C28x CPU组成概念框图

25.04.2020

1

仿真逻辑单元的主要功能是监视和控制 CPU以及其他外设的工作情况,并实现对设备 的测试和调试功能。

CPU的信号主要包括4种: ① 存储器接口信号 ② 时钟和控制信号 ③ 复位和中断信号 ④ 仿真信号

C28xTM 32-bit DSP

32x32 bit Multiplier

32-bit Timers (3)

Real-Time JTAG

RMW Atomic

ALU

32-bit Register

File

25.04.2020

C28xTM DSP Core

Single-cycle 32-bit multiplier makes computationally intensive control algorithms more efficient

MCeomnotrroyl SPuebri-pShyesrtaelms

Fast program execution out of both RAM and Flash memory 100-120 MIPS with Flash Acceleration Technology 150 MIPS out of RAM for time-critical code

Code security

128Kw Flash + 2Kw OTP

18Kw RAM

4Kw BInterrupt Management

150 MIPs C28xTM 32-bit DSP

32x32-bit Multiplier

32-bit Timers (3)

32位的乘法器,可执行32×32位的补码乘法,并产生 64位的结果。乘法器采用32位乘数寄存器(XT,)、32位乘积 寄存器(P)和32位累加器(ACC)。CPU的移位器实现对操作 数的移位操作。

25.04.2020

4

TMS320F2812 / TMS320F2810

Most Powerful - Most Integrated Dual Function Digital Signal Controller

25.04.2020

2

25.04.2020

F281x DSP的CPU 单元结构框图

3

C28x的CPU主要由总线、CPU寄存器、程序地址发 生器和控制逻辑、地址寄存器算术单元(ARAU)、算术逻 辑单元(ALU)、乘法器和移位器等逻辑部件组成,还包括 指令队列和指令译码单元、中断处理逻辑等。

ALU为32位的运算逻辑单元,主要执行算术运算和 布尔运算。在运算之前,ALU从寄存器、数据存储器或 程序控制逻辑单元接收数据,然后进行运算,最后把结果 存入寄存器或数据存储器中。

Communications Ports

Multiple standard communication ports provide simple interfaces to other components

5

Most C/C++ Efficient 32-bit DSP Core

Interrupt Management

内部数据总线:三组 Data Bus: 程序读数据总线PRDB (Program Read Data Bus)(0:31)。 数据读数据总线DRDB(0:31)。 数据/程序写数据总线DWDB(0:31) 数据写入DM和PM。

Real-Time JTAG

RMW Atomic

ALU

32-bit Register

File

25.04.2020

Peripheral Bus

Event Mgr A Event Mgr B 12-Bit ADC

Watchdog GPIO

McBSP CAN 2.0B SCI-UART A SCI-UART B

SPI

High-Performance CPU (C28xTM DSP Core)

150MIPS performance Single cycle 32 x32-bit MAC (or dual 16 x16 MAC) Very Fast Interrupt Response Single cycle read-modified-write F24x/LF240x Source Code Compatible

6

2812 DSP 总线结构

多组总线并行机制。 程序读、数据读、数据写三种情况 。

内部地址总线,三组 Address Bus: 程序读地址总线PAB (Program Address Bus)(0:21) 22根,4 MW。 数据读地址总线DRAB (Data Read Address Bus)(0:31) 32位。 数据写地址总线DWAB (Data Write Address Bus)(0:31)。

Three 32-bit timers support multiple control loops / time bases.

Single cycle read-modified-write in any memory location and 32-bit registers improve control algorithm efficiency