verilog可综合有限状态机的4种写法(夏文宇书注)

verilog 状态机 最佳写法

verilog 状态机最佳写法Verilog编程语言广泛应用于数字电路设计中,特别是在嵌入式系统和硬件描述语言中。

状态机是一种常用的设计模式,可以帮助我们描述复杂的行为和控制逻辑。

本文将介绍如何使用Verilog编写状态机,并提供一些最佳实践。

第一部分:Verilog简介Verilog是一种硬件描述语言,最初由美国自动化控制协会(ACM)开发。

它是一种用于描述、仿真和生成数字电路的高级编程语言。

Verilog提供了描述硬件的能力,使我们能够在逻辑级别上描述电路的行为。

第二部分:状态机简介状态机是一种抽象的数学模型,用于描述系统或程序的行为。

它由一组状态、输入和输出组成,并在不同状态之间进行转换。

状态机可以用于描述任何连续或离散的系统,包括硬件和软件。

第三部分:状态机的设计方法在Verilog中,我们可以使用参数化模块和状态寄存器来描述状态机。

参数化模块可以接受输入和输出,根据当前状态和输入转换到下一个状态,并产生相应的输出。

下面是一个简单的例子:```module fsm #(parameter N=3) (input logic clk, reset, input logic [N-1:0] input, output [N-1:0] output);typedef enum logic [1:0] {S0, S1, S2} state_t;state_t state, next_state;always_ff @(posedge clk or posedge reset) begin if (reset) beginstate <= S0;end else beginstate <= next_state;endendalways_comb begincase (state)S0: begin// State S0 behavioroutput = input;next_state = S1;endS1: begin// State S1 behavioroutput = ~input;next_state = S2;endS2: begin// State S2 behavioroutput = 2'b11;next_state = S0;enddefault: begin// Default behavioroutput = 2'b00;next_state = S0;endendcaseendendmodule```在这个例子中,我们定义了一个状态机模块,它有一个时钟信号、一个复位信号、一个输入信号和一个输出信号。

fpga 有限状态机例子

fpga 有限状态机例子有限状态机(Finite State Machine,FSM)是一种常见的设计模式,用于描述和实现具有有限数量状态的对象的行为。

在硬件设计中,有限状态机常常用于描述数字逻辑电路的行为。

以下是一个使用Verilog语言编写的简单有限状态机的例子:verilog复制代码module counter(input clk, reset, output reg [3:0] count);// 定义状态机的状态parameter IDLE = 4'b0000; // 初始状态parameter COUNTER = 4'b0001; // 计数状态// 状态机的当前状态reg [3:0] current_state;// 状态转移逻辑always @(posedge clk or posedge reset) begin if (reset) begincurrent_state <= IDLE; // 如果reset信号为高,则进入IDLE状态end else begincase (current_state)IDLE: beginif (count == 4'b1000) current_state <= COUNTE R; // 如果计数达到8,则进入COUNTER状态endCOUNTER: begincurrent_state <= IDLE; // 在COUNTER状态下,计数完成后回到IDLE状态enddefault: begincurrent_state <= IDLE; // 如果状态机处于未知状态,则强制回到IDLE状态endendcaseendend// 计数逻辑always @(posedge clk) beginif (current_state == COUNTER) count <= count + 1; // 在COUNTER状态下,计数器递增endendmodule在这个例子中,我们定义了一个简单的4位计数器。

有限状态机的verilog例子

有限状态机的verilog例子有限状态机(Finite State Machine, FSM)是数字电路设计中的一种基本构件,它可以用来实现各种复杂的控制逻辑。

在Verilog中,可以用模块(module)来描述一个有限状态机,使用参数(parameters)来定义状态数量和状态转移逻辑。

以下是一个简单的有限状态机的Verilog例子,该FSM有3个状态(S0, S1, S2)和两个输入(clk, rst_n)以及一个输出(next_state, out):```verilogmodule fsm(input wire clk, // 时钟信号input wire rst_n, // 低电平复位信号input wire [1:0] in, // 输入信号,这里位宽为2,可以扩展output reg next_state, // 下一状态输出output reg out // 输出信号);// 状态参数parameter S0 = 2'b00;parameter S1 = 2'b01;parameter S2 = 2'b10;// 状态寄存器reg [1:0] state;// 状态转移逻辑always @(posedge clk or negedge rst_n) beginif (!rst_n) begin// 当处于复位状态时,状态寄存器和输出都初始化为0state <= S0;out <= 1'b0;end else begin// 根据当前状态和输入信号,更新下一状态和输出case (state)S0: beginnext_state <= S1;out <= 1'b1;endS1: beginnext_state <= S2;out <= 1'b0;endS2: beginnext_state <= S0;out <= 1'b1;enddefault: beginnext_state <= S0;out <= 1'b0;endendcaseendendendmodule```在这个例子中:- `clk` 是时钟信号。

verilog 状态机写法

verilog 状态机写法在Verilog中,有几种常用的状态机写法,包括Mealy状态机、Moore状态机和通用状态机。

下面简要介绍每种写法的特点:Mealy状态机:输出依赖于当前状态和输入信号。

输出的变化可以与状态的变化同步。

Verilog代码示例:module MealyFSM (input logic clk,input logic reset,input logic input_signal,output logic output_signal);enum logic [2:0] states;logic [2:0] current_state, next_state;always_ff @(posedge clk or posedge reset) beginif (reset)current_state <= states[0];elsecurrent_state <= next_state;endalways_comb begincase (current_state)states[0]: begin // State 0if (input_signal)next_state = states[1];elsenext_state = states[0];output_signal = input_signal & next_state[0]; // Output depends on current state and input signalendstates[1]: begin // State 1if (input_signal)next_state = states[0];elsenext_state = states[1];output_signal = input_signal | next_state[0]; // Output depends on current state and input signalend// Add more states and conditions as neededendcaseendEndmoduleMoore状态机:输出只依赖于当前状态。

verilog hdl的四值电平逻辑,以及数值的类型和表示方法

verilog hdl的四值电平逻辑,以及数值的类型和表示方法在Verilog HDL中,四值电平逻辑指的是逻辑值包括四种状态:高电平(High)、低电平(Low)、高阻态(Z)和未知状态(X)。

这与传统的数字逻辑中只有高和低两种状态不同。

数值的类型和表示方法:1. 逻辑值:`'0'` 或 `'1'`: 逻辑0和逻辑1,分别表示低电平和高电平。

2. 线网类型 (Net Types):`wire`: 用于连接模块之间的信号,可以是四值逻辑中的任何状态。

3. 物理类型 (Physical Types):`reg`: 用于存储器或寄存器类型的变量,其值可以在仿真中被改变。

4. 连续赋值:`assign`: 用于连续赋值语句,例如 `assign a = b;`。

5. 数值表示:十进制、二进制、八进制和十六进制都可以在Verilog中表示数值。

例如,`4'b1010` 是二进制的表示方法。

6. 强类型推导:Verilog可以自动从代码中推导出变量的类型。

例如,如果一个变量只被赋值为逻辑0和1,那么它的类型将被推导为 `logic`。

7. 非确定值:有时,某些信号的值在仿真中可能不可预测或未知,可以使用非确定值 `x` 来表示。

8. 高阻态:在某些情况下,线网可能被配置为高阻态,以模拟开路或断开的情况。

这通常使用 `z` 来表示。

9. 数字系统中的信号和线网:在Verilog中,你可以定义信号(`signal`)和线网(`net`),它们可以是上述提到的任何类型和值。

10. 参数和常量:使用 `parameter` 定义常数,使用 `localparam` 定义局部常数。

这些常数可以是上述的任何数值类型。

11. 操作符:Verilog支持各种操作符,如逻辑操作符(与、或、非等)、算术操作符(加、减、乘、除等)和其他复合操作符(如异或等)。

操作符的行为取决于它们操作的值的类型和状态。

Verilog可综合有限状态机的4种写法

Verilog可综合有限状态机的4种写法Verilog可综合有限状态机的4种写法第一种:自然编码1.module fsm1(2.input i_clk,3.input rst_n,4.input A,5.output reg K1,6.output reg K2,7.output reg [1:0] state8.);[/color][/font]9.[font=Times New Roman][color=#000000]parameter Idle=2'b00,10. Start=2'b01,11. Stop=2'b10,12. Clear=2'b11;[/color][/font]13.[font=Times NewRoman][color=#000000][email=always@(posedge]always@ (posedge[/email]i_clk)14.if(!rst_n)15.begin16. state<=Idle;17. K2<=0;18. K1<=0;19.end20.else21.case(state)22. Idle:if(A)23. begin24. state<=Start;25. K1<=0;26. end28. begin29. state<=Idle;30. K2<=0;31. K1<=0;32. end33. Start:if(!A)34. state<=Stop;35. else36. state<=Start;37. Stop:if(A)38. begin39. state<=Clear;40. K2<=1;41. end42. else43. begin44. state<=Stop;45. K2<=0;46. K1<=0;47. end48. Clear:if(!A)49. begin50. state<=Idle;51. K1<=1;52. K2<=0;53. end54. else55. begin56. state<=Clear;57. K2<=0;58. K1<=1;60. default:61. state<=Idle;62. endcase63.endmodule第二种:采用独热编码,据说其可靠性和速度都不错1.module fsm2(2.input i_clk,3.input rst_n,4.input A,5.output reg K1,6.output reg K2,7.output reg [3:0] state8.);9.10.parameter Idle=4'b1000;11.parameter Start=4'b0100;12.parameter Stop=4'b0010;13.parameter Clear=4'b0001;14.15.always@(posedge i_clk)16.begin17. if(!rst_n)18. begin19. state<=Idle;20. K2<=0;21. K1<=0;22. end23. else24. case(state)25. Idle:if(A)26. begin28. K1<=0;29. end30. else31. begin32. state<=Idle;33. K2<=0;34. K1<=0;35. end36. Start:if(!A)37. state<=Stop;38. else39. state<=Start;40. Stop:if(A)41. begin42. state<=Clear;43. K2<=1;44. end45. else46. begin47. state<=Stop;48. K1<=0;49. K2<=0;50. end51. Clear:if(!A)52. begin53. state<=Idle;54. K2<=0;55. K1<=1;56. end57. else58. begin60. K2<=0;61. K1<=0;62. end63. default:state<=Idle;64.endcase65.end66.endmodule第三种:把输出直接指定为状态码,即把状态码的指定和状态机的输出联系起来,状态的变化直接用做输出据说可以提高输出信号的开关速度并节省电路资源(希望了解其机理的高手们能够解说下时怎样提高开关速度的?)1.module fsm3(2.input i_clk,3.input rst_n,4.input A,5.output K1,6.output K2,7.output reg [4:0] state8.);9.10.11.assign K2=state[4];12.assign K1=state[0];13.14.parameter Idle =5'b00000;15.parameter Start =5'b00010;16.parameter Stop =5'b00100;17.parameter StopToClear =5'b11000;18.parameter Clear =5'b01010;19.parameter ClearToIdle =5'b00111;20.21.always@(posedge i_clk)22.if(!rst_n)23.begin24. state<=Idle;25.end26.else27.case(state)28. Idle:if(A)29. state<=Start;30. else31. state<=Idle;32. Start:if(!A)33. state<=Stop;34. else35. state<=Start;36. Stop:if(A)37. state<=StopT oClear;38. else39. state<=Stop;40. StopToClear:state<=Clear;41. Clear:if(!A)42. state<=ClearToIdle;43. else44. state<=Clear;45. ClearToIdle:state<=Idle;46. default:state<=Idle;47.endcase48.endmodule第四:把状态的变化和输出开关的控制分成两部分考虑1.module fsm4(2.input i_clk,3.input rst_n,4.input A,5.output reg K1,6.output reg K2,7.output reg[1:0] state8.);9.10.11.//reg [1:0] state;12.reg [1:0] nextstate;13.parameter Idle=2'b00,14. Start=2'b01,15. Stop=2'b10,16. Clear=2'b11;17.always@(posedge i_clk)18.if(!rst_n)19. state<=Idle;20.else21. state<=nextstate;22.23.always@(state or A)24. case(state)25. Idle:if(A)26. nextstate=Start;27. else28. nextstate=Idle;29. Start:if(!A)30. nextstate=Stop;31. else32. nextstate=Start;33. Stop:if(A)34. nextstate=Clear;35. else36. nextstate=Stop;37. Clear:if(!A)38. nextstate=Idle;39. else40. nextstate=Clear;41. default:nextstate=2'bxx;42. endcase43.always@(state or rst_n or A)44.if(!rst_n)45. K1<=0;46.else47. if(state==Clear&&!A)48. K1<=1;49. else50. K1<=0;51.52.always@(state or rst_n or A)53.if(!rst_n)54. K2<=0;55.else56. if(state==Stop&&A)57. K2<=1;58. else59. K2<=0;60.endmodule。

verilog书写规范

海思高校合作——QA培训资料一、RTL CODE 规范1.标准的文件头在每一个版块的开头一定要使用统一的文件头,其中包括作者名,模块名,创建日期,概要,更改记录,版权等必要信息。

统一使用以下的文件头:// **************************************************************// COPYRIGHT(c)2005, Hislicon Technologies Co, Ltd// All rights reserved.//// IP LIB INDEX : IP lib index just sa UTOPIA_B// IP Name : the top module_name of this ip, usually, is same// as the small ip classified name just as UTOPIA// File name : file_name of the file just as “tx_fifo.v”// Module name : module_name of this file just as “TX_FIFO”// Full name : complete Emglish nme of this abbreviated//// Author : Athor/ID// Email : Author‟s email// Data :// Version : V 1.0////Abstract :// Called by : Father Module//// Modification history// ------------------------------------------------------------------------------------------------------// //// $Log$//// *********************************************************************2. 标准的module 格式(module 整体结构)对于模块的书写采用统一的格式便于项目内部成员的理解和维护,我们用批处理建立了一个MODULE模块,其内容解释如下:●端口定义按照输入,输出,双向的顺序:●模块名、模块例化名统一,例化名前加大写U_以区分(多次例化另加标识),三者关系:文件名:xxx .v (小写)模块名:XXX (大写)例化名:U_XXX (大写)IP 内部所有的模块名都要加IP名或者IP名简称作前缀,如USB_CTRL、USB_TX_FIFO。

verilog基本语法、模块写法

Verilog语言是一种硬件描述语言(HDL),用于描述和设计数字电路。

它广泛应用于数字系统的建模、验证和综合,是数字电路设计领域中的重要工具之一。

在Verilog中,模块是最基本的组织单位,模块中包含了电路的功能和行为描述。

本文将介绍Verilog语言的基本语法和模块写法,以帮助读者更好地理解和应用Verilog语言。

一、Verilog基本语法1. 注释在Verilog中,使用双斜杠(//)进行单行注释,使用/* */进行多行注释。

注释可以提高代码的可读性,便于他人理解和维护。

2. 变量声明Verilog中的变量可以分为寄存器变量(reg)和线网(wire)两种类型。

寄存器变量用于存储状态信息,线网用于连接各个逻辑门的输入和输出。

3. 逻辑运算符和位运算符Verilog中包括逻辑运算符(与、或、非等)和位运算符(与、或、异或等),用于对信号进行逻辑和位级操作。

4. 控制语句Verilog支持if-else语句、case语句等控制语句,用于根据不同条件执行不同的操作。

5. 模拟时钟在Verilog中,时钟是电路中的重要部分,通常使用时钟信号来同步各个元件的动作。

时钟可以通过周期性方波信号来模拟,使用$period 函数可以定义时钟的周期。

6. 仿真指令Verilog提供了多种仿真指令,用于初始化信号、设置仿真时间、输出波形图等操作,有助于仿真和调试电路。

二、模块写法1. 模块定义在Verilog中,一个模块包含了一组功能相关的硬件描述,可以看作是一个小型电路的抽象。

模块通过module关键字进行定义,其中包括模块名、输入输出端口声明等信息。

```verilogmodule adder(input wire [3:0] a,input wire [3:0] b,output reg [4:0] c);// 模块内部逻辑描述endmodule```2. 端口声明模块的端口包括输入端口(input)和输出端口(output),可以通过wire和reg进行声明。

verilog可综合

verilog综合小结一:基本Verilog中的变量有线网类型和寄存器类型。

线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器。

二:verilog语句结构到门级的映射连续性赋值:assign连续性赋值语句逻辑结构上就是将等式右边的驱动左边的结点。

因些连续性赋值的目标结点总是综合成由组合逻辑驱动的结点。

Assign语句中的延时综合时都将忽视。

过程性赋值:过程性赋值只出现在always语句中。

阻塞赋值和非阻塞赋值就该赋值本身是没有区别的,只是对后面的语句有不同的影响。

建议设计组合逻辑电路时用阻塞赋值,设计时序电路时用非阻塞赋值。

过程性赋值的赋值对象有可能综合成wire,latch,和flip-flop,取决于具体状况。

如,时钟控制下的非阻塞赋值综合成flip-flop。

过程性赋值语句中的任何延时在综合时都将忽略。

建议同一个变量单一地使用阻塞或者非阻塞赋值。

逻辑操作符:逻辑操作符对应于硬件中已有的逻辑门算术操作符:V erilog中将reg视为有符号数,而integer视为有符号数。

因此,进行有符号操作时使用integer,使用无符号操作时使用reg。

进位:通常会将进行运算操作的结果比原操作数扩展一位,用来存放进位或者借位。

如:Wire [3:0] A,B;Wire [4:0] C;Assign C=A+B;C的最高位用来存放进位。

关系运算符:关系运算符:<,>,<=,>=和算术操作符一样,可以进行有符号和无符号运算,取决于数据类型是reg ,net还是integer。

相等运算符:==,!=注意:===和!==是不可综合的。

可以进行有符号或无符号操作,取决于数据类型移位运算符:左移,右移,右边操作数可以是常数或者是变量,二者综合出来的结果不同。

部分选择:部分选择索引必须是常量。

BIT选择:BIT选择中的索引可以用变量,这样将综合成多路(复用)器。

敏感表:Always过程中,所有被读取的数据,即等号右边的变量都要应放在敏感表中,不然,综合时不能正确地映射到所用的门。

verilog 状态机写法

verilog 状态机写法Verilog是一种硬件描述语言,常用于设计和开发数字电路和系统。

在Verilog中,状态机是一种常用的建模方法,用于描述系统的状态和状态转移。

Verilog的状态机可以使用不同的写法来实现,通常有两种主要的方法:行为级描述和结构级描述。

行为级描述是一种以状态转移的逻辑和状态转移的条件为基础的写法。

在行为级描述中,我们需要定义状态变量和状态转移条件,然后使用if-else语句来实现状态转移逻辑。

以下是一个简单的例子,使用行为级描述写法实现一个简单的二进制计数器状态机:```verilogmodule binary_counter(input clk,input reset,output reg [3:0] count);reg [3:0] next_count;always @(posedge clk or posedge reset) beginif (reset) begincount <= 4'b0000;end else begincase (count)4'b0000: next_count = 4'b0001;4'b0001: next_count = 4'b0010;4'b0010: next_count = 4'b0011;4'b0011: next_count = 4'b0100;4'b0100: next_count = 4'b0101;4'b0101: next_count = 4'b0110;4'b0110: next_count = 4'b0111;4'b0111: next_count = 4'b1000;4'b1000: next_count = 4'b1001;4'b1001: next_count = 4'b0000;default: next_count = 4'b0000;endcasecount <= next_count;endendendmodule```在上面的例子中,我们定义了一个4位的计数器变量`count`,并在always块中定义了状态转移逻辑。

verilog的四种逻辑状态

Verilog的四种逻辑状态一、引言Verilog是一种硬件描述语言(HDL),用于对数字电路进行建模和设计。

在Verilog中,逻辑状态指的是信号的取值,常用的逻辑状态有四种:0、1、X和Z。

本文将介绍这四种逻辑状态的含义、用途和在Verilog中的表示方式。

二、0在Verilog中,0表示低电平或逻辑假。

当信号为0时,表示该信号处于低电平状态。

在数字电路中,常用的逻辑门如与门、或门、非门等,输入为0时输出一般为0,所以0在电路中是非常常见的逻辑状态。

在Verilog中,可以使用0或'0'表示逻辑值为0,例如:reg a = 0;。

同时,也可以使用1'b0来明确表示逻辑值为0。

三、1在Verilog中,1表示高电平或逻辑真。

当信号为1时,表示该信号处于高电平状态。

与0相反,1也是数字电路中常见的逻辑状态。

例如,在与门中,当输入都为1时,输出为1;在或门中,只要有一个输入为1,输出就为1。

在Verilog中,可以使用1或'1'表示逻辑值为1,例如:wire b = 1;。

同时,也可以使用1'b1来明确表示逻辑值为1。

四、X在Verilog中,X表示未知逻辑状态。

当信号的值为X时,表示该信号的确切逻辑值未知或未定义。

通常情况下,X会在电路中表示不确定性或故障。

在Verilog中,可以使用X或'x'表示未知逻辑值,例如:reg c = X;。

同时,也可以使用1'bx来表示。

五、Z在Verilog中,Z表示高阻态或高阻抗。

当信号的值为Z时,表示该信号处于高阻态,即无法确定信号的逻辑值。

Z通常用于表示电路中的三态输出、开关或未实现的输出。

在Verilog中,可以使用Z或'z'表示高阻态,例如:reg d = Z;。

同时,也可以使用1'bz来表示。

六、应用场景0、1、X和Z是Verilog中常用的逻辑状态,它们在不同的应用场景下具有不同的意义。

北航 夏宇闻 Verilog HDL语法具体讲解

语法详细讲解

载入存储设备

可以通过使用一个循环或系统任务来载入存有数据的整个存储 器。

ata ,,,,,,,,,,,,,,,0 000 ,,,,,,,,,,,,,,,0 101

reg [3:0] mem [0:15];

,,,,,,,,,,,,,,,1

initial

100

$readmemb(“my_rom_data”,mem); always @ (addr or read_en_)

,,,,,,,,,,,,,,,0

的节点或测试模块中在多个地方被赋值的信号)进行赋值。 initial begin

#10 assign top.dut.fsml.state_reg = `init_state;

语字语强语强法符法制法制详串详详激激,细,细,细励励,,讲讲,讲,,解,解,解

#20 deassign top.dut.fsml.state_reg; end force 和 release 用于寄存器类型和网络连接类型(例如:门级扫 描寄存器的输出)的强制赋值,强制改写其它地方的赋值。

语法详细讲解

强制激励

在一个过程块中,可以用两种不同的方式对信号变量或表达式进 行连续赋值。 ▪ 过程连续赋值往往是不可以综合的,通常用在测试模块中。 ▪ 两种方式都有各自配套的命令来停止赋值过程。 ▪ 两种不同方式均不允许赋值语句间的时间控制。 assign和deassign 适用于对寄存器类型的信号(例如:RTL级上

,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,

,,k注延,,,,,,,,:迟,,,,,,,,这期,,,#,,(两间,p,,e,个一,r,i,o,时直,d,,/,2钟 是,,),,,模低,,,,,,,,型电,c,l,k,有平,=,,,!些,,c,,l,不而同门,级行描为述描的述模的型模开型始

Verilog 的有限状态机

基于Verilog HDL的有限状态机1.有限状态机1.1 概述有限状态机是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。

有限状态机又可以认为是组合逻辑和寄存器逻辑的一种组合。

状态机特别适合描述那些发生有先后顺序或者有逻辑规律的事情,其实这就是状态机的本质。

状态机就是对具有逻辑顺序或时序规律的事件进行描述的一种方法在实际的应用中根据状态机的输出是否与输入条件相关,可将状态机分为两大类,即摩尔 (Moore)型状态机和米勒 (Mealy) 型状态机。

图 1Mealy型状态转移图1.2 状态机的描述方法状态机的描述方法多种多样,将整个状态机写到1个always 模块里,在该模块中既描述状态转移,又描述状态的输入和输出,这种写法一般被称为一段式FSM 描述方法;还有一种写法是使用两个always模块,其中一个always 模块采用同步时序的方式描述状态转移,而另一个模块采用组合逻辑的方式判断状态转移条件,描述状态转移规律,这种写法被称为两段式FSM 描述方法;还有一种写法是在两段式描述方法的基础上发展而来的,这种写法使用3 个always模块,一个always 模块采用同步时序的方式描述状态转移,一个采用组合逻辑的方式判断状态转移条件,描述状态转移规律,第三个always 模块使用同步时序电路描述每个状态的输出,这种写法称为三段式写法。

1.3 FSM的状态编码二进制码(Binary)和格雷码(Gray)属于压缩状态编码,这种编码的优点是使用的状态向量最少,但是需要较多的逻辑资源用来状态译码。

二进制码从一个状态转换到相邻状态时,可能有多个比特位发生变化,易产生中间状态转移问题,状态机的速度也要比采用其它编码方式慢。

格雷码两个相邻的码值仅有一位就可区分,这将会减少电路中相邻物理信号线同时变化的情况,因而可以减少电路中的电噪声。

Johnson码也有同样的特点,但是要用较多的位数。

独热码(One-hot)指对任意给定的状态,状态寄存器中只有l位为1,其余位都为0。

verilog的一些固定写法

verilog的一些固定写法Verilog是一种硬件描述语言,用于描述数字电路。

在Verilog 中有一些固定的写法和规范,以下是一些常见的固定写法:1. 模块声明:每个Verilog文件通常以模块声明开始,例如:module module_name (input input1, input input2, output output1);input和output关键字用于声明端口,module_name是模块的名称。

2. 端口声明:在模块声明中,端口通常按照输入和输出分别声明,例如:input input1, input input2;output output1;3. 数据类型声明:Verilog中常见的数据类型包括wire、reg、integer等,这些数据类型用于声明变量的类型和存储方式。

4. 时钟声明:在数字电路中,时钟是非常重要的,通常会使用时钟信号来同步各个部分。

时钟声明通常如下:input wire clk;5. 逻辑运算:在Verilog中,常见的逻辑运算包括与(&)、或(|)、非(!)、异或(^)等,这些逻辑运算符可以用于描述数字电路中的逻辑操作。

6. 连接符号:在Verilog中,连接符号用于连接不同的信号线,常见的连接符号包括逗号(,)和连接运算符({})。

7. 时序建模:Verilog中可以使用一些关键字来描述时序行为,比如always、posedge、negedge等,这些关键字用于描述触发器的行为。

以上是一些Verilog中的固定写法和常见规范,遵循这些规范可以使Verilog代码更加清晰易懂,也更容易被其他人理解和维护。

希望以上回答能够满足你的需求。

verilog四种循环方式

verilog四种循环方式verilog有四中循环方式分别是 forever,repeat while forinitialbeginclk = 0;wait(reset == 1'b1)forever #25 clk = ~clk;end其中wait 为电平控制,与posedge 和negedge不一样的是,他们是触发控制if (reset = 1'b0)repeat(10)begintemp = data[15];data = {data<<1,temp};endlocation = 0;if(data[0] == 0)location = 32;elsewhile(data[0] == 0)beginlocation += 1;data <<1;endfor就省略了。

还有一种零延迟循环,即alwaysbegin....end在具体的编程过程中,碰到了这样的问题,起初用for循环来实现,发现仿真的结果都一样,都是最后一个地址的值,原因是由于for在执行过程中很快,导致前面读出的值都被后面的值覆盖,最终出现最后一个值的情况。

以下是简单的for的实例,不能实现正确的读取rom。

module for(clk,dout);input clk;output [3:0] dout;reg [3:0] dout;reg [3:0] i;wire[3:0]table_in;wire [3:0]table_out;always @( posedge clk )for(i=0;i<16;i=i+1)dout<=table_out;assign table_in=i;rom wt(.table_in(table_in),.table_out(table_out));endmodule为了实现循环读取rom,可以将for语句改作if-else语句来实现,就可以了。

Verilog 硬件描述语言参考手册-北航夏宇闻经典教程

有时候,编译完了马上就能进行仿真,没有必要创建中间数据文件。

eg ----------------------------------------------------------------------------三. 语法总结

VectorReg[Bit] = Expression; VectorReg[MSB:LSB] = Expression; Memory[Address] = Expression; assign Reg = Expression deassign Reg;

TaskEnable(...);

3

disable TaskOrBlock; EventName;

描述组合和锁存逻辑的always块一定不能包含反馈,也就是说在always块中已被定义为 输出的寄存器变量绝对不能再在该always块中读进来作为输入信号。

is 时钟沿触发的always块必须是单时钟的,并且任何异步控制输入(通常是复位或置位信

号)必须在控制事件列表中列出。

g 避免生成不想要的锁存器。在无时钟的always块中,由于有的输出变量被赋了某个信号

Ÿ 应建立一个定义得很好的时钟策略,并在Verilog源代码中清晰地体现该策略(例如采

用单时钟、多相位时钟、经过门产生的时钟、多时钟域等)。保证在Verilog源代码中

Ÿ

Ÿ

Ÿ Ÿ

Ÿ

Ÿ

Ÿ

ŸŸLeabharlann Ÿ时钟和复位信号是干净的(即不是由组合逻辑或没有考虑到的门产生的) 要建立一个定义得很好的测试(制造)策略,并认真编写其Verilog代码,使所有的触 发器都是可复位的,使测试能通过外部管脚进行,又没有冗余的功能等。

verilog状态机的分类及编写方式

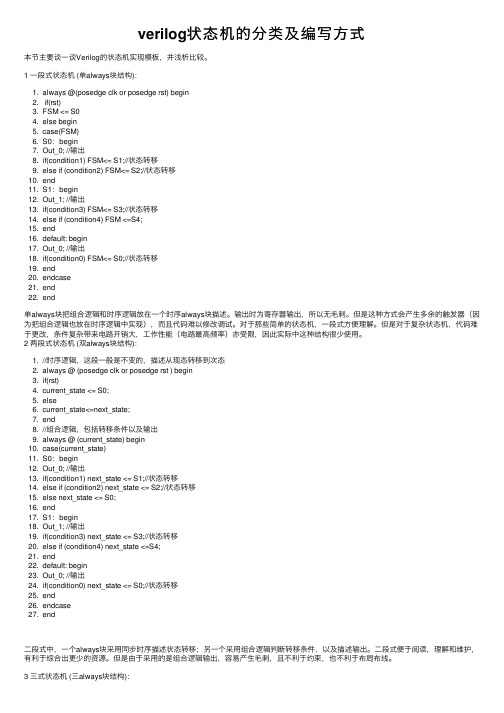

verilog状态机的分类及编写⽅式本节主要谈⼀谈Verilog的状态机实现模板,并浅析⽐较。

1 ⼀段式状态机 (单always块结构):1. always @(posedge clk or posedge rst) begin2. if(rst)3. FSM <= S04. else begin5. case(FSM)6. S0:begin7. Out_0; //输出8. if(condition1) FSM<= S1;//状态转移9. else if (condition2) FSM<= S2;//状态转移10. end11. S1:begin12. Out_1; //输出13. if(condition3) FSM<= S3;//状态转移14. else if (condition4) FSM <=S4;15. end16. default: begin17. Out_0; //输出18. if(condition0) FSM<= S0;//状态转移19. end20. endcase21. end22. end单always块把组合逻辑和时序逻辑放在⼀个时序always块描述。

输出时为寄存器输出,所以⽆⽑刺。

但是这种⽅式会产⽣多余的触发器(因为把组合逻辑也放在时序逻辑中实现),⽽且代码难以修改调试。

对于那些简单的状态机,⼀段式⽅便理解。

但是对于复杂状态机,代码难于更改,条件复杂带来电路开销⼤,⼯作性能(电路最⾼频率)亦受限,因此实际中这种结构很少使⽤。

2 两段式状态机 (双always块结构):1. //时序逻辑,这段⼀般是不变的,描述从现态转移到次态2. always @ (posedge clk or posedge rst ) begin3. if(rst)4. current_state <= S0;5. else6. current_state<=next_state;7. end8. //组合逻辑,包括转移条件以及输出9. always @ (current_state) begin10. case(current_state)11. S0:begin12. Out_0; //输出13. if(condition1) next_state <= S1;//状态转移14. else if (condition2) next_state <= S2;//状态转移15. else next_state <= S0;16. end17. S1:begin18. Out_1; //输出19. if(condition3) next_state <= S3;//状态转移20. else if (condition4) next_state <=S4;21. end22. default: begin23. Out_0; //输出24. if(condition0) next_state <= S0;//状态转移25. end26. endcase27. end⼆段式中,⼀个always块采⽤同步时序描述状态转移;另⼀个采⽤组合逻辑判断转移条件,以及描述输出。

Verilog 有限状态机设计 ppt课件

第八章 有限状态机设计

Verilog 有限状态机设计

MOORE状态机 MEALY状态机 有限状态机的几种描述方式 有限状态机的状态编码

8.1 有限状态机

构成

组合逻辑 状态译码、产生输出 时序逻辑 存储状态

分类

Moore 输出是现态的函数 Mealy 输出是现态和输入的函数

always @(state) /*该过程产生输出逻辑*/

begin case(state) S3: z=1'b1; default:z=1'b0;

endcase end endmodule

“101”序列检测器(单过程描述)

module fsm4_seq101(clk,clr,x,z); input clk,clr,x; output reg z; reg[1:0] state; parameter S0=2'b00, S1=2'b01, S2=2'b11, S3=2'b10;/*状态编码,采用格雷(Gray)编码方 式*/

parameter S0=2'b00,S1=2'b01,S2=2'b11,S3=2'b10;

/*状态编码,采用格雷(Gray)编码方式*/

always @(posedge clk or posedge clr) /*该过程定义当前状态*/

begin

if(clr) state<=S0; //异步复位,s0为起始状态

(1)用三个过程描述:即现态(CS)、次态(NS)、 输出逻辑(OL)各用一个always过程描述。

(2)双过程描述(CS+NS、OL双过程描述):使用两 个always过程来描述有限状态机,一个过程描述现态和次 态时序逻辑(CS+NS);另一个过程描述输出逻辑(OL)。

Verilog课件 状态机

青岛科技大学

2013-8-2

(15)

宋廷强 songtq@

W W W . Q U S T . E D U . C N

Stop: begin //符合条件进入新状态,否则留在原状态 if (A) begin state <= Clear; K2<= 1; end else state <= Stop; end Clear: begin if (!A) begin state <= Idle; K2<=0; K1<=1; end else state <= Clear; end endcase endmodule

青岛科技大学

2013-8-2

(4)

宋廷强 songtq@

状态机的结构

W W W . Q U S T . E D U . C N

• 状态寄存器: • 输出逻辑:

记忆状态机当前所处的状态,n个触发器可以记忆2n个状态

• 产生下一个状态的组合逻辑: 根据输入信号和当前状态,决定下一个状态

由当前状态和输出信号决定当前状态的输出。

青岛科技大学

20 W W . Q U S T . E D U . C N

Start: if (!A) state <= Stop; else state <= Start; Stop: if (A) begin state <= Clear; K2<= 1; end else state <= Stop; Clear: if (!A) begin state <=Idle; K2<=0; K1<=1; end else state <= Clear;

如何用Verilog来描述状态机

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

verilog可综合有限状态机的4种写法(夏文宇书注)

第一种:自然编码

module fsm1(

input i_clk,

input rst_n,

input A,

output reg K1,

output reg K2,

output reg [1:0] state

);

parameter Idle=2'b00,

Start=2'b01,

Stop=2'b10,

Clear=2'b11;

[email=always@(posedge]always@(posedge[/email] i_clk)

if(!rst_n)

begin

state<=Idle;

K2<=0;

K1<=0;

end

else

case(state)

Idle:if(A)

begin

state<=Start;

K1<=0;

end

else

begin

state<=Idle;

K2<=0;

K1<=0;

end

Start:if(!A)

state<=Stop;

else

state<=Start;

Stop:if(A)

begin

state<=Clear;

K2<=1;

else

begin

state<=Stop;

K2<=0;

K1<=0;

end

Clear:if(!A)

begin

state<=Idle;

K1<=1;

K2<=0;

end

else

begin

state<=Clear;

K2<=0;

K1<=1;

end

default:

state<=Idle;

endcase

endmodule

这种大家应该都熟悉的

第二种:采用独热编码,据说其可靠性和速度都不错module fsm2(

input i_clk,

input rst_n,

input A,

output reg K1,

output reg K2,

output reg [3:0] state

);

parameter Idle=4'b1000;

parameter Start=4'b0100;

parameter Stop=4'b0010;

parameter Clear=4'b0001;

always@(posedge i_clk)

begin

if(!rst_n)

state<=Idle;

K2<=0;

K1<=0;

end

else

case(state)

Idle:if(A)

begin

state<=Start;

K1<=0;

end

else

begin

state<=Idle;

K2<=0;

K1<=0;

end

Start:if(!A)

state<=Stop;

else

state<=Start; Stop:if(A)

begin

state<=Clear;

K2<=1;

end

else

begin

state<=Stop;

K1<=0;

K2<=0;

end

Clear:if(!A)

begin

state<=Idle;

K2<=0;

K1<=1;

end

else

begin

state<=Clear;

K2<=0;

K1<=0;

end

default:state<=Idle;

endcase

end

endmodule

第三种:把输出直接指定为状态码,即把状态码的指定和状态机的输出联系起来,状态的变化直接用做输出

据说可以提高输出信号的开关速度并节省电路资源(希望了解其机理的高手们能够解说下时怎样提高开关速度的?)

module fsm3(

input i_clk,

input rst_n,

input A,

output K1,

output K2,

output reg [4:0] state

);

assign K2=state[4];

assign K1=state[0];

parameter Idle =5'b00000;

parameter Start =5'b00010;

parameter Stop =5'b00100;

parameter StopToClear =5'b11000;

parameter Clear =5'b01010;

parameter ClearToIdle =5'b00111;

always@(posedge i_clk)

if(!rst_n)

begin

state<=Idle;

end

else

case(state)

Idle:if(A)

state<=Start;

else

state<=Idle;

Start:if(!A)

state<=Stop;

else

state<=Start;

Stop:if(A)

state<=StopToClear;

else

state<=Stop;

StopToClear:state<=Clear;

Clear:if(!A)

state<=ClearToIdle;

else

state<=Clear;

ClearToIdle:state<=Idle;

default:state<=Idle;

endcase

endmodule

第四:把状态的变化和输出开关的控制分成两部分考虑module fsm4(

input i_clk,

input rst_n,

input A,

output reg K1,

output reg K2,

output reg[1:0] state

);

//reg [1:0] state;

reg [1:0] nextstate;

parameter Idle=2'b00,

Start=2'b01,

Stop=2'b10,

Clear=2'b11; always@(posedge i_clk)

if(!rst_n)

state<=Idle;

else

state<=nextstate;

always@(state or A)

case(state)

Idle:if(A)

nextstate=Start;

else

nextstate=Idle;

Start:if(!A)

nextstate=Stop;

else

nextstate=Start;

Stop:if(A)

nextstate=Clear;

else

nextstate=Stop;

Clear:if(!A)

nextstate=Idle;

else

nextstate=Clear;

default:nextstate=2'bxx; endcase

always@(state or rst_n or A) if(!rst_n)

K1<=0;

else

if(state==Clear&&!A)

K1<=1;

else

K1<=0;

always@(state or rst_n or A) if(!rst_n)

K2<=0;

else

if(state==Stop&&A)

K2<=1; else

K2<=0; endmodule。