Verilog 有限状态机设计

第八次课-8章状态机精选全文

z<=0;

三、基于状态机的设计要点

1.起始状态的选择

起始状态是指电路复位后所处的状态,选择一 个合理的起始状态将使整个系统简洁高效。有的 EDA软件会自动为基于状态机的设计选择一个最佳 的起始状态。

2.状态转换的描述

一般使用case语句来描述状态之间的转换, 用case语句表述比用if-else语句更清晰明了。

有限状态机类型 有限状态机的Verilog描述 有限状态机的设计要点

一、两种有限状态机

二、有限状态机的Verilog描述

描述对象:

当前状态、下一状态、输出逻辑

描述方式: 单过程、双过程、三过程

单过程描述方式: 放在一个过程中描述,相当于采用时

钟信号同步,克服输出产生毛刺。但输出 逻辑相对于双过程,要延迟一个时钟周期。

end end

s3: begin if(x==0)

begin state<=s0; z<=0;

end else begin

state<=s4; z<=1; end end

s4: begin if(x==0)

begin state<=s0; end else begin state<=s4; z<=1; end end default:

双过程描述方式: 一个过程 由时钟信号触发的时序过程

(当时钟发生跳变时,状态机状态发生变 化。一般用case语句检查状态机的当前状态; 另一过程是组合过程,对于摩尔型,输出 只与当前状态有关,因此只需用case语句即 可,对米里型,因与当前状态和输入都有 关,因此可用case 语句和 if组合进行描述。

基于Verilog 的有限状态机设计

基于Verilog 的有限状态机设计与优化1 引言在集成电路的设计过程中, 不论是使用FPGA还是ASIC 来实现, 有限状态机经常是作为一个电路设计的关键部分而出现的. 状态机的功能是否完善( 是否强壮型) 对整个电路会产生重大的影响.有限状态机主要有两种类型: Moore 型状态机和M ealy 型状态机. Moore 型状态机是指输出只与当前状态有关, 与输入信号无直接关系. 而Mealy 型状态机的输出不只与当前状态有关, 还与输入信号有关.文中以目前常用的硬件描述语言Verilog HDL 为基础, 对不同的状态机编码类型和状态机描述风格对状态机性能的影响进行了深入的分析. 分别使用Xilinx ISE 和Design Compiler 对实例进行了综合,分析了面积、速度与功耗的信息, 给出了对于不同类型状态机的最佳编码风格.2 状态机编码状态的编码方式最常用的有二进制码、格雷码和独热码三种, 不同的状态机编码方式对状态机的影响非常大. 如表1 所示.二进制的编码从第一个状态到最后一个状态是按二进制码的顺序排列的, 是一种最普通的编码方式.表1 不同的编码比较十进制码Binary code Gray code One- hot code0 000 000 00011 001 001 00102 010 011 01003 011 010 1000用格雷码进行状态的变换时, 相邻状态转换只有一个状态位发生翻转. 这样就可以消除转换时由多条状态信号线的传输延迟所造成的毛刺, 大大地减少了由一个状态到下一个状态时逻辑的混淆可以降低功耗.one- hot 状态译码简单, 只有1 位是1 其他位为0, 易于修改, 可以减少组合逻辑, 但会使用更多的触发, 增加电路面积.Binary- code、Gray- code 编码使用最少的触发器, 较多的组合逻辑, 而One- hot 编码反之.因此, Binary 和Gray- code 适用于触发器资源较少, 组合电路资源丰富的情况( CPLD) , 对于FP GA 则更适用One- hot code, 因为这样可以充分利用FPGA 丰富的触发器资源. 另外, 小型设计通常使用Binary- code 和Gray- code, 对于大型的设计使用One- hot code 效果更佳.3 状态机的描述方法状态机的描述方法通常有三种: 一段式( one al ways) 、二段式( two always) 和三段式( three always) .3. 1 一段式一段式的状态机描述方法是指将整个状态机写到一个alw ays 模块里, 该模块描述当前状态转移, 又描述状态的输入和输出.由于一段式的描述方法是给STATE 自身赋值, 所以本身就会引入一个周期的延时, 需要在设计中通过预计算考虑进去.一段式的描述方法所有输出都是寄存器输出的, 因此不会产生毛刺, 但是这种组合逻辑和时序逻辑都写到一起的方法是不可取的, 而且在描述当前状态的时候还要考虑到下一状态的输出. 这种描述方法可读性差、难于理解和维护, 不利于时许约束、功能更改及调试, 对于Mealy 型的状态机来说, 容易出现Latches.3. 2 二段式二段式的状态机描述方法是指使用两个always模块, 其中一个always 模块采用同步时序的方式描述当前状态和下一状态的转移, 另一个alw ays 模块采用组合逻辑来描述下一状态和输出向量的赋值.二段式的描述方法比一段式的更合理, 它更易于阅读、理解和维护, 更利于综合并优化代码. 但是它的缺点是第二个alw ays 块组合逻辑的输出会出现毛刺, 影响电路性能.3. 3 三段式三段式的状态机描述方法是由二段式发展而来的, 在二段式两个alw ays 的基础上又增加了一个alw ays 块来描述每个状态的输出, 用寄存器寄存了一拍, 达到同步输出的目的.需要注意的是, 增加的一级寄存器会引入一个周期的延时, 需要在设计中通过预计算考虑进去, 避免逻辑发生错误. 这样一级寄存器的引入, 也就形成了FSMs 输入逻辑的一级流水.引入了组合逻辑寄存, 输出同步不仅会带来运行性能的提升, 还会增加系统的稳定性, 防止输出信号出现毛刺, 防止组合回路的产生.4 实例分析下面以一个简单红绿灯状态转移为例进行分析, 当RESET 信号给出以后进入IDEL 状态, 之后状态机的描述方法通常有三种: 一段式( one al 进入RED 状态, 之后进入GREEN 状态, 之后进入YELLOW 状态, 最后回到RED 状态. Default 时进入IDEL 状态.一4. 1 使用Xilinx ISE 进行分析在使用Xilinx ISE 对例子进行综合的时候, 右键点中综合软件, 选属性选型, 在HDL Options 中有一个优化选项为FSM Encoding Algorithm, 在其下拉菜单中选中AUTO( 默认项) , 工具就可以自动修改设计中的状态机的状态编码, 使其成为对FPGA 来说最优的编码风格.对于本设计来说, 由于只有4 个状态, 所以状态编码被优化成了Gray- code. 但是经过验证, 在状态较多的状态机设计中, 状态编码一般都被优化成One- hot code.通过表2, 对Xilinx ISE 的综合后报表进行分析可以看到, 由于one always 的状态机全部为时序电路,所以最大频率会比two alw ays 和three always 大.在面积方面, two always 型的状态机所占面积最小, three alw ays 稍大, 而one alw ays 型的状态机所用门数最多, 所占面积也最大.对于功耗来说, 使用Xilinx ISE 集成的Xpower进行功耗分析, 所得到的三种状态机编码风格的功耗并不存在明显差异.表2 Xilinx ISE 的综合结果使用门数最大频率one alw ays 8 313. 283MHztwo always 43 312. 891MHzthree alw ays 67 312. 891MHz4. 2 使用Design Compiler 进行分析在使用Design Complier 对所举实例进行分析话时, 分别选取了1always& binary、1always& one - hot、2always& binary、2alw ays& one - hot 、3alw ays& binary、3always& one- hot 等6 种设计, 每个设计分别设定了2 个时钟周期( . ns 和7ns) 进行分析. 综合得到的面积和延时的结果按顺序标在图2、图3 中. 表3、表4 给出了详细的数据.由图2 可见, 2alw ays 在面积上具有明显优势,其次是3alw ays. 由图3 对时序的分析可见, 2alw ays也是具有一定的优势.比较使用Design Compiler 和Xilinx ISE 的综合结果可以发现, 不论是使用FPGA 还是ASIC, tw oalw ays 所占面积总是最小的, 其次是three alw ays,而one alw ays 所占面积最大. 这主要是由于one alw ays 的状态机全部为时序电路, 所以花费的面积最大, three alw ays 由于多采用一级寄存器同步, 所以所花费的面积比two always 的要大一些.5 比较分析通过以上分别使用Xilinx ISE 和Design Compiler 对实例进行的分析, 可见two alw ays 的编码风格存在巨大的优势. 因为Moore 型的状态机输出只有状态寄存器驱动, 状态机所受影响差异不会很大,所以建议对Moore 型状态机采用two alw ays 的编码风格.而Mealy 型状态机, 输出不只与当前状态有关,还与输入信号有关, 输出是组合逻辑的输出, 这样在每个STATE 中产生的信号复杂而且有不同的timeskew , 如果信号直接输出而不引用寄存器同步的话, 在高频的电路中很可能会导致时序上的错误. 所以建议使用three alw ays 风格, 将输出同步一拍.对于one alw ays 的风格, 虽然在一些开源的IP盒中经常见到, 但是通过以上的分析, 可以发现这种状态及描述风格存在着巨大的缺陷.至于状态编码的使用, 对于FPGA 来说建议使用工具自动优化状态机的状态编码, 而对于ASIC 来说, 建议在小型设计中使用Binary- code 和Gray code, 而对于大型的设计则使用One- hot code.6 结束语文中结合了一个Verilog HDL 的实例, 对三种不同的状态机编码和状态机描述方式进行了深入的研究, 分析了其各自的优缺点. 并分别使用Xilinx ISE 和Design Compiler 对一个实例进行了综合, 对面积、速度与功耗进行了分析. 结果表明one alw ays的写法需要被摒弃, two alw ays 的编码风格适合Moore 型状态机, 而three always 的编码风格适合Mealy 型状态机. 文中同时也给出了适合不同设计的最优状态编码。

Verilog 有限状态机设计 ppt课件

第八章 有限状态机设计

Verilog 有限状态机设计

MOORE状态机 MEALY状态机 有限状态机的几种描述方式 有限状态机的状态编码

8.1 有限状态机

构成

组合逻辑 状态译码、产生输出 时序逻辑 存储状态

分类

Moore 输出是现态的函数 Mealy 输出是现态和输入的函数

always @(state) /*该过程产生输出逻辑*/

begin case(state) S3: z=1'b1; default:z=1'b0;

endcase end endmodule

“101”序列检测器(单过程描述)

module fsm4_seq101(clk,clr,x,z); input clk,clr,x; output reg z; reg[1:0] state; parameter S0=2'b00, S1=2'b01, S2=2'b11, S3=2'b10;/*状态编码,采用格雷(Gray)编码方 式*/

parameter S0=2'b00,S1=2'b01,S2=2'b11,S3=2'b10;

/*状态编码,采用格雷(Gray)编码方式*/

always @(posedge clk or posedge clr) /*该过程定义当前状态*/

begin

if(clr) state<=S0; //异步复位,s0为起始状态

(1)用三个过程描述:即现态(CS)、次态(NS)、 输出逻辑(OL)各用一个always过程描述。

(2)双过程描述(CS+NS、OL双过程描述):使用两 个always过程来描述有限状态机,一个过程描述现态和次 态时序逻辑(CS+NS);另一个过程描述输出逻辑(OL)。

fpga 有限状态机例子

fpga 有限状态机例子有限状态机(Finite State Machine,FSM)是一种常见的设计模式,用于描述和实现具有有限数量状态的对象的行为。

在硬件设计中,有限状态机常常用于描述数字逻辑电路的行为。

以下是一个使用Verilog语言编写的简单有限状态机的例子:verilog复制代码module counter(input clk, reset, output reg [3:0] count);// 定义状态机的状态parameter IDLE = 4'b0000; // 初始状态parameter COUNTER = 4'b0001; // 计数状态// 状态机的当前状态reg [3:0] current_state;// 状态转移逻辑always @(posedge clk or posedge reset) begin if (reset) begincurrent_state <= IDLE; // 如果reset信号为高,则进入IDLE状态end else begincase (current_state)IDLE: beginif (count == 4'b1000) current_state <= COUNTE R; // 如果计数达到8,则进入COUNTER状态endCOUNTER: begincurrent_state <= IDLE; // 在COUNTER状态下,计数完成后回到IDLE状态enddefault: begincurrent_state <= IDLE; // 如果状态机处于未知状态,则强制回到IDLE状态endendcaseendend// 计数逻辑always @(posedge clk) beginif (current_state == COUNTER) count <= count + 1; // 在COUNTER状态下,计数器递增endendmodule在这个例子中,我们定义了一个简单的4位计数器。

有限状态机的verilog例子

有限状态机的verilog例子有限状态机(Finite State Machine, FSM)是数字电路设计中的一种基本构件,它可以用来实现各种复杂的控制逻辑。

在Verilog中,可以用模块(module)来描述一个有限状态机,使用参数(parameters)来定义状态数量和状态转移逻辑。

以下是一个简单的有限状态机的Verilog例子,该FSM有3个状态(S0, S1, S2)和两个输入(clk, rst_n)以及一个输出(next_state, out):```verilogmodule fsm(input wire clk, // 时钟信号input wire rst_n, // 低电平复位信号input wire [1:0] in, // 输入信号,这里位宽为2,可以扩展output reg next_state, // 下一状态输出output reg out // 输出信号);// 状态参数parameter S0 = 2'b00;parameter S1 = 2'b01;parameter S2 = 2'b10;// 状态寄存器reg [1:0] state;// 状态转移逻辑always @(posedge clk or negedge rst_n) beginif (!rst_n) begin// 当处于复位状态时,状态寄存器和输出都初始化为0state <= S0;out <= 1'b0;end else begin// 根据当前状态和输入信号,更新下一状态和输出case (state)S0: beginnext_state <= S1;out <= 1'b1;endS1: beginnext_state <= S2;out <= 1'b0;endS2: beginnext_state <= S0;out <= 1'b1;enddefault: beginnext_state <= S0;out <= 1'b0;endendcaseendendendmodule```在这个例子中:- `clk` 是时钟信号。

Verilog 有限状态机设计(课堂PPT)

begin

case( state )

state0:

out = 3'b001;

state1:

out = 3'b010;

state2:

out = 3'b100;

state3:

out = 3'b111;

default:

out = 3'b001;

endcase

end

endmodule

11

8.2 有限状态机的Verilog描述

begin if(clr) qout<=0;

//异步复位

else case(qout)

3'b000: qout<=3'b001;

3'b001: qout<=3'b010;

3'b010: qout<=3'b011;

3'b011: qout<=3'b100;

3'b100: qout<=3'b000;

default: qout<=3'b000; /*default语句*/

state2 = 2’b11, state3 = 2’b10; // 格雷码

always @( posedge clk or posedge clr ) begin

if( clr ) state <= state0; // 定义初态 state <= next_state; end

8

always @( state or start or step2 or step3 ) // 状态转换

EDA技术与应用

第八章 有限状态机设计

1

基于Verilog HDL的有限状态机的优化设计

第二个进程组合逻辑 a as l y 模块的设计和二段式 的 w 设计相似 , 但是其只进行输入判断和状态转移规律描述 , 而不进行组合逻辑输出 ; 第三个进程也设计成 同步时序 a as l y 模块 ,采用同 w

步时序逻辑寄存 F M 的输出。 S

4三种状态机的逻辑、 电路 、 仿真分析

mp _t a e — ” jgi u uc O 一 / jg u— i s em r i / p / p t v. ” O” p/ t g r m n _ S m o

)

警

图 1 频 采集 图像 0视

图 8内核启动前加载摄 像头驱 动信息

不管你在何时插入 , 以上信息之一都表明 , 出现 摄像

头驱动加载成功 。驱动加载成功后 同时会在 /e dv目录下 产生一个 v eO i o 的设备节点 。 l命令可 以查看 , 图 9 d 用 s 如

所示 。

一

检验所设计 的 F M 的完备性 ,如果所设 计 的 F M不完 S S 备, 则会进入任意状态 , 仿真时很容易发现。

33三段式(h e — l y ) - T re awa s状态机 三段式状态机的设计 即使用三个进程对状态机进行 描述。第一个 a as l y 模块使用 同步时序描述状态之间的 w 转移 ; 第二个 a as l y 模块使用组合逻辑判 断状 态转移条 w 件, 描述状态转移规律 ; 第三个 a as l y 模块采用同步时序 w

成了远程视频数据 的采集 ,为整个 网络智能家居监控 系

统的实现打下了基础 。

摄像头被驱动后 ,需要编写一个对视频流采集 的应

用程序。 系统 中采用的是 m pg s em, 本 je—t a 这是一个视频 r 流服务器 , 里面有对整个视频采集及处理发送 的过程 。 首 先要 将其移植 到 目标板 上 , 也就 是 ¥ C 4 0平 台 , 3 24 并在 目标板上运行此视频流服务器 , 命令如下 :

Verilog学习----有限状态机的设计的一般步骤

Verilog学习----有限状态机的设计的⼀般步骤有限状态机的设计的⼀般步骤:(1)逻辑抽象,得出状态转换图。

就是把给出的⼀个实际逻辑关系表⽰为时序逻辑函数,可以⽤状态转换表来描述,也可以⽤状态转换图来描述。

这就需要:1)分析给定的逻辑问题,确定输⼊变量、输出变量以及电路的状态数。

通常是取原因(或条件)作为输⼊变量,取结果作为输出变量。

2)定义输⼊、输出逻辑状态的含意,并将电路状态顺序编号。

3)按照要求列出电路的状态转化表或画出状态图。

这样,就把给定的逻辑问题抽象到⼀个时序逻辑函数了。

(2)状态简化。

如果在状态转换图中出现这样两个状态,它们在相同的的输⼊下转换到同⼀状态去,并得到⼀样的输出,则称为等价状态。

显然等价状态是重复的,可以合并为⼀个。

电路的状态数越少,存储电路也就越简单。

状态化简的⽬的就在于将等价状态尽可能地合并,以得到最简状态图。

(3)状态分配。

状态分配⼜称状态编码。

通常有很多编码⽅法,编码⽅案选择得当,设计的电路可以简单,反之,选择的不好,则设计的电路就会复杂的多。

在实际设计中,须综合考虑电路的复杂度与电路性能之间的折衷。

在触发器资源丰富的FPGA设计中,采⽤独热码既可以使电路性能得到保障⼜可以充分利⽤其触发器数量多的优势,也可以采⽤输出编码的状态指定来简化电路结构,并提⾼状态机的运⾏速度。

(4)选定触发器的类型并求出状态⽅程、驱动⽅程和输出⽅程。

(5)按照⽅程得出逻辑图。

⽤Verilog来描述有限状态机,可以充分发挥硬件描述语⾔的抽象建模能⼒,使⽤always块语句和case(if)等条件语句及赋值语句即可⽅便实现。

有限状态机

实验五有限状态机一、实验目的:本次实验通过Verilog 硬件语言编写摩尔型有限状态机和米勒型有限状态机,掌握采用有限状态机产生各种控制信号的原理,熟悉如何选用合适的有限状态机进行电路设计,通过实验进一步了解原理图编辑方法和仿真方法。

二、实验要求:1、利用Verilog 硬件语言,参考提供的源程序,设计一个采用摩尔型有限状态机实现的流水灯控制程序;2、利用Verilog 硬件语言,参考提供的源程序,设计一个采用米勒型有限状态机实现的串行口发送程序;3、利用Verilog 硬件语言,参考提供的源程序,设计一个采用米勒型有限状态机实现的串行口接收程序;4、利用原理图编辑方法,将串行口发送和接收模块进行连接,实现完整的串行通信电路,并对该电路进行仿真。

摩尔型有限状态机实现的流水灯源程序module sled(clk,led);input clk;output [7:0] led;reg [7:0] led;reg[2:0] state;parameter s0=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100,s5=3'b101,s6=3'b110,s7=3'b111;always @(posedge clk)case(state)s0: begin state<=s1; led<=8'b00000001; end s1: begin state<=s2; led<=8'b00000010; end s2: begin state<=s3; led<=8'b00000100; end s3: begin state<=s4; led<=8'b00001000; end s4: begin state<=s5; led<=8'b00010000; end s5: begin state<=s6; led<=8'b00100000; end s6: begin state<=s7; led<=8'b01000000; end s7: begin state<=s0; led<=8'b10000000; end endcaseendmodule米勒型有限状态机实现的串行口发送源程序module s_tx(clk,en,dain,txd);input clk,en;input[7:0] dain;output txd;reg [7:0] da_temp;reg txd;reg [3:0] state;parameter swait=4'b0000,star=4'b0001,s1=4'b0010,s2=4'b0011,s3=4'b0100,s4=4'b0101,s5=4'b0110,s6=4'b0111,s7=4'b1000,s8=4'b1001,stop=4'b1010;always @(posedge en)da_temp<=dain;always @(posedge clk)if (!en) beginstate<=swait;txd<=1;endelsecase(state)swait: begin state<=star;txd<=1; endstar: begin state<=s1; txd<=0; ends1: begin state<=s2; txd<=da_temp[7]; ends2: begin state<=s3; txd<=da_temp[6]; ends3: begin state<=s4; txd<=da_temp[5]; ends4: begin state<=s5; txd<=da_temp[4]; ends5: begin state<=s6; txd<=da_temp[3]; ends6: begin state<=s7; txd<=da_temp[2]; ends7: begin state<=s8; txd<=da_temp[1]; ends8: begin state<=stop; txd<=da_temp[0]; endstop: begin state<=stop; txd<=1; endendcaseendmodule米勒型有限状态机实现的串行口接收源程序module s_rx(clk,dain,daout);input clk,dain;output [7:0] daout;reg [7:0] daout;reg [7:0] da_temp;reg [3:0] state;parameter star=4'b0000,s1=4'b0010,s2=4'b0011,s3=4'b0100,s4=4'b0101,s5=4'b0110,s6=4'b0111,s7=4'b1000,s8=4'b1001,stop=4'b1010;always @(negedge clk)case (state)star: if (dain)state<=star;elsestate<=s1;s1:begin state<=s2; da_temp[7]<=dain; ends2:begin state<=s3; da_temp[6]<=dain; ends3:begin state<=s4; da_temp[5]<=dain; ends4:begin state<=s5; da_temp[4]<=dain; ends5:begin state<=s6; da_temp[3]<=dain; ends6:begin state<=s7; da_temp[2]<=dain; ends7:begin state<=s8; da_temp[1]<=dain; ends8:begin state<=stop;da_temp[0]<=dain; end stop:if (!dain)state<=stop;elsebeginstate<=star;daout<=da_temp;endendcaseendmodule串行口通信系统原理图电路。

verilog有限状态机实验报告(附源代码)

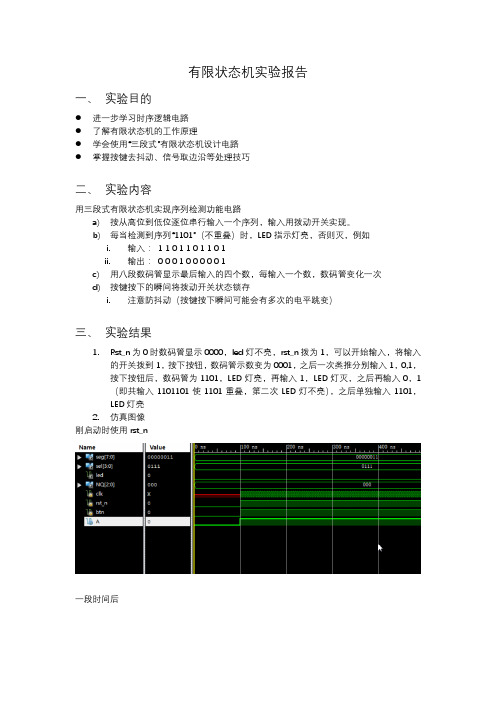

有限状态机实验报告一、实验目的●进一步学习时序逻辑电路●了解有限状态机的工作原理●学会使用“三段式”有限状态机设计电路●掌握按键去抖动、信号取边沿等处理技巧二、实验内容用三段式有限状态机实现序列检测功能电路a)按从高位到低位逐位串行输入一个序列,输入用拨动开关实现。

b)每当检测到序列“1101”(不重叠)时,LED指示灯亮,否则灭,例如i.输入:1 1 0 1 1 0 1 1 0 1ii.输出:0 0 0 1 0 0 0 0 0 1c)用八段数码管显示最后输入的四个数,每输入一个数,数码管变化一次d)按键按下的瞬间将拨动开关状态锁存i.注意防抖动(按键按下瞬间可能会有多次的电平跳变)三、实验结果1.Rst_n为0时数码管显示0000,led灯不亮,rst_n拨为1,可以开始输入,将输入的开关拨到1,按下按钮,数码管示数变为0001,之后一次类推分别输入1,0,1,按下按钮后,数码管为1101,LED灯亮,再输入1,LED灯灭,之后再输入0,1(即共输入1101101使1101重叠,第二次LED灯不亮),之后单独输入1101,LED灯亮2.仿真图像刚启动时使用rst_n一段时间后其中Y代表输出,即控制led灯的信号,sel表示数码管的选择信号,seg表示数码管信号四、实验分析1、实验基本结构其中状态机部分使用三段式结构:2、整体结构为:建立一下模块:Anti_dither.v输入按键信号和时钟信号,输出去除抖动的按键信号生成的脉冲信号op这一模块实现思路是利用按钮按下时会持续10ms以上而上下抖动时接触时间不超过10ms来给向下接触的时间计时,达到上限时间才产生输出。

Num.v输入op和序列输入信号A,时钟信号clk和复位信号,复位信号将num置零,否则若收到脉冲信号则将num左移一位并将输入存进最后一位。

输出的num即为即将在数码管上显示的值Scan.v输入时钟信号,对其降频以产生1ms一次的扫描信号。

有限状态机的Verilog设计与研究

微电子学与计算机

!""# 年第 !$ 卷第 !! 期

#$%&’( #$%&’() -./01

俞莉琼 付宇卓

# 上海交通大学微电子学院 上海 .<<<4< $ 摘 要 = 本文研究了用 "#$%&’( 实现有限状态机的各种不同的编码方式和描述风格 ! 并从综合 " 毛刺 " 面积 " 速度这

几 方 面 研 究 了不 同 实 现 方 式 的 利 弊 # 最 后 ! 以 >’? 芯 片 中 ,/@ @$A%;’$ 有 限 状 态 机 为 例 ! 我 们 用 ,#B%(6 ?’CD&%#$ $,? % 对七种设计进行了综合 ! 并分析了综合后的面积和时延信息 # 关键词 = "#$%&’( ! 有限状态机 ! 综合 ! 状态编码

态机 ! 这样不仅可以简化状态的定义 * 修改和调试 " 还 可 以 用 一 些 专 门 的 %-, 工 具 % 如 -" <4=3’ *-"

OPQ 从综合角度而言 " 组合输出消耗了一部分时

钟周期 " 即增加了由它驱动的下一个模块的输入延 时 %:02H= @)4’/ $! 这样不利于综合脚本的编写和综 合优化算法的实现 ! 综合的基本技巧是将一个设计 划分成 只 有 寄 存 器 输 出 且 所 有 的 组 合 逻 辑 仅 存 在 于模块输入端以及内部寄存器之间的各个子模块 ! 这样不仅能在综合脚本中使用统一的输入延时 " 还 能得到更优化的综合结果 ! 为了改进组合输出所带来的上述问题 " 可以改 用时序逻辑来描述输出向量 " 如后面两种描述风格 所示 !

EDA技术实用教程Verilog四版第8章

第8章有限状态机设计技术有限状态机及其设计技术是实用数字系统设计中的重要组成部分,也是实现高效率、高可靠和高速控制逻辑系统的重要途径。

广义而论,只要是涉及触发器的电路,无论电路大小,都能归结为状态机。

因此,对于数字系统设计工程师,面对的只要是时序电路设计,状态机的概念则是必须贯穿于整个设计始终的最基本的设计思想和设计方法论;只有从电路状态的角度去考虑,才能从根本上把握可靠,高效的时序逻辑的设计关键。

在现代数字系统设计中,状态机的设计对系统的高速性能、高可靠性、稳定性都具有决定性的作用。

读者对于此章的学习必须给于高度的关注。

有限状态机应用广泛,特别是对那些操作和控制流程非常明确的系统设计,在数字通信领域、自动化控制领域、CPU设计领域以及家电设计领域都拥有重要的和不可或缺的地位。

尽管到目前为止,有限状态机的设计理论并没有增加多少新的内容,然而面对先进的EDA工具、日益发展的大规模集成电路技术和强大的硬件描述语言,有限状态机在其具体的设计和优化技术以及实现方法上却有了许多新的内容和新的实现方法。

本章重点介绍用Verilog设计不同类型有限状态机的方法,同时考虑EDA工具和设计实现中许多必须重点关注的问题,如优化、毛刺的处理及编码方式等方面的问题。

8.1 Verilog状态机的一般形式就理论而言,任何时序模型都可以归结为一个状态机。

如只含一个D触发器的二分频电路或一个普通的4位二进制计数器都可算作一个状态机;前者是两状态型状态机,后者是16状态型状态机,都属于一般状态机的特殊形式。

但这些并非出自明确的自觉的设计目的和合理的状态机设计方案而导致的时序模块,未必能成为一高速、高效、稳定、控制流畅、修改便捷和功能目标明确的真正意义上的状态机。

基于现代数字系统设计技术自觉意义上的状态机的HDL表述形态和表述风格具有一定的典型性和格律化。

正是据此,现代EDA的综合器能从不同表述形态的HDL程序中轻易地萃取出(Extract)状态机设计,并加以多侧面多目标和多种形式的优化;甚至还能能动地改变、脱离甚至不遵从设计程序文字上的表述,而按照综合器自己的方式去优化状态机的设计。

Verilog HDL数字设计教程(贺敬凯)第5章

第5章 同步有限状态机设计

其仿真结果如图5-11所示。 【例5-5】 对应于步骤四的Verilog HDL建模。 ///产生JK激励信号:D触发器的激励d---->JK触发器的激励J 和K

module D_JK(d,q,j,k);

input d,q; output reg j,k;

always @(d,q)

利用多余状态,卡诺图化简后的激励方程和输出方程为:

n n D1 Q0 A,D0 A, Y Q1 A

第六步:画出逻辑图并检查自启动能力。逻辑图如图57所示。

第5章 同步有限状态机设计

图5-7 例5-1的逻辑图

第5章 同步有限状态机设计

经检查,该电路具有自启动能力。 至此解题完毕。 以上六步,我们均可以采用Verilog HDL进行电路建模, 下面从后向前对各个步骤进行建模,见例5-2至例5-9。

第5章 同步有限状态机设计

程序说明:

(1) 例5-4的实现要求得出输出方程和激励方程,然后才

能对时序逻辑电路建模。这种建模方法同例5-2一样,需要 手工做大量复杂的工作,而不是由计算机来完成复杂的计算 工作。 (2) 该模块的综合结果如图5-12所示。

第5章 同步有限状态机设计

图5-12 例5-4的综合结果

第5章 同步有限状态机设计

【例5-3】 对例5-2的改进——消除毛刺。 module input clk,A; output reg Y; wire q0,q1; mydff_2 dff0(.D(A),.Q(q0),.clk(clk)), dff1(.D(A&q0), .Q(q1), .clk(clk)); always @(posedge clk) Y= q1 & (~A); endmodule 该模块的综合结果如图5-10所示。 fsm_1(clk,A,Y);

基于Verilog HDL的有限状态机设计与描述

不会 进 入 死 循 环 , 使 由于 某 些 扰 动 进 入 非 法 状 态 , 能 很 快 即 也

的恢 复 到 正 常 的 状 态 循 环 中来 。

能 力 , 系统 在 系 统 级 或 寄 存 器 传 输 级 进 行 描 述 。 对

限状 态 机 已经 成 为关 键 。 传 统 的 有 限 状 态 机 的 描 述 方 式 有 状 态 转 移 图 , 态 转 移 状

图 1 有 限状 态机 结 构

() 限状 态 机 要 安 全 , 定 性 高 。这 就 要求 有 限 状 态 机 1有 稳

列 表 两 种 。随着 E A 技 术 的发 展 , 们 开 始 用 硬 件 描 述 语 言 D 人

sye n ei gHDL d srpin f S r to u e , s bl , ra a it, s e da dae fh s ls ed srb d Fn l , tls dV rl a o ecit s F M fei rd c d t it o o i n a i y e d bl i y p e rao tees e e c e . ial n y t r a i y

维普资讯

第 2 卷 第 4 9 期

VO . 9 12 N O. 4

计 算机 工 程 与设 计

Co mp t rE g n e n n sg u e n i e r g a d De in i

20 年 2 08 月

F b.2 0 e 0 8

文章编号 :0 072 20 ) 40 5 —3 10 —04(0 8 0 —9 80

De in a dd s rp in o n t tt c i eb s d o e i gHDL sg n e c t f i saema h n a e nv r o i o i f e l

第6章 有限状态机设计技术

A/K1=0

Start

!Reset /K2=0 K1=0 !Reset /K2=0 K1=0

Idle !Reset /K2=0 K1=0

!A Stop

(!Reset |!A )/ K2=0 K1=1

Clear

A/K2=1

图3.4 状态转移图

有限状态机的Verilog描述

1. 定义模块名和输入输出端口; 2. 定义输入、输出变量或寄存器; 3. 定义时钟和复位信号; 4. 定义状态变量和状态寄存器; 5. 用时钟沿触发的always块表示状态转移过程; 6. 在复位信号有效时给状态寄存器赋初始值; 7. 描述状态的转换过程:符合条件,从一个状态到

- 状态机可用于产生在时钟跳变沿时刻开关的 复杂的控制逻辑,是数字逻辑的控制核心。

Mealy 状态机

下一个状态 = F(当前状态,输入信号); 输出信号 = G(当前状态,输入信号);

输入

下一状态 激励信号 的逻辑

F

状态 寄存器

clk 输入

当前状态

输出逻辑 输出

G

时钟信号clk

图1 . 时钟同步的状态机结构 (Mealy 状态机)

表示方法之四

用输出指定的码表示状态的状态机

方法四采用了另一种方法:直接把状态码定义 为输出。也就是把状态码的指定与状态机控制 的输出联系起来,把状态的变化直接用作输出, 这样做可以提高输出信号的开关速度并节省电 路器件。这种设计方法常用在高速状态机中。 建议同学们在设计高速状态机时采用方法四的 风格。例中state[3] 和state[0]分别表示前 面两个例子中的输出K2和K1。

Clear: if (!A) state <= ClearToIdle;

有限状态机的Verilog设计与研究

谢谢观看

end

endcase

end

end

endmodule

该有限状态机使用三个寄存器来存储当前的状态,并在每个时钟周期检查输入 信号和当前状态来确定下一个状态。如果接收到读取信号,它将输出与输入相 同的数据,并在下一个时钟周期回到空闲状态。如果接收到写入信号,它也会 输出与输入相同的数据,并在下一个时钟周期回到空闲状态。该有限状态机的 设计是可综合的,因为它只包含基本的逻辑门和触发器,并且它的输出只依赖 于当前的状态和输入信号。

end else begin state <= STANDBY;

end

end

endcase

end

end

assign led = state;

endmodule

有限状态机的测试

为了确保有限状态机的正确性,需要对Verilog设计的有限状态机进行测试。 以下是测试过程中需要注意的几点:

end else begin state <= IDLE;

end

end

FLASH: begin

if (flash_timeout) begin state <= STANDBY;

end else begin state <= FLASH;

end

end

STANDBY: begin

if (activate) begin state <= FLASH;

有限状态机的Verilog设计与研究

01 引言

目录

02 有限状态机的设计

03 reg [1:0] state;

05

end else begin

04

if (rst) begin

06

Verilog 的有限状态机

基于Verilog HDL的有限状态机1.有限状态机1.1 概述有限状态机是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。

有限状态机又可以认为是组合逻辑和寄存器逻辑的一种组合。

状态机特别适合描述那些发生有先后顺序或者有逻辑规律的事情,其实这就是状态机的本质。

状态机就是对具有逻辑顺序或时序规律的事件进行描述的一种方法在实际的应用中根据状态机的输出是否与输入条件相关,可将状态机分为两大类,即摩尔 (Moore)型状态机和米勒 (Mealy) 型状态机。

图 1Mealy型状态转移图1.2 状态机的描述方法状态机的描述方法多种多样,将整个状态机写到1个always 模块里,在该模块中既描述状态转移,又描述状态的输入和输出,这种写法一般被称为一段式FSM 描述方法;还有一种写法是使用两个always模块,其中一个always 模块采用同步时序的方式描述状态转移,而另一个模块采用组合逻辑的方式判断状态转移条件,描述状态转移规律,这种写法被称为两段式FSM 描述方法;还有一种写法是在两段式描述方法的基础上发展而来的,这种写法使用3 个always模块,一个always 模块采用同步时序的方式描述状态转移,一个采用组合逻辑的方式判断状态转移条件,描述状态转移规律,第三个always 模块使用同步时序电路描述每个状态的输出,这种写法称为三段式写法。

1.3 FSM的状态编码二进制码(Binary)和格雷码(Gray)属于压缩状态编码,这种编码的优点是使用的状态向量最少,但是需要较多的逻辑资源用来状态译码。

二进制码从一个状态转换到相邻状态时,可能有多个比特位发生变化,易产生中间状态转移问题,状态机的速度也要比采用其它编码方式慢。

格雷码两个相邻的码值仅有一位就可区分,这将会减少电路中相邻物理信号线同时变化的情况,因而可以减少电路中的电噪声。

Johnson码也有同样的特点,但是要用较多的位数。

独热码(One-hot)指对任意给定的状态,状态寄存器中只有l位为1,其余位都为0。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

“101”序列检测器的Verilog描述(三个过程)

always @(state or x) 态*/ begin case (state) S0:begin end S1:begin else end /*该过程定义次

if(x) else if(x)

next_state<=S1; next_state<=S0; next_state<=S1; next_state<=S2;

频率计控制器设计举例

设计一个自动转换量程的频率计控制器,

用Mealy状态机实现。

cntlow = 1

进入100K量程(状态A) reset = 1; std_f_sel = 00 cntlow = 1 进入100K量程(状态C) reset = 1; std_f_sel = 01 cntlow = 1

module FSM( clk, clr, out, start, step2, step3 ); input clk, clr, start, step2, step3; output[2:0] out; reg[2:0] out; reg[1:0] state, next_state; parameter state0 = 2’b00, state1 = 2’b01, // 状态编码 state2 = 2’b11, state3 = 2’b10; // 格雷码

always @( posedge clk or posedge clr )

begin

if( clr ) else state <= state0; // 定义初态 state <= next_state;

end

always @( state or start or step2 or step3 ) // 状态转换

状态编码的定义

状态编码的定义方式2:用'define语句定义 'define state1 2'b00 //不要加分号“;” 'define state2 2'b01 'define state3 2'b11 'define state4 2'b10 case(state) 'state1: …; //调用,不要漏掉符号“'” 'state2: …; …… 要注意两种方式定义与调用时的区别,一般情况下,更倾向于 采用方式1来定义状态编码。一般使用case、casez和casex语 句来描述状态之间的转换,用case语句表述比用if-else语句更 清晰明了。

100K量程测量(状态B) reset = 0; std_f_sel = 00 cntover = 1 100K量程测量(状态D) reset = 0; std_f_sel = 01 cntover = 1

进入100K量程(状态E) reset = 1; std_f_sel = 11

1K量程测量(状态D) reset = 0; std_f_sel = 11

米里型(Mealy)状态机

输入 / 输出

现态

次态

Moore型状态图

module fsm(clk,clr,z,qout);//模5计数器 input clk,clr; output reg z; output reg[2:0] qout; always @(posedge clk or posedge clr) //此过程定义状态转换 begin if(clr) qout<=0; //异步复位 else case(qout) 3'b000: qout<=3'b001; 3'b001: qout<=3'b010; 3'b010: qout<=3'b011; 3'b011: qout<=3'b100; 3'b100: qout<=3'b000; default: qout<=3'b000; /*default语句*/ endcase end always @(qout) /*此过程产生输出逻辑*/ begin case(qout) 3'b100: z=1'b1; default:z=1'b0; endcase end endmodule

input clk, clr, start, step2, step3; output[2:0] out; reg[2:0] out; reg[1:0] state, next_state; parameter state0 = 2’b00, state1 = 2’b01, // 状态编码 state2 = 2’b11, state3 = 2’b10; // 格雷码

“101”序列检测器的Verilog描述(三个过程)

module fsm1_seq101(clk,clr,x,z);

input clk,clr,x; output reg z; reg[1:0] state,next_state; parameter S0=2'b00,S1=2'b01,S2=2'b11,S3=2'b10; /*状态编码,采用格雷(Gray)编码方式*/ always @(posedge clk or posedge clr) /*该过程定义当前状态*/ begin if(clr) state<=S0; //异步复位,s0为起始状态 else state<=next_state; end

EDA技术与应用

第八章 有限状Байду номын сангаас机设计

教学重点

MOORE状态机

MEALY状态机

有限状态机的几种描述方式

有限状态机的状态编码

8.1 有限状态机

构成

组合逻辑 状态译码、产生输出

时序逻辑 存储状态

分类

Moore 输出是现态的函数

Mealy 输出是现态和输入的函数

摩尔型(Moore)状态机

“101”序列检测器的Verilog描述(三个过程)

S2:begin if(x) next_state<=S3; else next_state<=S0; end S3:begin if(x) next_state<=S1; else next_state<=S2; end default: next_state<=S0; /*default语句*/ endcase end

8.2 有限状态机的Verilog描述

(1)用三个过程描述:即现态(CS)、次态(NS)、 输出逻辑(OL)各用一个always过程描述。 (2)双过程描述(CS+NS、OL双过程描述):使用两 个always过程来描述有限状态机,一个过程描述现态和次 态时序逻辑(CS+NS);另一个过程描述输出逻辑(OL)。 (3)双过程描述(CS、NS+OL双过程描述):一个过 程用来描述现态(CS);另一个过程描述次态和输出逻辑 (NS+OL)。 (4)单过程描述:在单过程描述方式中,将状态机的现 态、次态和输出逻辑(CS+NS+OL)放在一个always过程 中进行描述。

next_state <= state0;

always @( state ) // 状态译码及输出 begin case( state ) state0: out = 3'b001; state1: out = 3'b010; state2: out = 3'b100; state3: out = 3'b111; default: out = 3'b001; endcase end endmodule

output reg z;

reg[1:0] state; parameter S1=2'b01, S2=2'b11, S0=2'b00,

S3=2'b10;/*状态编码,采用格雷(Gray)编码方

式*/

“101”序列检测器(单过程描述)

always @(posedge clk or posedge clr) Begin if(clr) state<=S0; //异步复位,s0为起始状态 else case(state) S0:begin if(x) begin state<=S1; z=1'b0;end else begin state<=S0; z=1'b0;end end S1:begin if(x) begin state<=S1; z=1'b0;end else begin state<=S2; z=1'b0;end end S2:begin if(x) begin state<=S3; z=1'b0;end else begin state<=S0; z=1'b0;end end S3:begin if(x) begin state<=S1; z=1'b1;end else begin state<=S2; z=1'b1;end end default:begin state<=S0; z=1'b0;end /*default语句*/ endcase end endmodule

always @(state) /*该过程产生输出逻辑*/ begin case(state) S3: z=1'b1; default:z=1'b0; endcase end endmodule

“101”序列检测器(单过程描述)

module fsm4_seq101(clk,clr,x,z); input clk,clr,x;

start = 0 clr = 1 State0 out = 001 step3 = 1 start = 1